# Development of a Transmitter for High Temperature Ultrasound Imaging

a thesis by Espen Håland

FOR THE DEGREE OF

MASTER OF SCIENCE IN PHYSICS

Department of Physics and Technology University of Bergen June 2016

IN COLLABORATION WITH:

#### Abstract

This thesis presents the development and testing of a new transmitter in an ultrasound imaging tool used for imaging the inside of oil wells in temperatures of up to 180 °C. The imaging tool can have up to 288 transducer elements, driven by 16 transmitters. This generates a need for lots of switches, increasing the load capacitance, which results in a demanding current requirement.

Every part of the original transmitter is analyzed and potential improvements is proposed and implemented. After improving the design and component choices, a new layout is performed for one channel, using the same area as the old channel. Both the old and new design is soldered on one PCB to test them under the exact same circumstances.

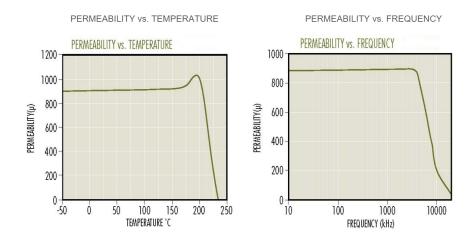

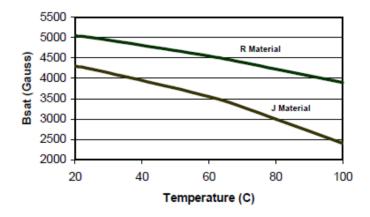

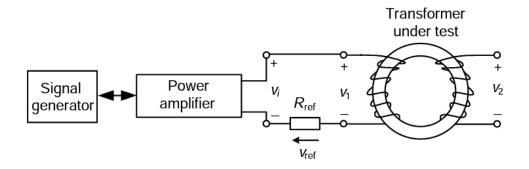

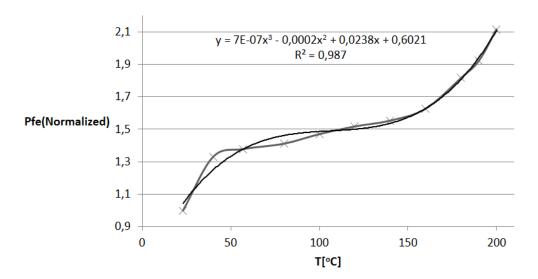

Tests have been done during the design process to verify components and to obtain coefficients for calculating core loss. This is used for calculating core loss and optimizing the core size.

With ultrasound imaging, the resolution is highly dependent on signal frequency. This is why Bergen Technology Center uses ultrasound transducers with upper frequencies of up to 6 MHz, especially for thickness measurements. But, the transmitter in use today for driving the transducers is only capable of maximum output signals up to 2 MHz.

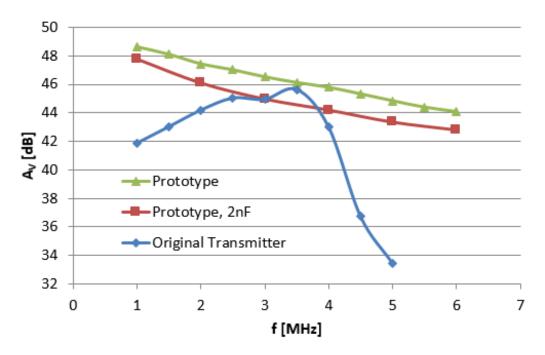

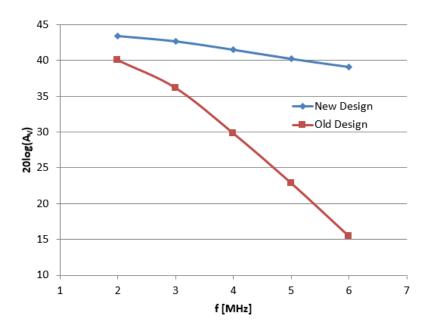

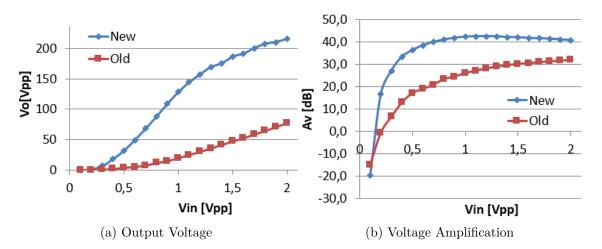

The new design has been tested both with dummy loads and in a complete tool. Tested with a complete ultrasound imaging tool, the new transmitter showed an increase in amplification from the old design of 24 dB at 6 MHz.

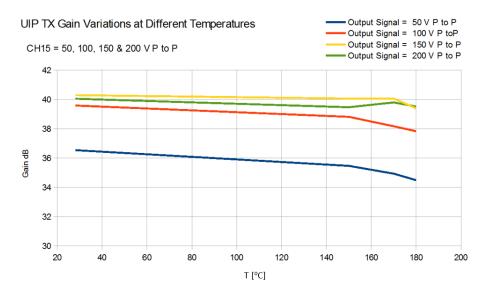

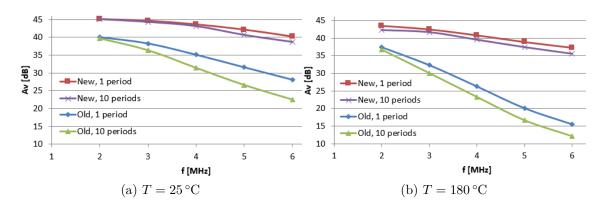

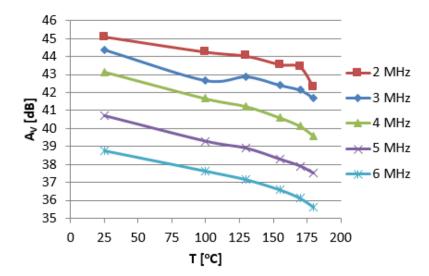

Temperature tests have been performed with dummy loads up to an ambient temperature of 180 °C. With maximum frequency, temperature and frame rate, the new design shows an amplification of 36 dB, 23 dB higher than the old design under the same circumstances. Temperature rise of the critical components has been logged during the tests, and is used with power dissipation for calculating thermal resistance.

Improvements has also been proposed for other parts of the imaging tool. New switches are proposed that will reduce the switch capacitance with 29 %, improving slew rate and output signal amplitude. A modification of the input signal is proposed that will decrease the output pulse duration and give better axial resolution.

## **Preface**

The work in this thesis has been carried out within the Research and Development department at Bergen Technology Center (BTC) between August 2015 and June 2016. It is submitted for the degree of Master of Science in Physics at the University of Bergen June 1st, 2016.

## Acknowledgments

First and foremost I would like to thank my supervisor, Kjetil Ullaland, for continuous help and guidance with writing this thesis. Your effectiveness and high working capacity is inspiring.

I am grateful for being given the opportunity to write my masters thesis at BTC by Dag-Håkon Frantzen and Tarjei Rommetveit. Further, I would like to thank my co-supervisor Nils Midtseter at BTC for all the valuable discussions and feedback throughout this work.

I would also like to extend my thanks to all colleagues at BTC for taking time to share their knowledge about ultrasound imaging.

Finally, I would like to thank my fellow students for all the interesting discussions and for making these years fly by.

Espen Håland Bergen, June 2016

# Contents

| Pı       | refac | e       |                                               | V  |

|----------|-------|---------|-----------------------------------------------|----|

| 1        | Intr  | oducti  | on                                            | 1  |

|          | 1.1   | Oil W   | ell Imaging                                   | 1  |

|          | 1.2   | Ultras  | ound Imaging Platform                         | 3  |

|          | 1.3   | About   | This Work                                     | 6  |

| <b>2</b> | Des   | ign Ar  | nalysis                                       | 9  |

|          | 2.1   | Transı  | mitter Load                                   | 10 |

|          |       | 2.1.1   | Possible Improvements on Transmitter Load     | 12 |

|          | 2.2   | Outpu   | at Stage                                      | 13 |

|          |       | 2.2.1   | Improvements Needed for Output Stage          | 14 |

|          |       | 2.2.2   | Thermal Considerations for Output Transistors | 17 |

|          | 2.3   | Transf  | ormer                                         | 19 |

|          |       | 2.3.1   | Core Saturation                               | 19 |

|          |       | 2.3.2   | Asymmetrical Drive of the Output Transistors  | 21 |

|          |       | 2.3.3   | Thermal Considerations for Transformer        | 21 |

|          | 2.4   | Differe | ential Amplifier                              | 27 |

|   |                                 | 2.4.1                                        | Stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28                      |

|---|---------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|   |                                 | 2.4.2                                        | Possible Improvements for Differential Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                      |

|   |                                 | 2.4.3                                        | Thermal Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                      |

|   | 2.5                             | Input                                        | termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33                      |

|   |                                 | 2.5.1                                        | Possible Improvements for Input Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                      |

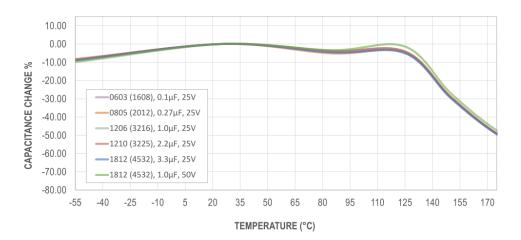

|   | 2.6                             | Passiv                                       | e Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35                      |

|   |                                 | 2.6.1                                        | Decoupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                      |

|   | 2.7                             | Diodes                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                      |

|   |                                 | 2.7.1                                        | Transient Voltage Suppression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                      |

|   |                                 | 2.7.2                                        | Output Diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40                      |

| 3 | Pro                             | totype                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43                      |

| • | 3.1                             | 0.2                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

|   | 0.1                             |                                              | d Circuit Board Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |

|   |                                 |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

|   |                                 | 3.1.1                                        | Footprints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                      |

| 4 | Test                            |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br><b>49</b>         |

| 4 | <b>Test</b> 4.1                 | t and (                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49                      |

| 4 |                                 | t and (                                      | Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>49</b><br>49         |

| 4 | 4.1                             | t and (                                      | Characterization Performed Before the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>49</b><br>49<br>51   |

| 4 | 4.1                             | t and C                                      | Characterization Performed Before the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49<br>49<br>51<br>51    |

| 4 | 4.1                             | Tests Prelim                                 | Characterization  Performed Before the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49<br>49<br>51<br>51    |

| 4 | 4.1                             | Tests 1 Prelim 4.2.1 4.2.2 4.2.3             | Characterization  Performed Before the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49<br>51<br>51<br>52    |

| 4 | 4.1 4.2                         | Tests Prelim 4.2.1 4.2.2 4.2.3 System        | Characterization Performed Before the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49 51 51 52 53          |

| 4 | 4.1<br>4.2<br>4.3               | Tests Prelim 4.2.1 4.2.2 4.2.3 System Linear | Characterization  Performed Before the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49 49 51 52 53 55       |

| 4 | 4.1<br>4.2<br>4.3<br>4.4        | Tests Prelim 4.2.1 4.2.2 4.2.3 System Linear | Characterization  Performed Before the Thesis  Ainary Tests  Operational Amplifier  Output Transistors  Core Loss  In Test  Interpolation Amplifier  Output Transistors  Core Loss  In Test  Interpolation Amplifier  Interpolation Amplifier  Output Transistors  Core Loss  In Test  Interpolation Amplifier  Interpolation Amp | 49 51 52 53 55 56       |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Tests Prelim 4.2.1 4.2.2 4.2.3 System Linear | Characterization  Performed Before the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49 49 51 52 53 55 56 57 |

|              | 4.7  | Single Period Test   | 62         |

|--------------|------|----------------------|------------|

|              | 4.8  | Amplifier Filter     | 63         |

| 5            | Disc | cussion              | 65         |

|              | 5.1  | Results              | 65         |

|              | 5.2  | Test Setup           | 66         |

| 6            | Con  | clusion              | 69         |

| $\mathbf{A}$ | Tra  | nsformer Loss Theory | 71         |

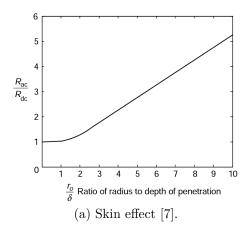

|              | A.1  | Skin Effect          | 71         |

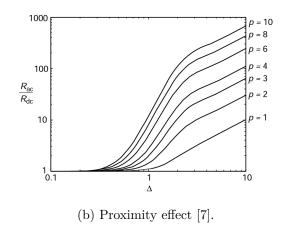

|              | A.2  | Proximity Effect     | 72         |

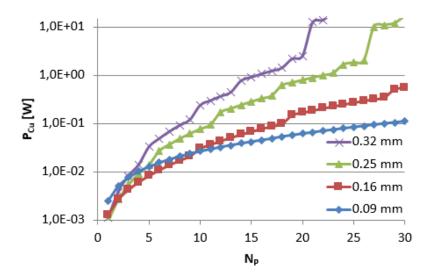

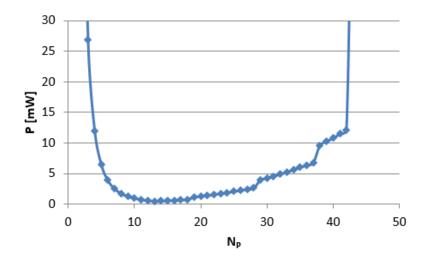

|              | A.3  | Core Loss            | 74         |

| В            | Dat  | asheets              | <b>7</b> 5 |

| $\mathbf{C}$ | Mea  | asurements           | 77         |

| Al           | obre | viations             | 79         |

## CHAPTER 1

## Introduction

## 1.1 Oil Well Imaging

Oil wells consist of a large number of steel pipes joined together to achieve a continuous hollow tube, extending several kilometers down through the earth surface. Oil companies are dependent on continuous production and need to be able to image the inside of the well to discover corrosion, fractures and other irregularities that can threaten well integrity. Objects can also get stuck in the oil well, making it essential to have an image of the situation to be able to perform a successful fishing operation.

A fishing operation is performed when an object is stuck in the well. The object and its surroundings is mapped in 3D to be able to choose an appropriate tool to retrieve it to the surface.

There are many imaging tools on the market today, including mechanical finger tools, optical cameras, X-ray imaging tools and ultrasound imaging tools. What makes developing downhole imaging tools challenging is the size restriction due to small pipe diameter as well as the demand for operating in high temperature and high pressure as depth increases. It can also be difficult to image through a mixture of oil, gas and water, depending on the imaging technology.

Mechanical finger tools are available for use in temperatures up to 177 °C. The principle is to let a set of fingers be pressed out from the cylindrical tool and continuously touch the inner wall. By monitoring the position of the fingers it is possible to measure the inner diameter. This tool is not suited for fishing operations. The accuracy depends on mechanical tolerances which will increase due to continuous wear of the fingers. The fingers can also get stuck in cracks and sediments.

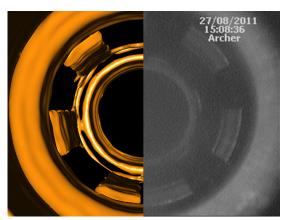

(a) 3D ultrasound image of a slotted steel pipe [3].

(b) Ultrasound image (left) and optical image (right) of a slotted steel pipe [3].

Figure 1.1: Images of a slotted steel pipe.

In optical cameras, light is converted to electrical signals. The high opacity of oil allows only small amounts of light to pass through, reducing the signal received in the camera. This can be prevented by filling the well with a transparent liquid, but is time consuming and costly. There are optical cameras that only fill a small volume in front of the tool with a transparent liquid, but these are limited to a maximum depth of  $1000\,\mathrm{m}$ .

The principle behind ultrasound imaging is to transmit an acoustic signal and measure the time it takes to reach the inner wall, reflect and return to the tool. Water and oil have similar acoustic properties, making it possible to capture images with high accuracy through this mixture, which is the most common content of production wells.

The large difference in acoustic impedance between gas and fluids like oil and water causes high signal reflection. This reduces the amount of acoustic energy making it all the way to the object you want to image, and thus low signal amplitudes for the received signal. Imaging through a mixture of oil and gas can therefore be difficult, especially if the bubbles are large, blocking the entire scan area.

A comparison between an image from the Ultrasound Imaging Platform (UIP) and an image from an industry leading optical camera is shown in 1.1b. The image shows a steel pipe which is slotted to allow flow from the reservoir into the pipe.

When drilling a well, drilling fluids (often referred to as mud) can be injected at the point of the drill bit to cool down and lubricate the drill bit. It also transports rock fragments towards the surface[28]. The acoustic properties of drilling fluids makes it difficult to use ultrasound imaging. Another situation showing difficulties for the UIP is through thick layers of sand that typically occur on the low side of non-vertical wells, depending on the inclination.

Figure 1.2: X-ray images of a wrench. 2D (middle) and 3D (right). The left image is from an optical camera [27].

A downhole imaging tool based on X-ray technology was recently announced, being able to image in all production fluids. It can also image through drilling muds[26] and sand covered objects, but is at the time limited for use up to a temperature up to 100 °C. A tool able to operate in temperatures up to 130 °C is said to be available i the second half of 2016[27]. 2D and 3D images from this X-ray tool is shown in Figure 1.2.

## 1.2 Ultrasound Imaging Platform

Bergen Technology Center AS (BTC), a wholly owned subsidiary of Archer AS, designs, develops and manufactures ultrasound imaging tools for downhole operation. The newest tool, UIP, produce high-resolution 3D images and measurements of well components. It has no moving parts and can operate in all production fluids.

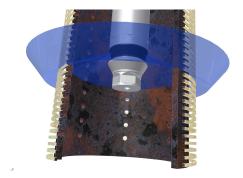

By changing transducers it can be configured to look along the well for fishing operations, as shown in 1.3a. It can also look sideways for measuring cracks, corrosion and sediments, as shown in 1.3b.

(a) UIP configured for looking along the well [3].

(b) UIP configured for looking sideways [3].

Figure 1.3: UIP configurations.

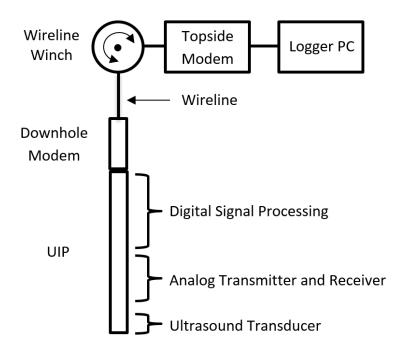

Figure 1.4: Block schematic of complete system for using UIP.

UIP is the second generation ultrasound imaging tool and is currently being field tested. To increase the number of imageable wells, the outer diameter has been reduced from  $76\,\mathrm{mm}$  to  $54\,\mathrm{mm}$ . The maximum operating temperature is increased from  $105\,^\circ\mathrm{C}$  to  $150\,^\circ\mathrm{C}$ , and it is a goal to increase it further to  $180\,^\circ\mathrm{C}$  in the near future.

A block schematic including all parts needed to capture ultrasound images with the UIP is shown in Figure 1.4.

UIP also offers the ability to take high precision measurements in all three dimensions, including measurement of the wall thickness. The measurements can be used to check if critical components are within acceptable tolerances and can be compared with earlier measurements to predict future durability.

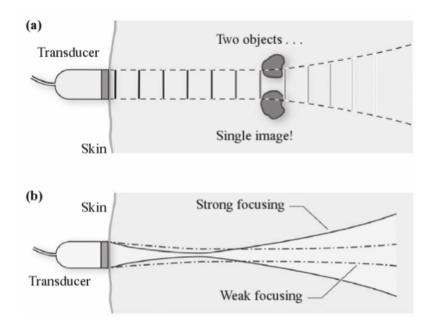

Right now the maximum transmit frequency for full output signal is 2 MHz, which inhibits realizing the full potential of the transducers that have higher upper frequency limits. This results in reduced resolution in both the lateral direction (perpendicular to the ultrasound beam), shown in Figure 1.6 and the axial resolution (parallel to the ultrasound beam) shown in Figure 1.7.

This thesis will document the process of improving the upper frequency to 6 MHz while still satisfying all other requirements. To understand the link between resolution and frequency, a little basic ultrasound theory is presented.

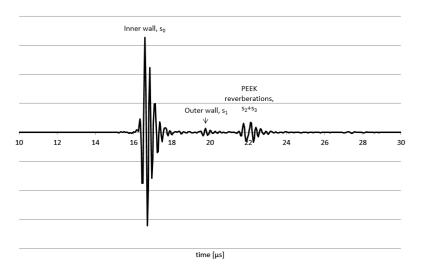

Ultrasound imaging is based on transmitting an ultrasound wave and recording the time it takes to travel from the source to the wall where it is reflected, and back

Figure 1.5: Thickness measurement trace showing importance of pulse duration.

to the source again. By knowing the speed of sound in the medium where the sound wave travels, it is possible to calculate the distance traveled. An example of a received signal is shown in Figure 1.5.

If the pulse duration is too long, the two first echoes will overlap each other making it hard to detect the outer wall, and thus the wall thickness. The pulse duration therefore limits the minimum measurable wall thickness, as shown in Figure 1.6.

Figure 1.6: Axial resolution and pulse length. In the upper figure, echoes do not overlap and can be resolved. In the lower figure, the surfaces are closer than half a wavelength, and can therefore not be resolved [29].

The lens thickness limits the maximum measurable wall thickness by causing the third echo seen in the trace, but this is not discussed in this thesis. The lens is needed to protect the transducers from high pressure, and the echo has a high amplitude because of the large difference in acoustic impedance between the lens and the well fluid.

Shorter pulses result in higher precision in thickness measurements where the axial resolution is important. The axial resolution is the minimum distance between two objects along the ultrasound beam needed to be able to separate them. The formula for calculating axial resolution is shown in (1.1) [20, p. 163].

Axial resolution =

$$\frac{1}{2}p_dc$$

(1.1)

Where  $p_d$  is the pulse duration calculated in (1.2).

$$p_d = \frac{1}{BW} \tag{1.2}$$

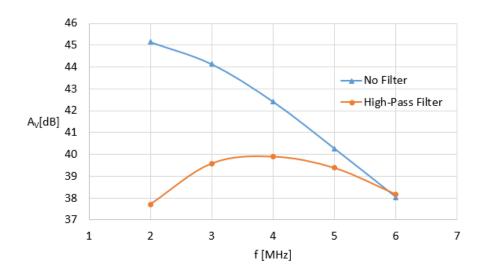

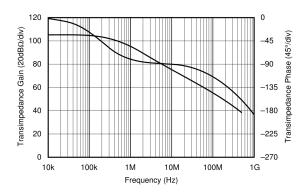

BW in (1.2) is the bandwidth of the signal, limited by the frequency response of the complete UIP, including both transmitter and transducer. The frequency response of the electrical circuit should be so good that the only thing limiting the system bandwidth is the transducer. To achieve this the maximum electrical signal reduction at the upper frequency of the transducer should be less than a tenth of the reduction caused by the transducer. The upper frequency of the transducer is defined as the point where the amplitude is reduced to the half of maximum amplitude, a reduction of 6 dB. The amplitude reduction of the original transmitter is measured to 18 dB at a frequency of 6 MHz.

The lateral resolution is the minimum distance needed between two objects perpendicular to the ultrasound beam to be able to separate them. It is inversely proportional to the signal frequency, as shown in (1.3) [20, p. 164]. D is the diameter of the transducer, while F is the distance from focal point to the face of the transducer. F is called the focal distance. c is the speed of sound in the medium.

Lateral resolution =

$$\frac{\lambda F}{D} = \frac{cF}{fD}$$

(1.3)

### 1.3 About This Work

BTC has identified the transmitter circuit as the main part limiting the frequency response of the UIP. The transmitter has been developed by a subcontractor for BTC. My task has been to improve the frequency response of the transmitter circuit for temperatures up to 180 °C.

Figure 1.7: Lateral resolution. (a) Lateral resolution without focusing is no better than transducer dimensions. (b) Two representations of reducing the cross-sectional area of the beam by focusing [29].

In Chapter 2, the original transmitter design is analyzed, starting with a characterization of the load it has to drive. By characterizing the load, requirements can be set up for the output stage of the transmitter. The chapter continues like this by analyzing one block at a time, possibly improving the block and setting up requirements for the next block. The chapter ends with a new design schematic for the transmitter, including all component changes.

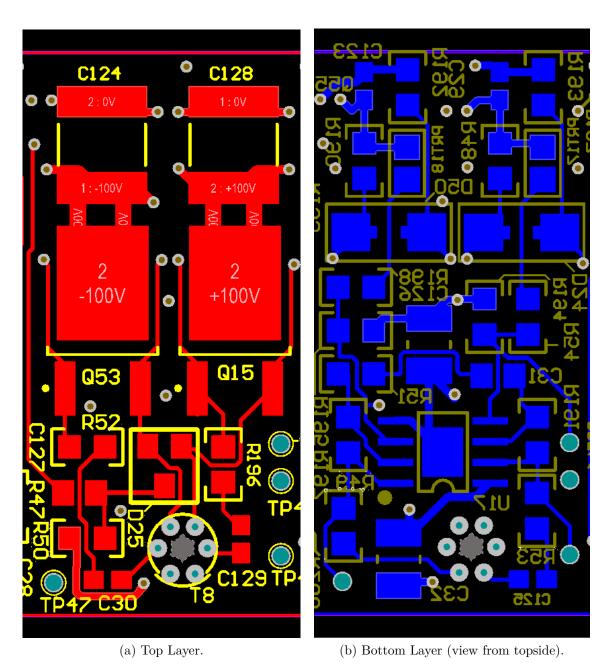

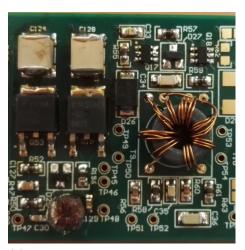

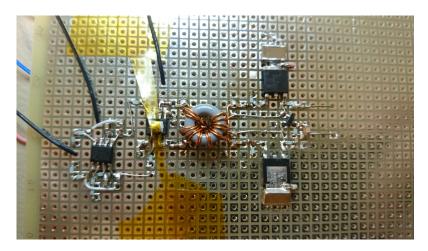

To save time and money, the new design is only implemented for one of the 16 channels on the transmitter board. This process is documented in Chapter 3, where I started with the original printed circuit board (PCB) layout done by the subcontractor. I did a new layout for one of the channels, implementing the new design with the existing power planes and shared circuitry. The total area used per channel is the same as in the original design and the layout can easily be copied for the other 15 channels.

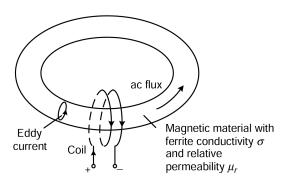

I soldered on components for the new design channel, as well as one channel with the old design and the shared circuitry. The toroidal ferrite cores were obtained as samples from Magnetics and wound by hand.

Chapter 4 starts with mentioning the tests performed by the subcontractor before the thesis. It then proceeds with all the testing done by me in the process of arriving at a complete working design. This includes characterization and verification of component functionality, as well as tests performed on the complete new design.

## Design Analysis

Before designing the original transmitter, some important requirements were defined as listed below. The maximum output amplitude is set equal to the maximum supply voltage from the power supply unit. This is not a requirement that has to be exceeded, but is rather a limit for when other parameters should be prioritized.

• Operational temperature: 0 °C to 180 °C

• Bandwidth: 2 MHz to 6 MHz

• Output Amplitude: ±100 V

• Supply Voltages:  $\pm 5 \,\mathrm{V}$  and  $\pm 100 \,\mathrm{V}$

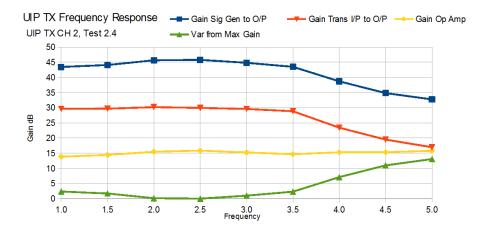

After the design and manufacturing of the original transmitter, the performance was tested and compared to the specifications. Tests documented in section 4.5 shows that the upper frequency for a maximum output signal is only 2 MHz for the original transmitter. This is the main motivation for improving the design.

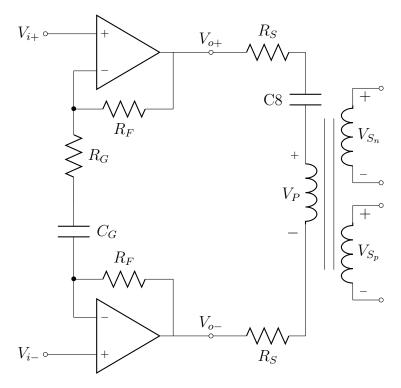

The original design is split into smaller parts and analyzed according to the specifications. The design parts and external connections are analyzed starting at the load and ending at the input signal. After analyzing each part, improvements are considered and implemented. All implemented improvements are taken into consideration when analyzing the next part.

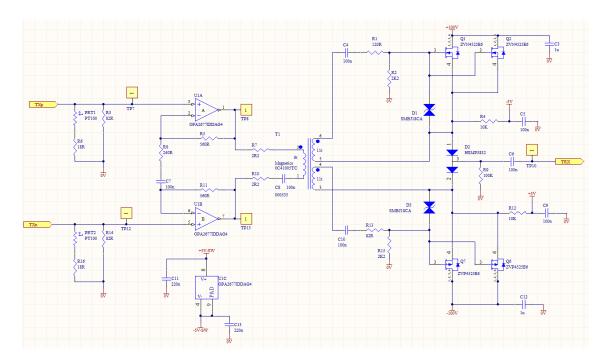

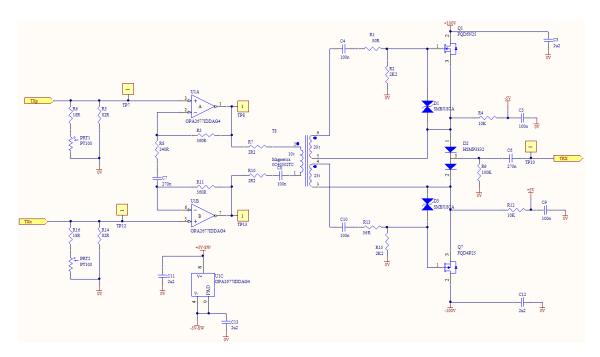

A complete schematic of the original transmitter is shown in Figure 2.1.

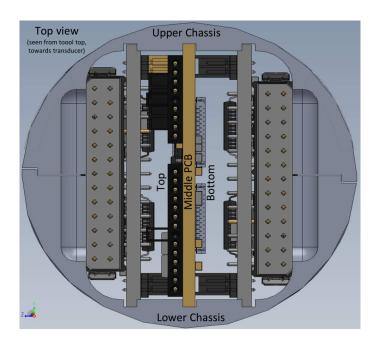

The complete tool is made to fit oil wells with an inner diameter down to 54 mm. The transmitter board is stacked together with two other boards as shown in Figure 2.2. On the bottom side of the board, the maximum component height is limited by

Figure 2.1: Schematic of the original transmitter.

the distance to components on the middle board. Maximum component height on the middle board in the position of the channels is 1.6 mm. The distance between the boards is 6 mm, resulting in a maximum available component height of 4.4 mm, minus a margin for uncertainties.

Each transmit channel currently occupies an area of  $5.8\,\mathrm{cm^2}$  on the PCB. There is almost no free space in each channel. In case some components need more space after replacement, others need to be downsized.

### 2.1 Transmitter Load

Each transmitter will be connected to two transducer elements at a time through a switch board. BTC currently use 4 different ultrasound transducers which differ in center frequency, bandwidth and number of elements. The complex impedance of these has been measured as a function of frequency by the manufacturer, as shown in Table 2.1. Dummy transducers for testing are made of a resistor and a capacitor in series, which model the transducers at the center frequency.

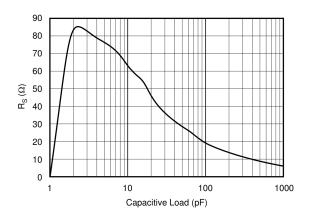

Each of the 16 channel outputs can be connected to a total of 288 output connection points. This allows for connecting a maximum amount of 288 transducer elements. To achieve this a total of 800 switches are used. Each transmitter is connected to 32 switches which are connected to 32 common connection points for all transmitters, called X/0..31/.

Figure 2.2: Inner mechanics of the UIP tool [3].

The 32 common connection points are each connected to 9 switches connected to separate transducers. In this way each of the connection points can be connected to 9 different transducers. Multiplying this with the number of connection points, 32, each transmitter can be connected to 288 different transducers.

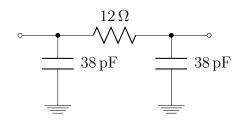

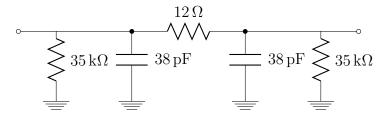

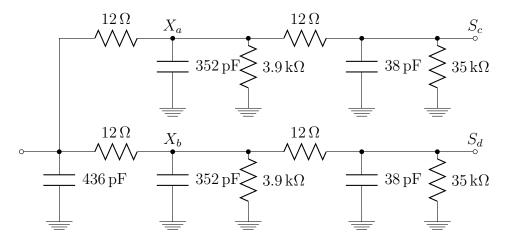

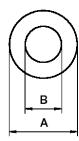

An open switch is modeled as a capacitor to ground. The capacitance for each open switch is typically 12 pF at 1 MHz [21]. A model for a single closed switch is shown in Figure 2.3.

The second stage of switches also includes bleed resistors to discharge the capacitance in between two switches when both switches are open. These bleed resistors exist on each side of the switch in both open and closed state. A model of the switch with bleed resistors in closed state is shown in Figure 2.4.

By using these two models it is possible to create a model for the impedance at each transmitter output when connected to two transducers, shown in Figure 2.5. The first node consists of 30 open switches and two closed switches in parallel, as the

Table 2.1: Transducer data measured by manufacturer Imasonic.

| Transducer | $f_c$ [MHz] | Zr   | Zi     | $R [\Omega]$ | C [pF] |

|------------|-------------|------|--------|--------------|--------|

| 6071A101   | 3.10        | 60.7 | -291.4 | 60.7         | 176    |

| 9887B101   | 4.00        | 27.6 | -150   | 27.6         | 265    |

| R5813B101  | 3.60        | 109  | -420.6 | 109          | 105    |

| 4475A101   | 4.76        | 26.0 | -152.3 | 26.0         | 220    |

Figure 2.3: Model for closed switch.

Figure 2.4: Model for closed switch with bleed resistors.

transmitter is connected to two of 32 connection points.

The nodes  $X_a$  and  $X_b$  show the impedance at each connection point. Each connection point can be connected to 16 transmitters and nine transducers, a total of 25 switches. When connecting one transmitter to two transducers, this equals 23 open switches and 2 closed switches in parallel. The nine switches on the transducer side also include bleed resistors. The nodes  $S_c$  and  $S_d$  represent connection points for transducers.

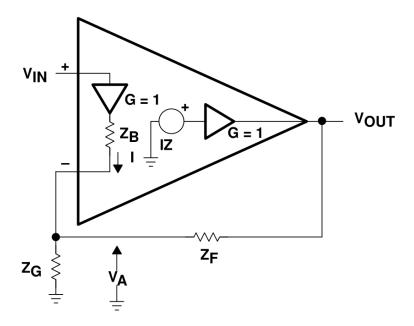

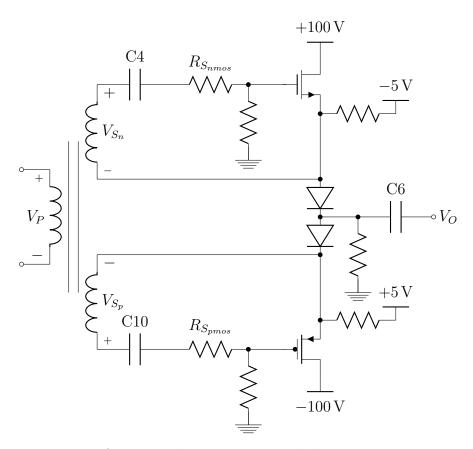

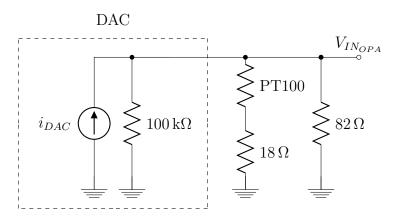

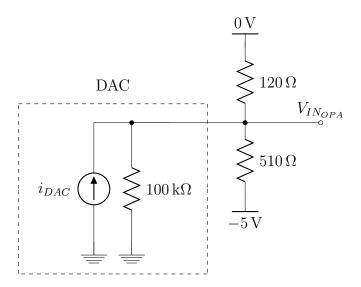

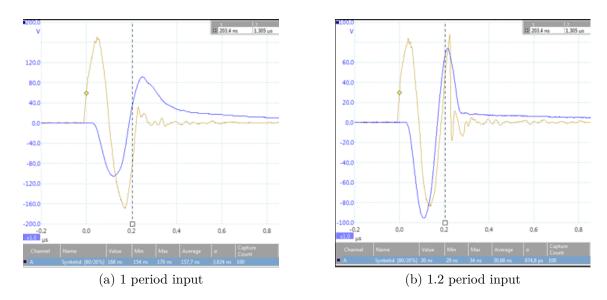

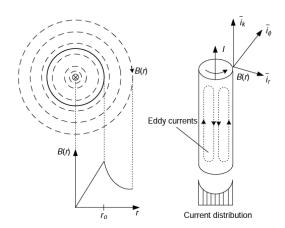

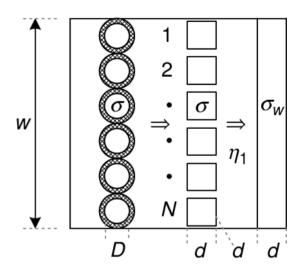

In addition to the impedance of the switches, the PCB tracks will introduce series resistance and inductance, as well as capacitance and resistance to ground.