# Design of High-Speed Digital Readout System for Use in Proton Computed Tomography

A thesis by

Ola Slettevoll Grøttvik

for the degree of

Master of Science in Physics

Department of Physics and Technology

University of Bergen

June 2017

#### Abstract

A team at the University of Bergen is developing a proton computed tomography (CT) scanner prototype. The proton CT (pCT) scanner will introduce fewer insecurities than conventional photon CT when analyzing the location of the tumor and the particle stopping power in the tissue in front of the tumor. The pCT will consist of multiple CERN-developed particle detector chips.

This work covers the design and development of a readout system for the pCT scanner. The requirements for the different parts of the system are formulated. Particular emphasis is put on the clock data recovery method employed for handling the 1.2 Gb/s data transmitted from the detector chips. Because of the high number of detector chips in each scanner layer, transceivers cannot be employed for this purpose. This constraint results in a custom design employing the I/O primitives to achieve phase and word alignment automatically.

A complete verification system is realized around a simulatable model of the particle detector chip. This system is used for verification of multiple readout procedures, as well as validation of detector chip communication and firmware functionality. The simulations are further verified in a physical hardware setup. The results of the I/O primitive approach are positive, but some errors are produced when employing longer cables.

## Preface

This work was carried out at the Department of Physics and Technology at the University of Bergen between August 2016 and June 2017. The pCT project was just initiated, and little documentation or information existed. Unraveling the design requirements and solving the challenges that turned up was done without much prior knowledge of a large system design.

## Acknowledgments

This work was largely influenced by my two great supervisors, *Professor Kjetil Ullaland* and *Associate Professor Johan Alme*. Thank you very much for all your help, guidance and patience. Working with something as important as cancer therapy, although indirectly, has been deeply rewarding. Thanks to *Professor Dieter Röhrich* for heading the pCT group and letting me be a part of it.

A huge thanks to Attiq Ur Rehman, Simon Voigt Nesbø and Shiming Yang which provided invaluable insight at several stages of the process. I would also like to express my gratitude to my fellow students at room 503. It has been two gratifying years and I hope I will encounter you all in the future.

Finally, I would like to thank my friends and family. A special thanks to Ingrid for comments and suggestions. Finally, I would like to especially thank Ida and my parents. Thank you for enduring everything and always being there.

Ola Slettevoll Grøttvik Bergen, June 2017

## Contents

| Pı           | refac         | e                                         | V    |

|--------------|---------------|-------------------------------------------|------|

| $\mathbf{A}$ | crony         | yms                                       | xi   |

| $\mathbf{G}$ | lossa         | ry                                        | xiii |

| 1            | Intr          | roduction                                 | 1    |

|              | 1.1           | Background and Motivation                 | 1    |

|              | 1.2           | About this Thesis                         | 1    |

|              | 1.3           | Thesis Outline                            | 3    |

|              | 1.4           | Citation Principles                       | 4    |

| <b>2</b>     | Rac           | diation Therapy and Proton CT             | 5    |

|              | 2.1           | Radiation                                 | 5    |

|              | 2.2           | Charged Particles Interaction with Matter | 5    |

|              | 2.3           | Photons Interaction with Matter           | 7    |

|              | 2.4           | Range and Biological Effects              | 9    |

|              | 2.5           | Cancer and Radiation Therapy              | 10   |

|              | 2.6           | Proton CT (pCT)                           | 12   |

| 3            | $\mathbf{AL}$ | ICE ITS and the ALPIDE Chip               | 15   |

|              | 3.1           | ALICE ITS                                 | 15   |

|              | 3.2           | ALPIDE Chip                               | 17   |

|              | 3.3           | ALPIDE Control Interface                  | 17   |

viii CONTENTS

|   | 3.4  | ALPIDE Data Interface                            | 19 |

|---|------|--------------------------------------------------|----|

|   | 3.5  | ALPIDE Operation                                 | 20 |

|   | 3.6  | ITS Readout Unit                                 | 24 |

| 4 | рСТ  | Γ Readout System                                 | 27 |

|   | 4.1  | pCT Requirements                                 | 27 |

|   | 4.2  | pCT Readout Unit (PRUdense)                      | 30 |

|   | 4.3  | Electronics                                      | 32 |

|   | 4.4  | Readout Process                                  | 36 |

|   | 4.5  | Clock and Data Recovery                          | 37 |

|   | 4.6  | Automatic Phase and Word Alignment Design        | 39 |

|   | 4.7  | Filtering, Tagging, and Buffering Design         | 47 |

|   | 4.8  | Offloading                                       | 52 |

|   | 4.9  | Communication and Control                        | 52 |

|   | 4.10 | Timing Requirements and TRIGGER Generation       | 58 |

|   | 4.11 | Power Control and Monitoring                     | 60 |

| 5 | Dev  | relopment and Testing                            | 63 |

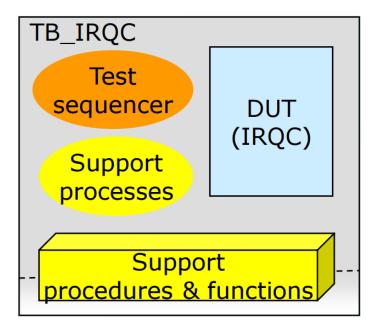

|   | 5.1  | ALWM Testbench Environment                       | 63 |

|   | 5.2  | Readout Unit Testbench Environment               | 66 |

|   | 5.3  | Test of Readout: Transceiver with Fabric Modules | 69 |

|   | 5.4  | Test of Readout: Transceiver Only                | 73 |

|   | 5.5  | Bus Replacement                                  | 74 |

|   | 5.6  | Test of Readout: CDR with I/O Delay Features     | 76 |

|   | 5.7  | Test of Readout: Automatic Phase Alignment       | 80 |

|   | 5.8  | Data Filtering Design Simulation                 | 85 |

| 6 | Disc | cussion and Conclusion                           | 87 |

|   | 6.1  | Readout Evaluation                               | 87 |

|   | 6.2  | Design Evaluation                                | 88 |

|   | 6.3  | Future Work                                      | 89 |

|   | 6.4  | Conclusion                                       | 91 |

| CONTENTS | ix |

|----------|----|

|          |    |

| A A             | ALPIDE BFM                         | 93    |  |

|-----------------|------------------------------------|-------|--|

| ВЕ              | irmware                            | 97    |  |

| C I             | Oata Readout Registers             | 105   |  |

| DΊ              | Cestbench Procedures and Functions | 107   |  |

| ЕТ              | Cest Software                      | 109   |  |

| F F             | Repository Structure 113           |       |  |

| $\mathbf{G}$ S  | Signal Integrity 115               |       |  |

| нм              | Methodology                        | 119   |  |

| H               | I.1 Information Gathering          | . 119 |  |

| H               | I.2 Design Strategies              | . 120 |  |

| H               | I.3 Simulation and Verification    | . 121 |  |

| H               | I.4 Hardware Testbench             | . 123 |  |

| $\mathbf{Bibl}$ | iography                           | 125   |  |

## Acronyms

**ADC** Analog-to-Digital Converter **HDL** Hardware Description Language **ALICE** A Large Ion Collider Experiment **HP** High Performance **ALPIDE** ALICE Pixel Detector HR High Range **ALWM** ALPIDE Lightweight Model IC Integrated Circuit AMBA Advanced Microcontroller Bus ILA Integrated Logic Analyzer Architecture **IP** Intellectual Property **ASIC** Application Specific Integrated Cir-ITS Inner Tracking System **AXI** Advanced eXtensible Interface JTAG Joint Test Action Group **LET** Linear Energy Transfer **BER** Bit Error Rate LHC Large Hadron Collider **BFM** Bus Functional Model LSB Least Significant Bit **CDR** Clock Data Recovery LVDS Low-Voltage Differential Signaling **CERN** Conseil Europen pour la Recher-MAC Media Access Control chè Nuclaire **MEB** Multi-Event Buffer **CMOS** Complementary Metal-Oxide MGT Multi-Gigabit Transceiver Semiconductor MMCM Mixed-Mode Clock Manager Glossary: CMOS Process MSB Most Significant Bit CPU Central Processing Unit CT Computed Tomography **PCB** Printed Circuit Board pCT Proton CT **DDR** Double Data Rate PHY Physical Layer **DMA** Direct Memory Access **PLL** Phase Locked Loop **DTC** Digital Tracking Calorimeter **pRG** Proton Radiography **DUT** Device Under Test PRUdense pCT Readout Unit **FIFO** First In First Out **RAM** Random Access Memory FPGA Field Programmable Gate Array RISC Reduced Instruction Set Comput-FROMU Framing and Management Unit ing **GBT** GigaBit Transceiver **RO** Read Only Glossary: GBT **ROM** Read Only Memory

xii Acronyms

RTL Register Transfer Level RW Read/Write

SCU System Control Unit

SEL Single Event Latch-up

SERDES Serializer/Deserializer

SEU Single Event Upset

SOBP Spread-Out Bragg Peak

Glossary: Bragg peak

SoC System-On-Chip

SRAM Static Random Access Memory

UART Universal Asynchronous Receiver

Transceiver

USB Universal Serial Bus

UVVM Universal VHDL Verification Methodology

**VHDL** Very High Speed Integrated Circuit Hardware Description Language *Glossary:* VHDL

**WO** Write Only

## Glossary

#### 8B/10B

An encoding algorithm that encodes a 8-bit word into a 10-bit word to achieve DC-balance.

#### Bragg peak

The region of high dose at the end of a charged particle's range.

#### **CMOS Process**

A specialized manufacturing process technology that are implemented to create transistors on silicon wafers to make ICs. The technology is often described by the length of a single transistor channel.

#### Combinational Design

A system in which outputs are a function of only its present input values.

#### **Fault**

Failure of a subsystem. May and may not produce an observable error.

#### **GBT**

Bidirectional optical link aimed at being radiation hard. Developed at CERN for use in Large Hadron Collider (LHC) upgrades.

#### Half-Duplex

In communications, a half-duplex system can communicate in both directions, but not simultaneously.

#### IP Core

An Intellectual Property core is collection of logic or code, that is specific to do a certain task in an IC often represented as a behavioral module. IP cores are an integral part of design reuse in electronic design automation industry.

#### Monolithic Active Pixel Sensor

Image sensor where all pixel detectors are implemented with individual amplifiers on IC with readout electronics included.

#### Rise Time

The amount of time required for a signal to transition from 10 percent to 90 percent of its final steady value.

xiv Glossary

#### Synthesis

The process of generating a representation of function in a lower level based on a more abstract level. Usually refers to when an FPGA design is transformed from a RTL level to logic gate level.

#### **Twinax**

Type of cable similar to a coaxial cable, but with two conductors instead of one. Becoming common in short-range high-speed applications.

#### VHDL

A language for describing digital electronic systems, and widely used for developing FPGA firmware.

#### Vivado Design Suite

Software suite for synthesis and analysis of HDL designs targetting Xilinx FPGAs.

#### Wrapper

A module which converts the signals of an interface to another interface. E.g., used to convert signals from a Wishbone compatible slave to an AXI compatible master.

## Introduction

## 1.1 Background and Motivation

The most common form of radiation therapy of cancer in Scandinavia has, until recently, been utilizing high energetic photons. Lately, greater focus has been given to radiation therapy with charged particles. This method benefits the patient due to the reduced irradiated volume of the patient during treatment and by maximizing the ratio between dose to tumor and dose to healthy tissue [1]. This reduces side effects like radiation-induced secondary cancers. In Norway, focus on proton treatment was given when the government in 2013 funded a new report targeting the possibilities for new radiation therapy centers [2].

137 000 patients were by January 2015 already treated with charged particles around the world, in which 86% were treated with protons [3]. However, the current technique for calculating how the particles will be absorbed by the body is using X-ray photons [4]. This method introduces uncertainties that can be reduced by employing proton computed tomography [5]. The University of Bergen has been granted project funding to develop a prototype proton CT scanner.

## 1.2 About this Thesis

The primary goal of this thesis is to start the design and development process of a readout system to be used in the proposed proton CT scanner. The project plans to use several of the CERN-developed particle detector chip called ALPIDE. These will be organized in several layers of multiple sensor chips, where all chips will be connected to FPGAs. The readout system must, therefore, work in a highly pipelined fashion in which each data channel operates independently of each other. Furthermore,

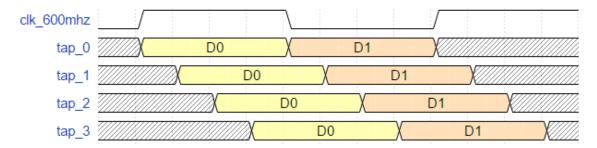

since the data speed of every detector chip is 1.2 GB/s, the data must be processed in a very efficient way to prevent bottlenecks during readout.

The readout system must also handle the control of all the chips. Each detector chip includes a control channel which serves two purposes [6]:

- 1. provide read and write access to internal chip registers, commands, configuration, and memories

- 2. distribution of trigger and other broadcast commands

The readout system must be able to perform all the necessary configurations of the chips, and also broadcast trigger commands synchronously to all detectors.

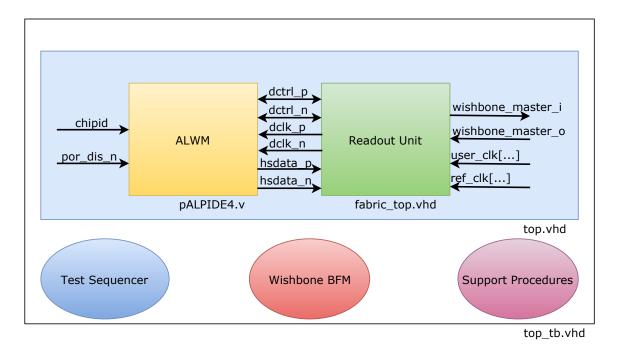

This work builds on the effort done by the ITS upgrade team at CERN, who are using the same sensor chip. Some time was spent on setting up a simulation testbench environment in which a simulatable model of the ALPIDE chip was incorporated. This testbench environment enabled modification of the firmware to represent the Proton CT (pCT) requirements. Later a physical test environment was set up using an ITS-developed PCB and a single ALPIDE chip.

A quite substantial amount of effort was put into the design of the pCT readout system concept and especially formulating requirements for the different parts of the system. This required both insights in the different ways ALPIDE chips operate, as well as how the triggering and timing should work to produce consistent data.

Different readout procedures were developed and tested in both the simulation environment and physically in hardware. In particular, a major challenge was to develop a reliable sampling method that employed regular I/O pins without the help of transceiver features.

A significant effort was put into the communication system and particularly defining a register handling format for the bus interface. This also included writing software to automatically produce the required register handling firmware, although this task is not entirely completed at the end of this work.

Software development was required to test the hardware designs thoroughly. This work involved using the Python programming language.

The majority of this work was done while interfacing a test board which was poorly documented. This brought an extra challenge to the process.

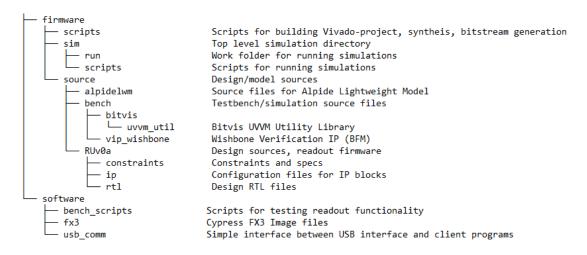

A strong emphasis was put on documentation and version control to ease future development. All code and documentation are collected in a git repository, and all changes done are thoroughly logged with commit messages. Notable milestones are saved with tags. All VHDL code written complies to the department's guidelines. All simulation, synthesis, and testing are accomplished by employing scripts and automated software.

#### 1.3 Thesis Outline

This thesis is divided into the following chapters:

Chapter 2: Radiation and Cancer Therapy This chapter starts with theory regarding radiation and cancer therapy. This theory is required to understand some of the benefits of proton cancer treatment and a proton CT scanner, which is explained in the second part of the chapter.

Chapter 3: ITS and the ALPIDE Chip This chapter describes the ALICE detector and the ITS upgrade, and is included due to the considerable similarities between this system and the proton CT scanner. An overview of the ALPIDE chip's operation modes and interfaces is given to help the reader understand some of the design choices made in later chapters. Ultimately, some of the ITS readout unit's modules are introduced and explained. These modules constitute the basis of the work done with the pCT readout unit.

Chapter 4: Readout System This chapter contains a comprehensive discussion of the complete pCT readout system. The system as a whole is introduced, followed by a more detailed discussion about the different units. Particular emphasis is put on the various stages of the readout process where data on the high-speed data interface on the ALPIDE is sampled by the readout unit. After that, the communication and control parts of the system are described before a discussion about the timing requirements and the trigger generation. Finally, the power control system is briefly outlined.

Chapter 5: Development and Testing This chapter reviews the development of the readout unit and the simulation and testing procedures.

Chapter 6: Discussion and Conclusion This chapter summarizes the work for this thesis, and then discusses the further tasks required to complete the system. Finally, there is a brief section that concludes the thesis and the results of the work.

Appendices The last section of the thesis includes multiple appendix chapters with too many details to be included in the main thesis. It includes both description of registers in the system, the procedures and functions of the ALPIDE BFM, as well as firmware and testbench overviews. The section also includes a summary of the test software, and an overview of the code repository. The two last appendices are

about the problems that may arise with high-speed digital signals and the methods needed when designing complex hardware. Specifically, the last chapter outlines Weste and Harris' [7] design strategies. Subsequently, a summary of techniques for detecting errors in a simulation environment is presented before some hardware testing principles are described.

## 1.4 Citation Principles

This thesis is using the principle that citations listed after the ending punctuation of a paragraph may refer to several statements in the section. Citations listed before any punctuation will always refer to the last statements.

## Radiation Therapy and Proton CT

This chapter outlines some of the differences between the behavior of electromagnetic radiation and charged particles. Further, it explains how these differences affect the patient when employing radiation for cancer therapy. Finally, the benefits of proton CT is presented.

### 2.1 Radiation

By definition, radiation is the emission and propagation of energy through space or a material medium. Radiation is characterized in various ways; including ionizing and non-ionizing radiation or charged particles and electromagnetic waves. [8, Chapter 1][9, Chapter 1]

Radiation is also characterized by the energy of the beam particle. If the energy is high enough to completely remove an electron from an atom by transferring energy to the medium, it is known as ionizing radiation. Some radiation is known as directly ionizing radiation because of how the particles directly can interfere with atoms. These include  $\alpha$  and  $\beta$  particles, as well as ions like protons and  $^{12}C$ . Uncharged particles like neutrons and photons are indirectly ionizing radiation, however, and they achieve ionization by creating by-products that can interact with atoms. [9, Chapter 5]

## 2.2 Charged Particles Interaction with Matter

Particles will be losing velocity and energy while traveling through matter. The energy, charge, and mass of the particles, and the type of matter it is moving in

$<sup>^{1}\</sup>alpha$ -particles are  $^{4}_{2}He$ -nuclei, and  $\beta$ -particles are charged particles indistinguishable from an ordinary electron, but may have positive charge [10].

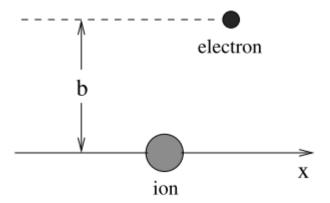

Figure 2.1: A charged particle is moving in the electron's electric field [8].

determine the type of processes that will be involved and the scale of the effects. For charged particles, several mechanisms will contribute to energy loss. Nonetheless, inelastic scattering with orbital electrons in the matter will often be the dominating mechanism due to the high electron density in matter.<sup>2</sup> This interaction can be modeled as in Figure 2.1. As the ion passes the orbital electron, the transfer of energy is caused by the Coulomb force between the charges. The amount of energy the ion loses depends on the distance between the particles, the amount of charge and the amount of time the ion uses in passing the electron. The latter means that the ion will lose more energy if it moves more slowly. The less kinetic energy, the more energy will be lost. [11, Chapter 4][10, Chapter 5]

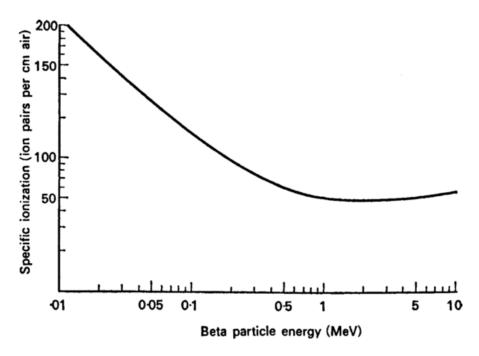

An important parameter is specific ionization, which expresses the linear rate of energy loss due to ionization and excitation. For a charged particle, specific ionization is the number of ion pairs formed per unit distance traveled. Figure 2.2 shows the relationship between the specific ionization and the Bethe-Bloch formula energy for a  $\beta$ -particle. Relativistic effects cause the somewhat increasing specific ionization at higher energy. Specific ionization is used when one is interested in the radiated particles' energy loss. If one is more focused on the absorber material, like in radiation therapy and radiation protection, it is common to use the term *Linear Energy Transfer (LET)*. This term quantifies the linear rate of energy absorbed by the medium and is defined by

$$LET \leq \frac{dE_L}{dl}$$

where  $dE_L$  is the average energy transferred to the medium traveling a distance dl. The need for two separate definitions implies that the energy locally absorbed by the medium is not equal to the energy lost by the moving particle. In fact, some of

<sup>&</sup>lt;sup>2</sup>A 10 MeV proton will lose most of its energy after moving only 0.25 mm in copper.

Figure 2.2: Relationship between particle energy and specific ionization in air [10, Figure 5-7].

the energy lost is carried away by energetic secondary electrons. [10, Chapter 5][11, Chapter 4][9, Chapter 14]

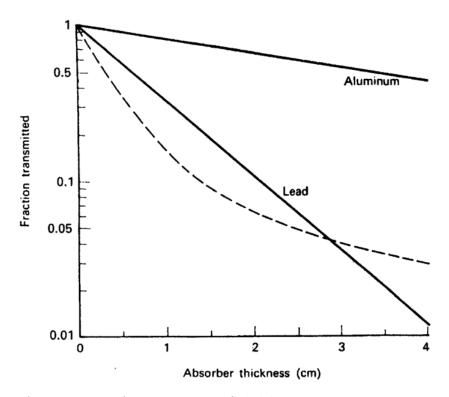

## 2.3 Photons Interaction with Matter

In 1925 de Broglie introduced the idea of the duality of nature and that electromagnetic waves could behave like particles [9, Chapter 1]. Electromagnetic radiation,<sup>3</sup> a beam of photon particles, will gradually lose intensity as it moves through matter. While  $\alpha$  and  $\beta$  particles may be completely absorbed, electromagnetic radiation can only be reduced in intensity. This attenuation is partly due to scattering of the photons, and partly due to absorption of the photons. Figure 2.3 shows how the intensity is exponentially attenuated by increasing the absorber thickness. Note the logarithmic nature of the graph, which entails that the intensity will never be reduced to zero. [11, Chapter 5][10, Chapter 5]

The main contributors to the attenuation of electromagnetic radiation are three processes; photoelectric effect, Compton scattering, and pair production. Photoelectric absorption occurs when a photon hits an orbital electron with a binding

<sup>&</sup>lt;sup>3</sup>High energy electromagnetic radiation may, depending on the energy level, also be called gamma  $(\gamma)$  or X-ray radiation.

Figure 2.3: Attenuation of gamma rays. Solid lines represent attenuation for monoenergetic gamma rays, and the dotted line represents a heterochromatic beam [10, Figure 5-13].

energy equal to or less than the photon energy. The photon disappears, and the resulting particle, the photoelectron, transfers its energy<sup>4</sup> by excitation and ionization. Compton scattering occurs when there is an elastic collision between a photon and an electron in the outer shell of the atom. These electrons can be considered "free" in the sense that the binding energy can be radically smaller than the energy of the photon. This collision causes the photon to change course, and lose some energy. Further, the hit electron has obtained the energy difference between the original and the scattered photon, moving out of the atom in an angle that represents the change in wavelength. [10, Chapter 5][11, Chapter 5]

Photoelectric effect and Compton scattering are dominant at energies below 1.02 MeV, consequently the energy equal to the rest mass of two electrons. While at higher energies, a photon can convert into an electron/positron pair, a so-called pair production. This conversion of electromagnet energy into mass can only take place when a photon is passing close to a particle, such as a nucleus, so that momentum is conserved. [10, Chapter 5]

$<sup>^4</sup>E_{pe}=hf-\phi$  where hf is the energy of the photon and  $\phi$  is the binding energy of the orbital electron.

The attenuation also varies widely with the type of absorber material. The difference between lead and aluminum is shown in Figure 2.3. The difference is due to the atomic number. The Compton effect, however, is almost entirely independent of the atomic number of the absorber. This is because the Compton effect deals with electrons in the outer shell, so-called "free" electrons, which are independent of atomic number. [10, Chapter 5]

## 2.4 Range and Biological Effects

For a beam of particles, the range is defined as the distance or thickness of absorber material needed for there to be no more observed particles than the background radiation [10, Chapter 4]. The fundamental difference in how charged particles and photons interact with matter is the reason why the distance traveled in matter is different. The distance any charged particle can move in matter is decided by a number of discrete collisions with a statistical distribution [11, Chapter 4]. The relation between energy and deposited energy shows that a charged particle will lose more and more energy before it eventually stops. Whereas a beam of photons has no explicit range because only the intensity of the beam is reduced. This can be observed in Figure 2.3, where the intensity of the beam never equals zero.

As we have seen, the energy absorbed by radiation may cause ionization and excitation of atoms in the absorbing material. This ionization may break up molecular bonds in the absorbing material. It follows that this may be extremely hazardous for biological tissue; as molecules break, living cells and genetic material may be severely damaged. The cells and even whole organisms may die [12, Chapter 32]. There are both direct and indirect effects of radiation that may cause harm to the cells. One direct effect is point mutations, a change in a single gene [10, Chapter 7]. The ionization or excitation may cause a molecular lesion that inflicts damage to normal function. Such damages are often repaired, but sometimes they prevail and are transferred to new generations of DNA cells. An example of indirect radiation effects is the creation of toxic and hazardous chemicals by nuclear reactions. Since most of the human body is water, one possible reaction is the creation of hydrogen peroxide which is a powerful oxidizing agent [10, Chapter 7]. The consequences of over-exposure may be acute and deterministic, or delayed and stochastic, like genetic effects and cancer.

Measuring the damage done to living tissue is extremely complicated. Consequently, significant attempts have been made to control the exposure to living organisms, and radiation dosimetry is the effort to quantify the effect of radiation on living tissue. The absorbed dose is the energy deposited per unit mass.

$$D = \frac{\Delta E}{\Delta m}$$

where the unit is called Gray(Gy). 1Gy = 1J/1kg. The absorbed dose may be used to measure all types of radiation, independent of the fundamental processes in which the energy is transferred. Even though the absorbed dose is not considered a sufficient measure of the biological effects of radiation, it is adequate to understand the benefits of cancer treatment with protons versus photons. [13, Chapter 43][10, Chapter 6]

## 2.5 Cancer and Radiation Therapy

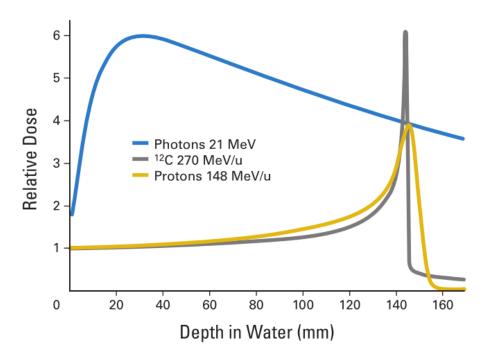

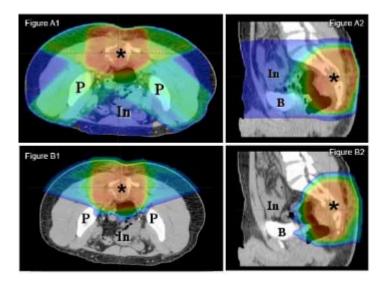

The effects of ionizing radiation on biological tissue may be employed for health purposes, and are used on a large scale both for diagnostics and therapy. Until recently, the conventional form of radiation therapy utilized photons. Although protons and heavier ions were introduced as possible candidates for cancer treatment as early as in 1946 [14], the high complexity and cost of technical realization may have slowed the development compared to conventional radiation [15]. Therefore, proton therapy has been in clinical use only since the 1970's [16]. As discussed, a charged particle, like protons and carbons, will lose more energy as they go further into the matter before eventually reaching the Bragg peak. The Bragg peak is the region where the charged particle will lose the majority of its remaining energy, and a close-to-zero dose will be absorbed by the material beyond this peak [14]. This behavior differs fundamentally from photons, which after a short build-up region, will decreasingly deposit energy as they move in the matter [17]. Thus, as shown in Figure 2.4, radiation therapy which utilizes protons or heavy ions may be more precise in delivering the dose to the tumor.

The particle beam may be tuned so that the Bragg peak is placed at any depth into the patient's tissue [5], and therefore able to hit tumors at any depth. The main benefit in using protons and heavier ions for cancer therapy is a reduction of the total dose absorbed by the patient. As can be observed in Figure 2.5, the dose distribution of a photon beam covers a much larger region than the proton beam. This reduction in absorbed dose entails that secondary radiation effects also may be reduced [2]. Long-term perspective is of particular importance when treating cancer in children. The reduced risk for radiation-induced cancer and other hazards, brought about by dose reduction, makes proton treatment very promising for child treatment. Concurrently, while minimizing the irradiated area, proton treatment allow for an increase in dose delivered to the tumor, and thus increasing the potential for controlling the tumor [17]. To summarize, proton therapy will theoretically both reduce side effects of the treatment, and also increase the chances of controlling the tumor. More research is needed, but clinical evidence indicates that tumors close to critical structures are benefiting the most from proton treatment [16].

Figure 2.4: Relative dose distribution profiles of photons, protons and carbon ions [14, Fig 1]

Figure 2.5: X-ray dose distribution (A1&A2) and proton dose distributions (B1&B2) [18].

As the Bragg peak is seldom wide enough, a set of beams with different energies are often needed in order to tune the proton beam to place the Bragg peak in the tumor, and cover the entire tumor [19]. The multiple beams are weighted with different energies to create the so-called Spread-Out Bragg Peak (SOBP), which covers the entire treatment volume. To achieve this, precise information regarding the tumor location and the particle stopping power in tissue preceding the tumor is needed. This information, however, is currently obtained mainly through X-ray photon CT [4]. The conversion between the behavior of photons in the CT and the protons in the therapeutic beam is associated with uncertainties up to several millimeters [5].

## 2.6 Proton CT (pCT)

The use of protons in CT is an imaging technique which will provide a low dose to the patient, and present range predictions which decrease the uncertainties introduced by X-ray photon CT [5]. While proton therapy requires protons to deposit their energy and stop in the tumor, proton CT requires particles to pass through the patient [20]. This is due to the particle's energy loss in the medium being the primary mechanism for image contrast and must be measured on the other side of the patient. Therefore, a proton CT scanner requires a high-energy proton beam. Figure 2.6 shows an example 3D rendering of pCT-reconstructed relative stopping power map.

Figure 2.6: Example of 3D rendering of pCT-reconstructed relative stopping power map [5, Fig. 14].

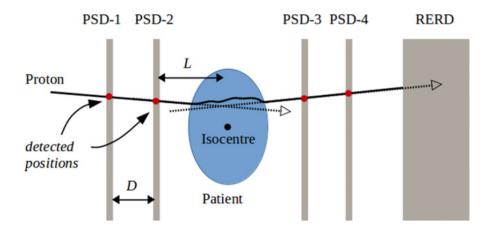

Some proposed Proton Radiography (pRG) and pCT systems use a proton integrating

approach, that calibrates a signal in a detector with the length traversed, averaged over many protons. This approach has some limitations; the proton integrating systems developed have produced degradation in spatial resolution and the presence of severe edge artifacts [20]. Proton-tracking is an alternative approach to obtain the required data. This technique measures each individual proton's residual energy after emerging from the patient. Figure 2.7 shows how a proton-tracking pCT system may be set up. It consists of multiple position-sensitive detectors and a detector measuring the residual energy-range. Multiple pCT prototypes follows this approach, including the project at the Loma Linda University [21] and the Italian project called PRIMA. Furthermore, these projects employ calorimeters or scintillators that require only one proton per element during a readout for valid measurements. [20]

Figure 2.7: A proton-tracking proton radiography/proton CT system [20, Figure 5]. Consists of four position-sensitive detectors (PSD) and a residual energy-range detector (RERD).

### 2.6.1 Bergen pCT Prototype

The aim of the pCT prototype which is being developed at the Department of Physics and Technology at the University of Bergen is rapid and precise reconstruction of tracks of the protons traversed through the patient. The measurements are done with a high-granularity semiconductor calorimeter, also called the Digital Tracking Calorimeter (DTC). A high granularity detector is realized by structuring a large number of detector chips which consist of 1024x512 pixels each. Each sensor pixel can detect deposition of energy above a given threshold. The DTC is constructed by creating multiple layers of multiple detector chips. The DTC will use the CERN-developed particle detector chip ALPIDE. This chip is described in Chapter 3.

The setup differs from other proton tracking approaches in that both position and energy deposition is obtained by a single detector instrument, the DTC. The proton

tracks measured will be used to calculate the deposited energy of the individual proton. The duality of this technique, calculating both the angle and position as well as the deposited energy of the protons, simplifies and reduces the cost of the pCT [4].

Furthermore, due to the pixelated nature of the CMOS detector, the DTC allows for measuring multiple protons per frame time. The high granularity of the sensors makes it possible to track several individual protons at the same time. This increases the proton rate capability of the detector and reduces the time required to produce a high-resolution image.

The structure of the pCT is not yet completely settled, and it follows that the task of designing a readout system must be highly adaptive and modular. A visualization of the structure and setup is presented in Section 4.1.

## ALICE ITS and the ALPIDE Chip

This chapter offers a brief presentation of the ALICE ITS detector upgrade, and explains the ALPIDE chip's operation modes and interfaces. It also presents a concise discussion of the ITS readout firmware modules. This design forms the basis of the pCT firmware development.

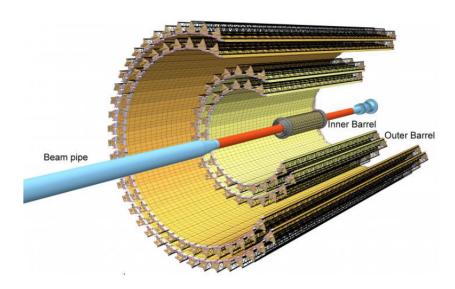

#### 3.1 ALICE ITS

The ALICE experiment at CERN is one of four large detector experiments that are registering collision event data at the LHC. ALICE is focused on heavy-ion collisions and the strong interaction sector of the Standard Model [22]. ITS is a multiple layer, silicon vertex detector at the heart of ALICE. An upgrade of the system will place the first detection layer closer to the beam line, reduce the material budget and improve the maximum readout rate [23]. The upgrade is scheduled during the second LHC shutdown (LS2) in the years 2019 - 2020.

Figure 3.1 shows how the ALPIDE chips will be placed in the ITS. There are seven layers of detector chips and the two outer and middle chip layers will be configured in the Outer Barrel mode. The output data rate of these chips will be reduced compared to the chips in the three inner layers, which are set up in Inner Barrel mode. The ALPIDE configuration modes are explained in Section 3.2.1. The different configurations and speed of the data streams are critical in the readout electronic's point of view [24]. It is challenging to accomplish clock data recovery with multiple data speeds. High-speed data recovery is often accomplished by utilizing transceivers (see Section 4.5.1) that require input data with a fixed rate.

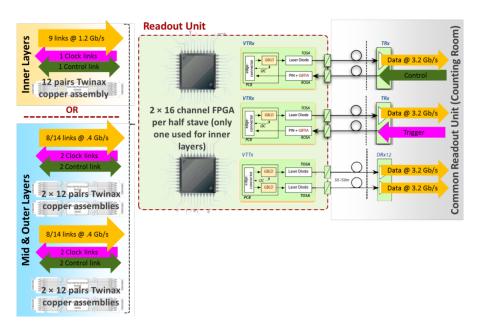

The readout system makes use of 192 identical readout units which are interfaced to the ALPIDE chips, as illustrated in Figure 3.2. These units cover the full ITS and provide the clock, control, and data links. An external device, the Central Trigger 3.1. ALICE ITS

Figure 3.1: ALICE ITS seven layers layout [24, Figure 1].

Figure 3.2: ITS Readout Unit implementation [24, Figure 37].

Processor, provides the trigger signal to the readout units which distribute the signal to the ALPIDE chips. Further links are connected to the Common Readout Unit, which is interfacing all readout units. This device handles the communication with the ALPIDE chips and receives the data for further processing.

## 3.2 ALPIDE Chip

The ALPIDE chip was developed for the ALICE ITS upgrade at CERN. The ALPIDE is a particle detector based on monolithic active pixel sensor, and is implemented in 180 nm CMOS technology process that is enhanced for imaging sensors [6]. The chip contains a matrix of 512x1024 pixels, which individually can detect an ionization energy over a common threshold level. A pixel hit can then be latched onto an in-pixel memory position if certain conditions are met. The information about pixel hits during a certain time period can be read out over a high-speed serial link.

#### 3.2.1 Operation Modes

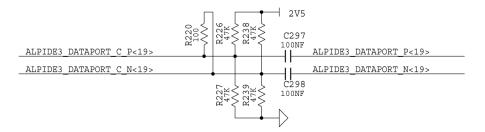

The ALPIDE can be configured to operate in three different modes; Inner Barrel Chip, Outer Barrel Master and Outer Barrel Slave. These modes make the ALPIDE work in separate ways related to where they will be placed in the ALICE ITS detector. However, in the proton CT, there may be a high rate of particle hits in all areas of the detector. Hence, it makes sense to focus on the Inner Barrel mode which provides the highest data transfer rate. A differential signaling 1.2 Gb/s serial data port is the Inner Barrel mode's data readout interface, where 8B/10B encoding makes the maximum data throughput 960 Mb/s. The control interface is also a differential signaling serial port, but at a significantly slower rate, 40 Mb/s. Consequently, its called the *slow* control interface. The interface supports bi-directional half-duplex signaling and multi-point connection. This means that several ALPIDE chips can be connected to the same control signal, but the chips require unique IDs to differentiate them from each other. The ID will also set the chip operation mode, as presented in Section 3.3.

## 3.3 ALPIDE Control Interface

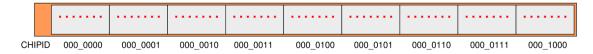

The ALPIDE chips are integrated on staves. The Inner Barrel stave contains nine ALPIDE chips stitched together, adding up to a total length of 27 cm. The IDs are interfaced to the chips through a dedicated 7-bit chip port, CHIPID. The three MSBs are used to set the operating mode of the chip. All zeroes indicate Inner Barrel mode.

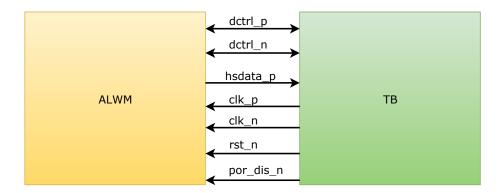

| Port         | Description                     | Direction | Type                                |

|--------------|---------------------------------|-----------|-------------------------------------|

| DCLK_P       | Main clock                      | IN        | Differential (M-LVDS <sup>a</sup> ) |

| DCLK_N       | Main clock                      | IN        | Differential (M-LVDS <sup>a</sup> ) |

| CHIPID [6:0] | Chip address and mode operation | IN        | CMOS, internal pull-down            |

| HSDATA_P     | High-speed serial data          | OUT       | Differential (LVDS <sup>b</sup> )   |

| HSDATA_N     | High-speed serial data          | OUT       | Differential (LVDS <sup>b</sup> )   |

| DCTRL_P      | Control interface               | IN/OUT    | Differential (M-LVDS <sup>a</sup> ) |

| DCTRL_N      | Control interface               | IN/OUT    | Differential (M-LVDS <sup>a</sup> ) |

| RST_N        | Global chip reset               | IN        | CMOS, internal pull-up              |

| POR_DIS_N    | Power-On Reset disable          | IN        | CMOS, internal pull-up              |

Table 3.1: ALPIDE interface ports relevant for Inner Barrel mode operation

The four LSBs provide the chip with an address ID unique to that stave. The IDs are used both to control a particular chip and to identify the data from a specific chip.

Figure 3.3: The chip ID scheme for Inner Barrel Mode [6].

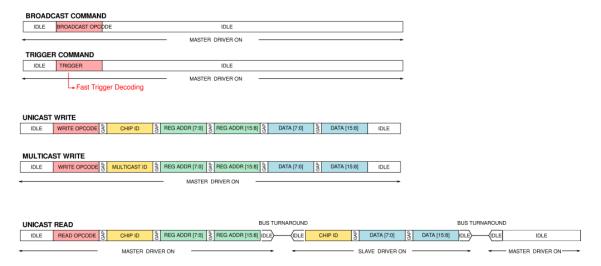

The control bus, DCTRL, enables read and write access to all ALPIDE control and status registers, as well as providing a command distribution channel. The ALPIDE chip contains a large set of local registers for configuration of operation. These registers control everything from PLL settings to data readout speed. They also serve as the configuration registers for multiple test features, e.g. test vectors to be transmitted over the high-speed serial link. Communication via the control bus is accomplished by sending pre-defined opcodes on the bus. The ALPIDE chips interpret the received opcode and then perform the requested action. Some opcodes are tailored for a single chip, e.g. unicast read, which is used to read the data stored in a register on a specified chip. Other opcodes, like multicast write, involve communication with all the chips connected to the same control port. There are also broadcast commands that trigger actions from all the chips but, in contrast to multicast commands, are without subsequent communication. One special broadcast

<sup>&</sup>lt;sup>a</sup> Designed concerning standard TIA/EIA-899 Electrical Characteristics of Multipoint-LVDS, but are not standard regarding the range of input common voltage.

<sup>&</sup>lt;sup>b</sup> Not standard regarding the range of input common voltage.

command is the TRIGGER command. The opcodes<sup>1</sup> for this command are decoded with much lower latency in the internal decoding by the ALPIDE chips than the other broadcast commands. The list of the predefined opcodes is available in the ALPIDE Operations Manual [6, Table 3.3].

Figure 3.4: Valid transaction formats [6].

The various opcodes require different transaction formats that fit the purpose of the opcode. E.g., if a single chip is to send data from one of its registers, the unique chip ID must be provided so that the intended chip can respond. Figure 3.4 illustrates the different transaction formats required for control bus communication.

### 3.4 ALPIDE Data Interface

The data interface when the chip is in the Inner Barrel mode is utilized by the differential serial port (HSDATA\_P and HSDATA\_N). By default, the data is encoded by the 8B/10B algorithm. 8B/10B is a coding method to achieve DC-balance, which is a requirement of some transmission media for the receiver to reliably distinguish between a high or low bit [25, 26, Chapter 2]. The ALPIDE will transmit a comma word when not transmitting data. Since no clock is transferred along the data from the ALPIDE, the comma word can be used for clock recovery and to achieve byte synchronization [25], and even phase alignment as proposed in Section 4.6.

<sup>&</sup>lt;sup>1</sup>There are four opcodes for the TRIGGER command which reflect the low latency nature of the opcode decoding. The decoding is based on the two LSBs of the command which is the same for all the four opcodes.

Data from the ALPIDE is formatted according to a predefined list of valid data words, as observed in Table 3.2. E.g., all data packets will begin with a 16-bit header that includes the chip ID and the value of the bunch crossing counter when the trigger corresponding to the data was received. An important data word is BUSY ON, which is transmitted on an assertion of the BUSY status. This is a state which is activated when the chip approaches saturation of its data processing capabilities.

| Data Word        | Length (bits) | Value (binary)                                                                                    |

|------------------|---------------|---------------------------------------------------------------------------------------------------|

| IDLE             | 8             | 1111_1111                                                                                         |

| CHIP HEADER      | 16            | 1010 <chip_id[3:0]><bunch_counter_for_frame[10:3]></bunch_counter_for_frame[10:3]></chip_id[3:0]> |

| CHIP TRAILER     | 8             | 1011 <readout_flags[3:0]< td=""></readout_flags[3:0]<>                                            |

| CHIP EMPTY FRAME | 16            | 1110 <chip_id[3:0]><bunch_counter_for_frame[10:3]></bunch_counter_for_frame[10:3]></chip_id[3:0]> |

| REGION HEADER    | 8             | 110 <region_id[4:0]></region_id[4:0]>                                                             |

| DATA SHORT       | 16            | 01 <encoder_id[3:0]><addr[9:0]></addr[9:0]></encoder_id[3:0]>                                     |

| DATA LONG        | 24            | 00 <encoder_id[3:0]><addr[9:0]>_0_<bit_map[6:0]></bit_map[6:0]></addr[9:0]></encoder_id[3:0]>     |

| BUSY ON          | 8             | 1111_0001                                                                                         |

| BUSY OFF         | 8             | 1111_0000                                                                                         |

Table 3.2: Valid data words [6, Table 3.37].

## 3.5 ALPIDE Operation

#### 3.5.1 Front-end

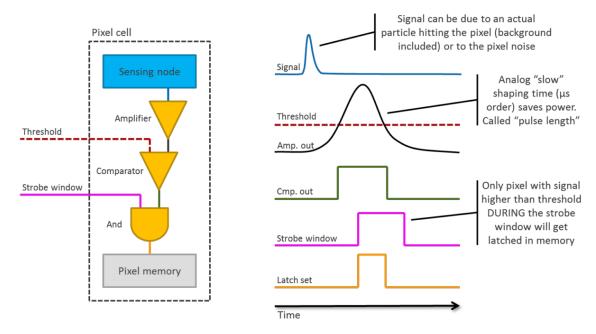

Each sensor pixel in the ALPIDE matrix has a width of 29.24  $\mu$ m and height of 26.80  $\mu$ m. An analog front-end circuit transforms the physical effects of a particle hit into a digital signal which is sent to the digital section of the pixel. The signal may set the hit state register of the pixel if the corresponding STROBE signal (see Section 3.5.3) is asserted simultaneously. Each pixel feature three state registers or buffers referred to as a Multi-Event Buffer (MEB) that store hit information. This means that each pixel may store a maximum of three hits at the same time. Depending on the readout mode (see Section 3.5.3 and 3.5.4), the BUSY status is asserted based on the number of filled registers. These registers can also be programmed digitally for testing purposes.

Figure 3.5 shows a simplified pixel logic schematic, including a timing diagram of a pixel hit. The analog front-end electronics are always on and can create a shaped signal at any time. The shaped signal output from the amplifier is in the order of µs. These design choices were made to save power [24]. The shaping signal is fed to a comparator and will produce a logic 1 if it exceeds the threshold value. The

Figure 3.5: Pixel logic schematic and timing diagram [24, Figure 15].

threshold value is variable and can be set via the control interface.<sup>2</sup> As discussed, if the comparator outputs a logic 1 while the strobe signal is asserted, the value is latched to the pixel MEB. Note that if two strobe windows are sufficiently close together, a shaping signal can extend between both windows, and as a result, a pixel hit may be registered twice.

## 3.5.2 Priority Encoders

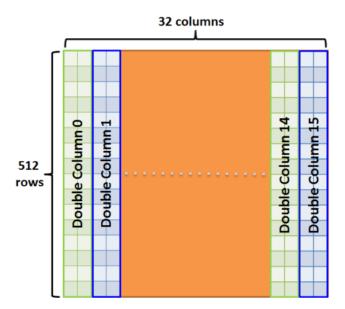

The pixels are split into 32 regions containing 16 double columns of pixels. A single region is observed in Figure 3.6. The data is read out from 512 priority encoder blocks, one for each double-column.

## 3.5.3 Triggering and Framing

To capture information about particle hits, the ALPIDE will store the collection of all pixel MEBs at a particular time in a frame or snapshot. Following a TRIGGER command, the chip generates a frame and subsequently transmits data from the chip. The TRIGGER command may be received on the control interface or generated internally by a sequencer. The TRIGGER command is handled by the Framing

<sup>&</sup>lt;sup>2</sup>Note that the threshold is set on a chip basis, and the threshold will naturally fluctuate between the pixels because of process variations, inter alia.

Figure 3.6: Double columns of data pixels in a single region [6, Figure 4.4].

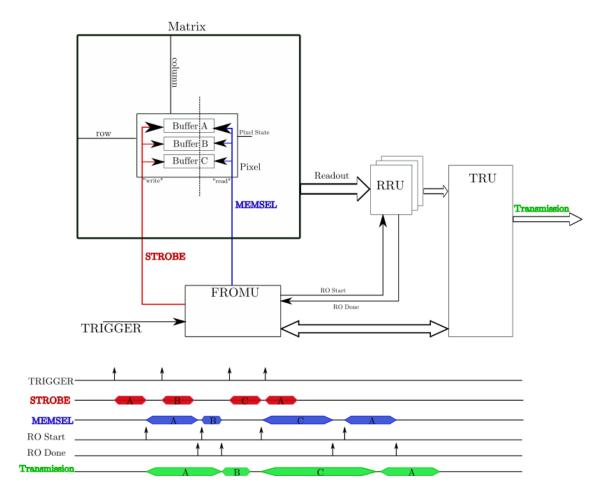

and Management Unit (FROMU), which then generates the STROBE signal that is connected to the digital section of the pixels (see Section 3.5.1). The window in which STROBE is asserted is called the framing window. The MEMSEL signal is also generated by the FROMU and indicates which register bank to be read out. As seen in Figure 3.7 the data is readout through the Region Readout Units and then to the Top Readout Unit which transmits the data off the chip.

The length of the framing window can be customized and is subjectable to which readout mode the chip is configured in. In triggered mode, the intended framing window is relatively short (hundreds of ns), and the start of the window is typically controlled by an external trigger source. In continuous mode, the framing window is intended to be longer (a few  $\mu$ s). The framing window is meant to be periodically initiated, and the intervals have a duration equal to the period between two consecutive framing windows. The internal sequencer can generate the trigger, with register control of strobe and gap length.

The two modes are in principle similar, except from the logic handling. *Triggered* mode will prioritize events that are already stored in the MEBs, and a TRIGGER command received when the buffers are full will not generate a new framing window. *Continuous* mode, however, will prioritize newly received frame requests over already stored data. In this mode, there must always be one buffer free of data.

Figure 3.7: Pixel MEB Management Scheme [6, Figure 3.7].

#### 3.5.4 BUSY State

It takes time to read out the data from the MEBs, and when the chip is near saturation of its data processing capabilities, the BUSY state is asserted. In an Inner Barrel configuration, the communication of the BUSY state to the outside world is done through the data link. In triggered mode, the chip is BUSY at the beginning of a framing window that addresses the last free buffer, when there is no more available storage for another framing window. All further TRIGGERs will be ignored until the BUSY state is over. The BUSY is done as soon as one of the buffers are completely read out. In continuous mode, BUSY is asserted at the beginning of a framing window targeting the second buffer, when there is only one free buffer left. A TRIGGER received in the BUSY state will initiate a framing window if the last buffer is available, whilst interrupting the ongoing readout to ensure that there is always a free buffer. This is signaled to the outside world with a flag on the data

chip trailer. BUSY is deactivated once two buffers are available.

The BUSY ON data word transferred while the chip is in the BUSY state does not contain any information about what caused the situation to occur. Note that a BUSY state may also occur when internal FIFOs in the readout units of the chip are saturated.

#### 3.6 ITS Readout Unit

The ITS readout unit provides 32 high-speed I/Os, and is interfacing a various amount of chips depending on which detector layer it is affiliated with. For the inner layers, one readout unit interfaces only one stave, and must therefore handle just nine data pairs, one clock, and one control line. A middle layer and an outer layer stave consists of 8 and 14 modules, respectively. A module consists of two master chips which interfaces the readout unit. Thus, for the outer layers, the readout units must handle 28 data pairs. For the middle layers the readout unit must handle 16 data pairs. This is illustrated in Figure 3.2.

The readout unit itself will consist of a PCB with a state-of-the-art FPGA chip that handles the majority of tasks in the programmable internal circuits. Data and control connections to the Central Trigger Processor and the Common Readout Unit are implemented optically with the CERN-developed GBT link.

#### 3.6.1 Modules Overview

The readout unit consists of three main modules that are interfaced to the ALPIDE chips; the control module, the data readout module, and the voltage module.

#### 3.6.2 Control Module

In order to communicate with the ALPIDE chips, the readout unit requires a control module that performs operations on the stave-shared communication line. The control module<sup>3</sup> handles all the slow control operations discussed in Section 3.3 and ensures that the bus turnaround operation is performed correctly. The module is operating on the same 40 MHz clock that is provided to the ALPIDE chips. The slow control output is serialized by this clock. However, to avoid metastability issues, the slow control data from the ALPIDE is sampled with a 160 MHz clock. The input is then deserialized by choosing a fixed point in the 160 MHz clock period. The phase

<sup>&</sup>lt;sup>3</sup>The pCT readout unit design can inherit the module developed by Matteo Lupi (matteo.lupi@cern.ch) at CERN.

position is set by a 2-bit register and is not obtained automatically. Hence, there are four positions of sample points to choose from. This method is tested successfully at CERN [27].

To avoid sending TRIGGER commands to the ALPIDEs when a chip is busy, the module monitors a busy signal. This busy signal may be connected to the output of a protocol checker (see Section 3.6.3). Note that the effect of this feature is that no other chips on the stave will receive a TRIGGER command if a single chip reports the busy state. However, the feature can be disabled by setting a register.

The communication to the ALPIDE chips is mainly controlled by the readout unit's bus interface and the control module registers. When writing to the CTRL register, the communication state machine is initialized and is employing the data stored in the DATA and OPCODE registers to determine which operation to perform. However, operations may also be initialized by asserting the TRIGGER or PULSE input signals. This means that these commands may be performed without interacting with the bus interface, e.g. by an external device that controls the TRIGGER operation for all the readout units (see Section 4.10.1). Note that the control module does not reject these external commands whenever a busy state has been detected.

#### 3.6.3 Data Module

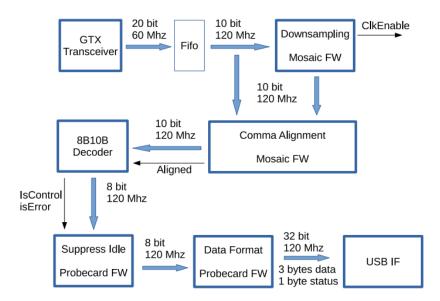

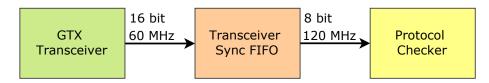

The data recovery for the ITS must handle the different operation modes of the detector chips in the different layers. This complicates the use of built-in FPGA transceivers to achieve byte synchronization because the transceivers rely on a given data rate. However, it is still possible to use the transceiver to sample each data bit. The ALPIDE has three data rates; 1.2 Gb/s, 600 Mb/s and 400 Mb/s. Fortunately, these rates are fractions of each other. The transceiver can sample the data at a fixed rate of 1.2 Gb/s. For the lower speed rates, this just means oversampling. For given settings, the data can be downsampled to reflect the actual data rate. The downsampling module excludes the bits that are sampled multiple times by the transceiver, and creates a 10-bit word. It is fairly trivial to activate and deactivate this kind of module by using a configuration register.

This design, shown in Figure 3.8, was developed by engineers at CERN. Comma detection and alignment, as well as 8B10B decoding, are realized by RTL modules. The design also involves the data chain until read out over a USB interface.

#### **Protocol Checker**

The protocol checker module is not included in the block diagram but is connected to the data output from the 8B10B decoder. Its purpose is to analyze the data transmitted from the ALPIDE and detect errors in the protocol. It will assert various

Figure 3.8: Block diagram of ITS readout data recovery system [27].

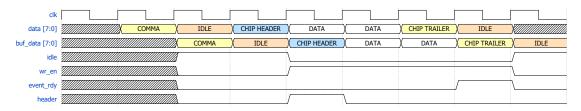

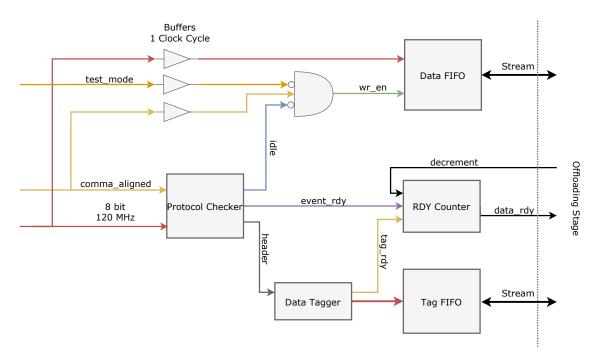

signals under certain conditions, for example when a chip is busy or a region is empty. The protocol checker module is described more thoroughly in Section 4.6.4. This module was later modified for pCT to be used for testing of test vectors (see Section 5.3.1), and then to aid with filtering, tagging, and buffer data (see Section 5.8).

## 3.6.4 Voltage Module

The purpose of the voltage module is to enable the voltage regulators that provide the ALPIDE with its required voltage and current. It is reused during the development phase for the pCT, but must be modified according to requirements discussed in Section 4.11.

## pCT Readout System

This chapter offers a discussion of the pCT system requirements and proposes a readout system design. Further, a readout unit and the different stages of the readout process are discussed in detail. The following sections present clock data recovery methods. This includes Section 4.5.2 which describes a data recovery method utilizing a transceiver for sampling data, comma alignment and 8B/10B decoding. This design is implemented and tested as discussed in Section 5.4. Section 4.6 portrays an automated approach to achieving phase and word alignment. This design is fully implemented and tested in Section 5.6 and 5.7.

Subsequently Section 4.7 is about data filtering, tagging and buffering and presents a design proposal that will handle these tasks. Parts of this design are realized and simulated in Section 5.8. However, further analysis is needed to develop a complete design.

The following section offers a discussion on communication between modules. This involves the choice of bus interface. Arguments are made as to which bus interface best suits the pCT design. The implementation and verification is described in Section 5.5.

The next part presents a discussion of how the pCT system should operate to accommodate the timing requirements of the scanner. Finally, the system's power control and monitoring features are briefly drafted. The last two sections are presented without specific design implementations.

## 4.1 pCT Requirements

The pCT scanner will utilize the ALPIDE chips in a layer-like fashion, but the details were not completely specified during the work of this thesis. The final specifications of the detector layout will depend on data simulations that will calculate the size

needed to create a sufficiently detailed picture of the phantom. The leading idea is that a detector with 40 layers with a 4 mm gap, consisting of aluminum and air, will be adequate to fulfill the requirements. One also expects that the cost of ALPIDE production will limit the detector size. A visualization of a pCT setup is shown in Figure 4.1a.

(a) Visualization of a pCT scanner with layers of detector chips.

Figure 4.1: Assumed detector layout. Size and distance are arbitrarily chosen and not to scale.

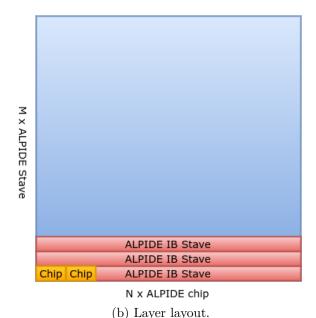

However, it can temporarily be assumed that a single layer will be constructed like a square made up of multiple Inner Barrel ALPIDE staves. As mentioned in Section 3.3, these staves contain nine ALPIDE chips that are bonded together. A layer will then require eighteen staves to create a square. Further, we assume that all layers will be equal in size and that there will be between 20 and 40 layers. We must, however, keep in mind that the specifications may change in the future and that the proposed system design must be modular in order to accommodate for updates. Figure 4.1b shows the tentative layout of a layer.

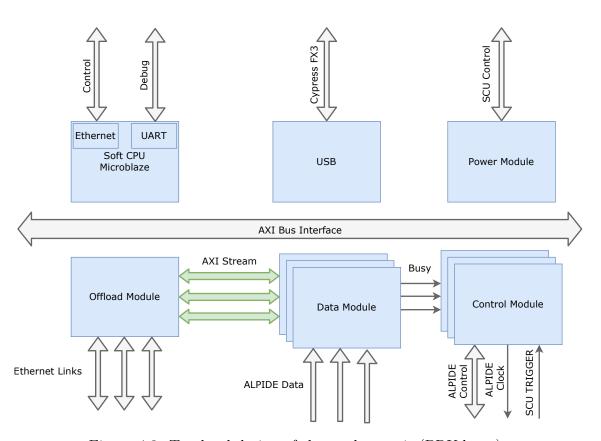

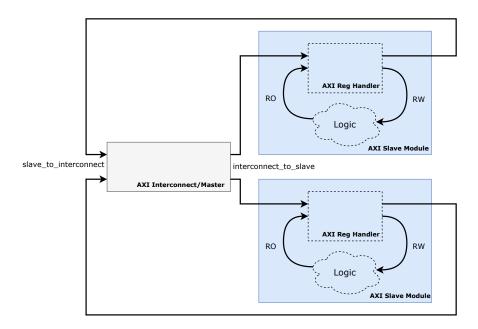

Figure 4.2: Block diagram of the proposed pCT Readout System.

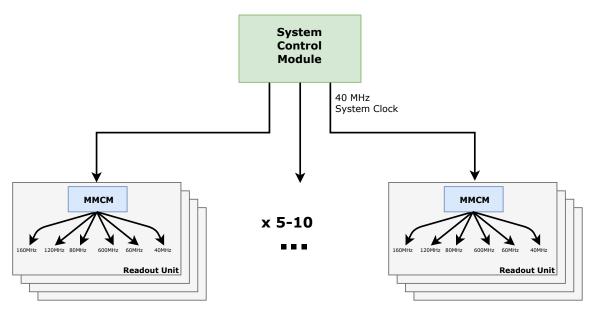

The block diagram of the proposed pCT readout system (see Figure 4.2) consists of two main units; the readout unit (PRUdense) and the System Control Unit (SCU). PRUdense is interfacing the ALPIDE chips' data channel and controls the communication channels. The SCU is responsible for distributing the system clock and monitoring of the status of the staves and the readout units. Additionally, the SCU may also distribute a trigger signal to the readout units. Both main system units can be controlled from the control room.

The design of the pCT scanner involves one major advantage compared to the design of the ITS: All layers will consist of inner barrel staves, and hence, the readout units need only handle a single data rate of 1.2 Gb/s. This simplifies the clock recovery and data sampling and also reduces the need for different configurations of the readout units.

The proposed layer size incorporates 162 ALPIDE chips that each sends data over its own LVDS line. However, the control and clock lines are shared between the chips on one stave. To achieve regularity (see Section H.2.2), it will be beneficial to create identical readout units. A further aim would be to design readout units that can handle one whole layer each. Though not critical, this would significantly reduce cost and complexity of the remaining system. The major point is that the readout units handle equal amounts of data links and that the origin of the data is recoverable when the data is transmitted to the data center.

The pCT scanner will in principle require less time than ITS to collect enough data to achieve the desired results, and a guessed estimate is between 1 and 10 seconds.

This is beneficial when considering data transfer from the readout units as it may enable buffering data before offloading. Another benefit is that critical chip failure, like single event latch-up (SEL), may not cause a significant amount of data loss, and reconfiguration of the chip can wait until the next data-taking procedure. Although, this must be verified by simulations.

A further difference between the ITS and pCT readout systems is the expected radiation levels in the environment in which the readout units are located. The assumption is that the pCT readout units will be placed with a certain distance to the proton beam, and that the baseline radiation will be low enough to avoid adverse interaction with the electronics. This must be verified by simulations and measurements, which falls beyond the scope of this thesis. Regardless, one must evaluate taking precautions in the design process and choosing alternatives that historically reduces the single event upset (SEU) rate.

In the ITS setup, the distance between detector chips and readout units requires data cables of 5 meters [28]. It is assumed that this will be reduced to between 1 and 2 meters for the pCT setup. This reduction is relevant for data readout testing where different possible cable lengths must be tested.

## 4.2 pCT Readout Unit (PRUdense)

The readout unit will interface an unknown number of ALPIDE sensor chips. The unit is named based on the density of ALPIDE chips it is interfaced to. It will be responsible for the following tasks:

- Receive and decode multiple high-speed data streams (1.2 Gb/s)

- Handle communication with multiple ALPIDE staves (40 Mb/s)

- Filter and distribute TRIGGER signals to the ALPIDE chips

- Combine multiple data streams into a convenient data format

- Tag the data streams with time and detector placement

- Detect BUSY ALPIDE chip

- Perform error checking

- Transmit data to central

- Monitor and control voltage and current

- Reconfigure ALPIDE chip in the event of SEL, or similar critical error

Potentially, if found beneficial:

• Buffer data on onboard RAM

However, it is beyond the scope of this thesis to cover all of these features in detail. Emphasis is put on finding the most efficient clock and data recovery method, as well as outlining all of the readout stages discussed in Section 4.4. The following

sections will discuss and examine the different design and implementation choices for the readout unit.

#### 4.2.1 Top Level Design

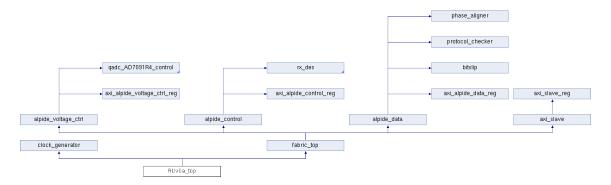

Figure 4.3: Top level design of the readout unit (PRUdense).

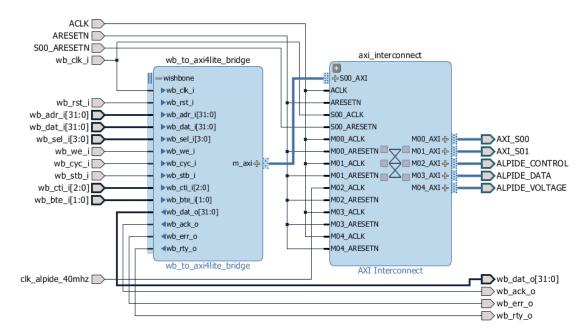

The top level design in Figure 4.3 shows the readout unit modules and how they are connected to the AXI bus interface. Bus interface discussion is covered in Section 4.9.

USB is used for communication and debugging until the soft processing system is implemented and tested. The UART channel is intended to be used as a debug channel and can indirectly communicate with the AXI bus via software running on the CPU. Ultimately, the processing system's main communication channel will be via one of the Ethernet links.

There are an equal number of data modules as there are ALPIDE chips connected to the readout unit. This module's task is to recover and sample the data correctly (see Section 4.5 and 4.6), filter redundant data words (see Section 4.7.1), and tag the data and buffer it (see Section 4.7.3), until it is read out on the AXI Stream interface to the offload module. Each module directly interface one ALPIDE data channel. The

data module can also analyze the data and alert the corresponding stave's control module if the ALPIDE is busy.

The control modules are controlling the ALPIDE control channel. Each module control one stave of ALPIDE chips. The module is also interfacing the SCU's triggering signal and must respond to an assertion of that.

The power module (see Section 4.11) is controlling the voltage and current regulators on the readout board, and monitors the power drawn by the ALPIDE chips. The module is interfacing the AXI bus and is mainly controlled and monitored by the SCU. Whether the SCU is interfacing the module via the AXI bus or via another interface is yet to be determined.

#### 4.3 Electronics

Reliable handling of many high-speed links will require parallel processing to avoid bottle-necking. Developing a custom ASIC would provide the performance needed, but this usually requires a high production quantity to be justified economically [7, Chapter 13]. It is, therefore, more common to use FPGAs in highly technical demanding scientific projects where the non-recurring engineering cost must be kept low, and design resources and time are scarce. An FPGA also provides a higher degree of flexibility in the design process, and this is especially useful in the development in the pCT due to the unknown or unclear specifications.

Two companies share the majority of the commercial FPGA market; Xilinx and Altera.<sup>1</sup> Both companies provide a variety of SRAM-based FPGA products with and without System-On-Chip (SoC) features. The chips vary in the number of programmable logic blocks, on-chip RAM blocks, high-speed transceivers, and more. Xilinx claims that their products are designed to have an inherently low susceptibility to SEUs [29]. Although it is assumed that the baseline radiation level will be low in the pCT readout environment, it will be higher than the natural background levels. Thus, a greater degree of resistance to radiation-induced upsets may be beneficial.

Changing FPGA provider, and thus tools, design flow, and much more, during a design process, is usually time-consuming and must be thoroughly evaluated. The design team for the ITS upgrade chose Xilinx chips as the design target early in the design process. Thus, large parts of the development that the pCT firmware will be based on are targeting Xilinx technology. Finding a Xilinx chip that fits the pCT requirements will be highly beneficial.

The newest Xilinx product family is called UltraScale+TM. The Virtex devices are the largest of the product family. They provide the highest quantity of programmable

<sup>&</sup>lt;sup>1</sup>Altera was recently acquired by Intel.

logic resources, but do not provide SoC features. The Zync devices, however, provide a powerful hard processor system, but significantly lower programmable resources. Figure 4.4a and 4.4b show product overviews of Virtex and Zync devices.

| Device Name                | VU3P      | VU5P      | VU7P      | VU9P      | VU11P     | VU13P     | VU31P     | VU33P     | VU35P     | VU37P     |

|----------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| System Logic Cells (K)     | 862       | 1,314     | 1,724     | 2,586     | 2,835     | 3,780     | 962       | 962       | 1,907     | 2,852     |

| CLB Flip-Flops (K)         | 788       | 1,201     | 1,576     | 2,364     | 2,592     | 3,456     | 879       | 879       | 1,743     | 2,607     |

| CLB LUTs (K)               | 394       | 601       | 788       | 1,182     | 1,296     | 1,728     | 440       | 440       | 872       | 1,304     |

| Max. Distributed RAM (Mb)  | 12.0      | 18.3      | 24.1      | 36.1      | 36.2      | 48.3      | 12.5      | 12.5      | 24.6      | 36.7      |

| Total Block RAM (Mb)       | 25.3      | 36.0      | 50.6      | 75.9      | 70.9      | 94.5      | 23.6      | 23.6      | 47.3      | 70.9      |

| UltraRAM (Mb)              | 90.0      | 132.2     | 180.0     | 270.0     | 270.0     | 360.0     | 90.0      | 90.0      | 180.0     | 270.0     |

| HBM DRAM (Gb)              | -         | -         | -         | -         | -         | -         | 32        | 64        | 64        | 64        |

| HBM AXI Ports              | -         | -         | -         | -         | -         | -         | 32        | 32        | 32        | 32        |

| Clock Mgmt Tiles (CMTs)    | 10        | 20        | 20        | 30        | 12        | 16        | 4         | 4         | 8         | 12        |

| DSP Slices                 | 2,280     | 3,474     | 4,560     | 6,840     | 9,216     | 12,288    | 2,880     | 2,880     | 5,952     | 9,024     |

| Peak INT8 DSP (TOP/s)      | 7.1       | 10.8      | 14.2      | 21.3      | 28.7      | 38.3      | 8.9       | 8.9       | 18.6      | 28.1      |

| PCIe® Gen3 x16 / Gen4 x8   | 2         | 4         | 4         | 6         | 3         | 4         | 4         | 4         | 5         | 6         |

| CCIX Ports <sup>(1)</sup>  | -         | -         | -         | -         | -         | -         | 4         | 4         | 4         | 4         |

| 150G Interlaken            | 3         | 4         | 6         | 9         | 6         | 8         | 0         | 0         | 2         | 4         |

| 100G Ethernet w/ RS-FEC    | 3         | 4         | 6         | 9         | 9         | 12        | 2         | 2         | 5         | 8         |

| Max. Single-Ended HP I/Os  | 520       | 832       | 832       | 832       | 624       | 832       | 208       | 208       | 416       | 624       |

| GTY 32.75Gb/s Transceivers | 40        | 80        | 80        | 120       | 96        | 128       | 32        | 32        | 64        | 96        |

| Extended <sup>(2)</sup>    | -1 -2L -3 |

| Industrial                 | -1 -2     | -1 -2     | -1 -2     | -1 -2     | -1-2      | -1-2      | -         | -         | -         | -         |

(a) Virtex Ultrascale+TM product overview [30].

| Device Name <sup>(1)</sup>                                                                            | ZU2EG                                                                      | ZU3EG                                                               | ZU4EG | ZU5EG | ZU7EG     | ZU6EG     | ZU9EG | ZU15EG | ZU11EG | ZU17EG | ZU19EG |  |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|-------|-------|-----------|-----------|-------|--------|--------|--------|--------|--|

| Processor Core Quad-core ARM® Cortex™-A53 MPCore™ up to 1.5GHz                                        |                                                                            |                                                                     |       |       |           |           |       |        |        |        |        |  |

| Memory w/ECC                                                                                          |                                                                            | L1 Cache 32KB I / D per core, L2 Cache 1MB, on-chip Memory 256KB    |       |       |           |           |       |        |        |        |        |  |

| Processor Core                                                                                        | Dual-core ARM Cortex-R5 MPCore™ up to 600MHz                               |                                                                     |       |       |           |           |       |        |        |        |        |  |

| Memory w/ECC                                                                                          |                                                                            | L1 Cache 32KB I / D per core, Tightly Coupled Memory 128KB per core |       |       |           |           |       |        |        |        |        |  |

| Graphics Processing Unit                                                                              |                                                                            | Mali™-400 MP2 up to 667MHz                                          |       |       |           |           |       |        |        |        |        |  |

| Memory                                                                                                |                                                                            | L2 Cache 64KB                                                       |       |       |           |           |       |        |        |        |        |  |

| Dynamic Memory Interface x32/x64: DDR4, LPDDR4, DDR3, DDR3L, LPDDR3 with ECC                          |                                                                            |                                                                     |       |       |           |           |       |        |        |        |        |  |

| Static Memory Interfaces NAND, 2x Quad-SPI                                                            |                                                                            |                                                                     |       |       |           |           |       |        |        |        |        |  |

| High-Speed Connectivity PCIe® Gen2 x4, 2x USB3.0, SATA 3.1, DisplayPort, 4x Tri-mode Gigabit Ethernet |                                                                            |                                                                     |       |       |           |           |       |        |        |        |        |  |

| General Connectivity                                                                                  |                                                                            |                                                                     |       |       |           |           |       |        |        |        |        |  |

| Power Management                                                                                      |                                                                            |                                                                     |       |       |           |           |       |        |        |        |        |  |

| Security                                                                                              | RSA, AES, and SHA                                                          |                                                                     |       |       |           |           |       |        |        |        |        |  |

| AMS - System Monitor                                                                                  | - System Monitor 10-bit, 1MSPS - Temperature, Voltage, and Current Monitor |                                                                     |       |       |           |           |       |        |        |        |        |  |

|                                                                                                       | 12 x 32/64/128b AXI Ports                                                  |                                                                     |       |       |           |           |       |        |        |        |        |  |

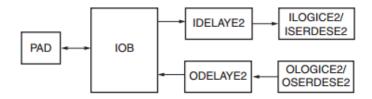

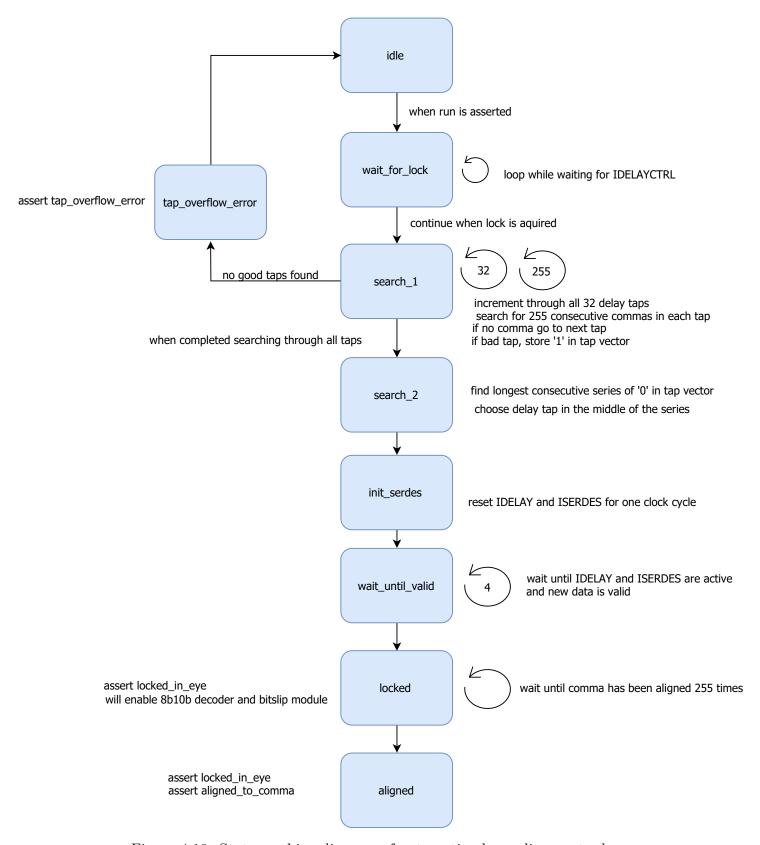

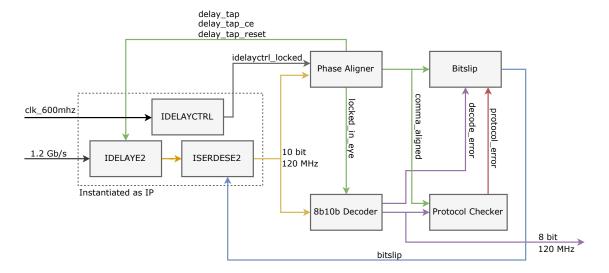

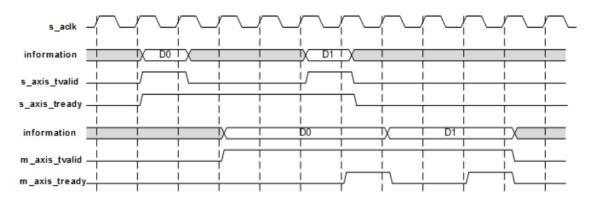

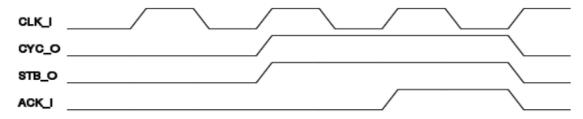

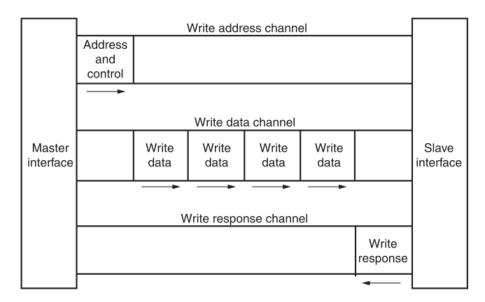

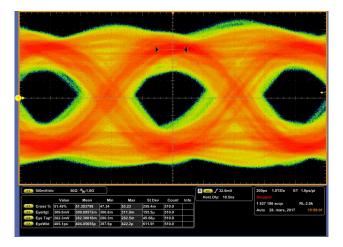

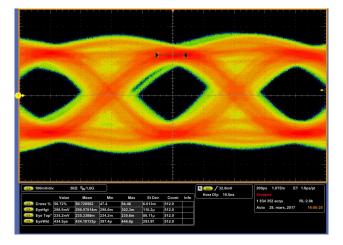

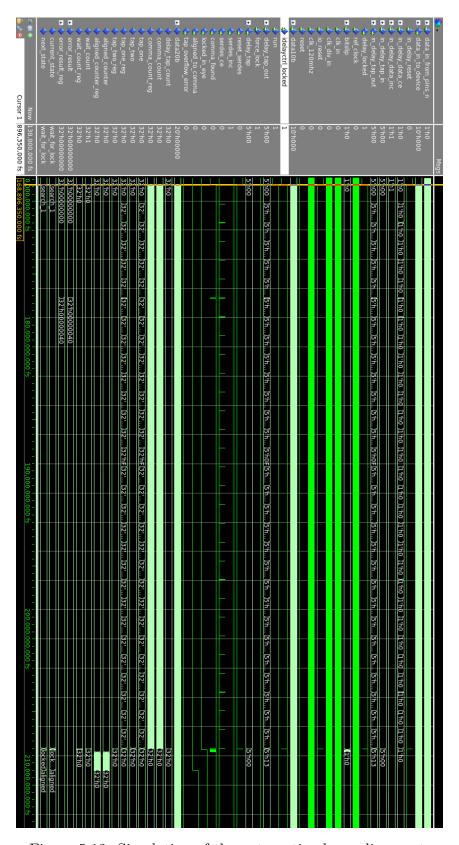

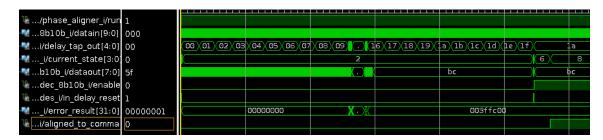

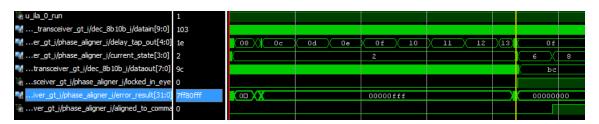

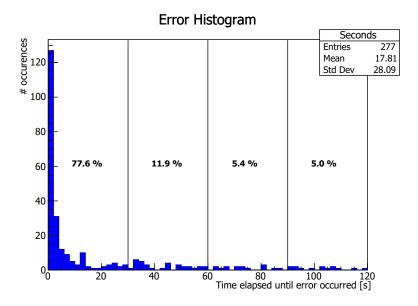

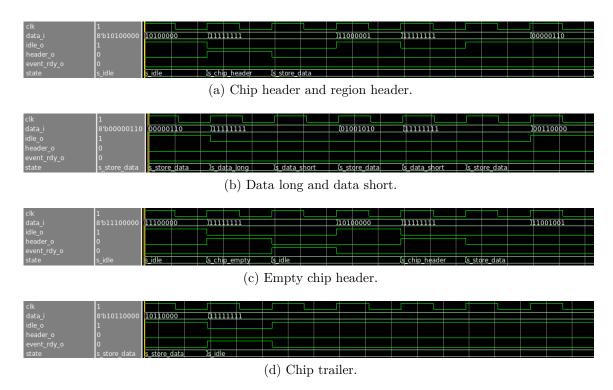

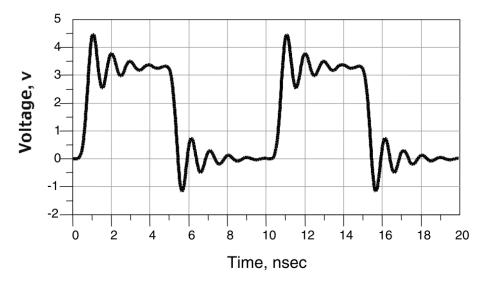

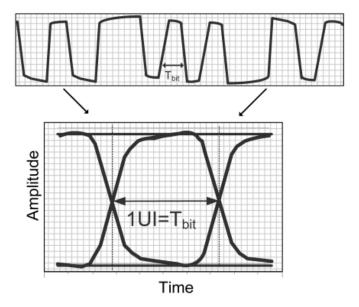

| System Logic Cells (K)                                                                                | 103                                                                        | 154                                                                 | 192   | 256   | 504       | 469       | 600   | 747    | 653    | 926    | 1,143  |  |