# A setup for electrical quality assurance of ATLAS SCT barrel modules

# Candidatus Scientiarum Thesis by Ola Kristoffer Øye

University of Bergen

Department of Physics

March 2003

## **Abstract**

The ATLAS SemiConductor Tracker (SCT) is part of the inner detector in the ATLAS detector at the LHC complex at CERN. SCT will consist of a system of silicon strip detectors with digital readout, reading out space point information from high-energy proton-proton collisions. The detector will be assembled from over 4088 detector modules, with one type of module for the barrel part (2112 modules) and one for the end-caps (1976 modules). Before the assembly, the modules need to undergo a thorough quality assurance (QA) procedure, both in terms of physical properties and electrical performance. This thesis describes the setup of an electrical QA system for SCT barrel modules at the University of Bergen

The University of Bergen is part of the SCT group *Scandinavian Cluster*, together with the University of Oslo and the University of Uppsala. The group is responsible for building and testing 384 detector modules.

## Acknowledgements

During the work on this thesis, I have had the opportunity to work with many helpful and resourceful people, and I would especially like to thank:

Professor Bjarne Stugu, supervisor, for letting me work on this project, and for advice both during the practical work and the writing process.

Bjørn Pommeresche, Lars G. Johansen and Arne Solberg in Bergen for always answering questions and helping me with practical issues.

Lars Eklund at Uppsala University/CERN for rewarding discussions and answers to numerous questions.

Werner Olsen for help with noise reduction in environmental chamber.

My fellow students at the physics department in Bergen.

Ola Kristoffer Øye Bergen, 28/03-2003

## **Contents:**

| Abstract                                                        | III |

|-----------------------------------------------------------------|-----|

| Acknowledgements                                                | V   |

| Chapter 1: Introduction to LHC and ATLAS                        | 1   |

| 1.1 CERN                                                        |     |

| 1.2 LHC                                                         |     |

| 1.2.1. Proton-proton collisions at the LHC                      | 4   |

| 1.3 ATLAS                                                       |     |

| 1.3.1 The Inner Detector (ID)                                   |     |

| 1.3.1.1 The Pixel detector                                      |     |

| 1.3.1.2 SCT (SemiConductor Tracker)                             | 9   |

| 1.3.1.3 Transition Radiation Tracker (TRT)                      |     |

| 1.3.2 Central Solenoid magnet (CS)                              |     |

| 1.3.3 Calorimeters                                              |     |

| 1.3.3.1 Liquid Argon Electromagnetic calorimeter (LAr EM)       |     |

| 1.3.3.2 Hadronic calorimeters                                   |     |

| 1.3.4 Muon system                                               |     |

| 1.3.4.1 Toroid muon magnet system                               |     |

| 1.3.4.2 Muon spectrometer                                       |     |

| 1.3.5 Triggers, Dataaqusition and Detector Control System (DCS) |     |

| Chapter 2: Theory                                               |     |

| 2.1 The Standard Model                                          |     |

| 2.2 Fundamental particles                                       | 16  |

| 2.2.1 Quarks                                                    |     |

| 2.2.2. Leptons                                                  | 17  |

| 2.3 The fundamental forces                                      |     |

| 2.3.1 The strong force                                          | 18  |

| 2.3.2 The electromagnetic force                                 |     |

| 2.3.3 The weak force                                            |     |

| 2.3.4 Electroweak unification.                                  | 21  |

| 2.4 The Higgs model                                             | 22  |

| 2.4.1 Higgs production/detection in ATLAS                       |     |

| 2.5 Open questions                                              |     |

| 2.5.1 Physics beyond the standard model                         |     |

| 2.5.2 Extra dimensions                                          |     |

| 2.5.3 Other questions                                           | 25  |

| Chapter 3: The SCT barrel module                                |     |

| 3.1 Silicon Strip Detectors                                     | 27  |

| 3.1.1 Semiconductors                                            | 28  |

| 3.1.2 Band theory of solids                                     | 28  |

| 3.1.3 p- and n-type semiconductors                              |     |

| 3.1.4 p - n junction                                            |     |

| 3.1.5 Silicon as a semiconductor                                |     |

| 3.1.6 Operational principle of silicon strip detectors          | 30  |

| 3.2 Baseboard                                                   |     |

| 3.3 Hybrid                                                      | 33  |

| 3.4 Front-end electronics                                                      | 34  |

|--------------------------------------------------------------------------------|-----|

| 3.4.1 The ABCD3T ASIC                                                          |     |

| 3.4.2 Command and clock reception for ASICS                                    | 36  |

| 3.4.3 Addressing scheme                                                        |     |

| 3.4.4 Signal flow                                                              |     |

| 3.4.5 Data routing on hybrid                                                   | 40  |

| 3.4.6 Readout protocol                                                         |     |

| 3.4.7 Control protocol                                                         |     |

| 3.4.8 Chip startup sequence                                                    | 44  |

| 3.4.9 Power requirements                                                       |     |

| Chapter 4: The setup                                                           | 45  |

| 4.1 Environmental chamber                                                      | 45  |

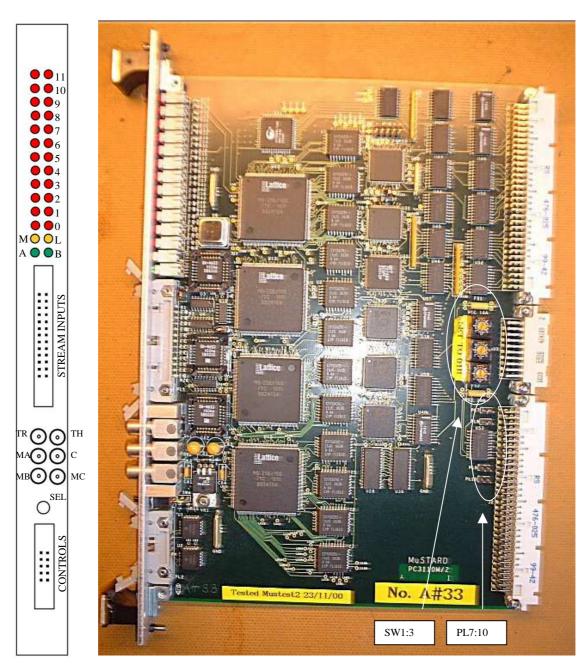

| 4.2 The VME system                                                             | 47  |

| 4.3 CLOAC                                                                      |     |

| 4.4 SLOG (SLOw command Generator)                                              | 53  |

| 4.5 MuSTARD                                                                    | 56  |

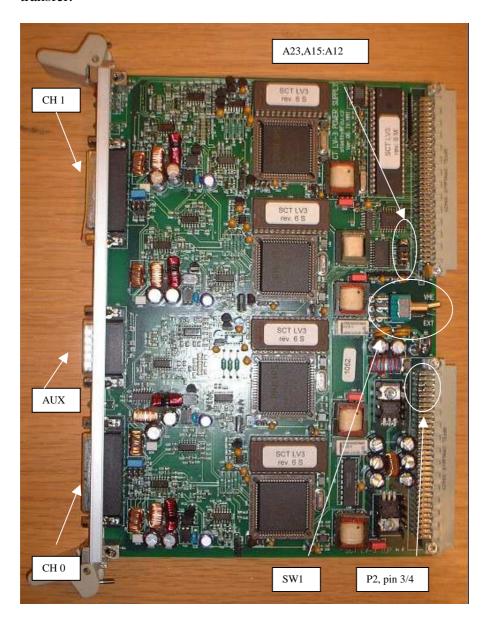

| 4.6 SCT-LV3                                                                    | 58  |

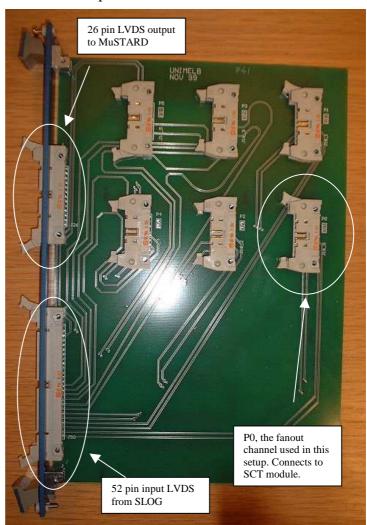

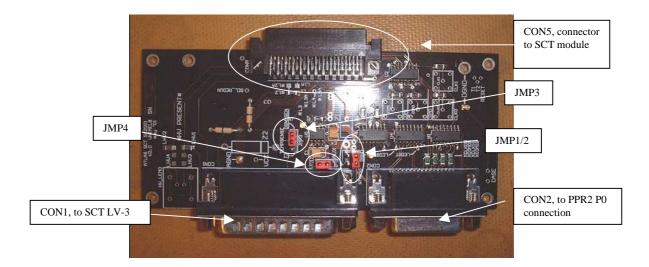

| 4.7 Patch Panel Replacer (PPR2)                                                | 61  |

| 4.8 Support card SC2001                                                        |     |

| 4.9 Windows NT computer running SCTDAQ                                         |     |

| 4.9.1 ROOT                                                                     |     |

| 4.9.2 Download/configuration of SCTDAQ                                         | 63  |

| 4.9.3 The SCTDAQ configuration files                                           |     |

| Chapter 5: The SCTDAQ software                                                 | 66  |

| 5.1 Overview                                                                   | 66  |

| 5.2 Example of operational principle: Changing the threshold of the SCT module | 68  |

| 5.3 Scans                                                                      | 70  |

| 5.3.1 Operational principle of scans                                           | 71  |

| 5.3.2 S-curves                                                                 |     |

| 5.3.3 Fitting of scans                                                         | 75  |

| 5.4 The macros used for electrical testing                                     | 76  |

| 5.4.1 Characterisation Sequence and Confirmation Sequence                      | 76  |

| 5.4.2 Results- and plot files                                                  | 77  |

| 5.4.3 Digital tests macros                                                     |     |

| 5.4.4 Analogue tests                                                           | 79  |

| 5.4.5 Pass/Fail criteria for electrical tests                                  | 93  |

| Chapter 6: Noise reduction in the setup                                        | 94  |

| 6.1 Noise from low voltage power supply (SCT-LV3 VME module)                   | 94  |

| 6.1.1 LV3 filter measurements                                                  | 98  |

| 6.1.2 Using two filters in serial connection                                   | 103 |

| 6.1.3 LV3 filter conclusions                                                   | 104 |

| 6.2 Noise from environmental chamber                                           | 105 |

| 6.2.1 Loss of communications due to relay switching                            | 105 |

| 6.2.2 Noise occupancy spike problem                                            | 108 |

| 6.3 Grounding of system                                                        | 113 |

| · · · · · · · · · · · · · · · · · · ·                                          | 114 |

| Chapter 7: QA procedures for the SCT barrel module           | 115 |

|--------------------------------------------------------------|-----|

| 7.1 QA of module parts                                       | 115 |

| 7.2 QA of completed module                                   |     |

| 7.2.1 Metrology                                              | 116 |

| 7.2.2 IV-curve/visual inspection                             |     |

| 7.2.3 Electrical testing                                     |     |

| 7.2.4 Thermal cycling                                        | 118 |

| 7.2.5 Cold long-term stability test                          |     |

| 7.2.6 Data examination                                       |     |

| 7.2.7 SCT Database/Web publishing                            |     |

| 7.3 Estimated time for QA                                    | 119 |

| Chapter 8: Oscillations in s-curves                          | 122 |

| 8.1 Characterisations in Bergen and Uppsala                  | 122 |

| 8.2 Oscillations with respect to different grounding schemes | 123 |

| 8.3 Temperature dependence                                   |     |

| 8.4 Oscillations versus input charge                         |     |

| 8.5 Power                                                    |     |

| 8.6 Crosschecks at Cambridge, RAL and CERN                   | 129 |

| 8.7 Oscillations conclusion                                  |     |

| Conclusion                                                   |     |

| References                                                   |     |

## **Chapter 1: Introduction to LHC and ATLAS**

### **1.1 CERN**

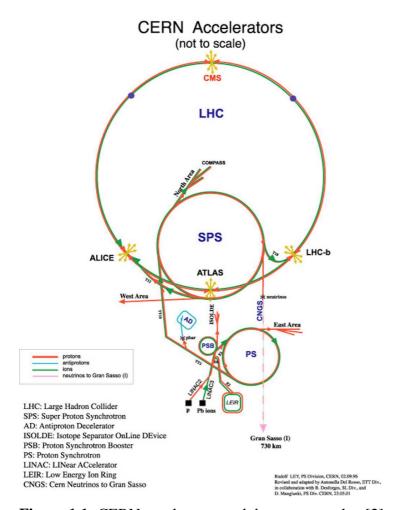

CERN (*Centre Européenne pour la Recherche Nucléaire/ European Organization for Nuclear Research*) is the world's largest particle physics centre, and is a collaboration between 20 European member states. It is situated approximately 10 km outside Geneva, on the border between France and Switzerland.

CERN was founded in 1953 by twelve founder states. A lot of questions in particle physics remained at the time unresolved, and the only way to get answers to these questions was to construct large particle accelerators for exploring the properties of matter at higher energies. CERN also had an important function as a unifying project for scientists from both sides of the recently ended World War 2.

Today, research at CERN is still mainly targeted at sub-nuclear physics, and the 6500 scientists working with CERN come from countries all over the world; USA, Japan, Canada, Russia, China, Israel and many more. This is over half of the particle physicists in the world, representing 500 universities and 80 nationalities.

CERN has housed a variety of detectors and accelerators since the start in 1953, and has always pushed the technology barrier forward. One of the first accelerators at CERN was the PS (*Proton Synchrotron*). It accelerated and provided protons for fixed target experiments at a beam energy of 26 GeV. The PS was later used as a part of SPS (*Super Proton Synchrotron*), completed in 1981, with a centre of mass energy up to 900 GeV. This was sufficient to give experimental evidence of the postulated W and Z bosons of the weak interaction, and is considered to be one of CERN's major accomplishments.

The most recent major accelerator operated at CERN is the LEP (Large Electron Positron collider). The planning of LEP started in 1977, and used e<sup>+</sup>e<sup>-</sup> as collision particles. The reason for choosing these particles was to be able to do further studies of the weak interaction, especially the Z boson. Since the electron and positron are very light particles, 0.511 MeV/c<sup>2</sup>, high beam energy was needed to reach the mass of the Z boson, 91.18 GeV/c<sup>2</sup>. Since a particle traveling in a circle emits energy inversely proportional to the radius of the circle, a large circular orbit was needed not to lose too much energy. For this purpose, a circular tunnel, 3.8 m wide and 27 km long, was drilled 100 m underground, see figure 1.1. Like the PS was used as part of the SPS, SPS (and thus PS) was used in LEP as particle injectors.

During the years of operation, the centre of mass energy was increased from 91 to 209 GeV (referred to as LEP-II), which made it possible to search for additional particles with higher mass. No such particles were found, and this is part of the motivation for building even larger accelerators. [1]

Figure 1.1: CERN accelerator- and detector complex [2]

## **1.2 LHC**

While LEP and LEP-II delivered important data, the energy limit of 209 GeV was not sufficient to test all the predictions of the Standard Model (see chapter 2), and no new particles were found in the energy range.

The need for even higher centre of mass energies to search for new or theoretically predicted particles, is the motivation for building the Large Hadron Collider (LHC), the next large accelerator at CERN, planned for completion in 2007. It will be installed in the 27 km LEP ring, with SPS as a preaccelerator, and will be a proton-proton collider with

centre of mass energy 14 TeV, 7 TeV for each proton beam. The luminosity will be  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, with beam crossings 25 ns apart. Each beam will contain 2835 bunches, with  $1 \times 10^{11}$  protons in each bunch.

LHC can also operate as an ion collider, using Pb beams with a centre of mass energy up to 1250 TeV, about thirthy times higher than the highest energy reached previously in any accelerator.

The LHC project features four detectors at various points in the accelerator (see figure 1.1):

- ATLAS, A Toroidal Large hadron ApparatuS: High luminosity general purpose proton-proton detector.

- CMS, *Compact Muon Solenoid*: High luminosity general purpose proton-proton detector, designed to provide particularly effective muon detection.

- ALICE, A Large Ion Collider Experiment: Ion-ion detector.

- LHC-B: Detector designed for studying B-physics.

To bend the proton beam around the ring, a strong magnetic field is needed. For this, 1296 superconducting dipole magnets operated at temperature 1.9 K, producing a field of 8.38 T will be used. A crossectional view of the ring, containing the two beampipes surrounded by the superconducting dipole magnets as well as cooling and shielding fascilities can be seen in figure 1.2.

For focusing the beam, 56 superconducting quadrupole magnets also operated at T=1.9 K is used. These are the magnetic equivalent of an optical lens, preventing the beam from spreading. The peak value of the field in the quadrupole magnets is 6.86 T.

Acceleration of the beam is done by 8 superconducting RF cavities placed in one of the straight sections of the ring. These create an accelerating field of 5 MV/m. The strong field will enable the protons to reach a speed of 9.71 km/h below that of light in vacuum, which means that a proton runs through the LHC ring in 88.924  $\mu sec$ , also referred to as the LHC beam crossing rate of 11.2456 kHz.

The cooling system for the superconducting elements is based on super-fluid helium, which has very efficient heat transfer properties. [3]

\_

<sup>&</sup>lt;sup>1</sup> Luminosity is defined as  $L = \frac{f \cdot n \cdot k^2}{A}$ , where f = frequency of circulation , n = number of bunches, k

<sup>=</sup> particles per bunch and A = cross-sectional area of bunch

## LHC DIPOLE: STANDARD CROSS-SECTION ALIGNMENT TARGET MAIN QUADRIPOLE BUS-BARS EAT EXCHANGER PIPE SUPERINSULATION SUPERCONDUCTING COILS BEAM PIPE VACUUM VESSEL BEAM SCREEN AUXILIARY BUS-BARS SHRINKING CYLINDER / HE I-VESSEL THERMAL SHIELD (55 to 75K) NON-MAGNETIC COLLARS IRON YOKE (COLD MASS, 1.9K) DIPOLE BUS-BARS SUPPORT POST

## Figure 1.2: Cross-section of LHC beam pipes [2]

## 1.2.1. Proton-proton collisions at the LHC

The data from LEP gave a very detailed picture of the fundamental particles and their interactions. From the data it is possible to see traces of higher energy physics, and from this extrapolate to which energies is needed to reach the domain of "new physics". It is believed that this area lays around 1 TeV, so LHC must be able to deliver beams that match this energy. To achieve this, the LHC uses proton-proton collisions with a centre of mass energy 14 TeV.

In most cases, the collisions between protons will be *soft collisions;* large-distance collisions with small momentum transfers. These collisions will dominate, with an event rate of  $\sim 10^9$  events/s, corresponding to 23 interactions creating 1000 particles at each bunch crossing, but will not be interesting. The interesting collisions will be those of single quark-quark/quark-gluon interactions, known as *hard scattering*, characterized by a large momentum transfer  $Q^2$ , giving rise to production of massive particles with high transverse momentum  $p_T$ . These will however have an event rate of only 1-10 events in  $10^8$  events, which means that selecting and extracting these events from all the uninteresting events (known as *pile-up*) will be a formidable challenge. [4]

Since the colliding quarks/gluons, also referred to as partons, only carry a fraction of the protons total momenta, this is the reason for the total centre of mass energy to be higher (14 TeV) than the energy needed for reaching the domain of 'new physics' (1 TeV).

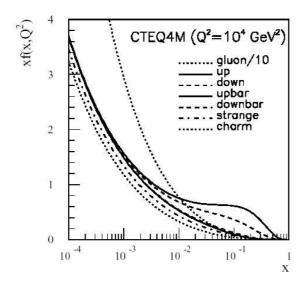

The fraction of the momentum a parton carries is referred to as x, also called *Bjorken* scaling variable. The probability of finding a parton carrying this fraction x is given by a Parton Distribution Function (PDF),  $f(Q^2,x)$ , depending both on x and the momentum exchange  $Q^2$ .

An example of such a function is shown in figure 1.3, at a large momentum transfer. We see that the probability of finding one parton carrying a significant part of the total momentum is small, and that the probability is shifted towards small x, which means that the sea-quarks carry a significant part of the momentum. For small  $Q^2$ , x is shifted towards  $\sim 1/3$ , meaning that the momentum is mainly carried by the three valence quarks.

**Figure 1.3:** Parton distribution function of the proton for momentum transfer 100 GeV. [4]

## **1.3 ATLAS**

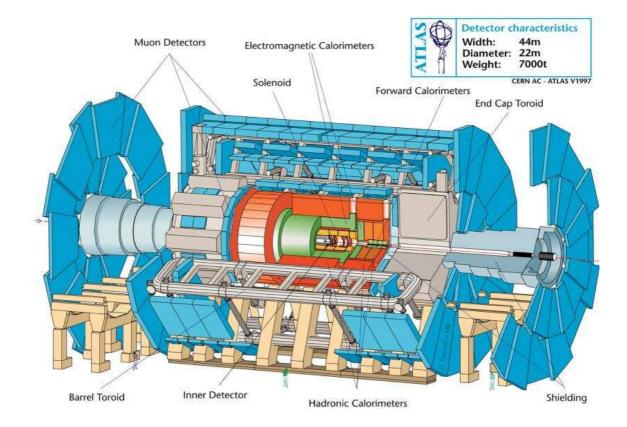

ATLAS (A Toroidal Large hadron collider ApparatuS) is a general purpose proton-proton detector. It is the physically largest detector in the LHC, and is also the largest collaborative effort ever attempted in the physical sciences, with 2000 scientists from more than 150 universities and 34 countries working together on the project. Figure 1.4 shows the ATLAS detector.

**Figure 1.4:** The ATLAS detector. [2]

Installation is expected to start in 2003, and the first run is scheduled to the start of 2007. Since ATLAS is a general purpose detector, it is designed to exploit the full potential of the LHC; it provides detection of leptons, hadrons, photons and neutrinos, featuring very precise tracking abilities and energy measurements.

ATLAS is divided into four major parts, each one described in the following sections:

- **Inner detector (ID)** tracks and measures the momentum of charged particles.

- **Calorimeter** measures the energy of electrons, photons and hadrons.

- Magnet systems bending charged particles for momentum and mass measurement.

- **Muon spectrometer** identifies and measures muons.

ATLAS will also feature a highly efficient trigger system to select the small number of interesting events from the large total number of events.

The coordinate system in ATLAS uses these axis and reference points:

- Origo placed at collision point (detector centre).

- X-axis horizontal, pointing towards the centre of the LHC-ring.

- Y-axis pointing upwards.

- Z-axis alligned with beam pipe so that it forms a right-handed coordinate system together with the X and Y axis.

- $\phi$  azimuthal angle measured around the beam axis.

- $\theta$  polar angle relative to the beam axis.

- $\eta = -\ln (\tan \theta/2)$ . This is known as the *pseudo-rapidity angle*.

- r distance from the collision point.

## 1.3.1 The Inner Detector (ID)

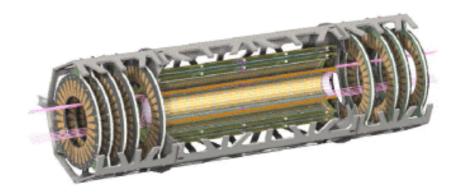

The inner detector is a tracking detector located closest to the interaction point in ATLAS. Its task is to reconstruct tracks and vertices of charged particles produced at the interaction point, as well as supplying the signature for short lived particles. The ID is situated in a solenoidal superconducting magnet system with a field of 2 T directed along the beam axis. This will cause the charged particles to bend, and based on the bending, the momenta of the particles can be determined with great precision.

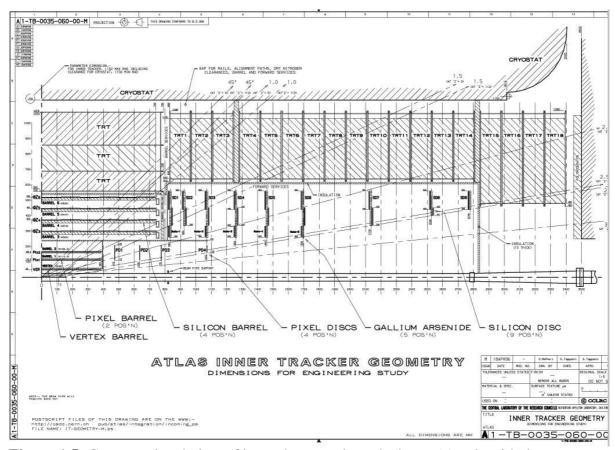

**Figure 1.5:** Cross-sectional view of inner detector along the beam (z)-axis with the interaction point down to the left.

The ID has a total length of 7 m and an outer radius of 115 cm, constrained by the cryostat containing the central solenoid manget (CS), and the liquid argon

electromagnetic calorimeter (LAr EM). It is divided into a barrel part covering  $/\eta/<1$  and a forward/end-cap part covering  $/\eta/<2.5$ .

The inner detector consists of three detector subsystems:

- The pixel detector

- The silicon strip detector (SCT)

- The transition radiation tracker (TRT)

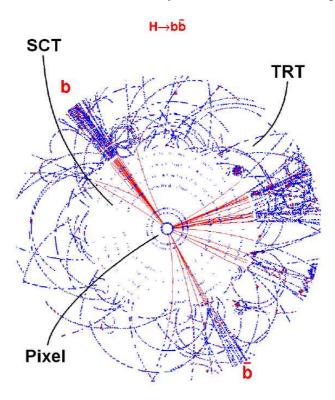

The track density and the radiation near the interaction point will be very high, so for the two innermost layers of the ID, semiconductor tracking devices have been chosen for detectors. They offer high resolution, and after an extensive development program they also offer high durability in the harsh radiation environment. The third layer of the ID is a straw detector, which offers tracking at lower granularity, but also at a much lower costs. Together, the three systems provides very robust tracking and pattern recognition abilities. Figure 1.6 shows a simulated event in the ID, demonstrating how the various parts of the inner detector will see the particles. The curving of the particle tracks is due to the 2T field in the inner detector, created by the central solenoid magnet.

**Figure 1.6:** Simulated event in inner detector.

#### 1.3.1.1 The Pixel detector

The pixel detector is the innermost layer in the detector, designed to provide a very high-granularity and high-precision set of measurements, as close to the interaction point as

possible. One of the important tasks of the inner detector is to discover signatures of short-lived particles such as B-mesons and tau leptons, important for finding traces of the Higgs boson. For this, very high resolution is needed.

The system consists of 140 million cells distributed over three barrel layers and eight forward discs, providing a minimum of three precision measurements over the full acceptance. It covers  $/\eta/<2.5$ , and the resolution is 12  $\mu$ m in the R $\phi$  plane and 66  $\mu$ m in the z plane, achieved by 50x300  $\mu$ m pixel cells of n+ type technology. The pixels are arranged in modules, with the entire system consisting of 1500 barrel modules and 1000 endcap modules. Tracks can be distinguished if separated by more than ~200  $\mu$ m.

Figure 1.7 shows the pixel detector, with the three barrels placed at approximately at r=4 cm, 10 cm and 13 cm, and the endcaps covering the radius 11 to 20 cm.

**Figure 1.7:** ATLAS Pixel detector

The radiation close to the interaction point is very high, estimated to 300 kGy of ionizing radiation, and over  $5x10^4$  neutrons/cm<sup>2</sup> over the ten years of operation, and for this reason, the innermost barrel is designed for replacement. It is expected to have a lifetime of three years at reduced luminosity, and one year at full luminosity.

Chips reading 24x160 pixels each do the electrical readout of the pixels. These provide functions for buffering readout in case of an L1 trigger, with individual circuitry for each pixel element. [5]

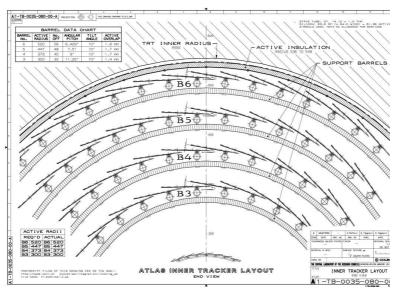

## 1.3.1.2 SCT (SemiConductor Tracker)

The semiconductor tracker is the next layer in the detector. It operates at a lower resolution than the pixel detector, but was chosen because of the lower cost, and also because of the reduced need for resolution due to multiple scattering from the inner layers of the detector. The SCT is built from modules of siliconstrip detectors, see chapter 3 for a detailed description. The modules are assembled in 4 cylindrical central barrels at r=30.0, 37.3, 44.7 and 52.0 cm, in addition to 9 forward and 9 backwards disks, giving a

total sensitive area of 61 m<sup>2</sup> and 6.2 million readout channels. The SCT also covers  $|\eta|$ <2.5, and the spatial resolution is 16  $\mu$ m in the R $\phi$  plane and 580  $\mu$ m in z.

The SCT is built from two types of modules, endcap modules and barrel modules, with a total of 2856 modules required for the four barrel layers.

**Figure 1.8:** Crossectional view of SCT barrel down the z-axis, showing the alignment of the SCT barrel modules.

Both the electronics on the module and the detector strips will produce significant heat, so cooling of the modules is an important issue. Defects due to irradiation have also shown strong temperature dependence, so the SCT and pixel detector will share a nitrogen atmosphere of -7 °C. A cooling system based on cooling pipes containing perfluorinated propane ( $C_3F_8$ ) kept at -14 °C will also be used. The pipes will be connected to each module to remove heat generated by the electronics and detecor leakage current. [6]

## 1.3.1.3 Transition Radiation Tracker (TRT)

The TRT surrounds the pixel and the strip detectors, and consists of 372 032 4 mm - diameter tubes of maximum length 150 cm, filled with gas (70 % Xe, 20% CF<sub>4</sub> and 10 % CO<sub>2</sub>), with a 30  $\mu$ m thick wire running through each tube. The TRT is, like the SCT and PIXEL detectors, divided in a barrel and endcap part, covering  $/\eta$ /<2.5 (see figure 1.5). The barrel covers the radius between r=56 and 107 cm, and the endcap r=64-103 cm. In the barrel, the tubes are placed parallel to the beam, and in the end-cap region perpendicular.

In each tube, a high voltage is maintained between the tube wall and the wire, so that when a particle traverses a tube, it produces a discharge, and a hit is detected. Through accurate timing of the discharge, it is also determined how far from the wire the particle passed. Each particle will on average hit 36 straws (see figure 1.6), and the points will together with the Pixel and SCT detector help reconstruct tracks at high resolution to determine momentum very precisely. The effective resolution of TRT will be  $50 \, \mu m$ .

The detector features two different thresholds, one for particles hits (low threshold) and one for transition-radiation hits (high threshold). Transition radiation is radiation in the X-ray region that arises when ultra relativistic particles cross a boundary between two media with different dielectric constants. In the end caps, the transition radiation is created by placing stacks of 12 15  $\mu$ m thick polypropylene foils (radiators) between each straw layer. In the barrel region, where space is a critical issue, the radiator will be put into all available space around the straws as sheets of loosely packed fibres with diameter 15  $\mu$ m, made of polypropylene/polyethylene.[7]

## 1.3.2 Central Solenoid magnet (CS)

The next layer in the detector is the solenoid magnet. This is a superconducting magnet kept at T=4.5 K, sharing cryostat with the EM calorimeter. The magnet is 5.3 m long, creating a field of 2 T at the interation point, dropping to 0.5 T at the end of the ID. Since the CS is placed in front of the LAr EM, the material use is minimised to optimise calorimeter performance.

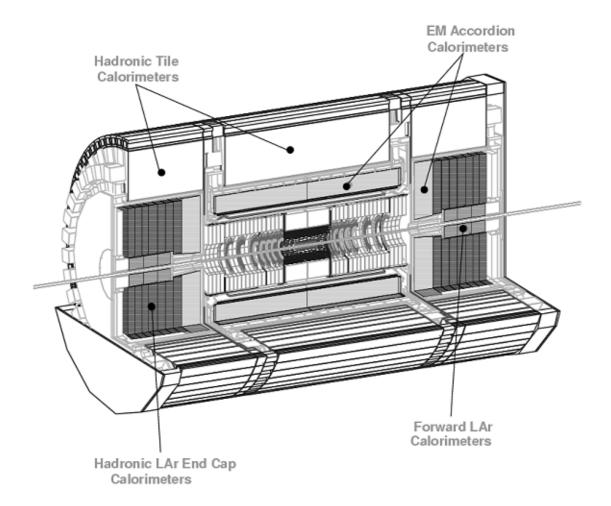

#### 1.3.3 Calorimeters

ATLAS features two calorimeters, whose purpose is to absorb particles to measure their energy:

- Liquid Argon Electromagnetic (LAr EM) calorimeter

- Hadronic calorimeter

## 1.3.3.1 Liquid Argon Electromagnetic calorimeter (LAr EM)

The first calorimeter, the *LAr EM calorimeter*, is designed to absorb light electromagnetically interacting particles;  $e^{\pm}$  and photons. It consists of an inner barrel cylinder and two end caps, covering  $/\eta/<3.2$ . On figure 1.9, the EM calorimeter is shown together with the other calorimeters of ATLAS. On the figure, the detector part of the EM cal. is marked as 'accordion calorimeters', reffering to the accordeon-like structure of the lead/liquid argon layers. When electrons and photons interact with the lead, which has a short radiation length, particle showers are created. These showers ionize the argon, in which the signal from the ionisation is picked up. The measurements are done in three samples, in addition to a presample done between the CS and the cryostat wall for energy loss adjustment due to the ID, solenoid and cryostat.

#### 1.3.3.2 Hadronic calorimeters

The *Hadronic calorimeters* is designed to absorb hadrons (particles made from quarks), covering  $/\eta/<4.9$ . It consists of three parts; Hadronic Tile, Hadronic LAr and Forward LAr, see figure 1.9. The tile part is built from sandwiched layers of iron and scintillator, with iron as the passive (absorber) material in which the hadronic particles shower develops. The scintillators are the active sampling layers measuring ionization from the particle showers.

Figure 1.9: ATLAS calorimeters

The hadronic tile calorimeter covers r=228.0 to r=423.0 cm, and the region  $0.8 < |\eta| < 1.7$ . Its total length in z direction is 1266.0 cm.

The Hadronic LAr End Cap Calorimeters has an outer radius of 2.03 m, covers  $1.5 < |\eta| < 3.2$  and uses much of the same technology as the EM LAr calorimeter. The forward LAr Calorimeters covers  $3.1 < |\eta| < 4.9$ , built of copper and tungsten. This part of

the calorimeter will operate under high radiation because of the small angle soft collisions from the majority of interactions.[5]

By comparing the total amount of energy measured with the centre of mass collision energy, one can find  $E_T^{miss}$ , the missing energy. This is due to neutrinos (see chapter 2), not directly observable in the detector. By determination of  $E_T^{miss}$ , the neutrinos in a process can be indirectly detected.

## 1.3.4 Muon system

Muons and neutrinos are the only particles that escape through the calorimeter. Since the muon has ~200 times the mass of the electron, the cross section for bremhsstrahlung is much smaller than for the electron, and muons mostly escape the calorimeter. They also have long enough lifetime to reach outside the calorimeter, in contrast to the heavier tau lepton, which has a much shorter lifetime. A separate muon detection system is thus needed.

## 1.3.4.1 Toroid muon magnet system

The barrel and endcap muon magnets create a toroidal magnetic field of approximately 4 T, consisting of 8 flat 25 x 5 m coils for the barrel part, and two 11 m high and 5 m thick endcaps, see figure 1.10. The magnets are superconducting, kept at a temperature 4.2-4.5 K. The toroids have air cores, to minimize scattering, and have also integrated cryogenics.

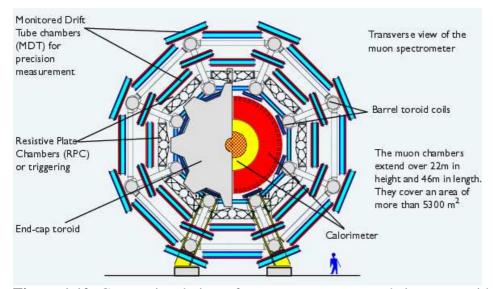

## 1.3.4.2 Muon spectrometer

The muon detector is the outermost layer in ATLAS, 26 m long with inner radius of 9.4 m and outer radius of 19.5 m. The deflection of the muon in the magnetic field is measured to identify the momenta and energy of the muons. The spectrometer covers  $|\eta|$ <2.5 and has a total area of 5300 m<sup>2</sup>, and can be divided into two functional parts; trigger chambers and precision chambers [5] also see figure 1.10).

The trigger chambers are used by the triggering system to detect interesting events based upon high  $p_T$ , see the next section. They provide a low resolution, ~1 cm, but very fast readout, <25 ns, to uniquely identify bunch crossings. The technology used is Resistive Plate Chambers for the barrel part, and Thin Gap Chambers for the end cap parts.

**Figure 1.10:** Crossectional view of muon spectrometer and air-core toroid magnet system.

The precision chambers provide a resolution of down to  $60 \,\mu\text{m}$ , but with a drifttime up to  $500 \, \text{ns}$ . The technology used is Monitored Drift-Tube chambers and Cathode Strip Chambers.

## 1.3.5 Triggers, Dataaqusition and Detector Control System (DCS)

With a beamcrossing rate of 40 MHz, one bunch each 25 ns, and 20-25 interactions per crossing, there will ~ $10^9$  events per second at the interaction point in ATLAS. On average, 1000 particles traverses the pseudo-rapidity region of  $|\eta|$ <2.5 at each bunch crossing (see section 1.2.1.) A data amount of 7 Tb per second would be generated if all events were to be recorded, which is far too much to store. This means that ATLAS must have some kind of criteria for selecting the interesting events, which should occur 10-100 times per second. The large amount of uninteresting events is known as *pile-up*, or *minimum bias events*, characterised by a low  $p_T$ .

The interesting events will be selected through very rapid analysis, using various criteria for tagging an event as interesting. The trigger system is divided in three levels, with each level examining a larger dataset. The first trigger, the level 1 (L1) trigger, has a decision time of 2.0  $\mu$ s, based on data from the calorimeters and dedicated trigger chambers in the muon spectrometer using high p<sub>T</sub> muons, electrons, photons, hadrons and jets as well as large  $E_T^{miss}$ , as indications of intersting events. The L1 trigger is designed to be a conservative trigging system, i.e. it should select *all* potentially interesting events, which means that it also selects a lot of eventually uninteresting events. Because of the decision time of L1, all data from the detectors must be kept in pipelines long enough for a L1 decision to be taken. The L1 is very fast, analyzing several Tbits/s, and should create a maximal L1 trigger rate of ~75 kHz, which is the highest rate the ATLAS front-end

systems can accept. This is upgradable to 100 kHz. All data from all detectors are kept in pipeline memories long enough for a L1 trigger to arrive. [5]

After L1, there is L2 analyzing, which focuses on region of interests marked by the L1 trigger. L2 has a decision time of <10 ms, and is followed by the L3 trigger which reconstructs the detector data and sends it to storage.

**Figure 1.11:** Event after L1 trigger cutoff due to high p<sub>T</sub> []

ATLAS will also use a sophisticated *Detector Control System* (DCS). The systems needs to monitor approximately 100 000 parameters of detector operation like currents, temperatures, humidity and such, and present these to operators in a practical way.

Each year, ATLAS will produce a data volume of 1 Pbyte (10<sup>15</sup>) bytes, which needs to be analyzed. Distributed networking will become very important to enable physicists, independent of location, to access data and perform physics analysis. How this will be implemented, is still an issue under discussion, and will greatly depend on the evolution of networks in the years both before and during the run of ATLAS.

## **Chapter 2: Theory**

This chapter gives an overview of the theoretical foundations of particle physics.

## 2.1 The Standard Model

Our present understanding of particle physics is contained in a theoretical framework called the Standard Model (SM). The theory has been gradually developed for over half a century, and is today in excellent agreement with experimental data, both from LEP and a variety of other experiments.

## 2.2 Fundamental particles

According to the theory, there are 12 fundamental particles, divided into three 'generations':

| Family             | Leptons                                    |                                               | Quarks                                       |                                        |  |

|--------------------|--------------------------------------------|-----------------------------------------------|----------------------------------------------|----------------------------------------|--|

| Spin               | 1/2                                        | !                                             | 1/2                                          |                                        |  |

| Electric<br>Charge | -1                                         | 0                                             | 2/3                                          | -1/3                                   |  |

| 1.generation       | e<br>Electron<br>m <sub>e</sub> =0.511 MeV | <b>V</b> <sub>e</sub> Electr. neutrino m<3 eV | <b>u</b><br>m <sub>u</sub> =1-5 MeV          | <b>d</b><br>m <sub>d</sub> =3-9 MeV    |  |

| 2.generation       | μ<br>Muon<br>m <sub>u</sub> =105.6 Mev     | ν <sub>μ</sub><br>Muon neutrino<br>m<0.19 MeV | <b>c</b><br>m <sub>c</sub> =75-170 MeV       | <b>S</b> m <sub>s</sub> =1.15-1.35 GeV |  |

| 3.generation       | τ<br>Tauon<br>m <sub>τ</sub> =1776.99 MeV  | ν <sub>τ</sub> Tauon neutrino m<18.2 MeV      | <b>t</b><br>m <sub>t</sub> =174.3±5.1<br>GeV | <b>b</b><br>m <sub>b</sub> =4-4.4 GeV  |  |

**Table 2.1:** Fundamental particles of the Standard Model [8]

For each fundamental particle, there exists an antiparticle with identical mass and spin, but with opposite charge. We say that particles are fundamental in the sense that they seem to occupy a single point in space and hence are point-like, also called local entities.

### **2.2.1 Quarks**

Quarks were first observed in 1968 at SLAC, as an indication of an inner structure in protons. Quarks exist in six *flavours*; *up*, *down*, *charm*, *strange*, *top* and *bottom* with corresponding anti-quarks. They are fermions, that is, they have an intrinsic spin of ½, and carry electric charge +(-)2/3 and -(+)1/3, thus interacting electromagnetically. The quarks also interact through the strong force, carrying a color charge. This charge exists in three different colors (anti-colors) red, green and blue, giving the quarks three additional degrees of freedom. The strong (color) force confines the quarks so that they create color-neutral objects, supported by the fact that a free quark has never been observed.

Particles composed of quarks are called hadrons, with particles made up from three quarks called baryons, and particles from one quark/anti-quark pair called mesons. The proton (u u d) and the neutron (u d d) are the only baryons found in nature, while the other baryons and the mesons are relatively short lived particles which eventually decays into stable particles. Whether the proton actually is stable or not, is still an unresolved issue, but it has been given a lower life time limit of  $1.6 \times 10^{25}$  years. [8]

## **2.2.2. Leptons**

Leptons are the other class of elementary particles. They are also fermions, and are, like the quarks, divided into three generations. The charged leptons are the electron, muon and tauon, carrying an electric charge of -1. The three particles couple with equal strength in electromagnetic interactions, known as *lepton universality*. The only difference between them is the mass, ranging from 0.5 MeV to 1710 MeV. It is a challenge of particle physics to try to find out why these masses are so different.

For each charged lepton, there is a corresponding *neutrino*. Until recently, the neutrinos were believed to be massless, but are now believed to have a small mass. Since they do not carry any charge, they interact with matter only through the weak force, and this, combined with their low mass, makes them very hard to detect.

## 2.3 The fundamental forces

The three forces described in the standard model are presented in table 2.2. Each force has its mediating particle, called *gauge bosons*, of integer spin. Gravity is also listed, although it is not yet, despite serious efforts, incorporated in the Standard Model. However, gravity is very weak at small scales, so it can be safely neglected.

One of the primary goals of particle physics is to unite all the four forces into one fundamental force, but so far, only the electromagnetic and weak force have been unified successfully. This was done in Electroweak theory (Salaam-Weinberg 1969), and is not

yet fully experimentally verified, since the Higgs boson is yet to be found (see section 2.4).

To each of the interactions, certain conservations laws apply. Some are conserved in all interactions:

- Energy (E)

- Momentum (*p*)

- Angular Momentum (*L*)

- Electrical charge

- Colour charge

- Baryon number (B)

- Lepton number  $(L_e, L_{\mu}, L_{\tau})$

Mathematically, the Standard Model is based on local relativistic quantum field theory, describing interactions due to the three forces with the theories QED, Electroweak Unification and QCD.

| Interaction          | Relative<br>strength                         | Range                | Mediating particle                                           | Charge of particle                     | Felt by                                                                              |

|----------------------|----------------------------------------------|----------------------|--------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------|

| Strong               | 1                                            | ~10 <sup>-15</sup> m | g (gluon)<br>Spin-1<br>m <sub>g</sub> =0                     | 1 of 8 color<br>charge<br>combinations | Quarks and gluons.                                                                   |

| Electro-<br>magnetic | ~10-2                                        | 1/r <sup>2</sup>     | γ ( <b>photon</b> )<br>Spin-1<br>m <sub>γ</sub> =0           | 0                                      | All particles carrying electric charge.                                              |

| Weak                 | at 10 <sup>-18</sup> m:<br>~10 <sup>-2</sup> | ~10 <sup>-18</sup> m | W <sup>±</sup><br>Spin-1<br>m <sub>W</sub> =80.4 GeV         | Electric charge: ± 1                   | Left-handed<br>particles, right<br>handed anti-<br>particles.                        |

|                      | at 10 <sup>-17</sup> m:<br>~10 <sup>-6</sup> |                      | <b>Z</b> <sup>0</sup><br>Spin-1<br>m <sub>Z</sub> =91.18 GeV | 0                                      | Left-handed<br>and right-<br>handed<br>particles, but<br>with different<br>strength. |

| Gravity              | ~10 <sup>-43</sup>                           | 1/r <sup>2</sup>     | Graviton<br>Spin-2<br>m <sub>G</sub> =0                      | 0                                      | Massive particles.                                                                   |

**Table 2.2:** The three fundamental forces in the Standard Model + Gravity. [9]

## 2.3.1 The strong force

The strong force is the force responsible for holding the nucleus and hadrons together, and must thus be stronger than the repulsive force due to the electromagnetic interactions between the positively charged protons in the nucleus.

The mediating particle of the strong force is the massless *gluon*, which can carry one of eight different color combinations of the colors red, green and blue.

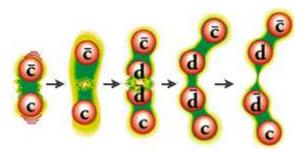

The strong force does not fall off with distance, but is rather believed to be proportional to *r*. This means that when two quarks move away from each other, the field between them, also called a *colour tube*, grows stronger. This is due to the fact that gluons carry colour charge and can thus couple to other gluons. Before the quarks are separated at an observable distance, the energy contained in the field between them reaches the pair-production energy, creating an additional quark/antiquark pair. This phenomenon is known as quark confinement, preventing single quarks from existing and always creating colour neutral objects, see figure 2.1.

**Figure 2.1:** Confinement of quarks due to strong force.

The interactions due to the strong force are described in the gauge theory known as Quantum ChromoDynamics (QCD). The quarks are symmetric under exchange of the three colours, which results in an SU(3) symmetric theory. The theory also only applies at very high energies, where the quarks can be considered as free particles.

## 2.3.2 The electromagnetic force

The field quantum of the electromagnetic force is the photon, being massless and carrying no charge. Because of this massless and chargeless nature of the photon, it has infinite range, while the strength of the force goes like  $1/r^2$ .

Photons couple to particles carrying electric charge. The nature of the electromagnetic force is believed to be fully understood, and is described in the theory Quantum Electrodynamics (QED), which has been very successful in describing a variety of phenomena. Due to the electromagnetic force only having one type of charge, the theory is a U(1) symmetric gauge theory, making the photon its own antiparticle.

#### 2.3.3 The weak force

While the EM force had infinite range due to the massless nature of the photon, the weak force has a very short range due to its heavy field quanta, the W<sup>±</sup> and Z<sup>0</sup> bosons. The Heisenberg uncertainty relation  $\Delta E \Delta t \ge \hbar$  limits the effective range of the weak force to ~10<sup>-18</sup> m.

The charged currents of the weak force,  $W^\pm$ , only couples to left-handed particles or right-handed anti-particles. A left-handed particle has its spin in the opposite direction of its momentum (negative helicity). All massive particles have both a positive and negative helicity component, but since these can be of significantly different magnitude, we can say that for the weak force, P (spatial inversion)-parity is not conserved (since this inverts the helicity, making a left-handed particle a right-handed particle and opposite).

For the charged currents, this violation is maximal, but for  $Z^0$  only partial, since  $Z^0$  couples to both left- and right-handed particles, but with different strength. The weak force is also C (charge) parity violating, since changing the charge of a particle turns it into its antiparticle, but keeps the helicity and thus changes the coupling to weak interactions. However, the combined CP-parity is conserved for most weak processes. The fact that not all weak processes obey the combined CP-parity, is not satisfactorily explained in the standard model, and is an area that is currently being studied, and also will be studied in LHC, in particular through the studies of B-mesons.

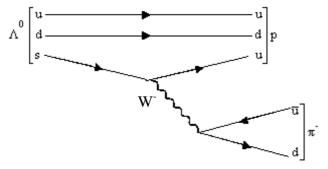

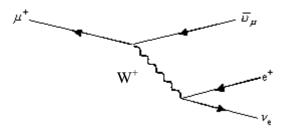

The weak force is also responsible for the decays of the heavier 2. and 3. generation particles, being the only force that can 'change' the type of a particle. Two examples are shown in the Feynman diagrams below.

**Figure 2.2:** Feynman diagram showing  $\Lambda^0 \rightarrow p + \pi^-$ .

Figure 2.2 shows an example of an  $\Lambda^0$  particle decaying into a proton and a  $\pi^-$  via a W boson. This is known as a *Flavour Changing Current*. In this case, an s quark changes to an u quark through emission of a W. This is a change across a generation, and is possible because the W bosons couple not to the mass eigenstates of the quarks, but to linear combinations of these, given by the *Cabibbo-Kobayashi-Maskawa (CKM)-matrix*. The Standard model forbids Flavour Changing Neutral Currents (FCNC), meaning no interactions in which the  $Z^0$  boson changes one quark to another.

For leptons, the question whether a lepton can change between different generations through charged currents, and thus violating the conservation of lepton number, is still an unresolved issue.

**Figure 2.3:**  $\mu^+ \rightarrow e^+ + \nu_e + \overline{\nu}_{\mu}$

Figure 2.3 shows the decay of a  $\mu^+$  into a muon antineutrino, a positron and an electron neutrino through the emission of a W<sup>+</sup> boson, also known as muon decay.

#### 2.3.4 Electroweak unification

In 1968, Salam and Weinberg showed that the electromagnetic and weak interactions could be understood as two aspects of the same interaction. They showed that one could, by introducing a new quantum number *weak isospin T*, group the left-handed (interacting through charged currents) fermions into isospin doublets with T=1/2, and right-handed fermions into isospin singlets with T=0. The doublet components could transform into each other via the weak interaction, obeying an SU(2) symmetry.

The gauge bosons have T=1, making it possible to group the  $W^\pm$  bosons into a triplet, postulating a third  $W^0$  boson with  $T_3=0$ . A singlet with T=0 was also needed, so a boson  $B^0$  with T=0 was postulated. The  $B^0$  gauge boson is connected with the quantum number hypercharge (a combination of isospin and electric charge), governed by a U(1) symmetry. It turns out that the real particles the photon and  $Z^0$  can be described as linear combinations of the theoretical particles  $W^0$  and  $B^0$ :

$$\left| \gamma \right\rangle = \cos \theta_{w} \left| B^{0} \right\rangle + \sin \theta_{w} \left| W^{0} \right\rangle$$

$$\left| Z^{0} \right\rangle = -\sin \theta_{w} \left| B^{0} \right\rangle + \cos \theta_{w} \left| W^{0} \right\rangle$$

$$(1)$$

This mixing is expressed as a rotation through the *electroweak mixing angle*  $\theta_W$ , also known as the *Weinberg angle*. This showed the connection between the weak- and the electromagnetic force, with the resulting theory being a SU(2)xU(1) symmetric theory.

## 2.4 The Higgs model

For the electroweak theory to be gauge invariant, the particles involved need to have zero mass, which is obviously not the case. To solve this problem, the concept of spontaneous symmetry breaking is introduced in the theory, requiring an asymmetric ground state with a non-vanishing vacuum expectation value.

The symmetry breaking gives rise to four scalar (spin 0) fields, which at first give us expressions that have no physical meaningful interpretations. However, three of these fields can be removed by local gauge transformation, which in turn gives masses to the weak gauge bosons.

Since spontaneous symmetry breaking requires a non-zero vacuum expectation value, the value is interpreted as a field being present all over space, with the leptons acquiring mass by interacting with this field through the *Yukawa-coupling*.

This leaves us with one of the initial four scalar fields left, interpreted as the scalar (spin=0) particle the *Higgs boson*. If this particle exists, it should be detectable in ATLAS, verifying the theory of how the particles acquire their masses, one of the most central and fundamental questions in particle physics.

## 2.4.1 Higgs production/detection in ATLAS

As discussed in the previous section, the Higgs mechanism provides an explanation for the particle masses, so if signs of the Higgs boson are detected in ATLAS, it will be a major success of the Standard Model. If it is not found, the explanation of mass will need to be revised. It is clear that this is an important issue of the theory, and has to be tested.

The Standard Model does not predict the mass of the Higgs boson, but the present lower limit from LEP is around 108 GeV. If the Higgs boson is not found at the Tevatron at Fermilab, the lower limit could be extended up to ~120 GeV. There is an upper theoretical limit of 1 TeV to preserve unitarity at high energy.

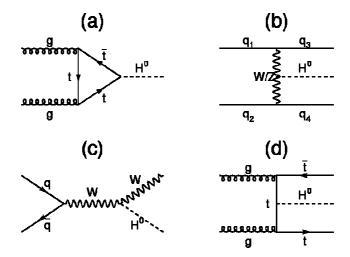

**Figure 2.4:** Feynman diagrams showing the most important Higgs production channels: a) Gluon fusion through top loop, b) Vector boson fusion, c) Associate production with W, d) Associate production with top pair.

Production of a Higgs boson will in LHC be dominated by gluon fusion, but other processes will also contribute. In figure 2.4, the four most important processes, valid for all realistic Higgs masses, are shown.

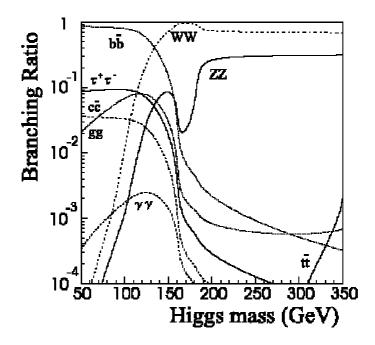

Although the production of Higgs does not depend on its mass  $m_H$ , the channels to which it can decay has a strong mass dependence. In figure 2.5, the expected total branching ratios of the Higgs boson is shown as a function of the Higgs mass.

**Figure 2.5:** Total Higgs decay branching ratios as function of the Higgs mass.[4]

The mass range is usually divided in three, each with its own dominant decay channels:

- $m_H < 120 \text{ GeV}$ : H → b b dominates, since b-quarks are the most massive fermions cinematically accessible in this region. However, the QCD background will be  $10^5$  larger, meaning it will be impossible to extract this signal from the background, so other channels will be experimentally more useful in the detection of the Higgs boson.

- $80 < m_H < 150 \text{ GeV}$ :  $H \rightarrow \gamma \gamma$ . This process is very rare, but provides very clean signatures, so it can be used for identifying a Higgs boson.

- 130 GeV<  $m_H$ < 2  $m_Z$ :  $H \to WW(*) \to lvlv$  and  $H \to ZZ(*) \to 4$  l dominates, where one of the vector bosons can be virtual.

- $m_H > 2 m_Z$ : WW and ZZ pairs dominate, both bosons real. This is the easiest region to discover the Higgs in, since the ZZ  $\rightarrow$  4 l gives a very clear signature, almost background free.

## 2.5 Open questions

The standard model is not a complete theory in the sense that it completely describes particle physics; there are still many open questions. 18 or more parameters, depending on the counting scheme, must be filled in the theory based on experimental values, and has no accepted or verified theoretical explanation. [10]

## 2.5.1 Physics beyond the standard model

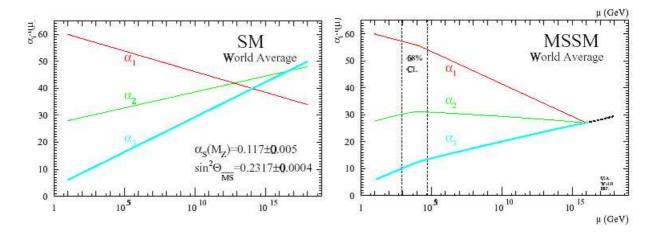

There are several arguments that point in the direction that the standard model is not the ultimate theory of particle interactions. Among these is the lacking physical justification of the Higgs field, and that the Standard model fails to unify the coupling constants of the three forces at high energies ( $\sim 10^{16}$  GeV). However, if the Standard Model is augmented with the concept of *SuperSYmmetry (SUSY)*, it succeeds in combining the three coupling constants, as shown on figure 2.5. This is referred to as *MSSM (minimal supersymmetric standard model)*.

**Figure 2.5:** Coupling constants of the EM, weak and strong forces as function of energy in SM and MSSM [4].

Supersymmetry predicts that each particle should have its SUSY partner, resulting in quarks/squarks, leptons/sleptons, with the fermion partners being bosons, and opposite. The masses of these partners have a lower experimental limit of 100 GeV (250 GeV for squarks/gluinos), and the decay modes, i.e. the patterns by which the SUSY particles can be discovered, will like the Higgs, depend on the unknown mass of the SUSY partners.

#### 2.5.2 Extra dimensions

There exists several theories using the concept extra dimensions. Some of these will be explored in ATLAS, for example the Randall-Sundrum scenario. The extra dimensions are introduced to solve the *hierarchy problem* of the Standard Model, the question why the forces are of so different scale, with a ratio  $10^{-43}$  between the strength of the strong force and gravity. The answer to this could be that gravity propagates through extra dimensions, not making all its force 'visible' for us.

## 2.5.3 Other questions

There are several other unresolved issues that will be subject to further investigation in ATLAS/LHC:

- *Are quarks and leptons really elementary particles?*

- Can gravity be incorporated in the Standard Model?

- Further insight in the nature of CP violation.

- *Are there more particle generations, and if not, why three?*

- How do the coupling constants evolve over the unprecedented range of energy?

We see that there are many open questions, and hopefully, some of the answers can be found from the data from LHC/ATLAS.

## **Chapter 3: The SCT barrel module**

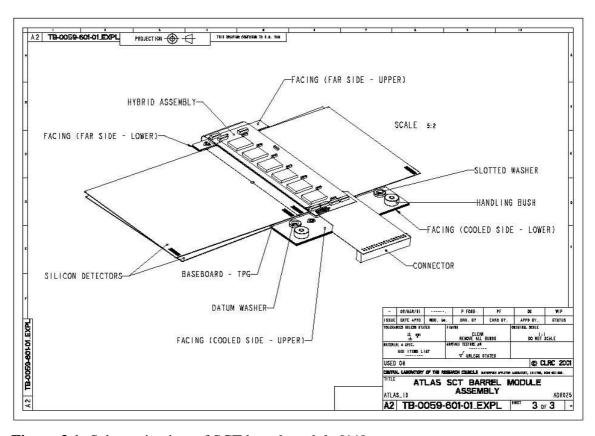

The SCT barrel module will be used for constructing the SCT detector, part of the Inner Detector in ATLAS (see chapter 1 for an overview of the ID and ATLAS). The detector will be constructed from four barrels and 9 end caps, with the barrel and end caps being assembled from only two types of modules; barrel and end cap modules, making it a highly modular system. Figure 3.1 shows a barrel module.

**Figure 3.1:** Schematic view of SCT barrel module [11]

Each SCT module consists of three major parts:

• Four silicon single sided reverse biased p-on-n strip detectors. Two detectors are bonded strip-to-strip to form 126.09 mm long strips. Two such configurations are then glued together back to back with a 40 mrad stereoangle, separated by a VHCPG baseboard. The detectors have a strip spacing of 80 µm, so the resolution perpendicular to the strips is very high. However, because of the 40

The SCT barrel module

- mrad stereo angle, a resolution along the strips is achieved as well, giving a resolution of 16  $\mu$ m in  $R\phi$  and 580  $\mu$ m in z.

- VHCPG (Very High Thermal Conductivity Pyrolytic Graphite) Baseboard. The baseboard is placed between the detectors, and works as a physical support, conductor and thermal transporter.

- **Hybrid with on-detector readout electronics.** The hybrid carries the front end electronics; 12 ABCD3T ASICS with one readout channel for each strip on the module.

Each part can be seen on the figure, and in the following sections, each part will be given a more detailed description.

## 3.1 Silicon Strip Detectors

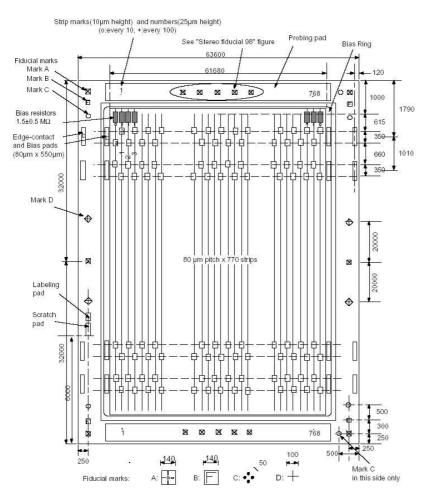

On the figure below, a single silicon strip detector is shown. It consists of 768 silicon strips (diodes), its dimensions are 63.56x65.6 mm, and the spacing between each strip is  $80 \mu m$ . The detector is specified to be  $285\pm15 \mu m$  thick.

**Figure 3.2:** Geometrical layout of silicon strip detector (ATLAS98) [12]

The SCT barrel module 27

In the next sections, an overview of semiconductors generally and the operation of the silicon detector specifically will be given.

#### 3.1.1 Semiconductors

Semiconductors are a group of materials whose conductivity lies between that of conductors and insulators. The conductivity of semiconductors range from 10<sup>-8</sup> to 10<sup>5</sup> S/cm, and contrary to metals, the resistance decreases with temperature. Semiconductors have been known since early nineteenth century, but the fields in which they could be applied were not realized before 1947, when the first transistor was made at Bell Laboratories, clearly one of the most important technological discoveries of the 20<sup>th</sup> century.

#### 3.1.2 Band theory of solids

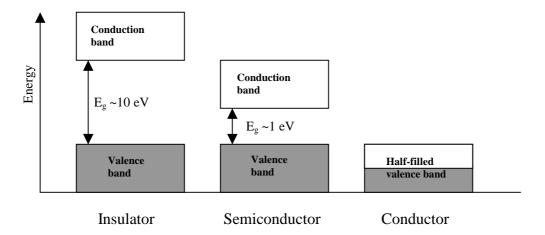

The conductivity of different materials a can be explained in terms of energy bands. The figures below show the band structure of an insulator, a metal and a semiconductor.

Figure 3.3. Band theory of solids

The bands represent the energy levels available to the electrons in the material, and are due to the splitting of energy levels that occur when atoms are brought close together. A material has a range of energy bands, and at low energy levels, there is an *energy gap*  $E_g$  between the levels. This means that the electrons in one band need a certain energy  $E_g$  to "jump" up to the next band.

In an insulator, the outermost band, also called the *valence band*, is completely filled, and the energy gap to the next band with unoccupied states, the *conduction band*, is large, typically  $E_g \sim 10$  eV. This means that the energy needed for an electron to move from the valence band to the conduction band is very large, and there are thus very few electrons occupying these states. This means in turn that there are few "free" electrons to drift with an applied field, giving the material a high resistance.

28 The SCT barrel module

Semiconductor materials are characterised by having a much smaller energy gap,  $E_g \sim 1$  eV. This makes it possible for many electrons to be thermally excited to the conduction band. However, this depends on the thermal energy of the electrons, which means that semiconductors are poor conductors at low temperatures. However, as the thermal energy increases, the number of electrons excited to the conduction band increases, resulting in a strongly temperature dependent conductivity, in contrast to metals, where conductivity slowly decreases with temperature.

In a conductor, the outermost band in the material is not full. This means that the electrons have many unoccupied states very close to their own energy, and a small amount of thermal energy is all that is needed for the electron to move to a nearby state. So when an electric field is applied, the electrons move very easily with the field, due to the vacant states in the energy band.

## 3.1.3 p- and n-type semiconductors

There are both positive and negative charge carriers in a semiconductor. When an electron is excited from the valence band to the conduction band, it leaves a *hole* in the otherwise filled band. A valence electron from a nearby site can then move to the empty hole, and the hole thus appears as a travelling positive charge, e+.

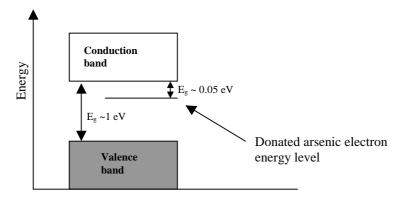

To alter the properties of a semiconductor, a technique called doping is used. This involves adding specific impurities into the semiconductor to change its conductive properties. For example: A semiconductor from group 4 (four valence electrons) is doped with Arsenic, which has five valence electrons. Four of these electrons participate in the bonding, leaving one almost free electron in the arsenic atom. Its energy level is very close to the conduction band, and only a small amount of thermal energy is needed to excite the electron to the conduction band, see figure 3.4, making it practically free to move in the lattice of the semiconductor. The arsenic effectively *donates* an electron to the semiconductor, and is thus called a *donor*. The semiconductor then has an excess of free electrons, and is called a *n(egative)-type* semiconductor.

**Figure 3.4:** n-type semiconductor energy bands.

On the contrary, if a semiconductor is doped with atoms having *less* valence electrons than itself, the doping atom has a vacant state in its electron shells, referred to as a *hole*. This leaves a free state for other electrons in the valence band to move into, and the donor thus *accepts* an electron and is called an *acceptor*. The energy levels of these holes lie in the energy gap, but only right above the valence band, which makes it easy for an electron to move into a hole. This is called a p(ositive)- type semiconductor, since it have an excess of holes in its lattice.

## 3.1.4 p - n junction

If p- and n-type semiconductors are joined in a *p-n junction*, the holes and the electrons in the border between the two materials will combine to form a *depletion region*. The donor electrons of the n-type will occupy the holes of the p-type conductor, and the region will thus be *depleted* for moving charge carriers. When the electrons of the n-type material moves over to the p-type, they leave immobile positive ion cores, which will set up a field over the depletion region, of order  $10^3 - 10^5$  V/cm, which keeps the depletion region free of mobile charges. This field creates a potential barrier, preventing further diffusion of holes and electrons across the border. The depletion region is typical a few  $\mu$ m wide. The p-n junction is also called a diode, and its most notable feature is its ability to pass current in only one direction. If a positive voltage is applied to the p-side of the junction, the potential barrier is decreased, and a current can flow through the p-n junction, known as *forward bias*. If a positive voltage is applied to the n-side, the depletion region increases, and only a very small leakage current can flow through the p-n junction. This is called *reverse biasing* of the p-n junction, and is the principle used in the silicon strip detectors.

#### 3.1.5 Silicon as a semiconductor

Silicon is an elementary solid-state semiconductor, belonging to the IV group in the periodic system. It is the most used semiconductor material, mainly for two reasons; it has high availability, being a very usual material in the earth's crust, and it yields a low leakage current.

## 3.1.6 Operational principle of silicon strip detectors

The reasons for using silicon strips as detectors are many; low cost, good spatial/energy resolution, fast response time, and good signal to noise ratio. The output signal is directly proportional to the energy deposited by the particle passing through the silicon, which makes it easy to measure this energy.

The ionization energy (the energy needed to produce an electron-hole pair) of silicon is 3.6 eV. The mean energy loss for a mip<sup>2</sup> particle traveling through the 285 µm silicon wafer is, according to the Bethe Bloch formula ~90 keV, which corresponds to about 25 000 electron-hole pairs. [13]

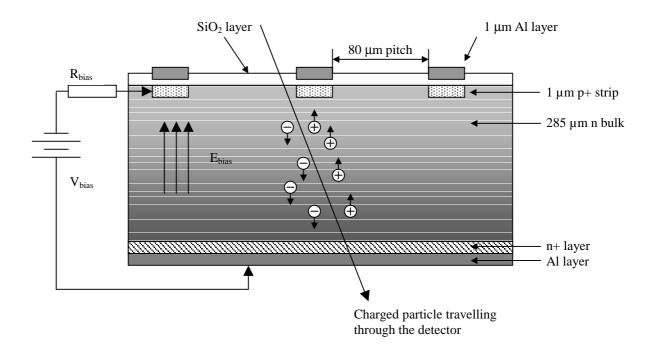

Below (figure 3.5) is shown a cross section of the detector. It consists of a p-n junction in the form of highly doped boron (Br) doped p+-type strips, 16-20  $\mu$ m wide over a 285  $\mu$ m thick n-type silicon bulk. The p+ strips are capacitively (AC) coupled to 1  $\mu$ m thick Al strips, 16-22  $\mu$ m wide, which collect the charge from the p+ strips. The Al strips are in turn bonded to the readout electronics. The material used between the Al and p+ strips are SiO<sub>2</sub>, to avoid a direct (DC) coupling between the high voltage bias and the sensitive readout electronics. There is an n+ layer on the other side of the bulk to ensure good ohmic contact to the 1  $\mu$ m layer of Al which is connected to the positive bias voltage (in the range 0-500 V).

Figure 3.5: Cross-sectional view of a silicon strip detector

When a voltage is applied to the Al layer, this sets up a reverse bias over the p-n junction, creating a depletion zone in the bulk material. When a charged particle passes through the bulk, it ionizes atoms in its path, which causes electron-hole pairs to be created. Some of these recombine before they can be collected, but most of the charge should be picked up by the Al-strips of the detector. The overall charge collection efficiency of the detectors is specified to be at least 90 %.

<sup>&</sup>lt;sup>2</sup> Minimum ionizing particle

To obtain a good signal to noise ratio, a low leakage current through the p-n junction is required. At the testing stage, a maximum leakage current of  $6~\mu A$  at 150~V is specified. However, during operation at LHC, the high radiation doses will alter the properties of the silicon, giving rise to a higher leakage current, and thus higher noise. To minimize this effect, the system is cooled down, as the leakage current on irradiated modules has been shown to double for every 7~C. Due to radiation, the n-bulk will over time change to p-type, a phenomenon known as type inversion. Since the strips are p+, it will still be possible to maintain a depletion region, but at a higher bias. After 10 years of LHC operation at planned luminosity, a bias of 350~V will be required.

### 3.2 Baseboard

The VHCPG (very high thermal conductivity pyrolytic graphite) baseboard is the central element in the SCT module, sandwiched between two pairs of detectors. Its task is to support the detectors mechanically, to transfer heat from the detectors and the readout electronics to the cooling pipes of the SCT. The latter will be gradually more important as the leakage currents increase due to radiation damage. The combination of these two capabilities is very important, as leakage currents have been shown to increase rapidly with temperature. It is also important for the baseboard to have the lowest possible mass, to minimize the total weight of the SCT detector. In figure 3.6 below, a baseboard is shown.

**Figure 3.6:** SCT barrel module baseboard [14]

The baseboard has a thickness of  $380\pm15~\mu m$ , and has an in-plane thermal conductivity up to 1850~W/m/K at  $20~^{\circ}C$ , increasing 0.4~% for each degree lower in temperature it is operated. Orthogonal to the baseboard, the thermal conductivity is down to 6~W/m/K. This is due to the planar mosaic ordering of the carbon structures in the material, and ensures that heat gets transported efficiently. Attached to each side of the baseboard are BeO facings plates which connects the module to the environment. These have a thermal conductivity greater than 280~W/mK at  $20~^{\circ}C$  and are  $250~\pm10~\mu m$  thick. The BeO facings will be connected to the cooling pipes in the SCT detector. [14]

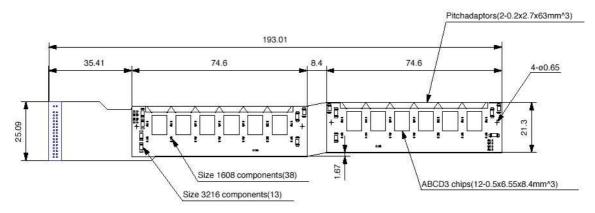

## 3.3 Hybrid

The hybrid is a four layer Cu/Polymide flexible circuit placed on a carbon-carbon bridge, carrying the front-end readout electronics for the silicon strip detectors. It consists of two main hybrid sections, each 74.6 x 21.3 mm connected with a 8.4 mm long interconnect (to wrap it around the module), and a 35.4 mm long connection to the pigtail cable. The thickness of the hybrid without components is 1.1 mm, with the highest components giving it a total height of 2.6 mm. Shown on figure 3.6 is a schematic drawing of a hybrid. 'Build-up' technology is used for constructing the hybrid, making it small and light and eliminating all cablings.

Figure 3.6: SCT barrel hybrid [15].

When mounted on the module, the hybrid forms a mechanical bridge over the detectors to avoid mechanical, electrical and thermal contact which could cause damage to the detectors.

The front-end electronics is placed on the hybrid, this means that there are 12 ABCD3T ASICS<sup>3</sup>, six on each side, wire bonded to 128 strips each. The ABCD3T ASIC is described in section 3.4. The ASICs dissipate a power of 6 W nominally, which makes the thermal conductivity of the hybrid important. For this purpose, the Cu/Polymide flexible circuit is mounted on a carbon-carbon bridge with high thermal conductivity,

<sup>&</sup>lt;sup>3</sup> ASIC – Application Specific Integrated Curcuit

700 W/m/K. To connect the chips directly to this thermally conducting bridge, the flexible circuit has thermal "through-holes" with diameter  $300~\mu\text{m}$ , vertically connecting the backside of the chips directly to the carbon-carbon bridge. When a circuit is glued to the carbon-carbon bridge, the through-holes are filled with electrically conductive adhesive, which gives each hole an estimated thermal conductivity of 40~W/mK. There are a total of 17~such holes per chip.

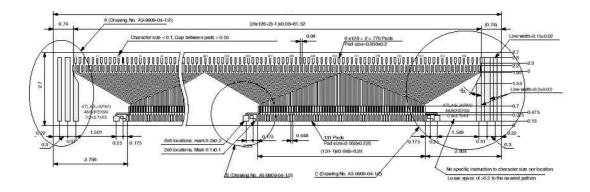

While the pitch between the silicon strips of the detector is 80  $\mu$ m, the corresponding pitch between ASICS read-in channels is 48  $\mu$ m. In order to make it possible to do a simple parallel wire-bonding when connecting the detector to the ASICS, a pitch adaptor is placed in front of the ASICS. It is made with thin-film technology, using 1-1.5  $\mu$ m thick aluminium deposition on a glass substrate.

**Figure 3.7:** Pitch adapter connecting detector strips to input pads of ABCD3T, with the detector bonded to the upper side and ASCIS to the lower side [15].

The hybrid is also able to measure the temperature of the module, using thermistors with  $R_{25}=10~k\Omega\pm1$ % and  $B=3435~K\pm1$ %. The temperature can then be calculated from the measured resistance of the thermistors from the formula: [15]

$$R = R_{25}^{\left[B\left(\frac{1}{T} + \frac{1}{298}\right)\right]}$$

(T is given in absolute temperature) (2)

#### 3.4 Front-end electronics

The front-end electronics on the hybrid consists of 12 ASICS of the type ABCD3T, interconnected via the circuitry of the hybrid. During development of the chip, low mass, low power consumption and high radiation tolerance have been important design goals.

The placing of the chips on the hybrid can be seen on figures 3.1 and 3.6. Each chip is wire-bonded to clock and control connections as well as the 128 outputs of the pitch adapter, which in turn is bonded to 128 silicon strips. A description of the chip and its operational principles will be given in the following sections.

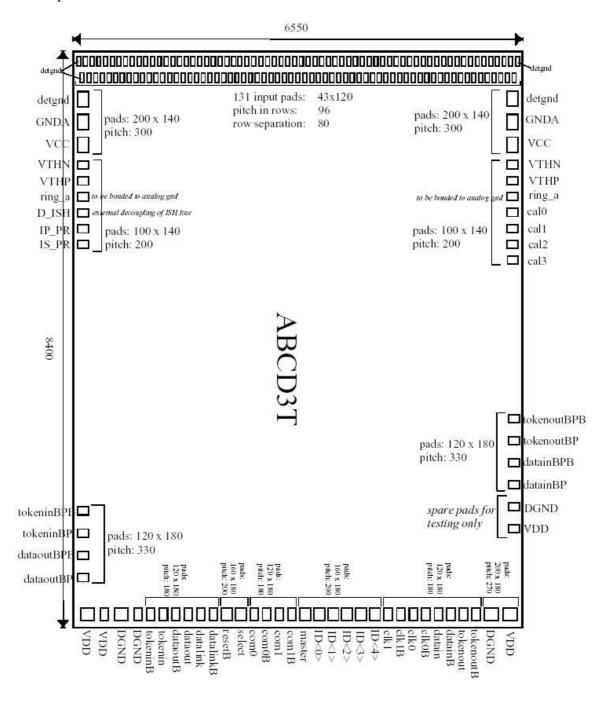

#### 3.4.1 The ABCD3T ASIC

The ABCD3T is an ASIC (*Aplication Specific Integrated Circuit*) designed for the purpose of digital readout of silicon strip detectors in the ATLAS SCT. Figure 3.8 shows the chip with dimensions and connections.

**Figure 3.8:** ABCD3T ASIC. Clock, and control connections can be seen on the lower side of the figure, power and tokens are on the left and right sides, while the connection to silicon strip are on the upper side of the figure. [16]

## 3.4.2 Command and clock reception for ASICS

Each chip has a dual set of clock and command inputs to increase the fault tolerance of the system. Which clock and command input to use, is set by the external SELECT signal.

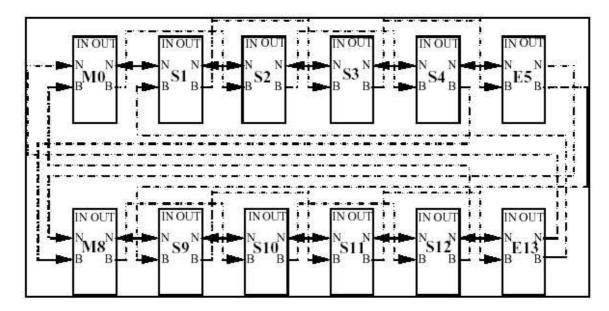

## 3.4.3 Addressing scheme

To uniquely identify each ABCD3T on the hybrid, the chip has a 6 bit address. The MS bit is for historical reasons set to 1. ID(4) is tied to the SELECT input (see previous paragraph), selecting which clock/command input to use, while ID(3:0) is used to identify the twelve chips on the module, referred to as the geographical address. ID(6:0) is for each chip on the module wire bonded to a unique set of logic levels, to give them a unique address in case a chip needs to be individually addressed.

#### 3.4.4 Signal flow

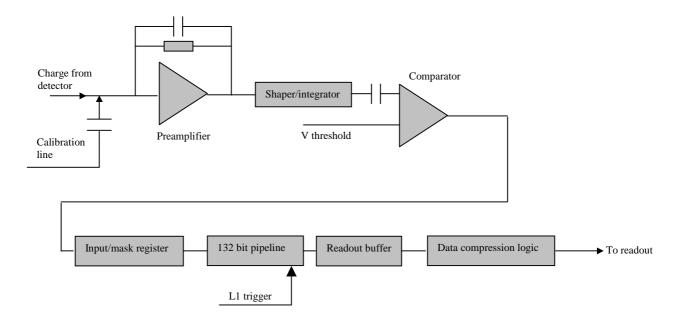

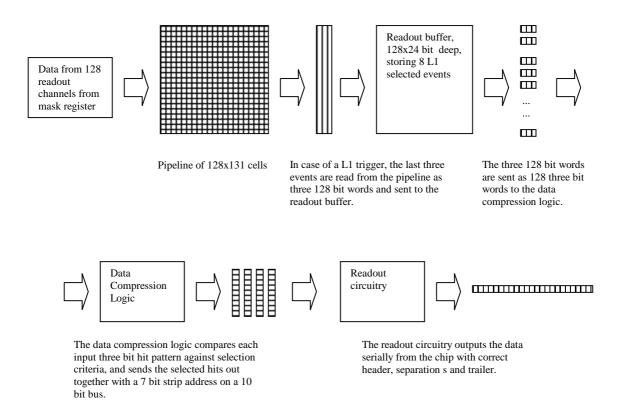

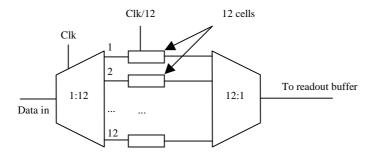

The ABCD3T has 128 inputs, one for each silicon strip. When a particle traverses the silicon, electron-hole pairs are made, and due to the field, the holes travel to the p+ strips, which are capacitively coupled to aluminium strips wire-bonded to the input of ABCD3T. The signal flow through the chip for the picked up charge from a silicon strip is shown in the diagram below, and each stage will be given a description in the following sections. In the chip, there are 128 such paths, each one to be connected to a silicon strip.

**Figure 3.9:** Signal flow for a single channel in the ABCD3T chip.

#### Calibration circuit

In the chip, each channel is connected to a 100 fF capacitor. At a certain control command, a pulse is sent from the capacitor, simulating a strip being hit. There are a total of four such calibration lines in the chip, connected cyclic to the channels. The calibration signal is selectable in the range 0-160 mV (0-16 fC) in steps of 0.625 mV (0.0625 fC). The ability to send in a known charge and see the chip's response to this is a very useful feature of the chip, used extensively during the electrical testing of the module.

The calibration circuit has a register associated with it, the strobe delay register, which determines the relative delay between the rising edge of the clock input and the rising edge of the calibration strobe.

## Preamplifier/Shaper

When the charge is first picked up, it is sent to a preamplifier. The amplified signal is then integrated by a shaper with peak time 20 ns, converting the pulse to a voltage level with gain  $\sim 50$  mV/fC for nominal shaper current of 20  $\mu$ A. The maximum noise allowed is 1500 electrons rms for an unirradiated module, 1800 for irradiated. The linearity should be better than 5% in the range 0-4 fC. Before the pulse is sent to the comparator, it is sent through an AC coupling to remove DC offsets in the pulse level.

## Comparator

The comparator compares a threshold voltage level to the input signal to determine if it should be recorded as a hit. If the input signal is higher than the threshold level, it outputs a logic 1 signal. The threshold voltage is applied from an internal DAC, set by the control software, and is common to all channels in the chip. The setting range from 0 fC (0 mV) to 12.8 fC (640 mV), with nominal setting 1 fC, adjustable in steps 0.05 fC (2.5 mV), with absolute accuracy 1 %. However, to compensate for channel-to-channel variations, there is for each channel a TrimDAC, allowing a threshold correction individual for each channel to be set. This is selected with a four bit register with four selectable ranges, ranging from 0-60 mV to 0-240 mV. This feature is crucial for compensating channel-to-channel variations, and will grow more important with time, as the offset spread in channels is expected to increase after radiation.

## Input/Edge detection register

The input register latches the incoming data, delivering a well defined pulse width for further processing, and thus marks the beginning of the digital readout, see figure 3.11. The edge detection is able to detect a high to low transition, and if edge detection is enabled, only high to low transitions will be recorded as hits.

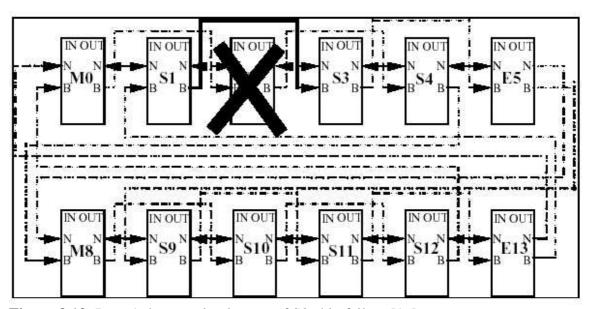

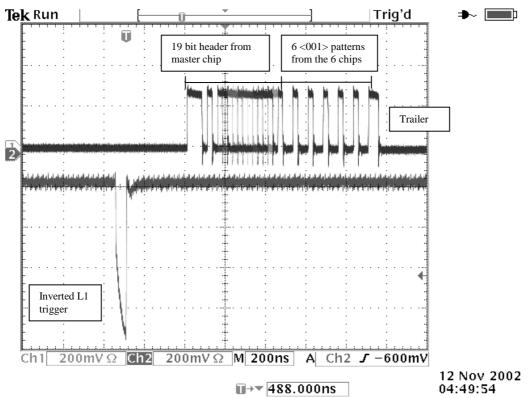

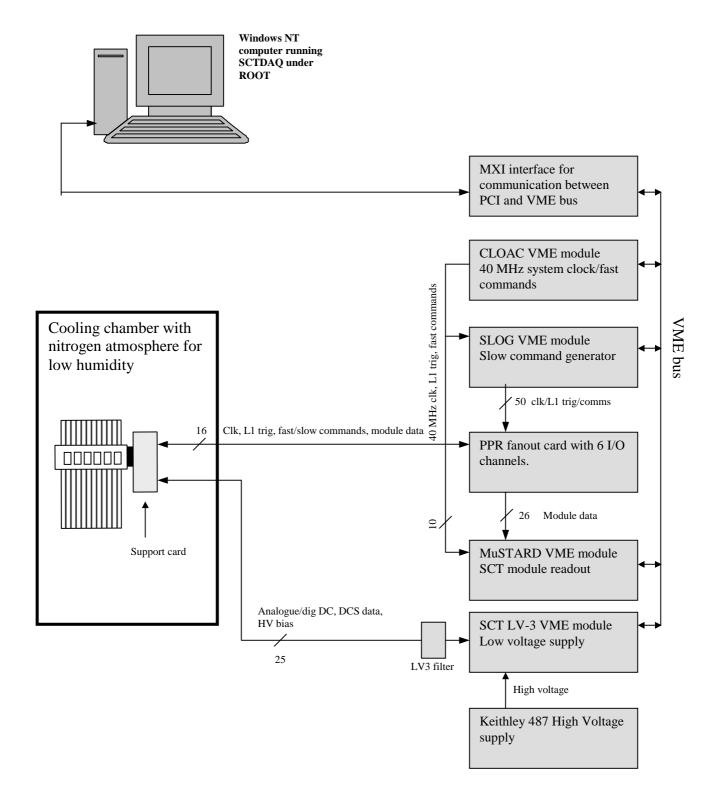

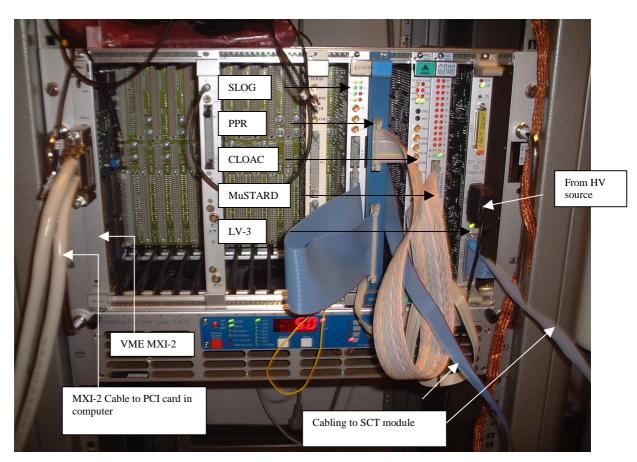

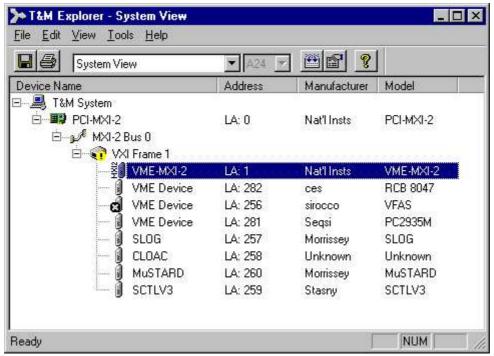

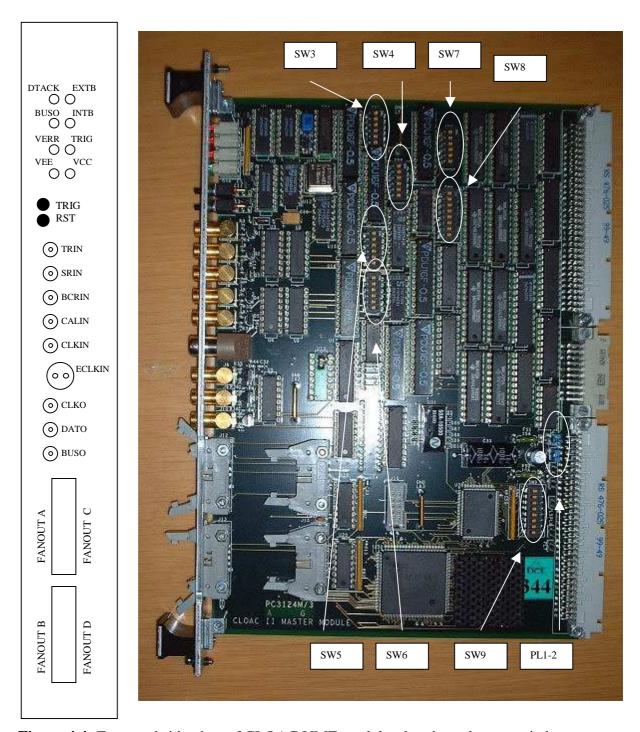

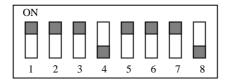

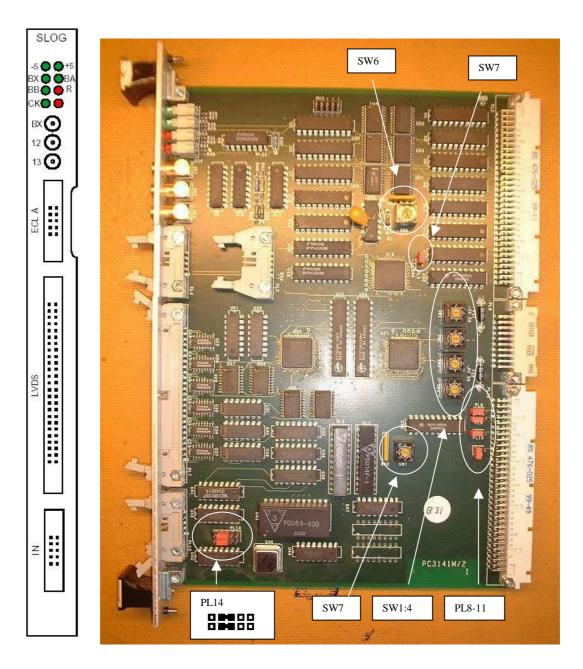

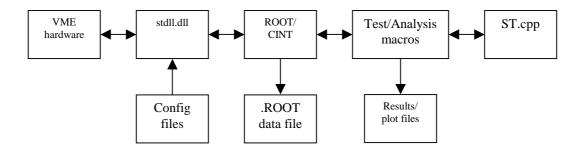

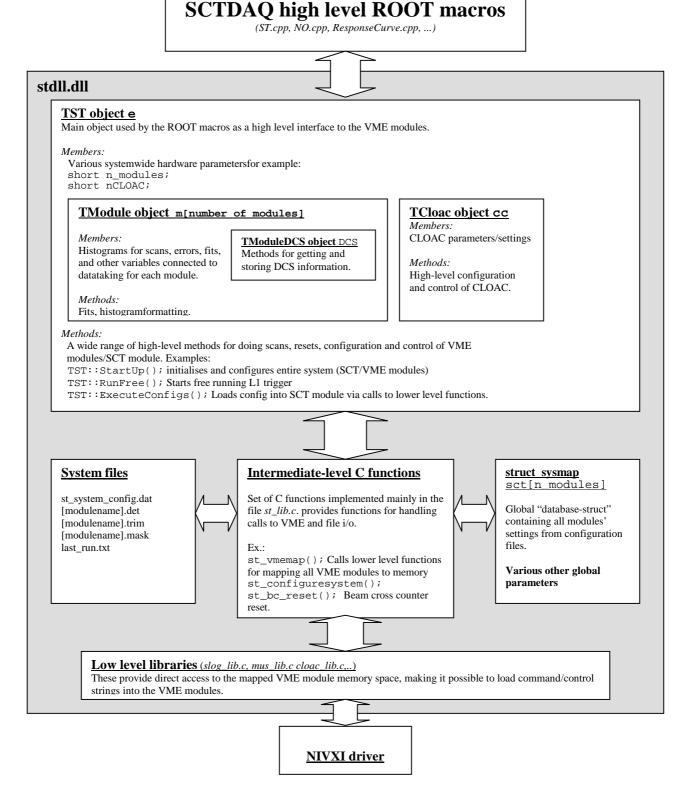

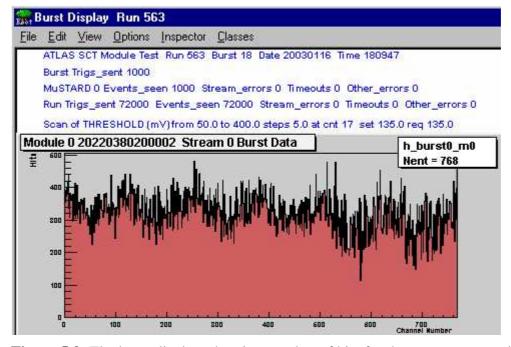

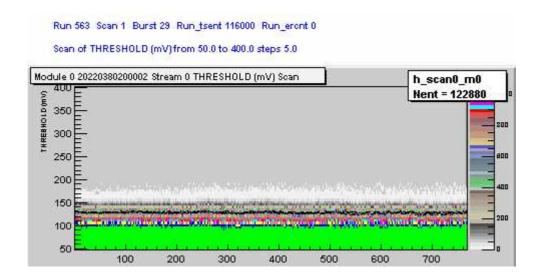

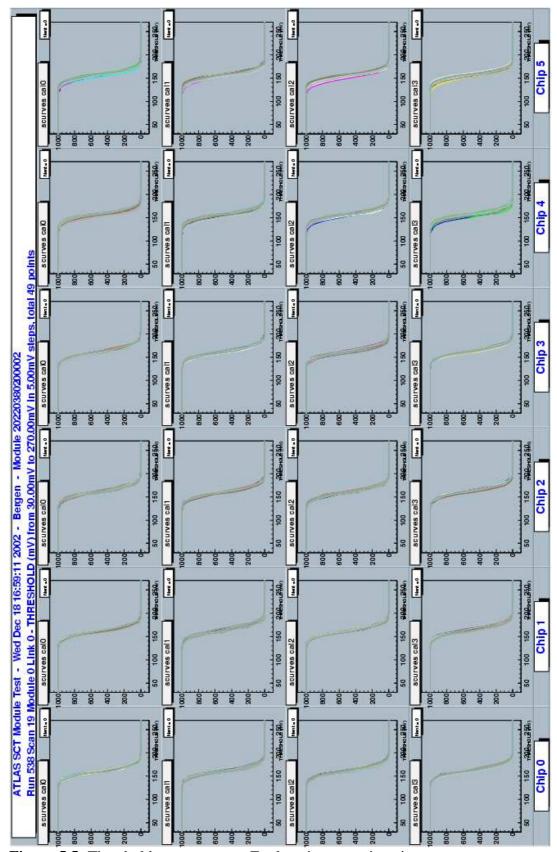

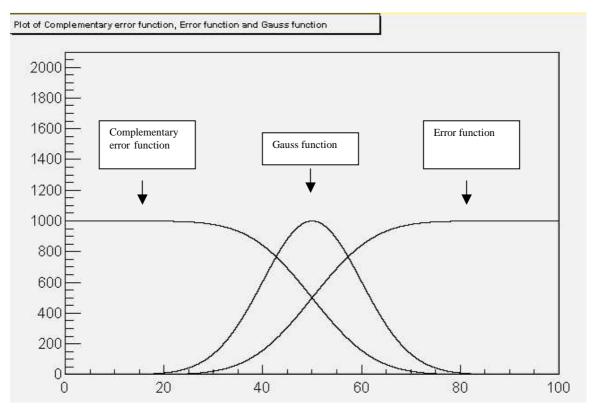

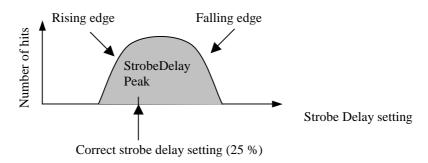

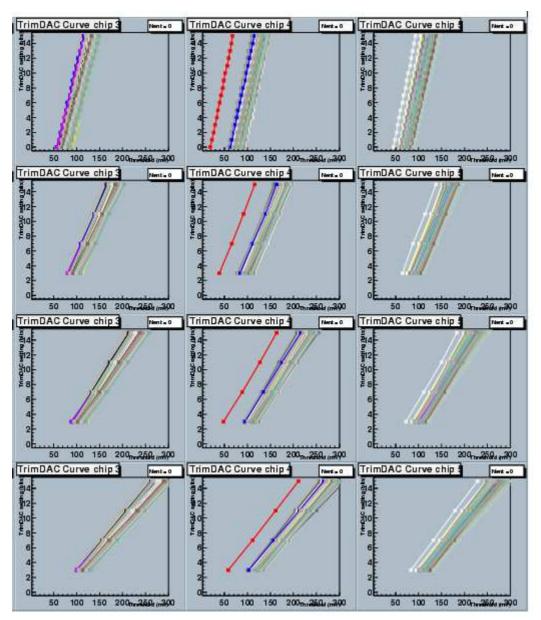

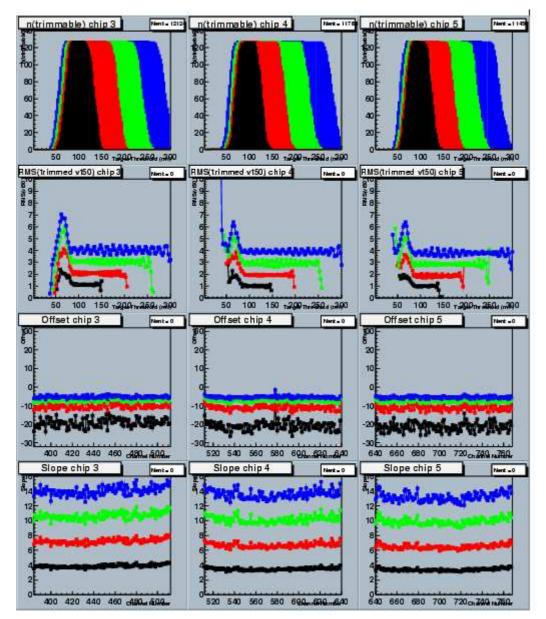

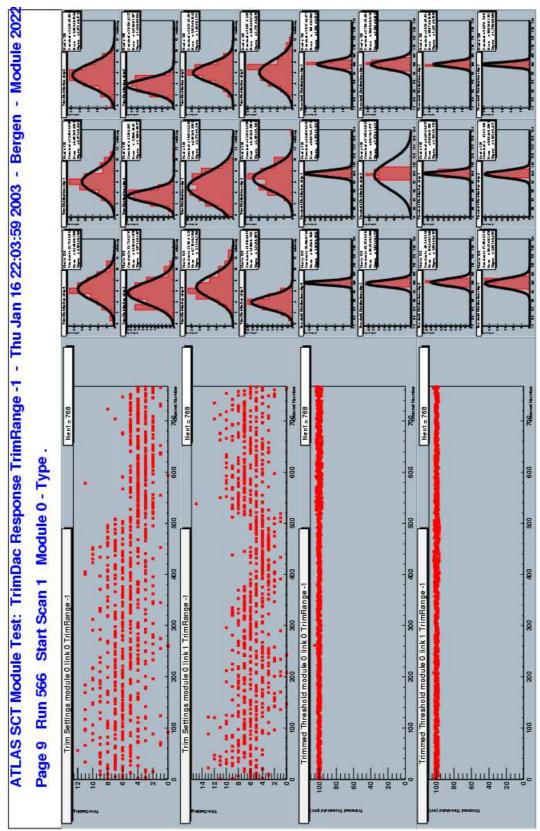

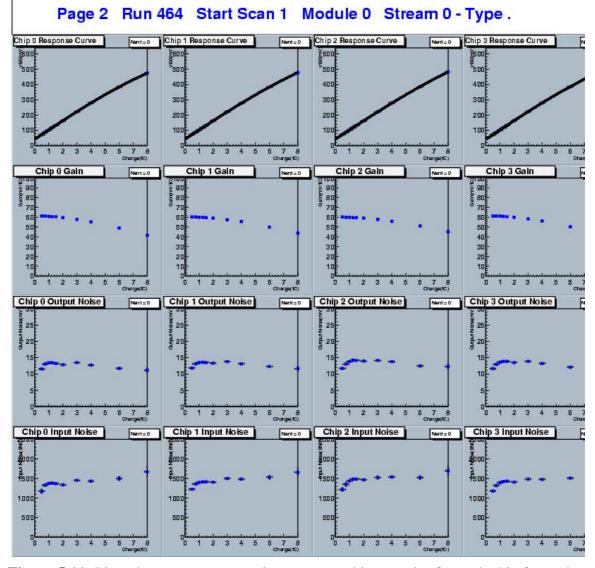

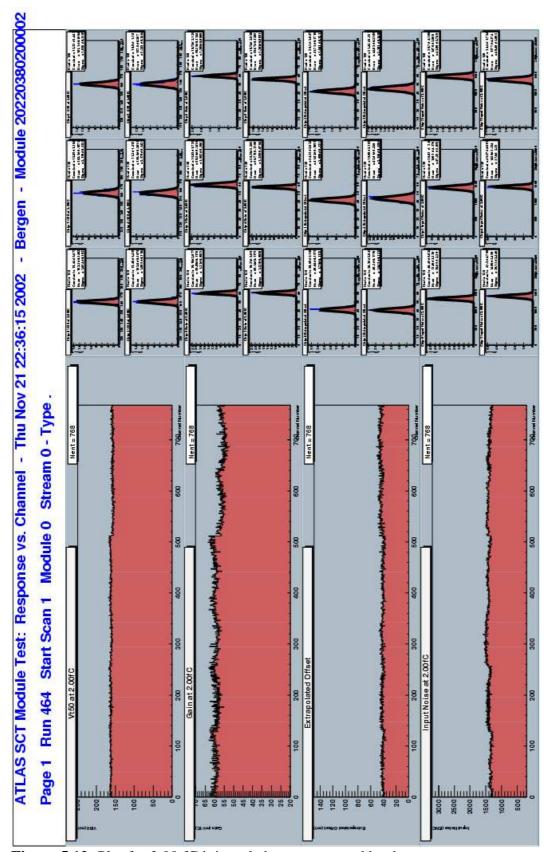

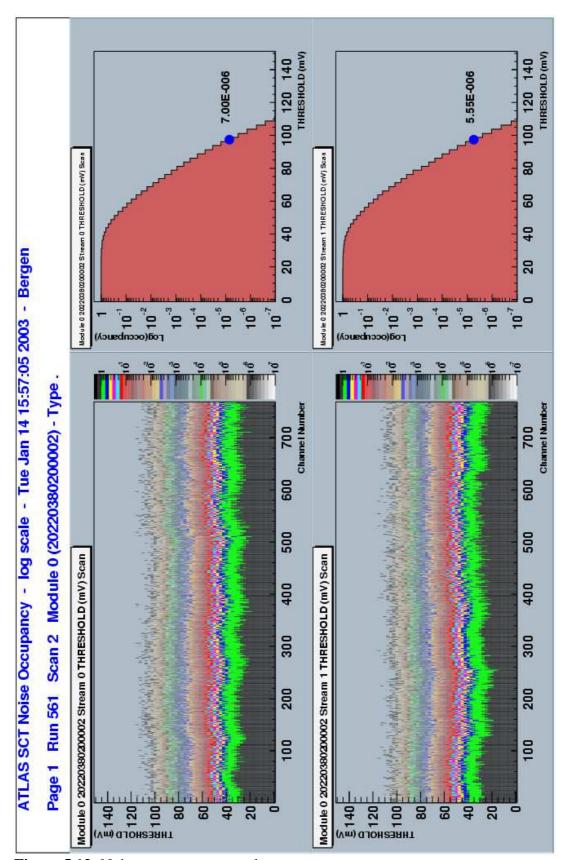

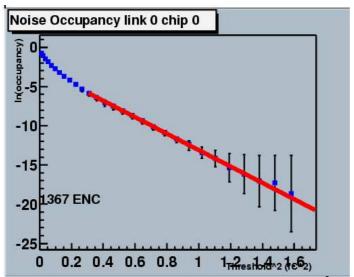

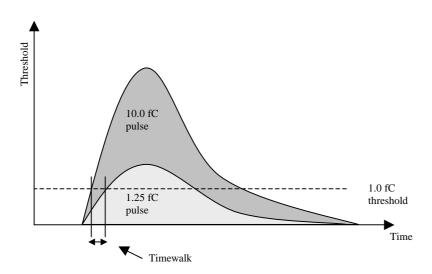

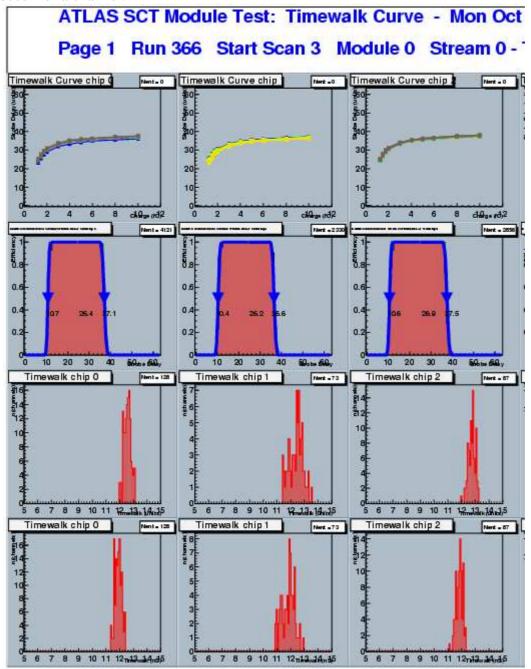

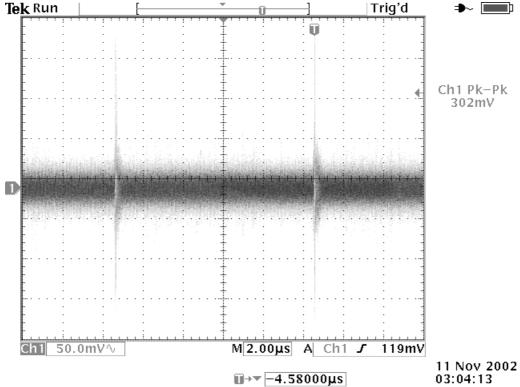

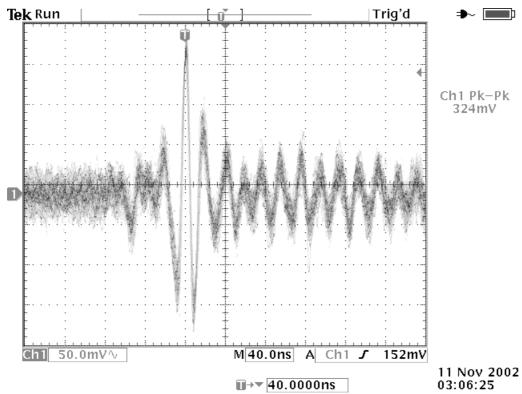

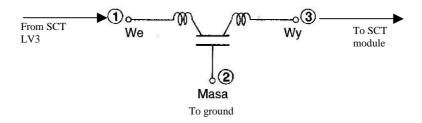

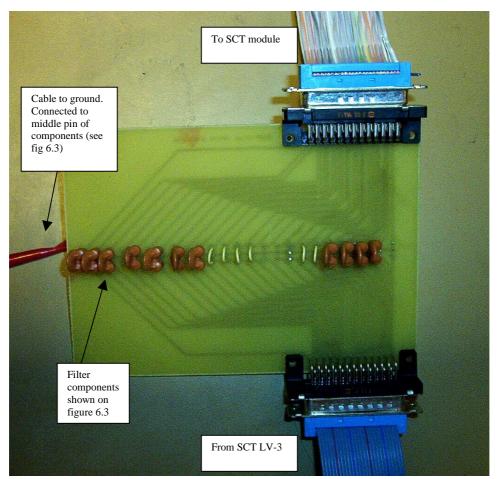

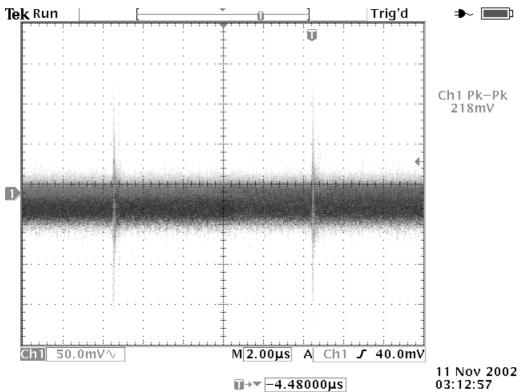

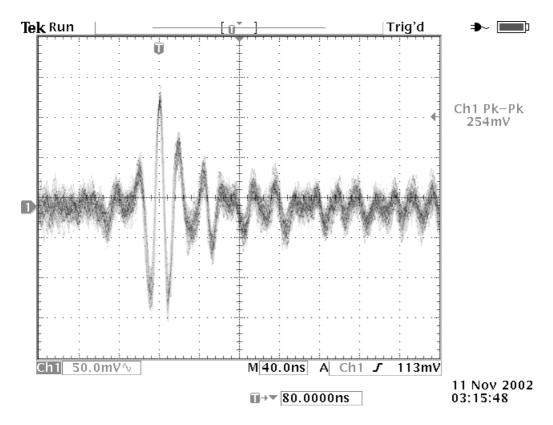

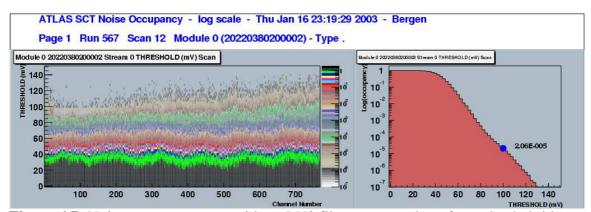

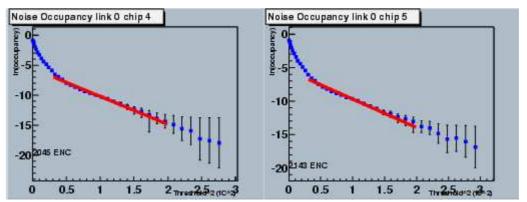

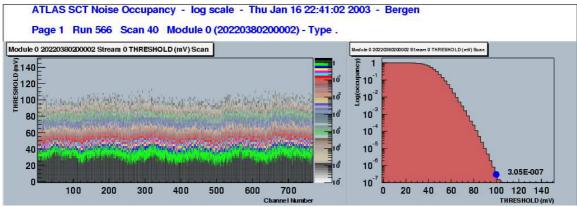

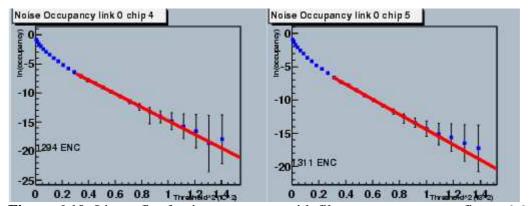

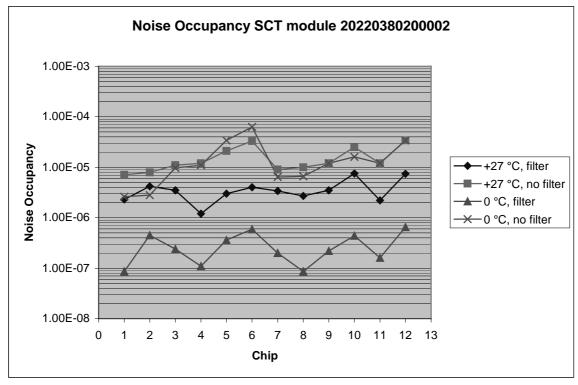

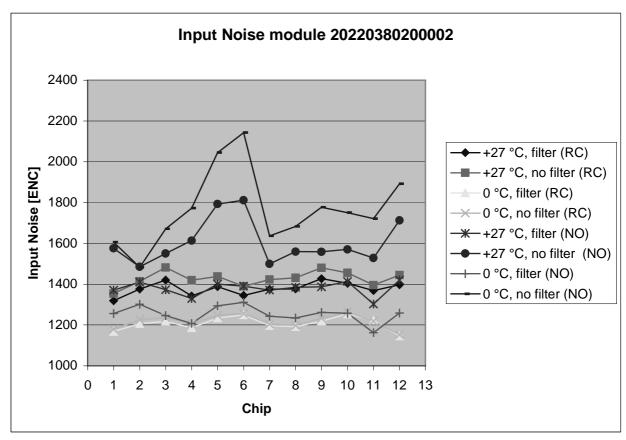

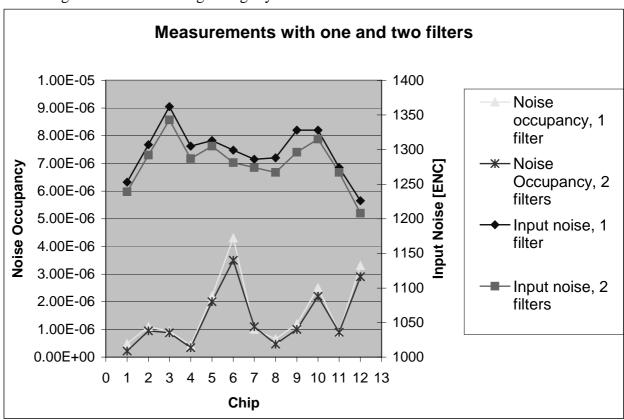

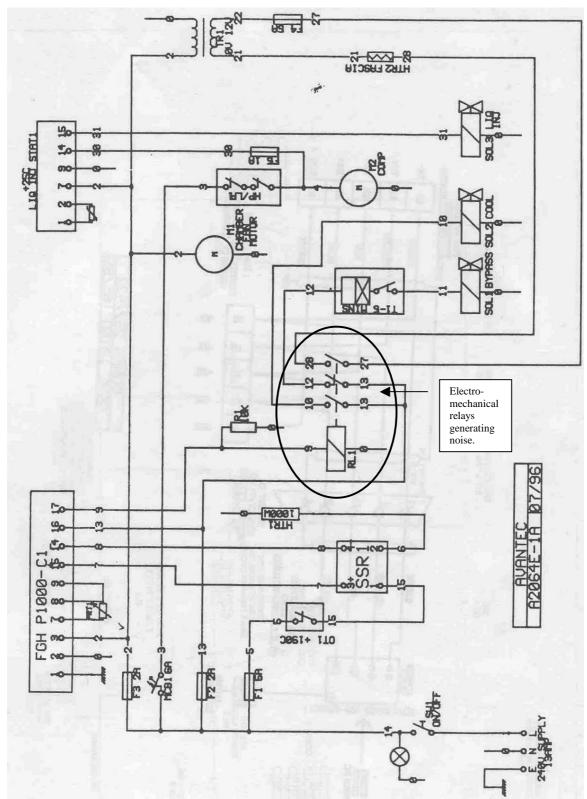

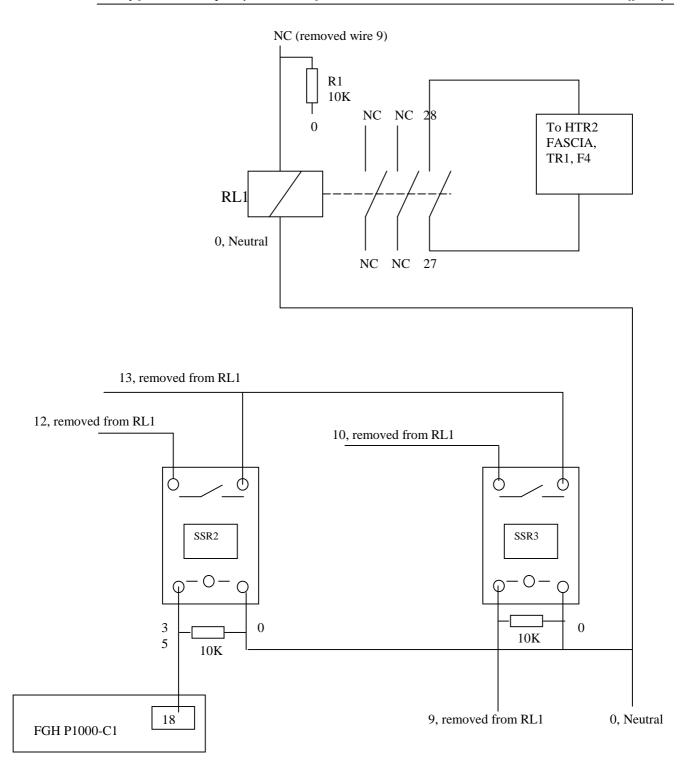

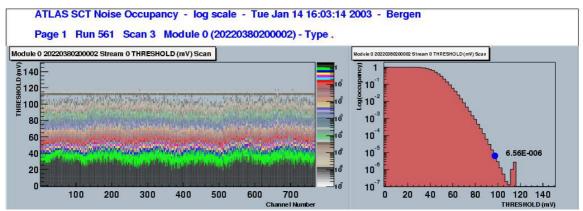

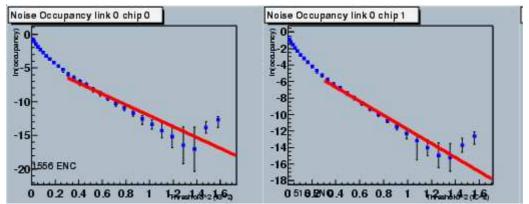

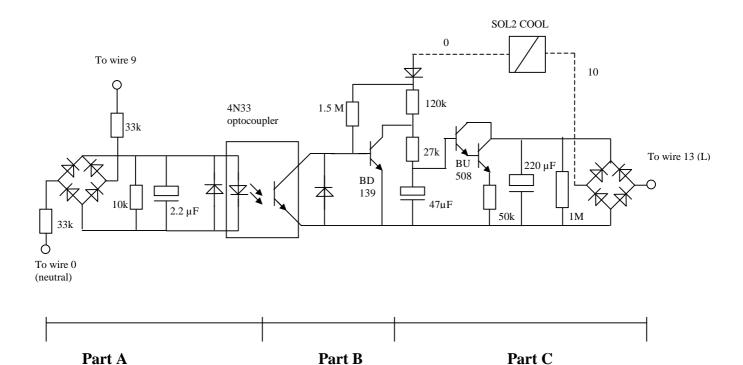

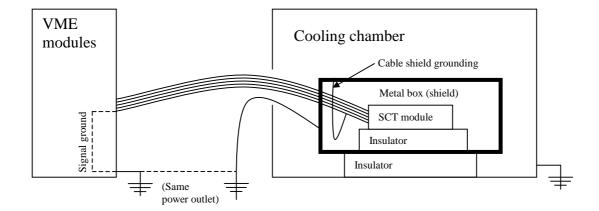

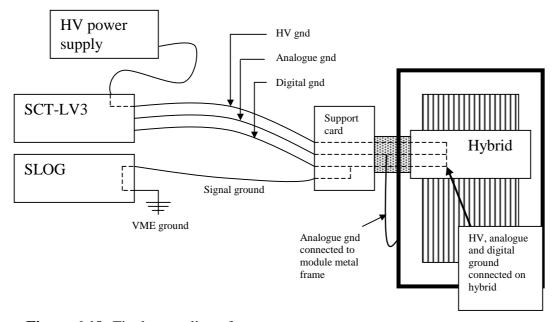

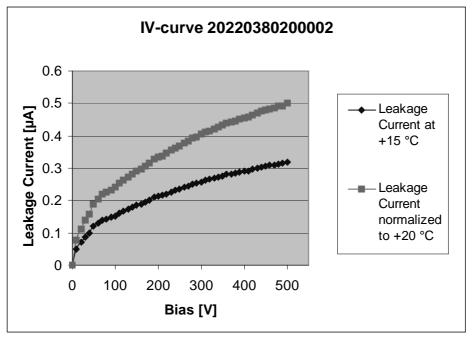

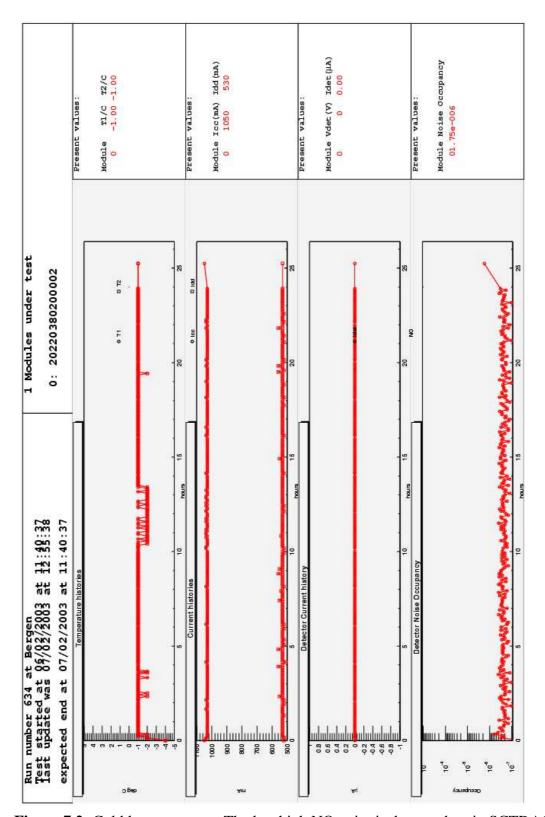

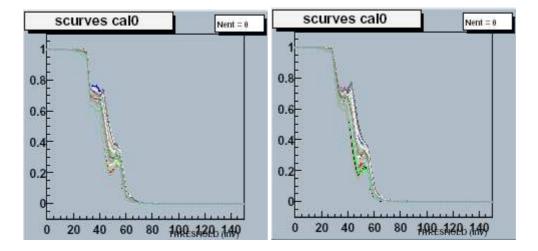

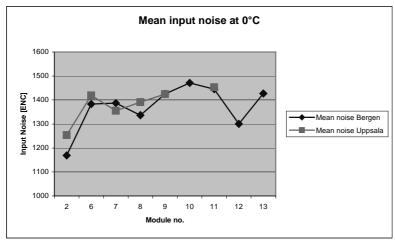

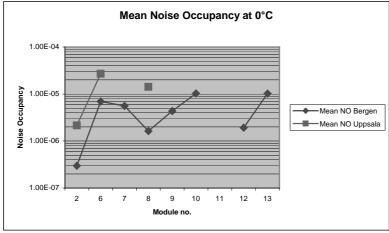

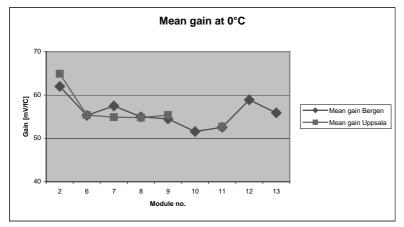

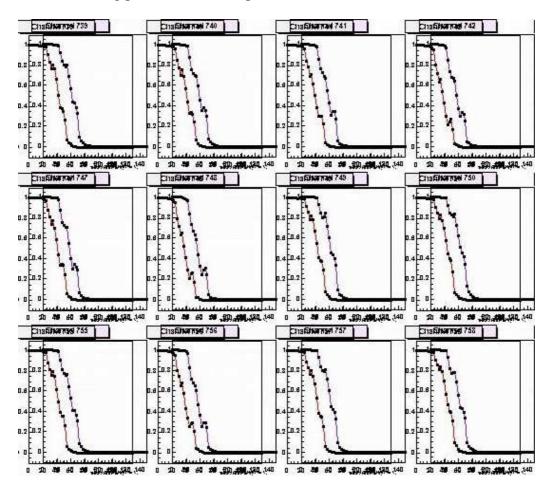

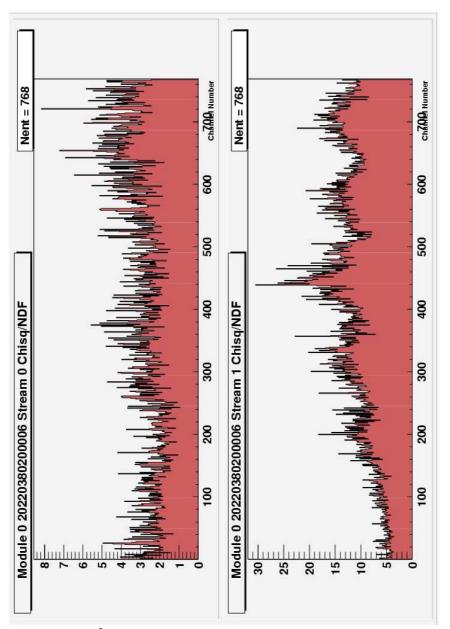

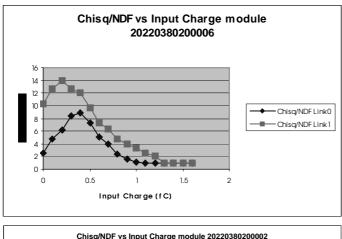

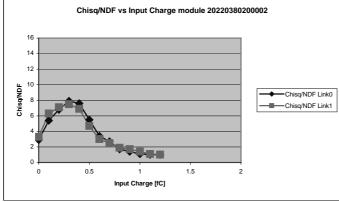

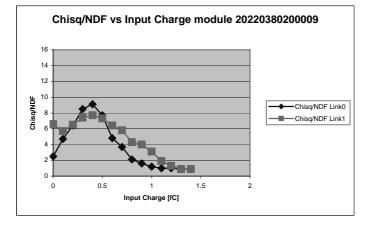

#### Mask register