## Ethernet-Based Control System and Data Readout for a Proton Computed Tomography Prototype

A thesis by

Karl Emil Sandvik Bohne

for the degree of

Master of Science in Physics

Department of Physics and Technology

University of Bergen

June 2018

## Abstract

At the University of Bergen (UiB), work is underway to develop a proton based computed tomography prototype. Proton CT (pCT) is an alternative to photonbased imaging that shows great promise as a technology for use in proton treatment planning, while also delivering lower doses of harmful radiation than its X-ray based counterpart. Particle treatment planning is currently achieved by performing X-raybased CT scans, of which the results are used to estimate a particle dose through a translation process. This introduces systemic errors due to the fundamentally different manners in which photons and particles interact with matter. pCT used for dosage planning purposes could eliminate the need for this conversion, allowing for treatment more precise and effective than what is currently possible.

The work needed to realize the complete pCT is extensive, and this thesis is primarily concerned with the control system for the multiple proton CT readout units (PRU) that will be used in the machine. This system will facilitate communication between a control room and the readout units, allowing an operator to determine the status of various system parameters such as power consumption, voltages and temperatures, program PRU peripherals according to a desired configuration, perform system initialization, trigger resets, etc. Such a system may also perform other tasks, such as automatic system-monitoring, or could provide assistance in the datareadout process.

This thesis discusses the requirements of such a system and how it might be realized, details its design, and describes in addition the full implementation of the required PRU field programmable gate array (FPGA) firmware on the current development board. Software for a soft-core processor running a lightweight OS and instantiated in the FPGA fabric is developed and tested successfully; providing serial- and Ethernet communication links via which a board can be controlled and monitored remotely, using a simple platform-independent API. Additionally, a DMA-based solution for data-readout is designed, implemented, and verified to be working by reading out actual detector data.

Other aspects of the system are also discussed, including ways of distributing a synchronized clock and trigger, power-monitoring, and future development. A primer on the workings of a proton CT in addition to particle-/photon matter interaction fundamentals is provided.

## Acknowledgements

The work detailed in this thesis would not have been possible without the guidance provided by my two advisors, professor *Kjetil Ullaland* and associate professor *Johan Alme.* A special thanks goes to them, for providing me with invaluable advice and feedback along the way. I also owe *Ola Slettevoll Grøttvik* a great deal for introducing me to the project, answering my questions, for his feedback, and for keeping me occupied throughout the past year. I am also grateful to the pCT group for allowing me to contribute to the project.

Additional appreciation goes to the guys in room 312 for keeping the collective spirit of the group high. Although the office at times more closely resembled an internetcafe/break-room hybrid than a place of study, these past two years would not have been the same without them. I would also like to thank the fantastic group of people with whom I first enrolled, five years ago, who has made this period not only tolerable, but at times even enjoyable.

I thank my family for their continued encouragement, and last but not least, my loving and supportive Julie, for being who she is, and for tolerating me these past seven-or-so years.

## Contents

| A | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |                  |  |                         |                  |                  |   |                  |                   | iii                                                             |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|--|-------------------------|------------------|------------------|---|------------------|-------------------|-----------------------------------------------------------------|

| A | Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                  |  |                         |                  |                  |   |                  |                   | $\mathbf{v}$                                                    |

| A | Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |                  |  |                         |                  |                  |   |                  |                   | xv                                                              |

| G | Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |                  |  |                         |                  |                  |   |                  | х                 | vii                                                             |

| 1 | 1 Introduction         1.1 Project Motivation and Goals         1.2 Thesis Structure                                                                                                                                                                                                                                                                                                                                                              |                                  |                  |  |                         |                  |                  |   |                  |                   | <b>1</b><br>1<br>2                                              |

| 2 | <ul> <li>2 Computed Tomography</li> <li>2.1 Ionizing Radiation</li></ul>                                                                                                                                                                                                                                                                                                                                                                          | · ·                              |                  |  | <br>                    |                  |                  |   |                  |                   | <b>5</b><br>5<br>7<br>7<br>8                                    |

| 3 | <ul> <li>3 The UiB pCT and the ALPIDE Pixel Sensor</li> <li>3.1 The ALPIDE Pixel Sensor</li> <li>3.1.1 Basic Principles of Operation</li> <li>3.1.2 Pixels</li> <li>3.1.3 Data Transmission Unit</li> <li>3.1.4 ALPIDE - Readout Unit Interface</li> <li>3.1.5 Control Interface and Chip Addressing</li> <li>3.2 The UiB pCT</li> <li>3.3 Existing pCT Systems</li> <li>3.4 Readout Electronics</li> <li>3.4.1 Current Implementation</li> </ul> | • • •<br>• • •<br>• • •<br>• • • | ·<br>·<br>·<br>· |  | · · ·<br>· · ·<br>· · · | ·<br>·<br>·<br>· | ·<br>·<br>·<br>· |   | ·<br>·<br>·<br>· | · · · · · · · · · | <b>11</b><br>11<br>12<br>13<br>13<br>14<br>15<br>15<br>16<br>17 |

| 4 | <ul> <li>4 The pCT Control System</li> <li>4.1 Features of a pCT Control System</li> <li>4.1.1 RU - Host Interface</li> <li>4.1.2 Board Initialization</li> <li>4.1.3 Provision of House-Keeping Data</li> <li>4.1.4 ALPIDE Monitoring</li></ul>                                                                                                                                                                                                  | · ·                              |                  |  | <br><br>                |                  |                  | • |                  |                   |                                                                 |

|          |      | 4.1.5 Additional Features and Data Readout                                                                 | 25              |

|----------|------|------------------------------------------------------------------------------------------------------------|-----------------|

|          |      | 4.1.6 The AXI Master                                                                                       | 25              |

|          | 4.2  | Clock- & Trigger Distribution                                                                              | 26              |

|          | 4.3  | The PRU Processor                                                                                          | 27              |

|          |      | 4.3.1 Operating Systems                                                                                    | 28              |

|          | 4.4  | PRU Software Applications                                                                                  | 30              |

|          | 4.5  | A Summary of the Previous Sections                                                                         | 31              |

|          |      | •                                                                                                          |                 |

| <b>5</b> | Firi | mware                                                                                                      | 33              |

|          | 5.1  | Requirements                                                                                               | 33              |

|          | 5.2  | Implementation                                                                                             | 35              |

|          |      | 5.2.1 Ethernet Subsystem                                                                                   | 35              |

|          |      | 5.2.2 MicroBlaze Configuration                                                                             | 37              |

|          |      | 5.2.3 UART                                                                                                 | 37              |

|          |      | 5.2.4 Monitor Module                                                                                       | 37              |

|          | 5.3  | Readout of Detector-Data                                                                                   | 38              |

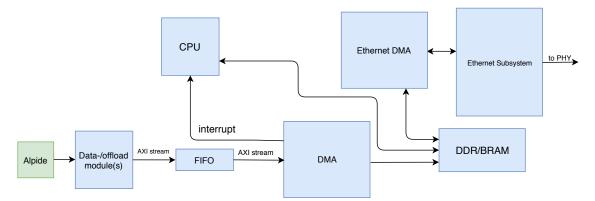

|          |      | 5.3.1 Development-Stage Data Readout                                                                       | 38              |

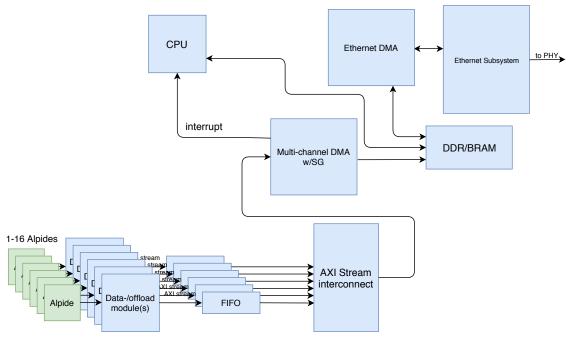

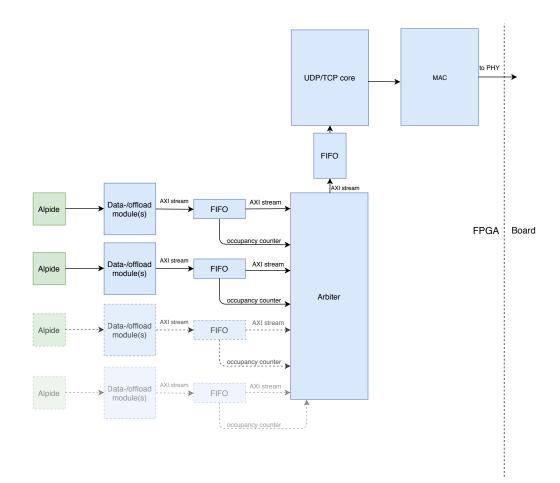

|          |      | 5.3.2 Data-Readout in a Complete System                                                                    | 40              |

|          |      | 5.3.3 Other Considerations                                                                                 | 43              |

| G        | Car  | atual Magaama Farmat and Dratagal                                                                          | 45              |

| 6        | 6.1  | ntrol Message Format and Protocol                                                                          | <b>43</b><br>45 |

|          | 6.2  | Requirements       An Application-Level Protocol                                                           | 45<br>46        |

|          | 0.2  | 6.2.1       Packet Format                                                                                  | 40<br>46        |

|          |      | 6.2.2 Considerations for Unreliable Interfaces                                                             | 40<br>47        |

|          |      | 6.2.3 COBS                                                                                                 | 47              |

|          |      | 6.2.4 Packet Fields                                                                                        | 48              |

|          |      | 6.2.5 Message Replies                                                                                      | -40<br>50       |

|          | 6.3  | Addressing ALPIDEs via a Peripheral Command                                                                | 50<br>50        |

|          | 6.4  | Hardware Offloading of the CRC- and COBS Calculations                                                      | 51              |

|          | 0.1  |                                                                                                            | 01              |

| <b>7</b> | Sof  | tware                                                                                                      | 53              |

|          | 7.1  | Requirements                                                                                               | 53              |

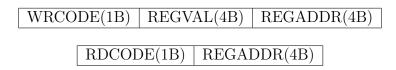

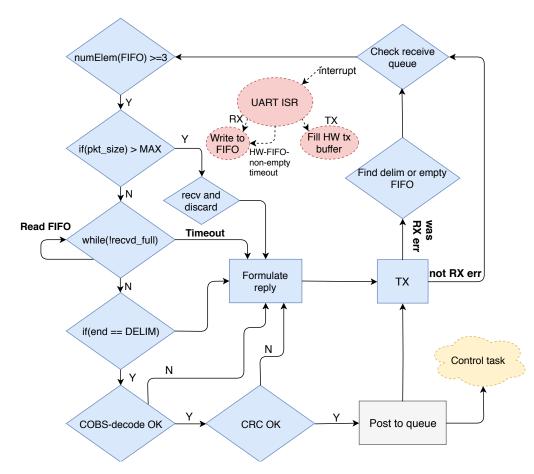

|          | 7.2  | Overview                                                                                                   | 53              |

|          |      | 7.2.1 Development Principles                                                                               | 54              |

|          | 7.3  | Software Structure                                                                                         | 54              |

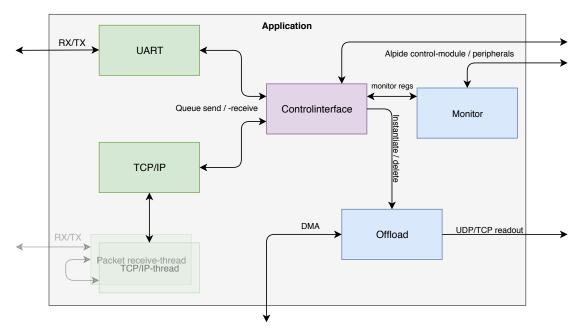

|          |      | 7.3.1 Control interface                                                                                    | 55              |

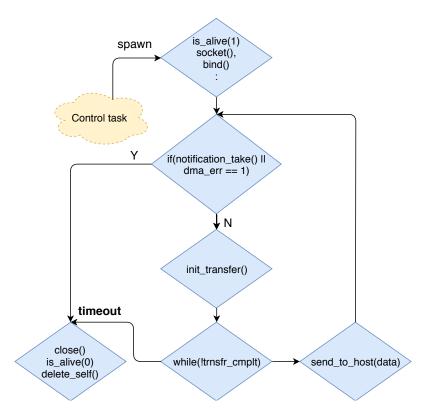

|          |      | 7.3.2 Data-Readout                                                                                         | 56              |

|          |      | 7.3.3 Monitoring $\ldots$ | 57              |

|          | 7.4  | ALPIDE Control Module Driver                                                                               | 58              |

|          | 7.5  | Data-Exchange Between Threads                                                                              | 58              |

|          | 7.6  | Software Configuration                                                                                     | 59              |

|          |      | 7.6.1 LwIP and FreeRTOS                                                                                    | 59              |

|          | 7.7  | Future development                                                                                         | 60              |

| ~        | C    |                                                                                                            | 0.0             |

| 8        | v    | tem Testing                                                                                                | <b>63</b>       |

|          | 8.1  | Host-Side Software                                                                                         | 64              |

|          | 0.0  | 8.1.1 API                                                                                                  | 65<br>65        |

|          | 8.2  | Testing                                                                                                    | 66              |

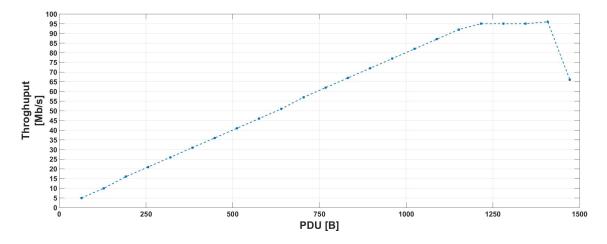

|              |      | 8.2.1   | Testing of Communication                        | 66 |

|--------------|------|---------|-------------------------------------------------|----|

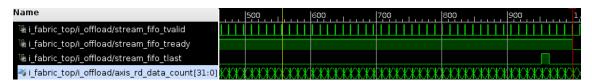

|              |      | 8.2.2   | Test Bench for the Updated ALPIDE Data Module   | 67 |

|              |      | 8.2.3   | Test of Data-Readout Solution                   | 68 |

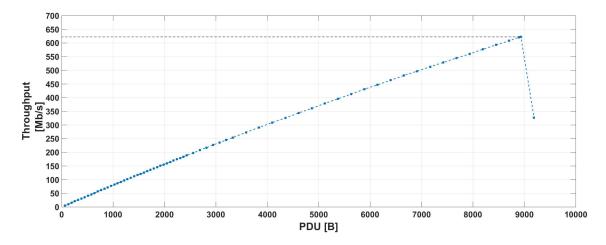

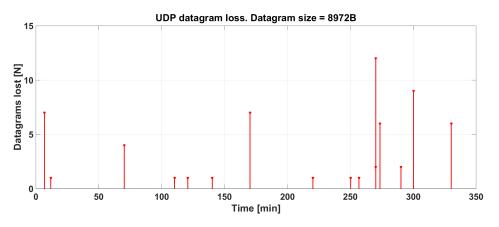

|              |      | 8.2.4   | UDP Packet Loss                                 | 70 |

|              |      | 8.2.5   | TCP                                             | 72 |

|              |      | 8.2.6   | Testing of the Full Readout Chain               | 72 |

|              |      | 8.2.7   | Testing of Self-Contained PRU Monitoring        | 74 |

| 9            | Con  | clusior | and Future Work                                 | 77 |

|              | 9.1  | Perform | mance Evaluation                                | 77 |

|              | 9.2  | Design  | Evaluation                                      | 78 |

|              | 9.3  | Future  | Work                                            | 79 |

|              |      | 9.3.1   | Porting of the Python Software                  | 79 |

|              |      | 9.3.2   | Porting of the Embedded Software                | 79 |

|              |      | 9.3.3   | Extension of the Readout-System                 | 79 |

|              |      | 9.3.4   | Implementation of Higher-Level Control Software | 79 |

|              | 9.4  | Conclu  | usion                                           | 80 |

| A            | Cod  | ling St | yle                                             | 81 |

| в            | Res  | ource l | Usage                                           | 83 |

|              | B.1  | RAM     |                                                 | 83 |

| $\mathbf{C}$ | SPA  | D       |                                                 | 85 |

|              | C.1  | Reques  | sts and Command Types                           | 86 |

|              | C.2  | Replies | 5                                               | 87 |

|              | C.3  |         | bles                                            | 87 |

| D            | Pyt  | hon Fr  | amework                                         | 89 |

| $\mathbf{E}$ | Var  | ious    |                                                 | 93 |

|              | E.1  |         | DE Mask-Application                             | 93 |

|              | E.2  |         | nentation and Commenting                        | 95 |

| $\mathbf{F}$ | Rep  | ository | 7 Structure                                     | 97 |

| Bi           | blio | raphy   |                                                 | 99 |

|              | e    | ,       |                                                 |    |

# List of Figures

| $2.1 \\ 2.2$ | 2D radiography showing source, target and detector setup Showing the dose delivered by a beam of photons, <i>modified</i> - and <i>native</i>                                                                     | 5        |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|              | protons as they pass through tissue                                                                                                                                                                               | 6        |

| 2.3          | Comparison of dosimetric planning with protons (top) to photons (bottom) [5]                                                                                                                                      | 7        |

| 2.4          | Typical pCT layout, showing separate tracking planes and calorimeter and the path of a proton                                                                                                                     | 8        |

| $3.1 \\ 3.2$ | Block diagram showing the main components of an ALPIDE chip [10].<br>Showing how a voltage on the input to the analog section cause a<br>hit to be stored in the pixel buffer if it surpasses a threshold while a | 12       |

| 3.3          | strobe is applied [10]                                                                                                                                                                                            | 13       |

| 3.4          | operations. [10]                                                                                                                                                                                                  | 14<br>14 |

| 3.5          | A model of the UiB pCT Digital Tracking Calorimeter (DTC), with ALPIDE chips in a horizontal stave configuration shown in dark                                                                                    |          |

| 3.6          | blue [11]                                                                                                                                                                                                         | 15<br>18 |

| 4.1          | The pixel-matrix addressing scheme [10]. Writing 0xFFFF to the address formed by the region selector field set to 0b1111 and the row bit and both column bits set would for instance mask/clear all pixels,       |          |

| 4.2          | depending on the pixel configuration register                                                                                                                                                                     | 21       |

| 4.0          | AXI control module.                                                                                                                                                                                               | 24       |

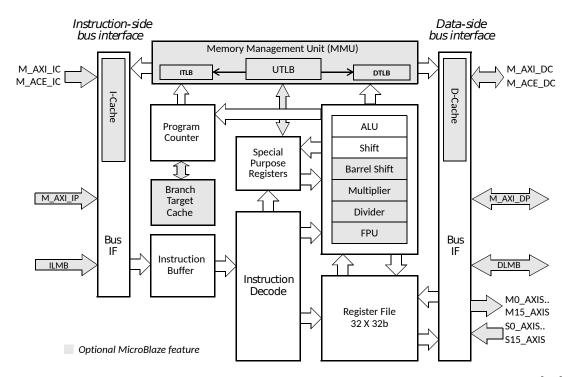

| 4.3<br>4.4   | Illustrating the low likelihood of non-overlapping strobe-windows<br>MicroBlaze architecture, showing the optional features grayed out [19].                                                                      | 26<br>27 |

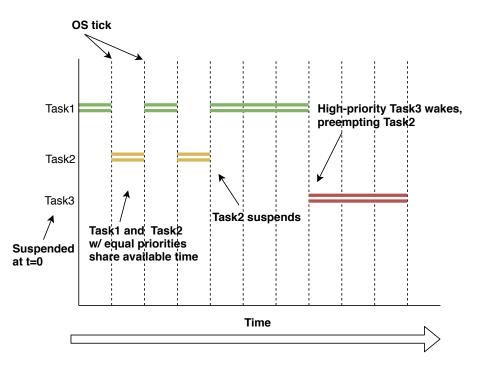

| 4.4<br>4.5   | Program flow in an RTOS-based system                                                                                                                                                                              | 21<br>28 |

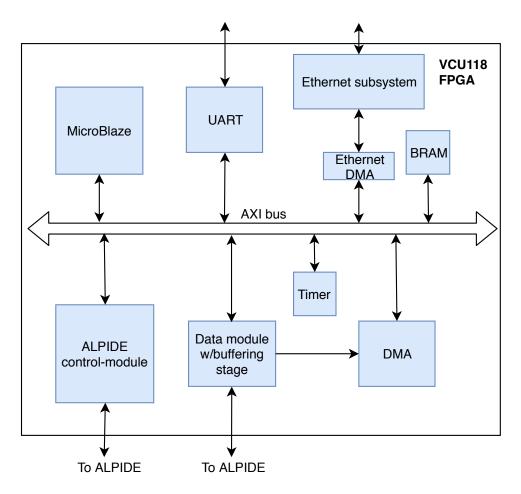

| 5.1          | Simplified diagram showing modules that relate to the control system<br>and development-stage data readout, as implemented on the FPGA                                                                            |          |

| <b>F</b> 0   | on the VCU118 board.                                                                                                                                                                                              | 34       |

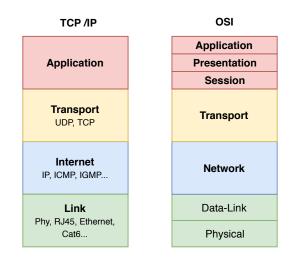

| 5.2          | The TCP/IP- / OSI stacks and overlap.                                                                                                                                                                             | 35       |

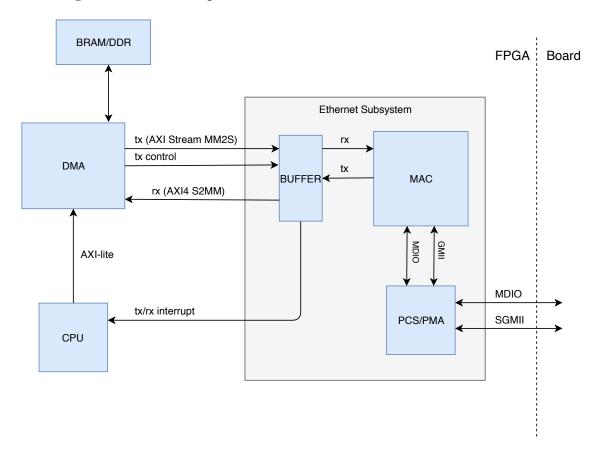

| 5.3          | Blocks central to Ethernet-functionality, as implemented on the VCU118 FPGA.         | 36       |

|--------------|--------------------------------------------------------------------------------------|----------|

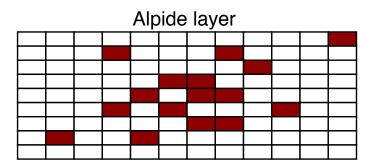

| 5.4          | Chips that are closer to center of a detector layer receive the majority of the hits | 38       |

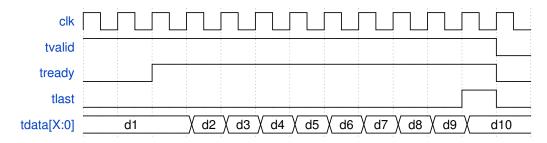

| $5.6 \\ 5.7$ | An example AXI-stream transaction                                                    | 40       |

|              | and UDP/TCP cores                                                                    | 42       |

| $7.1 \\ 7.2$ | Central threads in the MicroBlaze application                                        | 54       |

| 7.3          | similar, but is not required to verify encoding or CRCs                              | 55<br>56 |

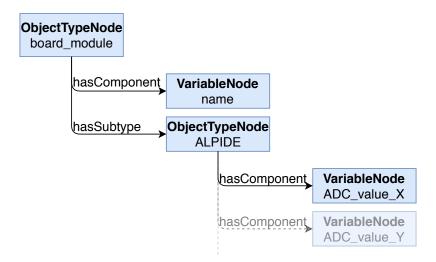

| 7.3<br>7.4   | Illustrating the OPC UA information model.                                           | 50<br>61 |

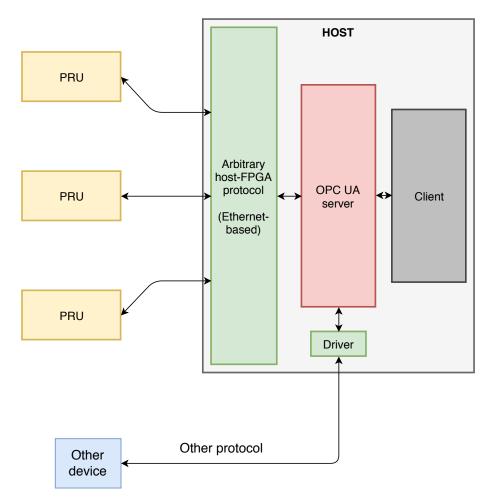

| 7.5          | A possible control system for the pCT                                                | 62       |

| 8.1          | Testing setup showing VCU118 board, FPGA Mezzanine Card (FMC),                       | 69       |

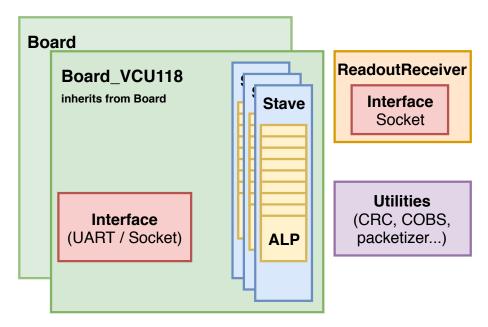

| 8.2          | and ALPIDE carrier                                                                   | 63       |

| 0.2          | with the exception of the Utilities-block.                                           | 64       |

| 8.3          | Print-out of the serial output as the PRU is assigned an address via                 |          |

|              | DHCP, and as it receives a connection                                                | 65       |

| 8.4          | UDP throughput as a function of PDU size on a 100 Mb link                            | 69       |

| 8.5          | UDP throughput as a function of PDU size on a 1000 Mb link with                      | 70       |

| 8.6          | Jumbo frames enabled                                                                 | 70<br>71 |

| 8.7          | A DMA transfer of ALPIDE data, as recorded by the internal logic                     |          |

| 8.8          | A print-out of an ALPIDE data-stream, formatted as PRU words by                      | 72       |

| 0.0          | the ALPIDE Data Module (ADM).                                                        | 73       |

| 8.9          | Showing a snippet of control-data read out while transfers are ongoing.              | 73       |

| 8.10         | Showing a gap of eight cycles between assertion of tready on the DMA                 |          |

| 0.11         | receive-side.                                                                        | 74       |

|              | Intermittent assertion of tready on the DMA engine.                                  | 74       |

| 8.12         | Debug-interface print-out of the embedded software reporting exceeded thresholds     | 75       |

| E.1          | The pixel-matrix addressing scheme [10]                                              | 93       |

| E.2          | The pixel-matrix $[10]$                                                              | 94       |

| F.1          | The MicroBlaze subsystem as it was implemented on the VCU118                         |          |

|              | platform.                                                                            | 98       |

# List of Tables

| 3.1 | Illustrating some basic specifications of previously developed pCTs [13].  | 16 |

|-----|----------------------------------------------------------------------------|----|

| 3.2 | ALPIDE readout-data format before processing on the PRU [10]. $\therefore$ | 16 |

| 5.1 | Xilinx DMA v7.1 figures at $100 \text{ MHz} [33]$                          | 41 |

| 5.2 | Control register                                                           | 43 |

| 5.3 | FIFO depth and -threshold register                                         | 43 |

| 5.4 | bytes-offloaded counter register, 32msb                                    | 43 |

| 5.5 | bytes-offloaded counter register, 32lsb                                    | 43 |

| 5.6 | FIFO-overflow counter register                                             | 43 |

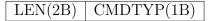

| 6.1 | Application level protocol - Base packet format.                           | 46 |

| 6.2 | Application level protocol - Header and trailer, respectively              | 46 |

| 6.3 | Consistent overhead byte stuffing example                                  | 47 |

| 6.4 | A packet appended with a 16 bit CRC and byte-stuffed with COBS             | 48 |

| 6.5 | Payload - format for register writes- and reads, respectively              | 48 |

| 6.6 | Payload - ALPIDE register writes and reads, respectively                   | 49 |

| 6.7 | Payload - ALPIDE broadcast opcodes.                                        | 49 |

| 6.8 | Application level protocol - Reply packet                                  | 50 |

| 7.1 | Showing the format of an MQTT packet                                       | 60 |

| 8.1 | Test results with the updated data module                                  | 67 |

| 8.2 | PRU Headers.                                                               | 73 |

| D 1 | December of comments in the ded in the MinneDless subsection               | ດາ |

| B.1 | Resource usage of components included in the MicroBlaze subsystem          | 83 |

| C.1 | Application level protocol - CMDTYPes                                      | 86 |

| C.2 | Payload - format for register writes- and reads respectively, and values   |    |

|     | of the WR/RD-field                                                         | 86 |

| C.3 | Payload - ALPIDE register writes, -reads, and opcodes, respectively        | 86 |

| C.4 | Payload - The <i>special</i> command type                                  | 87 |

| C.5 | Reply-data ACKs/NACKs                                                      | 87 |

| C.6 | Example write-request and response                                         | 87 |

| C.7 | Example read-request and response                                          | 88 |

| C.8 | Example ALPIDE write-request and response, and contents of payload.        |    |

| C.9 | Example ALPIDE read-request and response.                                  | 88 |

### Acronyms

**ACM** ALPIDE Control Module **ADC** Analog to Digital Converter **ADM** ALPIDE Data Module ALICE A Large Ion Collider Experiment ASIC Application Specific Integrated Circuit **AXI** Advanced eXtensible Interface **BRAM** Block RAM **BSP** Board Support Package **CERN** European Organization for Nuclear Research CMS Compact Muon Solenoid **COBS** Consistent Overhead Byte Stuffing **CRC** Cyclic Redundancy Check **CT** Computed Tomography **DMA** Direct Memory Access **DTC** Digital Tracking Calorimeter **DTU** Data Transmission Unit **FIFO** First-in, First-out (queue type) FMC FPGA Mezzanine Card **FPGA** Field Programmable Gate Array **IB** Inner Barrel **IP** Internet Protocol / Intellectual property (-core) **ISR** Interrupt Service Routine **ITS** Inner Tracking System

LVDS Low Voltage Differential Signaling **LwIP** Lightweight IP (software library) **MAC** Media Access Control (-address) **MEB** Multi Event Buffer **MQTT** Message Queuing Telemetry Transport MTU Maximum Transmission Unit **NIC** Network Interface Controller **OB** Outer Barrel **pCT** Proton CT **PDU** Protocol Data Unit PRU Proton CT Readout Unit **RISC** Reduced Instruction Set Architecture SCADA Supervisory Control and Data Acquisition SCU System Control Unit **SDK** Software Development Kit **TCP** Transport Control Protocol **UART** Universal Asynchronous Receive Transmit **UDP** User Datagram Protocol **UiB** University of Bergen

## Glossary

- **8b10b encoding** Encoding scheme that maps 8 bits of data into a 10 bit symbol in order to provide DC-balance and facilitate clock-recovery.

- **Datagram** In the context of UDP: The PDU of the UDP protocol.

- **Jumbo frame** An Ethernet frame with more than 1500 bytes of payload, up to a maximum of 9000.

- Manchester encoding Encoding scheme where each bit is encoded as either a high- followed by a low value, or vice versa.

- **SNMP** Network management-/monitoring protocol for collecting information on managed networked devices.

- **Struct** In a C-context: an object-like data type with an arbitrary number of fields of arbitrary type.

- Super-loop Large infinite loop in software containing an application or subroutine.

- **TCP/IP** A collection of protocols that together make up the Internet Protocol Suite.

Chapter 1

## Introduction

The use of particle therapy in clinical medicine is growing; in 2016 alone, more than 170000 patients were treated with particles, with the majority of these receiving treatment using protons [1]. The dose a patient is to receive must be determined beforehand, and this is currently calculated based on the results of conventional X-ray CT scans. This introduces inaccuracies which reduce effectiveness, and can lead to long-term health issues due to accidental radiation of healthy tissue causing secondary cancers. With pCT, this translation process could be eliminated, leading to more effective treatment while also reducing unnecessary exposure to radiation.

In 2016, the University of Bergen received funds to facilitate development of a pCT prototype. The prototype will consist of several layers of CERN-developed pixel detectors, originally designed for use in the ALICE experiment. These are sensitive to impacting particles and photons, and will enable precise reconstruction of the tracks and residual energies of individual protons, which are both required in order to perform dose planning.

#### 1.1 Project Motivation and Goals

Some work towards a pCT prototype has been completed: In 2016, the feasibility of using a digital tracking calorimeter for both tracking and residual-energy measurements of individual protons was verified, and in 2016 and -17, a block design for a prototype was laid out, parts of the electronics for the readout-units designed, and the detector-chips themselves selected and partly tested.

Several of these chips will interface to specially designed readout boards; the PRUs. Each board will manage several pixel detectors, and contain data processing modules that handle the data these produce, firmware that allows this data to be read out, and other auxillary modules. It is also likely to expand further as development progresses. A system is required that allows for the configuration, monitoring and control of these modules. Although considerable work remains before the pCT is realized, this thesis primarily discusses the requirements- as well as the implementation of such a control- and monitoring system. One of the goals was to design a system that was sufficiently general for it to be of use in similar projects in the future, and that could easily be extended or built upon as the pCT project progresses.

Initial PRU development was done on a CERN-developed readout board, but has since migrated to a new Xilinx FPGA platform. No control interface existed for the new board, and neither did a method for readout of produced detector data. A subsystem that could perform this task was also needed so that elements of the design could be tested.

Finally, as the project is still in its relatively early stages, the details of the modules that will be included in the system are not fully decided. Alterations to the existing design that could streamline and simplify the development process could possibly be made, and this was also explored.

#### 1.2 Thesis Structure

# Chapter 2 - Computed Tomography and Particle/Photon - Matter Interactions

This chapter describes the workings of both conventional- and proton based CT. How particles and photons interact with matter, how they deposit energy as they do so and how this is used to form images is shown. Some of the promising aspects of pCT are discussed.

#### Chapter 3 - UiB pCT and the ALPIDE Pixel Sensor

This chapter describes the pCT in development at UiB, including a description of the pixel detectors used in the project, as well as the overall structure of the prototype, and how it differs from existing pCTs.

#### Chapter 4 - A pCT Control System

This chapter explains the need for a system that can be used to control the various components of the pCT. It defines the roles such a system is required to fill, any additional tasks it might perform, how these might change as the project develops, and outlines how such a system should be implemented.

#### Chapter 5 - Firmware

This chapter discusses the firmware necessary in order to provide the functionality described in chapter 4. With the exception of a module that requires external system components that are not yet available, this firmware was fully implemented as part of the work performed during this thesis, and this process is detailed. In addition, a DMA-based solution suitable for detector-data readout during the development stage was developed, and this is also described. Additional aspects of this process that will become relevant as the project evolves are discussed.

#### Chapter 6 - Development of an Application Level Protocol

This chapter develops a simple application-level protocol for transferring arbitrary data between two parties, which can be used to provide access to memory mapped modules on a device. It also defines optional additions to control the pixel detectors as well as the master-module responsible for carrying out the control related tasks. The former simplifies these operations while greatly reducing the overhead this typically involves.

#### Chapter 7 - Software

An embedded processor was implemented in the FPGA fabric as part of the design developed in chapter 5. Software for this CPU was written in order to provide communication links to a host, using the protocol developed in chapter 6. The processor also controls the DMA-readout process, and is capable of automatically monitoring on-board modules. This software is described in this chapter, and possible future development is outlined.

#### Chapter 8 - System Testing

This chapter details the testing performed of the developed system. The functionality and reliability of the communication links and the embedded software in general is verified, the modules present on the current system are tested, and so is the readout solution developed in chapter 5. Finally, the full readout chain is tested.

#### Chapter 9 - Discussion and Conclusion

This chapter discusses the results of this thesis, evaluates design choices made, and provides a discussion on future development of the pCT project.

#### Chapter 2

## Computed Tomography

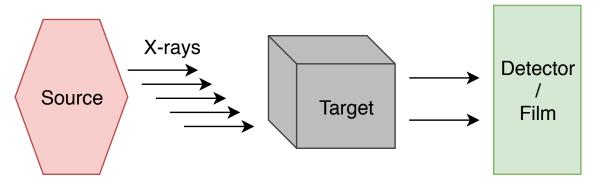

Conventional computed tomography (CT) is based on radiography. In 2D radiography, high-energy X-rays are produced by a generator and passed through a target to be imaged. Part of the radiation is absorbed in the target, while the remainder passes through, impacting what is typically either a film or detector. The X-ray beam is attenuated to varying degrees by the different materials that make up the target, which is reflected by the image formed on the film or by the detector.

Figure 2.1: 2D radiography showing source, target and detector setup.

Computed tomography builds upon this principle by combining several such images taken from different angles. This is typically done by moving the target along one axis, around which the detector and source are simultaneously spun or vice-versa. The end result, after processing, is a series of cross-sectional images which can be processed further, forming a three-dimensional image of the volume. The technology is in wide use, and in 2007 in the US alone, more than 60 million such scans were performed [2]. In addition to diagnostic imaging, CT as already mentioned sees broad application as a technology to aid in radiation- or particle therapy treatment planning.

#### 2.1 Ionizing Radiation

A criticism of the widespread use of CT for imaging purposes has been its adverse health effects due to the ionizing effects of X-rays [2]. This use has been linked to irradiated patients experiencing a higher rate of cancer development than those not exposed, and younger patients seeing a further increased risk [3] [4]. These effects stem from the ionizing radiation produced by a CT, which in general is any form of radiation sufficient in energy to liberate electrons from the nuclei they orbit. This can occur both when the electrons are impacted by other subatomic particles, or through their interactions with photons. The effect of this when it occurs within tissue is cellular degradation through damage done to DNA and other cell structures; it is thus an undesired side-effect of imaging, but forms the basis of particle-/photon therapy.

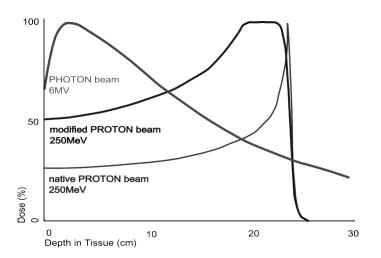

Figure 2.2: Showing the dose delivered by a beam of photons, *modified*- and *native* protons as they pass through tissue.

#### 2.2 Interactions of Photons and Matter

As photons enter a physical medium, they interact with it via three central methods; they are absorbed by it through the photoelectric effect, scattered via Compton- and Rayleigh scattering, or cause pair production to occur.

Of these, primarily the first two are relevant in relation to CT as the latter typically occurs at energies higher than those used for imaging. In the photoelectric effect, a passing photon with sufficient energy<sup>1</sup> ejects orbiting electrons from their nuclei. Compton-scattering describes inelastic collisions between incoming photons and orbiting electrons<sup>2</sup>, where some of the photon energy is transferred to the electron (which are in this case not ejected). The photons then scatter away at some angle.

The effects cause a beam of photons to deposit its energy almost linearly as it passes through a medium, and the affected photons are effectively removed from the beam.

<sup>&</sup>lt;sup>1</sup>As governed by  $E_k = hf - \phi$ , with  $\phi$  being the *work function*, representing the binding energy of the electron and therefore the lowest energy a photon that ejects the electron may have.

<sup>&</sup>lt;sup>2</sup>With the photon post-collision possessing energy equal to  $E'_{\gamma} = \frac{E_{\gamma}}{1 + (E_{\gamma}/m_e c^2)(1 - \cos(\theta))}$

#### 2.3 Interactions of Particles and Matter

Protons deliver their energy to surrounding matter via several mechanisms; through their interactions with electrons via the Coulomb force or atomic nuclei, Bremsstrahlung, or nuclear reactions. Of these, their interactions with electrons cause the majority of their energy loss. Below is the Bethe-formula, describing the loss of energy as charged particles pass through a medium:

$$-\frac{dE}{dx} = \frac{4\pi}{m_e c^2} \cdot \frac{nz^2}{\beta^2} \cdot \left(\frac{e^2}{4\pi\epsilon_0}\right)^2 \cdot \left(\ln\left(\frac{2m_e c^2\beta^2}{I\cdot(1-\beta^2)}\right) - \beta^2\right), \quad \beta = \frac{v}{c}$$

From this it can be seen that the energy loss of the particles *increases* as  $\frac{1}{v^2}$ . This attribute gives rise to the characteristic *Bragg-peak* of protons as shown in figure 2.2, displaying the Bragg-curve of two proton-beams.

#### 2.4 Particle Therapy and Proton CT Motivation

The phenomenon of the Bragg peak is exploited in particle therapy to deliver ionizing radiation to a localized area. Typically the target is a tumor, which the radiation is intended to damage by ionizing the cells of which it consists.

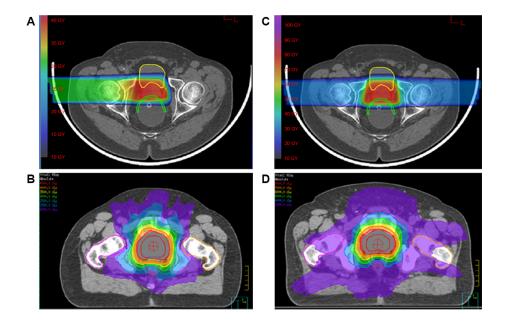

The focused Bragg peak of particles can thus be used to deliver doses that are more precise than their photon counterparts. This is seen in figure 2.3, showing dosimetric planning with protons (top) and photons (bottom). Image A shows the expected dose deposition using a single lateral beam while image C shows the result if two opposing sources are used. The two bottom images show treatment with X-rays at different intensities.

Figure 2.3: Comparison of dosimetric planning with protons (top) to photons (bottom) [5].

Typically, a proton beam used for this purpose consists of protons at varying energies. This causes their Bragg-peaks to appear at different depths in the tissue, allowing an entire tumor to be irradiated. This is the cause of the appearance of the *spread-out-bragg-peak* (SOBP) for the modified proton beam seen in figure 2.2.

#### 2.4.1 Proton CT

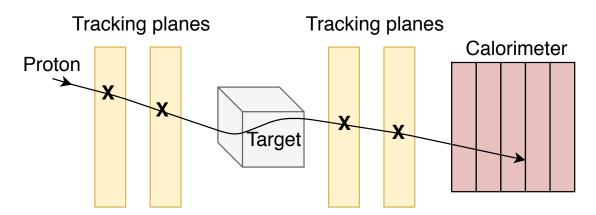

A central difference that separates conventional CT from proton-based CT stems from the interactions described in the previous sections. Photons either pass through the target *completely*, or are absorbed, whereas particles collide on their way through. This causes them to scatter and exit the target at an angle different to the one at which they entered, and with their kinetic energies reduced. For proton imaging, *tracking planes* are therefore also required so that the proton tracks can be recorded, and these are typically placed behind as well as in front of the target. From these measurements, the most-likely-path (MLP) of the particles are estimated, while the residual energies are calculated by a separate calorimeter.

Figure 2.4: Typical pCT layout, showing separate tracking planes and calorimeter and the path of a proton.

Whereas particle therapy requires the protons to stop in the area of the tumor, Proton CT requires the protons to pass through so that their bragg peak appears in the residual-energy detector. pCT thus require beam energies in excess of that used for therapeutic purposes.

It was mentioned that a calculated particle dose is based on a translation process. This involves observing the attenuation of X-rays (represented by Hounsfield Units, or HU) as it is passes through tissue, and converting this to proton relative stopping power, or RSP. This introduces range inaccuracies on the order of 2-3% [6]. These inaccuracies must be accounted for, and this is typically done by making the treatment robust so that the focused Bragg peak is not fully utilized.

A pCT as shown above eliminates the errors introduced by the HU - RSP conversion by providing a *direct link* between imaging and therapy, while minimizing damage to healthy tissue due to the Bragg peak and hence the majority of the deposited energy appearing external to the target to be imaged. Energy deposition is low with pCT; a head scan performed by a pCT showed only 1.39 mGy delivered [7], while a head scan performed with the conventional type was in one case found to be approximately  $57 \,\mathrm{mGy}$  [8].

#### Chapter 3

# The UiB pCT and the ALPIDE Pixel Sensor

Accurate reconstructions of proton-trajectories as they pass through a medium in addition to measurements of their residual energies are needed when using a pCT for dosage planning purposes. The prototype under development at UiB will achieve this by layering square arrangements of CERN-developed monolithic pixel sensors that are sensitive to incidental photons and particles which exceed a set energy-threshold. This chip is described in some detail in this chapter<sup>1</sup>, as is the general design of the UiB pCT as it currently stands.

The ALPIDEs used in the UiB pCT will serve *both* tracking- and energy deposition measurement purposes. In this respect the system will differ from many other designs, which typically use separate instruments to fill the two roles. However, it is important to note that the ALPIDE itself is not a calorimeter, and that energy deposition is calculated by observing the number of layers that are penetrated by a proton.

#### 3.1 The ALPIDE Pixel Sensor

The ALPIDE is a particle detector originally designed at CERN for use in the ALICE experiment as part of the upgrade of the Inner Tracking System (ITS) [9]. It is capable of detecting particles and photons via a  $512 \times 1024$  array of sensitive pixels, where each pixel consists of a sensing diode where a voltage appears as incidental high-energy photons and particles ionize its surrounding area. In addition, the chip contains an amplification-, shaping-, and discriminator stage as well as a digital section. This pixel-matrix is mounted on an ASIC that facilitates data-transfer, chip-control, and power-distribution.

<sup>&</sup>lt;sup>1</sup>The given descriptions are largely based on the ALPIDE Operations Manual [10].

#### 3.1.1 Basic Principles of Operation

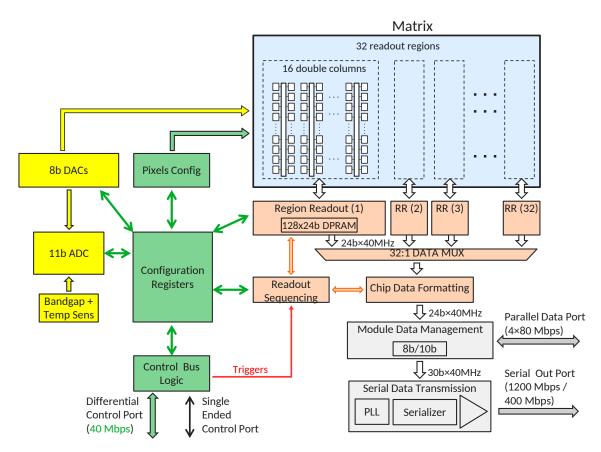

Figure 3.1 shows an ALPIDE block diagram. It displays the pixel array as separated into regions sixteen double-columns wide, where each white square in a double column contains a pixel. The vertical bars splitting the double columns contain priority encoders that control the order in which pixel data is read out. As hits are registered they are first buffered in RAM, and afterwards passed to the data transmission unit (DTU) (shown in gray), where they are framed, 8b10b-encoded, and transmitted on a high-speed serial link at a configurable speed.

The green blocks containing control-related functionality as well as the DTU show two sets of inputs. Which of these are used depend on the ALPIDE configuration.

Figure 3.1: Block diagram showing the main components of an ALPIDE chip [10].

#### 3.1.2 Pixels

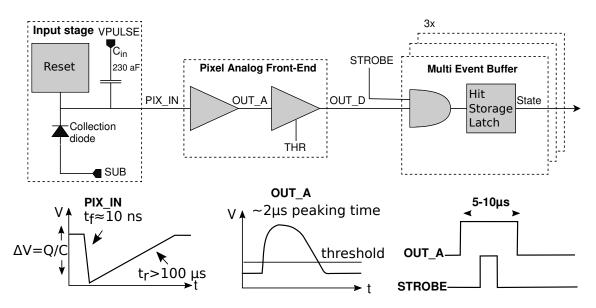

Each pixel in the array contains a sensing diode placed at the input to an analog stage which discriminates on the voltage at this diode<sup>2</sup>. A bias voltage can be adjusted to increase or decrease the discrimination threshold, and voltages that exceed it cause the active-low output to be applied to the digital section. If the input to this section is low while a strobe signal is high, it is stored in the multi event buffer

<sup>&</sup>lt;sup>2</sup>For testing purposes, a signal can also be induced by charging a test-capacitor at this input, while a digital pulse can be applied to the digital section to directly set the pixel state register. Both can be used to force a "hit".

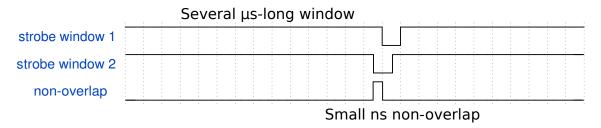

(MEB) and can be read out as a "hit". The generation of a strobe signal follows from the reception of a trigger, which, depending on chip configuration can either cause strobes to be generated continuously afterwards (*continuous mode*), or only once (*triggered mode*). The strobe-window duration is configurable, and can be set between 25 ns to 1638.4 µs. Up to three hits may be stored in the MEB; if a window is asserted that will place a hit into a second (in the triggered mode) or third (in the continuous mode) buffer-slot, the chip produces a BUSY-signal, causing further triggers to be ignored until the MEB is below this threshold.

Figure 3.2: Showing how a voltage on the input to the analog section cause a hit to be stored in the pixel buffer if it surpasses a threshold while a strobe is applied [10].

#### 3.1.3 Data Transmission Unit

The DTU provides a fast serial link for readout of pixel data. The ALPIDE can be used in two different configurations: *Outer Barrel (OB)*- and *Inner Barrel (IB)* mode, but is only used in the latter in the UiB pCT. In this case, each chip transmits 8b10b-encoded data via low voltage differential signaling (LVDS) at a max rate of 1.2 Gb/s. Without decoding, this corresponds to a 960 Mb/s data rate. Data rates of 600 Mb/s and 400 Mb/s are also possible in this mode.

#### 3.1.4 ALPIDE - Readout Unit Interface

In the IB-configuration, nine ALPIDEs are mounted together on a *stave*. In this arrangement, the pixel detectors share a global differential 40.08 MHz clock which is multi-dropped to the chips. A differential control line (*slow control*) is also shared amongst the ALPIDEs that provides access to the 16 bit address-space of a chip, where control-commands are addressed either to a single chip via a chip ID system, or to an entire stave via *multicast*. Readout-data is sent off-chip via differential links unique to each ALPIDE at one of the three possible speeds.

#### 3.1.5 Control Interface and Chip Addressing

One of the inputs on the ALPIDE is the seven-bit chip ID. Chips in the IB configuration shall have the three most significant bits of this input set to 0b000 to designate them as such, while the four least significant bits assign a unique identifier, which is then used when addressing it via slow-control.

#### Protocol

Transactions via slow-control are by default manchester encoded to facilitate ACcoupling, which can be toggled by writing to an ALPIDE register. Data sent via the differential control line consists of 10 bit wide characters; beginning and ending respectively with a low start- and stop-bit, and having a byte of payload between the two. Several operations consisting of one or more characters are supported, which are identified by an initial opcode. These operations are shown in figures 3.3 and 3.4. A *multicast* write is performed on all chips on a stave.

| IDLE BROADCAST OPCODE IDLE                                                                     |                  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|--|--|

| ← MASTER DRIVER ON ←                                                                           |                  |  |  |  |  |  |  |  |

|                                                                                                | MASTER DRIVER ON |  |  |  |  |  |  |  |

| TRIGGER COMMAND                                                                                |                  |  |  |  |  |  |  |  |

| IDLE TRIGGER IDLE                                                                              |                  |  |  |  |  |  |  |  |

| MASTER DRIVER ON                                                                               | ;                |  |  |  |  |  |  |  |

| → Fast Trigger Decoding                                                                        |                  |  |  |  |  |  |  |  |

|                                                                                                |                  |  |  |  |  |  |  |  |

|                                                                                                |                  |  |  |  |  |  |  |  |

| UNICAST WRITE                                                                                  |                  |  |  |  |  |  |  |  |

| IDLE WRITE OPCODE                                                                              | LE               |  |  |  |  |  |  |  |

|                                                                                                |                  |  |  |  |  |  |  |  |

| MULTICAST WRITE                                                                                |                  |  |  |  |  |  |  |  |

| IDLE WRITE OPCODE & MULTICAST ID & REG ADDR [7:0] B REG ADDR [15:8] B DATA [7:0] B DATA [15:8] | LE               |  |  |  |  |  |  |  |

| MASTER DRIVER ON                                                                               | >                |  |  |  |  |  |  |  |

Figure 3.3: Showing the format of ALPIDE broadcasts and uni-/multicast write operations. [10].

Figure 3.4: Showing the format of an ALPIDE read operation [10].

The *bus-turnaround phase* shown in figure 3.4 requires the master to stop driving the bus for fifty clock cycle in order to allow the chip to respond to the received request.

#### 3.2 The UiB pCT

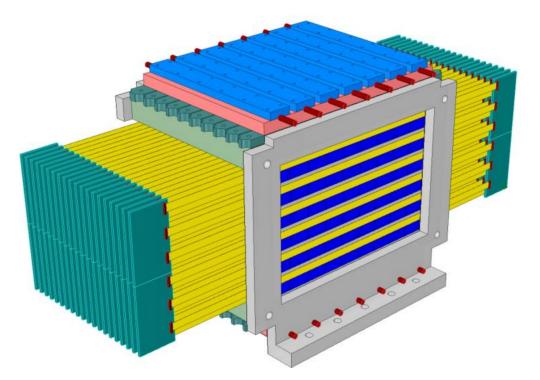

The UiB pCT will utilize the ALPIDEs both for tracking- and energy measurements, and only in their IB configuration as this allows for the highest data rate and for the chips to mounted in the stave configuration. Several staves can then be mounted in parallel, forming a square arrangement in what is referred to as a *layer*.

A number of detector- and aluminum absorber layers that decelerate the protons will be sandwiched together and fixed in a support-structure that combined will make up the DTC; the detector structure enabling tracking- and energy deposition measurements of the protons.

Figure 3.5: A model of the UiB pCT DTC, with ALPIDE chips in a horizontal stave configuration shown in dark blue [11].

The tracking layers will not be external to the DTC, but will instead be realized by excluding the absorbing layers between the two foremost detector layers. These will then perform the tracking, while the remaining layers act as the calorimeter. The implementation of the rear tracking planes is not yet decided, but these will likely also be ALPIDE-based. The light-blue bars on the red plate seen at the top of the structure facilitates cooling of the DTC.

#### 3.3 Existing pCT Systems

Several prototype designs have been developed in the recent years due to the increasing use of particle therapy, with the majority of these being of the type with separate tracking instruments and calorimeters. One example is a head scanner using 200 MeV protons developed at the Loma Linda University Medical Center [12].

The machine is capable of measuring more than 1 million protons per second, enabling a scan to be performed in 7 minutes, making it one of the fastest currently available pCTs. A phantom<sup>3</sup> is rotated between two silicon-strip tracking stages, and residual energy is measured via a final scintillator stage. Table 3.1 lists some additional systems and their basic specifications.

Table 3.1: Illustrating some basic specifications of previously developed pCTs [13].

| Group Position sensitive<br>detector technoloy |            | Residual energy<br>detector technology | Proton rate<br>(Hz) |

|------------------------------------------------|------------|----------------------------------------|---------------------|

| LLU/UCSC/NIU                                   | x-y SiSDs  | Csl calorimeters                       | 15K                 |

| LLU/UCSC/NIU                                   | x-y SiSDs  | Plastic scintillator hybrid telescope  | 2M                  |

| PRIMA II                                       | x-y SiSDs  | YAG: Ce calorimeters                   | $1\mathrm{M}$       |

| INFN                                           | x-y Sci-Fi | x-y Sci-Fi                             | $1\mathrm{M}$       |

| NIU/FNAL                                       | x-y Sci-Fi | Plastic scintillator telescope         | 2M                  |

Compared with existing systems, the very high readout speeds that are possible with the ALPIDEs will represent one of the prime advantages of the UiB prototype. This has the effect of greatly reducing the time needed to perform a full scan, making the UiB design very efficient. In addition, the fine granularity of the pixel arrays should provide high spatial resolution.

#### 3.4 Readout Electronics

Readout-data produced by the ALPIDEs, as well as their slow-control signals, will interface to electronics located on the pCT Readout Unit (PRU), of which there will be several. Each board will contain a Xilinx FPGA that centrally will be used to process detector-data as it is streamed to the unit in the form shown in table 3.2.

| Data Word        | Length (bits) | Value (binary)                                                                                    |

|------------------|---------------|---------------------------------------------------------------------------------------------------|

| IDLE             | 8             | 1111_1111                                                                                         |

| CHIP HEADER      | 16            | 1010 <chip_id[3:0]<bunch_counter_for_frame[10:3]></chip_id[3:0]<bunch_counter_for_frame[10:3]>    |

| CHIP TRAILER     | 8             | $1011 < readout_flags[3:0] >$                                                                     |

| CHIP EMPTY FRAME | 16            | 1110 <chip_id[3:0]><bunch_counter_for_frame[10:3]></bunch_counter_for_frame[10:3]></chip_id[3:0]> |

| REGION HEADER    | 8             | $110 < \text{region}_id[4:0] >$                                                                   |

| DATA SHORT       | 16            | $01 < \text{encoder}_id[3:0] > < \text{addr}[9:0] >$                                              |

| DATA LONG        | 24            | $00 < \text{encoder\_id}[3:0] > < \text{addr}[9:0] > \_0\_< \text{hit\_map}[6:0] >$               |

| BUSY ON          | 8             | 1111_0001                                                                                         |

| BUSY OFF         | 8             | 1111_0000                                                                                         |

Table 3.2: ALPIDE readout-data format before processing on the PRU [10].

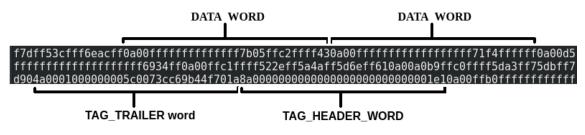

Each ALPIDE will connect to its own ALPIDE data module, which handles a large part of this process. It performs 8b10b-decoding, filters out the IDLE-words produced by a chip when no data is ready for readout, packets data according to a custom format (*PRU words*), and monitors the busy-signal produced by a chip if it is unable to process additional hits. Several words will be buffered in block RAM (BRAM) FIFOs and afterwards forwarded to a data-readout stage where the data is streamed off-board; likely over Ethernet.

Communication between the ALPIDEs and PRUs as well as chip trigger-delivery

$<sup>^{3}</sup>$ An object used to evaluate and tune the performance of medical imaging devices.

will be facilitated by the CERN-developed<sup>4</sup> ALPIDE Control Module (ACM) that interfaces the shared stave control line and handles the distribution and timing of the commands shown in figures 3.3 and 3.4. Operations on a chip are performed following a three-step process, where a chip-write is performed by writing the registeraddress and value to two of the module's registers, and triggering the execution of the operation by writing the chip ID and write-opcode to a third. A read requires only an address and the triggering write, with the value at the requested address available in a further control module register. With a layer size of 108 detector-chips, each PRU FPGA will require 12 of these blocks.

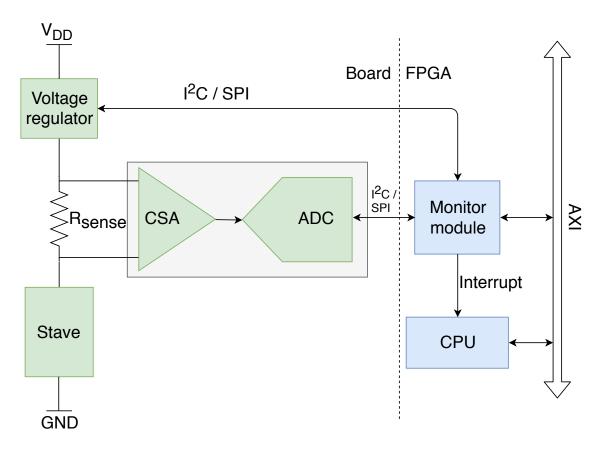

To control the PRU devices in general, and to provide a direct or indirect control link with a host, a master control module is required. This will also be responsible for the configuration of PRU modules on startup, automatic power- and temperature monitoring, and possibly other tasks. This module and its implementation is discussed thoroughly in the following chapters. There will also be a block that interfaces to the external voltage regulators that supply the ALPIDEs, allowing control of these and providing the host with monitoring data.

The ALPIDE trigger source will be a device external to the PRUs, and may also be responsible for distributing a synchronized clock to the readout units. The implementation of this module is not yet decided, but possible alternatives are discussed in chapter 4.

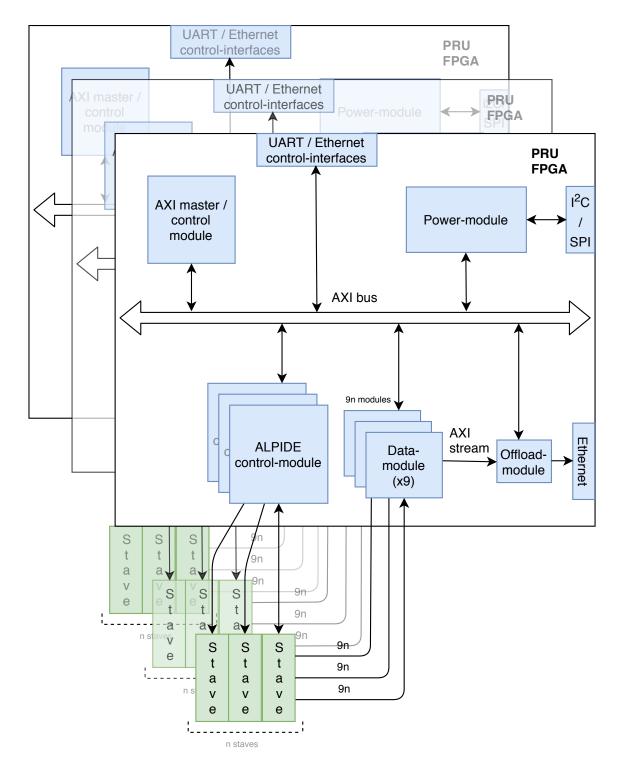

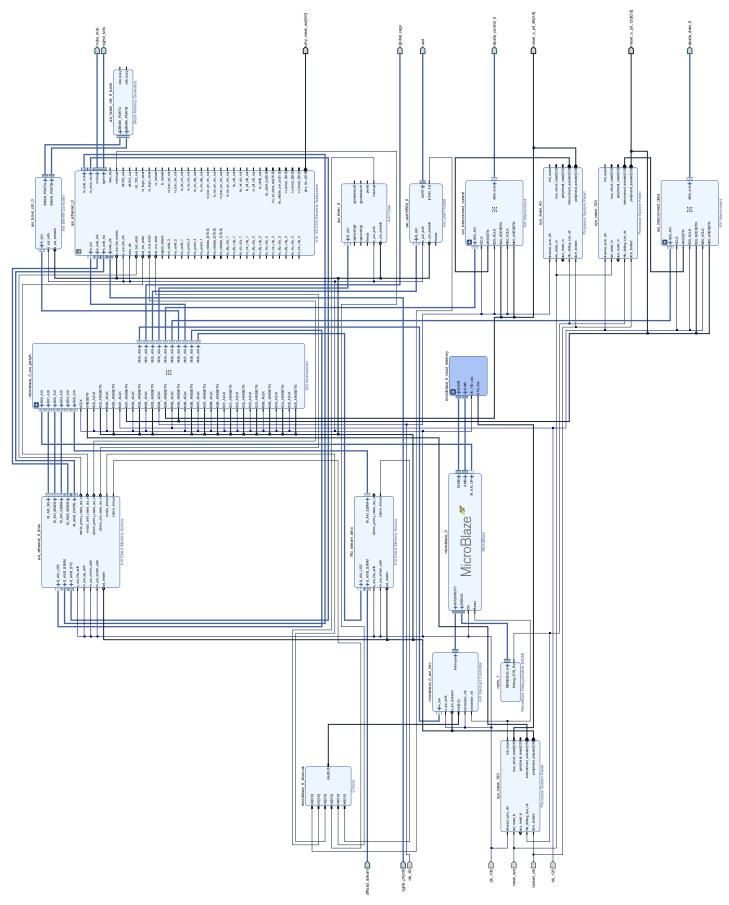

Ideally each unit will handle one ALPIDE layer although this will dictated based on the amount of readout-data produced. Additionally, all modules on the PRU FPGAs will be compliant with the Advanced eXtensible Interface (AXI) standard, which simplifies connectivity as it is supported by all Xilinx IP, and also allows for automatic generation of interconnects between modules, and for these to automatically handle any clock-domain-crossings. A block diagram of the PRU FPGAs is shown in figure 3.6.

#### 3.4.1 Current Implementation

While the PRUs that will be installed in the complete pCT prototype will consist of custom boards, current work is being done using a VCU118 development board on its Xilinx Virtex Ultrascale+ VU9P FPGA. Any implementations that were made as part of the work done in this thesis were made on this device. When work was started, the design included a single ACM and ADM, and a connection to an ALPIDE is provided via a custom FMC, interfacing to a FireFly-to-PCIe adapter, which in turn connects to the ALPIDE carrier board.

$<sup>^4 \</sup>rm Since modified by Ola Slettevoll Grøttvik (ola.grottvik@uib.no) to be AXI-compliant, whereas the original was a Wishbone-module.$

Figure 3.6: The PRU, showing the most central modules of the currently planned design.

## Chapter 4

# The pCT Control System

In the complete pCT, each PRU will contain a multiple of several of the modules discussed in section 3.4, and a subsystem on the PRU that allows for complete control and monitoring of these is required. This involves in part the design and implementation of the AXI master control module located on the readout boards, any additional firmware this requires, as well as host-side software that interfaces to this module and allows for visualization and remote control. The master control module can be either embedded within the FPGA, or be an external unit. In any case, the system will be responsible for the following:

- Implementation of protocols for PRU AXI master host (control room, testing setup, etc) communication.

- Facilitation of communication between the AXI master and all modules on the PRU.

- Initialization of the readout boards: on power-up, automatically configure devices present.

- Provision of assistance related to procedures such as data-readout.

- Provision of house-keeping data for monitoring and logging purposes.

- Application of chip-specific configurations for the ALPIDEs. Possibly streamed to the master-device or collected from on-board memory.

- Automatic monitoring of chip- and board currents and voltages.

The system may be required to fulfill additional roles, and a design must be flexible enough to accommodate this. In addition, the PRUs will interface to the control room either directly or through some other device, and making this interface simple is therefore an additional consideration. This will reduce the need for specialized hardware, and allow use of tried-and-tested protocols. This chapter further specifies the requirements of such a system, considers several options for its design, and proposes some alternatives. The realization of a complete control system lies outside the scope of this thesis, but core elements are developed, implemented and tested, and are described in chapters 5, 6, 7, and 8. Future extensions and alterations are also discussed towards the end of their respective chapters. During the design process, emphasis was placed on developing a scalable-, self-sufficient-, and flexible system that could be used by itself in the development- and testing phase, and further built upon for use with the finished product.

## 4.1 Features of a pCT Control System

### 4.1.1 RU - Host Interface

For a host to communicate with the PRUs, data must be transmitted to the controlunit on the readout-boards over a suitable interface such as Ethernet, USB, RS-232 or others. RS-232 defines electrical signal characteristics such as voltage levels and timing, as well as the properties of related mechanical connectors and the circuitry [14]. Signals are transmitted over a single wire, limiting transmission distance and resulting in poor signal integrity. The high voltage swings limits performance, and there is no concept of addressing. RS-422 is a similar standard, but has a lower swing, operating between -6V and +6V, which improves signaling-rate. Differential signaling is used, which enhances noise immunity<sup>1</sup>. Still, the upper data-rate of RS-422 is 10 Mb/s, and if, during the development stage, detector-data is to be read out over the same link as the control- and monitoring data, then this will not suffice. Again, there is no built-in concept of addressing, which would have to be developed. RS-485 is in many ways similar to RS-422, but can be multidropped to several devices. The 10 Mb/s bandwidth must however be shared amongst the connected devices.

USB can provide much better throughput, but is unsuitable for transmission over longer distances; although the standard does not explicitly define an upper limit to cable length, it defines the electrical characteristics it must meet, which puts an upper limit at around 1.2 m. PCIe is an additional option, which offers performance up to 126 Gb/s if using third generation PCIe and 16x links. PCIe over cable is possible, and mounting the board in a specialized enclosure is therefore not necessary, although a PCIe card on the host side that interfaces with such a cable is. This introduces some complexity and cost. For control, there is no need for such performance, and sourcing and purchasing the cabling and interface card would be problematic for development. Range is limited if copper cabling is used, but Samtec for instance offers third generation PCIe over optical at ranges up to 300 m at 4x or 8x link-widths [15].

Ethernet is a family of protocols and standards that defines physical interconnects and cabling, the discrete transmission of data in the form of *Ethernet frames*, addressing schemes, and error checking. On top of Ethernet the TCP/IP protocol suite is often used, which handles aspects of addressing, lost frames (depending on

<sup>&</sup>lt;sup>1</sup>Noise that is picked up by one wire will be picked up by the second to an almost equal degree. As the "signal" is interpreted as the difference between the two, the noise is cancelled out.

transport protocol), routing, checksums and congestion handling. Generally, the lower levels consist of pre-existing firmware/software solutions while the user implements or uses a specific application-layer protocol. Compared to the alternatives listed above, Ethernet is more demanding in terms of implementation on the PRU side, and real-time control and monitoring, if this is wanted, is generally not possible. However, interfacing Ethernet requires only twisted pair cable and a network switch. Multiple applications may also transmit over a single Ethernet link through the use of sockets, allowing in this case both control- and readout-data to be transmitted through the same cable, during the early stages of the project.

For control, Ethernet is a suitable choice, providing speed, flexibility in terms of use (control and data-readout) and expansion, ease of setup, low cost, and offering existing communication protocols for all levels. A serial UART interface should also be available in order to provide a simple debugging channel for each board.

Relaying control-data to individual readout units via a *master PRU* and other indirect host - board interfaces are also possible, but it can be argued that a direct channel between each board and host provides both better flexibility as well as simplicity of implementation; The master PRU would mandate the design of a separate board, and separate interfaces between host - PRU and PRU - PRU would have to be developed.

### 4.1.2 Board Initialization

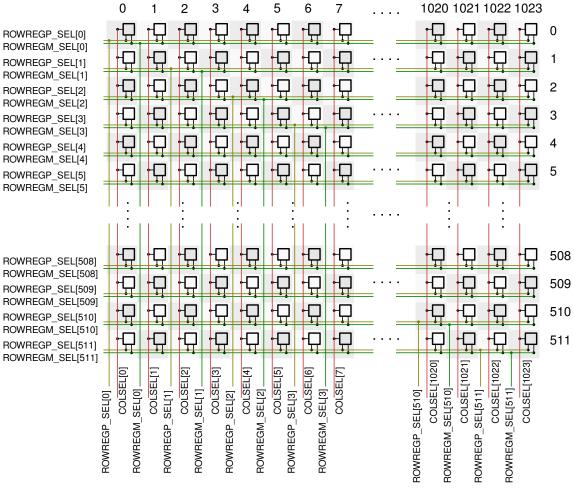

The PRU modules must be configured on start-up, or on reception of one or more commands instructing this to be performed. For an ALPIDE, initialization consists of a register programming sequence and the application of a pixel-mask that is applied in order to exclude noisy or otherwise defective pixels from readout. The AXI-master is responsible for carrying out these procedures, and could possibly do so by using chip-specific settings stored in on-board flash memory. However, local storage of configurations will likely not be necessary, which can be argued by first noting that for each ALPIDE there are only eighteen periphery control- and fifteen DAC registers that must be set, as well as one ADC control register that must be configured with chip-specific settings. Mask-application is a more comprehensive task, and the number of operations required to apply these will vary based on the number of defects in the chips. All 524288 pixels can in theory be masked on an individual basis (see section E.1 for a brief overview of this process), but the addressing scheme used to access the pixels is implemented in a manner that reduces the number of necessary write-operations. This allows masking of even a significant number of pixels in an efficient manner.

| Configuration address bus    |             |                          |          |          |               |                           |                         |                             |                            |

|------------------------------|-------------|--------------------------|----------|----------|---------------|---------------------------|-------------------------|-----------------------------|----------------------------|

| Region Selector Field < 4:0> | 3'b100      | Region<br>Broad-<br>cast | Not Used | Not Used | Toggle<br>Bit | Pulse<br><15:0><br>Select | Row<br><15:0><br>Select | Column<br><31:15><br>Select | Column<br><15:0><br>Select |

| Bit < 15:11>                 | Bit < 10:8> | Bit 7                    | Bit 6    | Bit 5    | Bit 4         | Bit 3                     | Bit 2                   | Bit 1                       | Bit 0                      |

Figure 4.1: The pixel-matrix addressing scheme [10]. Writing 0xFFFF to the address formed by the region selector field set to 0b1111 and the row bit and both column bits set would for instance mask/clear all pixels, depending on the pixel configuration register.

In other words, the amount of data that must be written in order to configure a chip is not excessive. Configurations may also change over time, and if data is stored onboard, it would have to be updated on a per-board basis. It is likely that updating a central repository will be easier to manage. Instead, ALPIDE-specific settings could be kept in a database and applied from the host side. Ignoring any protocol-specific overhead, the amount of data needed to configure each chip can be estimated:

The width of the ALPIDE address space as well as its registers is 16 bits. In addition, a control value of 16 bits must also be written to the control module. The transaction is performed on the 32 bit AXI bus however, and therefore 24 B must be written per write-transaction. If a particularly bad detector requires, for instance, a third of its pixels to be masked, the amount of data that would need to be provided to the ACM would be approximately:

$$24 B \times 3 \, operations \times \frac{N_{pixels}/16}{3} \approx 0.78 \, MB$$

30 % is in essence a non-functional detector, so this number is pessimistic. Additionally, the ALPIDE addressing scheme allows for several rows, columns or regions to be masked simultaneously, which might often be the case if pixels are malfunctioning. For instance, the ALPIDE chip that was used to test the systems developed in this thesis has one entire inoperative column.

If configuration data is stored on-board, the overhead in the above operation does not need to be stored. Masks could be represented as a group of 32 bit unsigned integers, with each bit of an integer indicating whether or not to mask a pixel. Each ALPIDE would then need 65.5 kB to store a complete mask, and an additional 136 B (approximately) to store the remaining registers. A layer consisting of 108 ALPIDEs would then require 7.09 Mb of data in total.

#### **Board Configuration Times**

Some estimations should be made regarding the time required to complete the procedures mentioned in section 4.1.2, as it could dictate whether configuration data should be stored on-board or streamed to each unit.

The majority of the modules on the AXI bus require little configuration, possessing only a few registers each. Likewise, setting the periphery control-, DAC- and the chip-specific ADC registers on the ALPIDEs is not an extensive procedure. As such it is the pixel masks that will require the largest amount of configuration data. An estimate on the time required to perform this procedure can be found by first noting that the ALPIDE write-operation equates to  $1.8 \,\mu\text{s}/\text{pixel}^2$  if the module is operating on a 40 MHz clock. Masking the pixels of the hypothetical ALPIDE would then complete in about 0.019 s, or 2.12 s for a layer of size 108, again without regards to the master control module overhead.

If configuration data is streamed to each board by sending the AXI addresses and data to write to the ACMs, this equates to 72 bytes per group of 16 pixels, excluding

$<sup>^{2}3</sup>writes \times 3operations \times (((7+1)cycle)/write)/40MHz \approx 1.8 \,\mu s.$  7 cycles are needed to initiate an AXI transaction, while 1 cycle is needed to transfer the data bits.

any protocol overhead, as stated. With 0.78 MB of data required in order to apply a mask, a layer of size 108 would require 84.9 MB of data to be streamed to the PRU in this case. On saturated 10 Mb, 100 Mb, or 1000 Mb links, this would take 67.2 s, 6.72 s, or 0.672 s, respectively, to transfer. These are all acceptable numbers, and more effective ways of transferring this data is possible, as the majority in the above estimations stem from overhead. In any event it is desirable to minimize time spent on the configuration stage, although gigabit transfer rates if using a soft core processor at a relatively low clock rate are unlikely.

### 4.1.3 Provision of House-Keeping Data

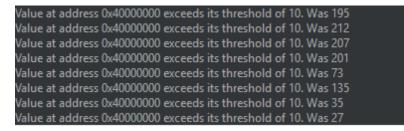

The ALPIDE is equipped with a 10-bit ADC, which after calibration provides values of chip temperature as well as all its voltages and currents. For monitoring-purposes, these must be read out, with the calibration procedure performed by either the master control module or the host. The conversion between raw ADC register values and corresponding units requires some floating point arithmetic, but the amount is small enough<sup>3</sup> that it can be performed by the on-board master control module, even if this is a low-performance soft core CPU. The control-unit can either provide these values automatically, or as a response to a request.

### 4.1.4 ALPIDE Monitoring