# Single Event Upsets in SRAM FPGA based readout electronics for the Time Projection Chamber in the ALICE experiment

Ketil Røed

Thesis for the degree of Philosophiae Doctor (PhD) at the University of Bergen

September 23, 2009

## Acknowledgements

My time as a doctoral student has finally come to an end with the submission of this thesis. During the last years I have been given the opportunity to work on the interesting and challenging subject of radiation effects in semiconductor devices. Being part of CERN and the ALICE collaboration has been a door opener to a large group of international experts. This has not only given invaluable input to my thesis but also resulted in many new friends with whom I never would have met otherwise. Even though there have been moments of hard work and lack of motivation, looking back it has still been a great experience.

Many people deserve special thanks for their support and contribution. First of all I would like to thank the Faculty of Engineering at Bergen University College for employing me and giving me this opportunity. The PhD has been carried out in a joint collaboration with the doctoral student program at the Department of Physics and Technology, University of Bergen. Many thanks to my supervisors Kjetil Ullaland at the University of Bergen and Håvard Helstrup and Terje Natås at the Bergen University College.

Dieter Röhrich deserves special attention for his major contributions regardless of not being one of my official supervisors. His experience and network of contacts has been of crucial importance to the progress of my work. Realizing this thesis would have been very difficult without his involvement.

Sharing my time between the two institutions I have to thank Håvard for his continuous effort in making any related administrative aspects of this as transparent as possible. I am also grateful for his positive thinking and support during my PhD thesis work. In particular his encouragement and detailed feedback during the writing phase has been an important contribution to finally completing my thesis.

Already having Kjetil Ullaland as the supervisor of my Master thesis project, I was happy to see him also take on the same responsibility for my PhD. Through our many fruitful discussions he has been a main source of knowledge and inspiration. With his direct approach and know-how he has encouraged me to take responsibility and helped me to stay focused and on track.

Throughout my PhD period I have had the pleasure of working closely with Jo-

han Alme. Sharing not only some of the same tasks, but also a number of offices and Maryland cookies together, there was never a dull moment. He has been an important motivator and friend and I hope that the future will bring new possibilities of working together. I would also like to thank Kenneth Aamodt, Sebastian Bablok, Dominik Fehlker, Kalliopi Kanaki, Dag Toppe Larsen, Matthias Richter, Boris Wagner, and Gaute Øvrebekk for numerous and helpful discussions on topics like ROOT, C++, programming in general, and ALICE physics. Torsten Alt and Gerd Tröger should also be mentioned for their contributions and many interesting discussions. In particular also for the extracurricular activities when visiting Heidelberg. Solfrid Sjåstad Hasund and Rune Fosse are thanked for their contribution to my teaching responsibilities at the Bergen University College. Additionally I would like to thank my other colleagues at the Department of Physics and Technology at the University of Bergen and at the Bergen University College who have contributed in one way or the other.

A special thanks must be given to Henry Tang, Kenneth Rodbell, Conal Murray, Giovanni Fiorenza and their colleagues at the T.J. Watson IBM Research Center in Yorktown, New York, USA. I am grateful to Henry for always giving of his time and being an endless source of information through our many and long discussions. During my 7 months visit in their group I gained a significant amount of knowledge in physics based Monte Carlo simulations and related topics. The Norwegian Research Council should also be thanked for financially supporting this visit through the Leiv Eiriksson mobility programme. Moreover, I have to thank Jennifer Hill for her generous hospitality in addition to the rest of the gang living in Overlook Road. Thank you for making my stay in the US a memorable one.

From the Institute of Experimental Physics SAS, Košice, Slovak Republic and CERN, I have to thank Blahoslav Pastirčák for his generous help and contribution to the Monte Carlo simulations of the radiation environment. Luciano Musa and his group at CERN are also acknowledged as part of the ALICE TPC collaboration and RCU project team in particular. Jon Wikne and Eivind Olsen at the Oslo Cyclotron, University of Oslo, and Alexander Prokofiev at The Svedberg Laboratory, University of Uppsala, should also be thanked for all their help during the many hours of irradiation testing I have participated in over the last years. I would also like to thank my new colleagues at CERN for their understanding during the finalizing part of my PhD thesis.

Special thanks goes to Trud for her support and kindness, and finally I am deeply grateful to my parents for their unconditional help and support during these years.

Ferney-Voltaire, September 2009

## Abstract

The front-end electronics of the TPC detector, one of the major detectors of the ALICE experiment at CERN, utilizes an SRAM based FPGA to control the readout of detector data. Compared to traditional ASIC design, an SRAM based FPGA was chosen because it offers the flexibility of in-field programmability. However, when used in radiation exposed environments, FPGAs have shown to be susceptible to radiation induced effects such as single event upsets. A single event upset is induced when a single ionizing particle deposits a sufficient amount of energy to alter the logic state of a memory element. In an SRAM based FPGA the user-programmed functionality depends on the data stored in millions of these memory elements. A single event upset in one or several of these memory cells may result in unexpected and incorrect behaviour. Consequently, for the FPGA in the TPC front-end electronics, this can potentially cause the readout of detector data to temporarily break down. It is therefore important to investigate how radiation induced failures can be reduced or even avoided if possible.

Due to its stochastic nature, a single event upset has to be treated in terms of its probability to occur. This probability is determined by the sensitivity of a memory cell to a specific type of radiation, and further what type of radiation environment it will finally be operated in. Moreover, depending on how a given memory cell is utilized by a system, a single event upset may or may not result in a detectable malfunction of that system.

The main purpose of this thesis has been to investigate these aspects for the SRAM based FPGA in control of data readout in the TPC front-end electronics. By means of Monte Carlo simulations, test procedures and mitigation approaches a major objective has been to qualify this FPGA for reliably operation in the radiation environment produced by particle collisions in the ALICE experiment.

This thesis presents updated Monte Carlo simulation of particle energy spectra and fluences in more precise locations than what has previously been done. Irradiation tests have further been carried out in order to investigate the single event upset sensitivity of the SRAM based FPGA. The results are discussed in light of independent results reported in literature. Combined, Monte Carlo simulation and irradiation test results have been used to predict the single event upset rate expected during operation in the ALICE experiment.

Due to the number of FPGAs utilized in the TPC front-end electronics, single event upsets can be a reliability concern. In order to reduce the probability of system malfunction, a reconfiguration solution was developed that enables the possibility to clear single event upsets in the configuration memory of the FPGA. Irradiation test results show that combined with additional system level mitigation techniques, this reconfiguration solution can be used to finally reduce the functional failure rate of the FPGA.

Because irradiation testing can be time consuming, costly and sometimes even technically difficult, a software based fault injection solution has been implemented without any modification to the existing hardware setup. It provides an alternative and possibly systematic method of testing how a single event upset may impact the operation of the FPGA. Test results show good agreement with comparable irradiation test results.

Finally physics based Monte Carlo simulations are discussed as an additional method to investigate single event upset in memory devices. A general methodology is presented and applied to the specific case study of the TPC front-end electronics FPGA.

## Contents

| A            | cknov | vledgments                                                 | i         |

|--------------|-------|------------------------------------------------------------|-----------|

| $\mathbf{A}$ | bstra | $\mathbf{ct}$                                              | iii       |

| 1            | Intr  | oduction                                                   | 1         |

|              | 1.1   | The ALICE experiment                                       | 2         |

|              |       | 1.1.1 Physics goals                                        | 2         |

|              |       | 1.1.2 Detectors                                            | 3         |

|              | 1.2   | The TPC front-end electronics                              | 5         |

|              |       | 1.2.1 Readout Control Unit                                 | 5         |

|              |       | 1.2.2 Choice of FPGA technology                            | 6         |

|              | 1.3   | Primary objective and main contributions                   | 8         |

|              | 1.4   | Outline                                                    | 10        |

| <b>2</b>     | Rad   | liation effects in the TPC RCU main FPGA                   | 11        |

|              | 2.1   | Single Event Effects                                       | 12        |

|              | 2.2   | Basic mechanism                                            | 14        |

|              |       | 2.2.1 Charge generation and collection                     | 14        |

|              |       | 2.2.2 Single event upsets in SRAM memory                   | 15        |

|              |       | 2.2.3 Single event upsets in the FPGA configuration memory | 16        |

|              |       | 2.2.4 The physics of single event upsets                   | 17        |

|              | 2.3   | The TPC radiation environment                              | 20        |

|              |       | 2.3.1 Particle multiplicity                                | 21        |

|              |       | 2.3.2 Previous work                                        | 22        |

|              |       | 2.3.3 Updated simulations with new geometry description    | 22        |

|              |       | 2.3.4 Discussion                                           | 25        |

|              | 2.4   | Summary                                                    | 29        |

| 3            | RC    | U radiation tolerant system solution                       | <b>31</b> |

|              | 3.1   | Partial reconfiguration                                    | 31        |

|          |               | 3.1.1 Xilinx Virtex-II Pro configuration memory             | 32                                                                                                                                                                                           |

|----------|---------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |               | 3.1.2 Configuration process                                 | 34                                                                                                                                                                                           |

|          |               | 3.1.3 Partial reconfiguration on the RCU                    | 37                                                                                                                                                                                           |

|          |               | 3.1.4 Limitations of partial reconfiguration                | 37                                                                                                                                                                                           |

|          | 3.2           |                                                             | 38                                                                                                                                                                                           |

|          |               |                                                             | 39                                                                                                                                                                                           |

|          |               | -                                                           | 42                                                                                                                                                                                           |

|          | 3.3           |                                                             | 45                                                                                                                                                                                           |

|          | 3.4           | 3                                                           | 46                                                                                                                                                                                           |

| 4        |               | elerated beam testing of the Xilinx Virtex-II Pro 7 and the |                                                                                                                                                                                              |

|          | $\mathbf{RC}$ | 8                                                           |                                                                                                                                                                                              |

|          |               | 0                                                           |                                                                                                                                                                                              |

|          | 4.1           |                                                             |                                                                                                                                                                                              |

|          |               | 0 0                                                         |                                                                                                                                                                                              |

|          |               | 8                                                           |                                                                                                                                                                                              |

|          |               | 0 0 0                                                       |                                                                                                                                                                                              |

|          | 4.2           |                                                             |                                                                                                                                                                                              |

|          |               |                                                             |                                                                                                                                                                                              |

|          |               | 8                                                           |                                                                                                                                                                                              |

|          |               |                                                             |                                                                                                                                                                                              |

|          | 4.3           | 0                                                           |                                                                                                                                                                                              |

|          | 4.4           | Summary                                                     | 66                                                                                                                                                                                           |

| <b>5</b> | -             | 0 2                                                         | 69                                                                                                                                                                                           |

|          | 5.1           | •                                                           |                                                                                                                                                                                              |

|          |               | • •                                                         |                                                                                                                                                                                              |

|          |               | 5 1                                                         |                                                                                                                                                                                              |

|          |               |                                                             | 37<br>38<br>39<br>42<br>45<br>46<br>47<br>47<br>48<br>50<br>55<br>55<br>55<br>56<br>60<br>55<br>55<br>55<br>66<br>65<br>56<br>66<br>56<br>66<br>70<br>70<br>71<br>71<br>77<br>77<br>81<br>88 |

|          | 5.2           | 0 0                                                         |                                                                                                                                                                                              |

|          |               | 0                                                           |                                                                                                                                                                                              |

|          | 5.3           |                                                             |                                                                                                                                                                                              |

|          |               | C C C C C C C C C C C C C C C C C C C                       |                                                                                                                                                                                              |

|          |               |                                                             |                                                                                                                                                                                              |

|          | 5.4           | Discussion and Summary                                      | 88                                                                                                                                                                                           |

| 6        |               |                                                             | 91                                                                                                                                                                                           |

|          | 6.1           |                                                             |                                                                                                                                                                                              |

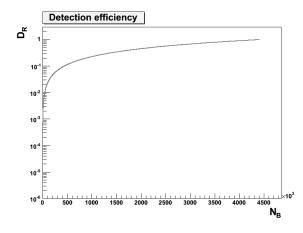

|          |               | 6.1.1 SEU cross section from Monte Carlo simulations        | 93                                                                                                                                                                                           |

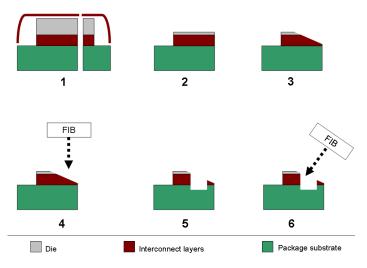

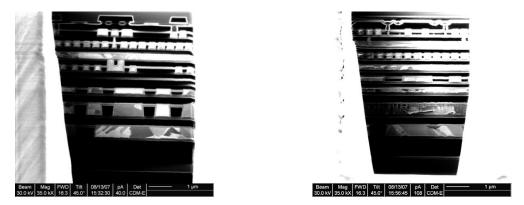

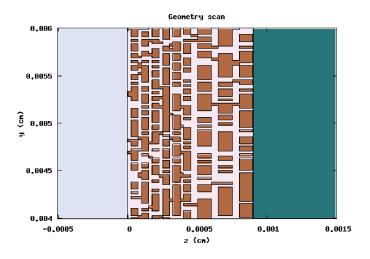

|              | 6.2  | Resolving case study geometry                                   | 94  |

|--------------|------|-----------------------------------------------------------------|-----|

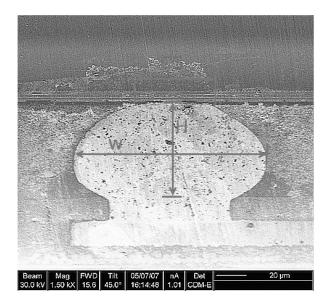

|              |      | 6.2.1 Structural analysis                                       | 95  |

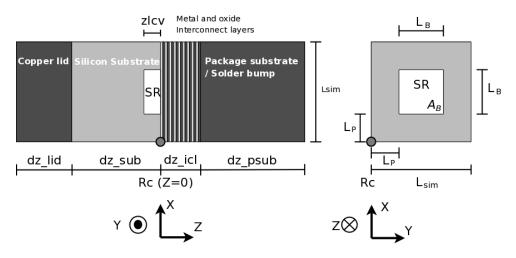

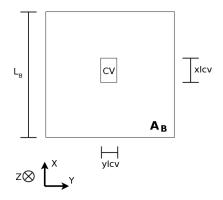

|              |      | 6.2.2 Generic geometry input description                        | 98  |

|              | 6.3  | Preparation and setup of simulation tools                       | 99  |

|              |      | 6.3.1 Fluka specifics                                           | 99  |

|              |      | 6.3.2 Modifications of the SEMM2 model                          | 105 |

|              |      | 6.3.3 Status                                                    | 107 |

|              | 6.4  | Fluka simulation results                                        | 108 |

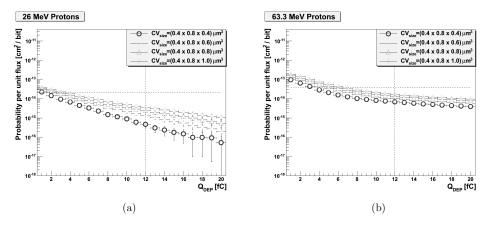

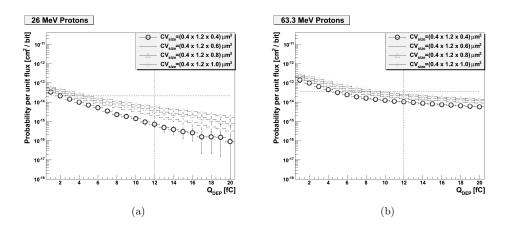

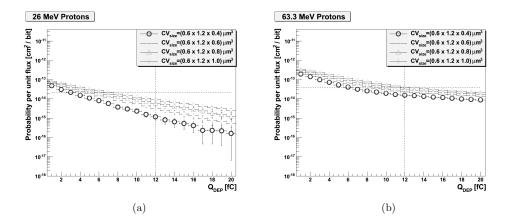

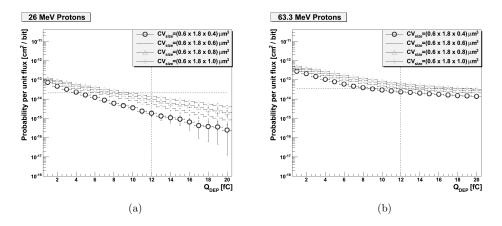

|              |      | 6.4.1 Collection Volume variability study                       | 108 |

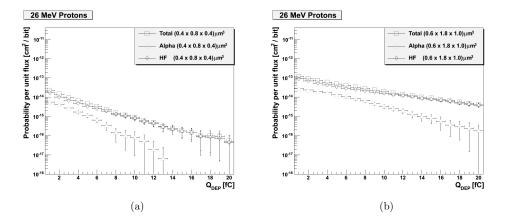

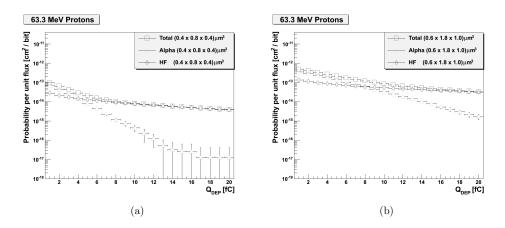

|              |      | 6.4.2 Contribution from $\alpha$ -particles and heavy fragments | 111 |

|              |      | 6.4.3 Role of metal interconnect layers                         | 115 |

|              | 6.5  | Summary                                                         | 116 |

| 7            | Cor  | clusion and outlook                                             | 119 |

| A            | AliI | Root simulations of the TPC radiation environment               | 123 |

|              | A.1  | Previous work                                                   | 123 |

|              | A.2  | Geometry description                                            | 124 |

|              |      | A.2.1 Description of front-end cards                            | 124 |

|              |      | A.2.2 The RCU scoring region                                    | 126 |

|              |      | A.2.3 The C++ code of the geometry description                  | 126 |

|              | A.3  | Visual check using energy scoring                               | 130 |

|              | A.4  | Fluence results for the 6 scoring regions                       | 132 |

|              | A.5  | Fluence as a function of energy                                 | 138 |

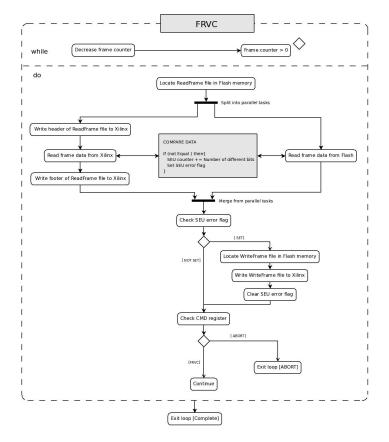

| в            | Flov | w diagram of the FRVC procedure                                 | 141 |

| $\mathbf{C}$ | Irra | diation test results                                            | 143 |

|              | C.1  | SEU cross section results                                       | 143 |

|              |      | C.1.1 Total dose calculation                                    | 146 |

| D            | Clas | ss diagram of fault injection software                          | 147 |

| $\mathbf{E}$ | SEU  | J Monte Carlo simulation                                        | 149 |

|              | E.1  | FPGA geometry analysis                                          | 149 |

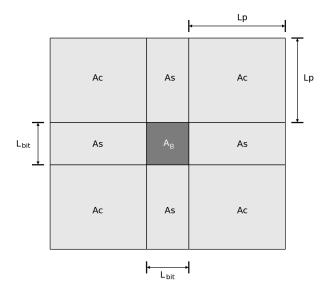

|              | E.2  | Determining an optimal simulation target area                   | 151 |

|              | E.3  | SEMM2.vBergen setup specifics                                   | 155 |

|              |      | E.3.1 Tables of simulation parameters                           | 155 |

|              |      | E.3.2 Input file example                                        | 158 |

| $\mathbf{F}$ | List of Publications |                     |     |  |  |

|--------------|----------------------|---------------------|-----|--|--|

|              | F.1                  | As main contributor | 163 |  |  |

|              | F.2                  | As collaborator     | 163 |  |  |

## Chapter 1

## Introduction

SRAM<sup>1</sup> based Field Programmable Gate Arrays (FPGAs) have become a very attractive alternative in many applications due to the continuous increase in density of user programmable resources and embedded memory. Compared to traditional ASIC<sup>2</sup>, design, SRAM based FPGAs offer advantages such as decreased cost and development time. In addition one of the major benefits is considered to be their ability to be programmed in the field. This offers great flexibility as it allows to reprogram already deployed devices with new functionality or improved versions of existing implementations. For complex detector systems like the ALICE<sup>3</sup> experiment where changes may be needed up to the very last minute, reprogrammability may prove to be a vital feature. It will also allow continued development to improve functionality after start-up of the experiment. With the use of ASICs, any upgrades would not be possible without the need to replace hardware. Moreover, as the AL-ICE experiment will be physically inaccessible for most of its operational life time, replacing hardware would require parts of the detector system to be dismantled. The flexibility offered by SRAM FPGAs is therefore a major reason why they were chosen for the project described in this thesis.

A major drawback of SRAM FPGAs is their susceptibility to radiation induced effects [1], in particular single event upsets. Single event upsets are caused by ionizing particles which may deposit enough energy in the device to alter the logic state of a memory element. Since the user-programmed functionality depends on the data stored in millions of these memory elements, a single event upset may give rise to unfavourable effects in the expected functionality.

In the ALICE experiment, beams of particles will be collided at extreme energies to study a state of matter known as quark-gluon plasma [2]. These collisions will

<sup>&</sup>lt;sup>1</sup>SRAM: static random access memory.

<sup>&</sup>lt;sup>2</sup>ASIC: Application Specific Integrated Circuit.

<sup>&</sup>lt;sup>3</sup>ALICE: A Large Ion Collider Experiment. See section 1.1 for further introduction.

generate new particles which can be detected by different sub-detectors of ALICE to determine properties like for instance particle type, energy and momentum. However, particles from these collisions will also pose a reliability risk to the readout electronics of these sub-detectors. For example, in the Time Projection Chamber, which is the main tracking detector of ALICE, the readout of data is controlled by an SRAM based FPGA. If vital functionality should be lost due to a single event upset, large amounts of data may be lost unless the source of the failure can be repaired in time or even avoided in the first place. Due to the dense architecture of the detectors and the fact that the radiation field is dominated by neutrons, physical shielding of the electronics is practically not possible in ALICE. Nor is it wanted as extra material should be avoided if possible in order to minimize the distortion of the physics measurements. The main challenge is therefore to apply the appropriate measures in order to reduce the consequences of such effects. The process or technique applied to reduce the failure probability of a system is often referred to as mitigation of the system.

This thesis is based on the various aspects related to qualifying an SRAM based FPGA for use in the ALICE experiment. The work focuses on investigating the underlying mechanisms responsible for single event upsets in the ALICE environment, the probability of experiencing failures, and a method to repair and test the effects of single event upsets.

### 1.1 The ALICE experiment

The LHC is a circular accelerator located at CERN<sup>4</sup>, the European Organization for Nuclear Research. It has a circumference of about 27 km and located about 100 m below the ground level. With to adjacent beam pipes bunches of particles will travel in opposite directions and collide at dedicated experimental locations. ALICE is one of four main experiments at LHC.

#### 1.1.1 Physics goals

The main purpose of ALICE is to study a state of matter known as quark-gluon plasma, which is believed to have existed soon after the Big Bang. Quarks are bound together into hadrons<sup>5</sup> by the strong force, which is mediated by gluons. As the

<sup>&</sup>lt;sup>4</sup>CERN: Conseil Européen pour la Recherche Nucléaire.

<sup>&</sup>lt;sup>5</sup>Hadrons contain two subsets of particles: baryons, made up of 3 quarks, and mesons, made up of a quark-antiquark pair. Common baryons are the protons and neutrons, while pions are typical a example of mesons produced in particle physics experiments.

potential associated with the strong force increases with distance, quarks cannot appear as isolated particles under normal conditions. With the extreme energy density and temperatures that will be achieved in the nucleus-nucleus collisions at the LHC, it is expected that matter will undergo a phase transition into a plasma of unbound quarks and gluons, the quark-gluon plasma. As the quark-gluon plasma expands and cools, it will transform into hadronic matter. The quark-gluon plasma can therefore not be studied directly. Instead a set of observables are identified as indicators of its existence. More details on ALICE physics can be found in [3].

#### 1.1.2 Detectors

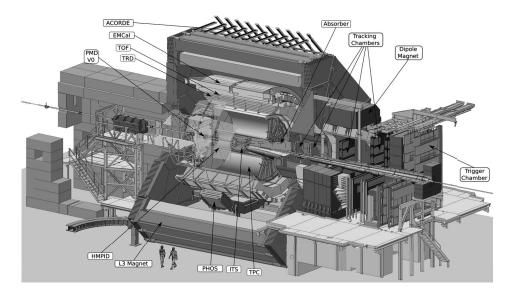

The ALICE detector shown in figure 1.1 is optimized for heavy ion collisions. Beams of lead ions and protons will enter from each side of the detector and collide in the interaction point which is at the centre of the detector. The detector has an onion-like structure where the various sub-detectors are arranged in different layers from inside to the outside. Each sub-detector is optimized to study specific properties of the particles produced in the Pb-Pb collisions.

Figure 1.1: Layout of the ALICE detector [2].

#### The Time Projection Chamber (TPC)

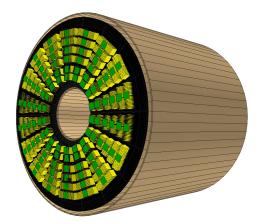

The TPC, shown in figure 1.2, is the main tracking detector in ALICE and is optimized for charged particle momentum measurements. It consists of a cylindrical shaped field cage and has an inner radius of 85 cm, an outer radius of 280 cm, and an overall length along the beam direction of 510 cm. Charged particles produced in the collisions will ionize the gas inside the field cage and electrons will drift in the electric field between the central high voltage electrode and the two end plates. Each of the two end plates is divided in 18 trapezoidal sectors where multiwire proportional chambers provide the required charge amplification. Each sector is again sub-divided into an inner and outer chamber with slightly different wire geometry spacing and pad sizes. This is done to provide better spatial resolution as the track density is higher closer to the beam line. The full readout plane of the TPC is divided into a total of 570132 pads where each pad corresponds to one data readout channel. As the TPC front-end electronics is located directly behind the

Figure 1.2: Layout of the ALICE TPC detector.

two end plates of the field cage, it is expected that radiation induced effects will pose a reliability risk. Thus the radiation environment in this location is further investigated in section 2.3 of this thesis.

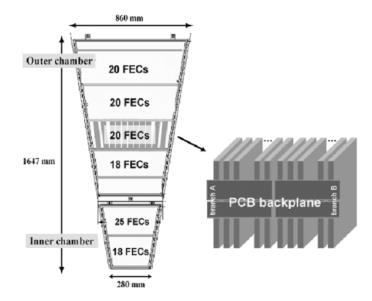

### **1.2** The TPC front-end electronics

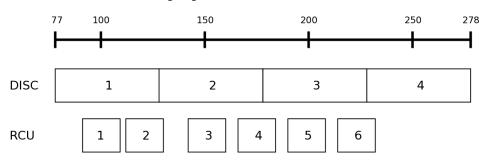

The 18 trapezoidal sectors on each side of the TPC are divided into 6 readout partitions of which 2 are located in the inner chamber and 4 in the outer chamber as shown in figure 1.3. Each readout partition is controlled by the readout control unit which is connected to a number of front-end cards. The main task of the front-end cards is to processes the signals generated by charge deposition on the readout pads. In total 216 readout control units and 4356 front-end cards are needed to read out data from 570132 channels.

Figure 1.3: Each TPC sector is divided into 6 readout partitions. One RCU per readout partition is in charge of reading out data from the detector through the FECs [4].

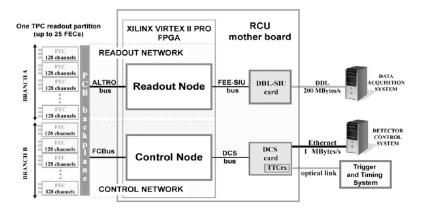

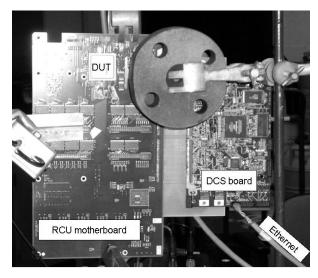

#### 1.2.1 Readout Control Unit

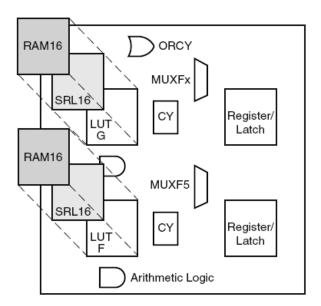

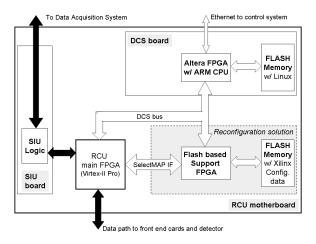

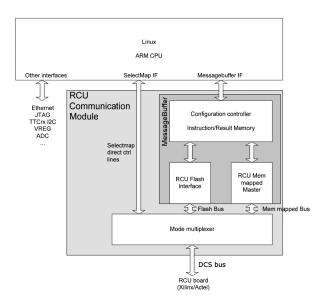

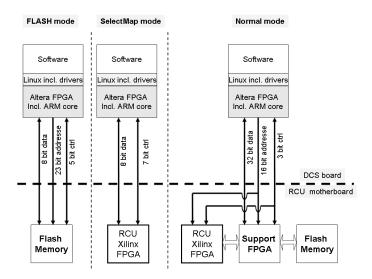

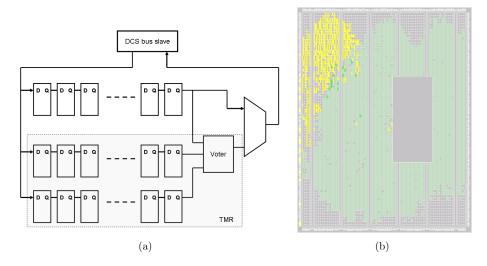

The Read Out Control Unit (RCU) consists of the RCU motherboard, the Detector Control System board (DCS board) and the Source Interface Unit (SIU). A Xilinx Virtex-II Pro FPGA, hereafter called the RCU main FPGA, is mounted on the back side of the RCU motherboard. The RCU main FPGA plays a key role in the TPC front-end electronics as it is in charge of data readout from the TPC detector. It is responsible for moving data from the front-end cards to the SIU were the data is optically transmitted via the data detector link to the data acquisition system. In addition it carries out tasks related to configuration and housekeeping of the front-end cards. The RCU is therefore divided into a readout network and a control network with a corresponding readout node and control node in the RCU main FPGA user design. This is illustrated in figure 1.4. Through the DCS bus

Figure 1.4: The architecture and readout path of the TPC electronics for one readout partition [4].

the control node of the RCU main FPGA is connected to the DCS board which essentially is an embedded computer running Linux. In this way remote access can be provided through a standard Ethernet connection. This option adds flexibility to the system even though the front-end electronics is physically inaccessible. Upgrades of the RCU main FPGA can therefore be carried out after start-up of the experiment. Detailed information about the RCU and front-end electronics can be found in [5], [6], and [7].

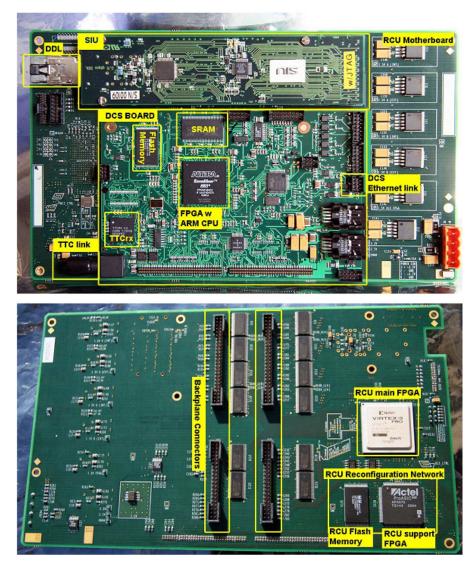

#### 1.2.2 Choice of FPGA technology

Because the RCU main FPGA is a vital part of the data readout path, it is important that it remains fully functional during the operation of the experiment. At the time when the RCU main FPGA device choice was made, different FPGA technologies were therefore evaluated based on their single event upset susceptibility. Reprogrammability was also an important requirement as this would allow to develop and upgrade the user design during and after commissioning of the detector. The standard available technologies considered were:

Figure 1.5: Top: The RCU motherboard with the DCS board and SIU card attached: Bottom: The back side of the RCU motherboard where the FPGAs and reconfiguration network are located.

- *SRAM*, where the user-programmed functionality is stored in SRAM memory cell.

- Flash, where the memory element is a floating gate transistor that can be turned off by injection charge into the floating gate.

- Anti-fuse, where an electrically programmable switch that is initially high impedance forms a low resistance and permanent connection when programmed.

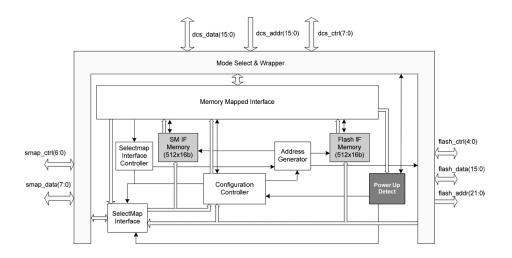

Anti-fuse and Flash based FPGAs are non-volatile. This means that the userprogrammed functionality continues to be stored when the power is turned off. No external circuitry is therefore needed to program the FPGA when powered on. Once an anti-fuse switch is programmed, the process can not be reversed. Anti-fuse FP-GAs are therefore not susceptible to configuration loss due to single event upsets [8]. Nonetheless, due to their one-time programmability, this technology was not considered as an alternative candidate for the RCU main FPGA. Flash based FPGAs are also considered inherently single event upset tolerant [9] and contrary to anti-fuse FPGAs, they can be reprogrammed. However, at the time when the device choices were made, no Flash based FPGAs were available with enough resources to implement the data acquisition design of the RCU main FPGA. In-field programmability was also limited due to the need of a higher programming voltage than what was available for the readout electronics. These limitations strongly favoured the use of SRAM based FPGAs even though they are known to be sensitive to single event upsets. In the end an SRAM based FPGA from Xilinx was found suitable because it offered the possibility of partial reconfiguration on an operational system. An external system can therefore be designed in order to detect and repair single event upsets in the configuration memory of the Xilinx FPGA without disrupting its operation [10]. This external system is further described in chapter 3 where it is referred to as the reconfiguration network of the RCU main FPGA. Along with the RCU main FPGA it is located on the back side of the RCU motherboard as shown in figure 1.5. In contrast to the RCU main FPGA, fewer resources were required to implement the control functionality of the reconfiguration network. A Flash based FPGA from Actel was therefore chosen together with a Flash memory device to store the configuration data of the RCU main FPGA.

### **1.3** Primary objective and main contributions

The purpose of this thesis is to investigate the various aspects related to qualifying the Xilinx Virtex-II Pro FPGA for use in the radiation environment of the ALICE experiment. First of all this requires knowledge about the radiation environment at the location where the device is operated. This can be obtained through simulations using Monte Carlo transport codes. Accelerated beam tests are mandatory in order to investigate how sensitive a device is to a certain type of radiation. In relation to single event upsets this sensitivity is referred to as the single event upset cross section,  $\sigma_{SEU}$ . When combined with the knowledge of the radiation environment, it can be used to predict the rate at which single event upsets will occur in the ALICE experiment. The effects and consequences of single event upsets are however difficult to accurately quantify. Single event upsets in FPGAs are not one to one correlated to measurable errors in the expected functionality. Additional testing is therefore needed to investigate this issue, and also to measure the effectiveness of any techniques applied in order to reduce the failure probability. Physics based simulations is another method that can provide additional insight into how different types of radiation and material compositions of a device may contribute to the single event upset rate.

All these aspects are treated in this thesis and the main contributions are listed below:

- Monte Carlo simulations to determine the radiation environment in the location of the RCU main FPGAs, presented in section 2.3.3.

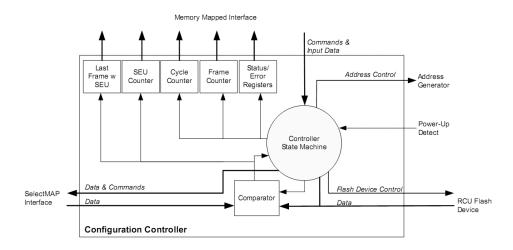

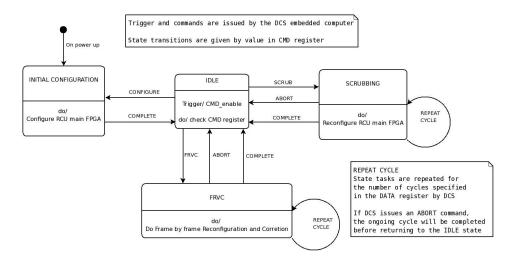

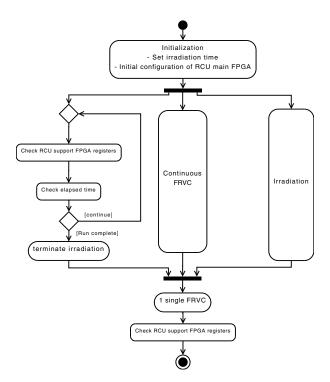

- Development of the RCU support FPGA user design that is in charge of the various reconfiguration procedures for the RCU main FPGA. This design is presented in section 3.2.2 and was developed together with Johan Alme [11]. An important feature of this design is the ability to carry out frame-by-frame read back to verify the integrity of the configuration memory, and further correct single event upsets if detected. It is an important part of the mitigation strategy for the RCU main FPGA.

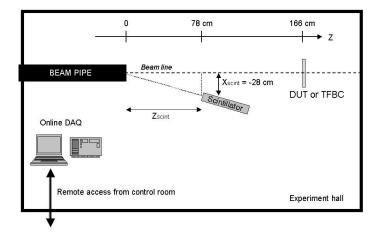

- Accelerated beam tests to investigate the single event upset sensitivity of the Xilinx Virtex-II Pro FPGA configuration memory in a 29 MeV proton beam at the Oslo Cyclotron (OCL). The results are presented in section 4.2.1.

- Accelerated beam tests to investigate the effectiveness of the frame by frame, read back, verification and correction procedure when combined with other system level error detecting and correcting techniques. The results are presented in section 4.2.2.

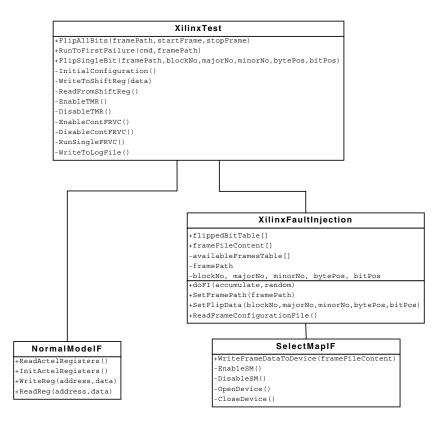

- Implementation of a fault injection solution on the RCU as a method to test how single event upsets may effect the functional behaviour of the final RCU main FPGA user design. This method, which is presented in chapter 5, can for

instance be used to test the effectiveness of any mitigation strategies applied to the design.

• Preparation of a test case study where physics based simulations will be carried out to investigate the single event upset rate of the Xilinx Virtex-II PRO FPGA. The work is presented in chapter 6.

### 1.4 Outline

This thesis is divided into seven chapters including this introduction chapter. Chapter 2 starts by giving a brief overview of the basic single event effects related to SRAM memory and FPGAs. The basic mechanism responsible for the single event upsets is then presented along with how single event upsets may affect the SRAM memory cell and FPGA. The second part of the chapter focuses on the radiation environment in the location of the RCU main FPGA, and simulation results are presented. Chapter 3 introduces partial reconfiguration and how it is applied to the RCU main FPGA. Special attention is given to the RCU reconfiguration network and the RCU support FPGA responsible for the different configuration procedures. Chapter 4 presents the results of the accelerated beam tests of the RCU main FPGA. The single event upset cross section for the configuration memory is measured using a 29 MeV proton beam at the Oslo Cyclotron. A standard shift register design is further used to demonstrate how the reconfiguration network in combination with triple modular redundancy will reduced the consequences of SEUs. Finally some predictions are made of the expected number of single event upsets when the RCU main FPGA is operated in the ALICE radiation environment. Chapter 5 describes how fault injection is implemented for the RCU main FPGA. A case study is presented to demonstrate how fault injection can be used to test the effect of single event upsets on the RCU main FPGA user design. This case study uses the same, however somewhat smaller in size, shift register design as for the accelerated beam tests. Chapter 6 describes how physics based simulations are carried out for a case study of the RCU main FPGA. Physics based simulations using Monte Carlo transport codes can be applied to study how the single event upset rate may be affected by different material compositions and types of radiations. xsFinally the thesis is concluded in chapter 7 with and outlook on prospective work.

## Chapter 2

## Radiation effects in the TPC RCU main FPGA

It has become a well established fact that modern digital integrated circuits can be sensitive to ionizing radiation. When for instance an SRAM cell is exposed to a transient noise pulse, this may change the state of the memory cell from a logical 1 to a logical 0 or vice versa. The basic mechanism responsible is the energy deposition from an incoming ionizing particle traversing the sensitive part of the SRAM cell. This effect is commonly referred to as a single event upset (SEU) or soft error.

SEUs are the main radiation effects of concern for the SRAM based RCU main FPGA in the TPC front-end electronics. They can lead to a variety of undesirable effects where the loss of vital control functionality is the main worry. An SEU may result in breakdown of the readout of data from the TPC detector. In order to avoid or reduce the consequence of an SEU, it is essential to have a good understanding of the basic mechanism responsible, including its potential effects in the FPGA. An overview and introduction to this subject is therefore given in the first part of this chapter. The SEU rate or frequency of a device is strongly dependent on the radiation environment it is exposed to. The last part of the chapter will therefore describe the radiation environment that is expected in the vicinity of the TPC front-end electronics.

SEUs are not the only radiation induced effects in integrated circuits. A number of other radiation effects also exist that may have temporary or even permanent damaging potential. However, in a radiation environment consisting of mainly energetic hadrons, which is the case for the TPC detector, it is the SEU which is of main concern and consequently the focus of this chapter and thesis.

### 2.1 Single Event Effects

Numerous acronyms are used by the radiation effects community to describe the different types of radiation effects in digital integrated circuits. This section gives a brief overview and description of the most relevant effects related to SRAM based FPGAs. Another compact summary of radiation effects related to Xilinx FPGAs can be found in [12].

The common term for any measurable effect resulting from the deposition of energy from a single ionizing particle strike, is a single event effect (SEE). The most relevant SEEs are:

#### Single Event Upset (SEU)

The JEDEC standard [13] defines an SEU as a soft error caused by the transient signal induced by a single energetic particle strike. In [14], it is said to occur when a radiation event causes a charge disturbance large enough to reverse or flip the data state of a memory cell, register, latch, or flip-flop.

An SEU can be defined in a number of ways. Essentially it refers to any type of memory cell whose content or value has been changed into an erroneous state due to a radiation event. As a memory cell stores the value of a bit, it is also commonly referred to as a bit flip, meaning the bit value has been flipped or inverted. An SEU can be categorized as a soft error. The error is "soft" because the device is not permanently damaged by the radiation. When new data is written to the struck memory cell, the device will store it correctly [14].

#### Multiple Bit Upset (MBU)

An MBU is a single radiation event that results in more than a single bit being flipped. Each bit flip is essentially an SEU. An MBU is therefore considered to be a subset of the SEU. They are usually a small fraction of the total number of observed SEUs. The MBU probability is however steadily increasing as geometries shrink [15], [16]. Since most conventional error correcting techniques are only capable of detecting and correcting single bit flips, MBUs are an increasing reliability concern. Still, the conclusion from [16] is that approximately 1-3% of the upsets induced by a 63.3 MeV proton beam are MBUs for the Xilinx Virtex-II Pro FPGA. MBUs will therefore not be the main source leading to functional failures in the RCU main FPGA. Determining the MBU cross section was therefore not within the scope of this thesis.

#### Single Event Transient (SET)

An SET is a transient pulse in the logic path of an IC. Similar to an SEU, it is induced by a charge deposition of a single ionizing particle. An SET can be propagated along the logical path where it was created. It may be latched into a register, latch or flip-flop causing their output value to change. In the case of the Xilinx FPGAs the FPGA structure by its nature is highly resistant to SETs due to the large capacitive loading of the single path [17]. Compared to SEUs in the FPGA configuration memory, SETs are therefore considered a negligible problem and are not treated in this thesis.

#### Single Event Functional Interrupt (SEFI)

Xilinx [15] defines SEFI as an SEE that results in the interference of the normal operation of a complex digital circuit. SEFI is typically used to indicate a failure in a support circuit, such as loss of configuration capability, power on reset, JTAG<sup>1</sup> functionality, a region of configuration memory, or the entire configuration. For the Xilinx Virtex-II Pro FPGA used as the RCU main FPGA, the SEFI cross section is typically orders of magnitude lower than the SEU cross section [17]. As for the previously mentioned SETs, further investigation of SEFI rates are not considered for this thesis.

#### Single Event Latchup (SEL)

The latchup phenomenon occurs when a spurious current pulse activates the parasitic bipolar transistors that are inherent in complimentary metal-oxide-semiconductor (CMOS) structure [18]. The result is an abnormally high current state which may lead to permanent damage if not restored to normal operation by a power cycle. If the origin of the current pulse is an ionizing particle it is called a single event latchup. Because it is a potentially destructive event, it is not categorized as a soft error. SELs are typically a problem for devices operating in environments of energetic heavy ions such as in space. For environments consisting of single hadrons only, such as the ALICE TPC or in terrestrial applications, SELs are considered a negligible problem. No high current events, that needed a power cycle to be restored, were detected during the accelerated beam test presented in chapter 4.

<sup>&</sup>lt;sup>1</sup>JTAG: Joint Test Action Group.

### 2.2 Basic mechanism

#### 2.2.1 Charge generation and collection

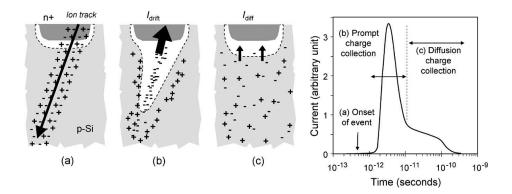

As a charged particle passes through matter it loses energy through the process known as ionization. This is the starting point of all single event effects. Along its path, the charged particle generates electron-hole pairs through scattering with the atomic electrons of the material. In this process the target nucleus remains at a fixed location due to the small amount of energy transferred. The charged particle is only slightly deflected and its path can therefore be considered as a straight line. If the path traverses a reverse-biased p-n junction, charge carries are collected by the electric field and drifted to the nearby node where a current/voltage transient is created [14]. The process is illustrated in figure 2.1. Charge collection is dominated by the faster drift process followed by a slower diffusion process. An additional effect of the generated column of electron-hole pair, is its distortion of the electric field. A funnel shaped extension of the depletion region enhances the drift collection, and effectively more charge can be collected at the node. The funnel concept was first introduced by Hsieh in [19] and depends on the doping concentration of the substrate. Increasing the doping concentration will decrease the distortion of the electric field lines. The amount of collected charge is a complex

Figure 2.1: Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a energetic ion [14].

combination of factors like the size of the device, biasing of the various circuit nodes, substrate structure and device doping [14]. In addition the type of ion, its energy and trajectory through the node plays an important role.

#### 2.2.2 Single event upsets in SRAM memory

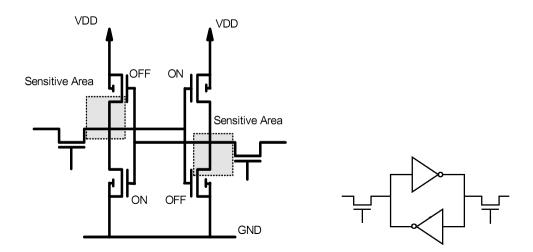

A single event upset was previously defined as bit flip in a memory cell caused by the transient signal induced by a single energetic particle strike. Figure 2.2 shows a schematic of a 6-transistor SRAM cell. It consists of cross coupled inverters each with one NMOS and one PMOS transistor. The sensitive regions in an SRAM cell are the drain areas of the transistors in the "OFF" state. These regions correspond to a reverse biased pn-junction capable of collecting the charge carriers. When a particle strikes one of the drain areas, a transient current pulse will be created at the output of the respective inverter. This current pulse is then propagated to the input of the other inverter pair. If the width and amplitude of the pulse are sufficient, the next inverter stage will change its output as a consequence. Effectively, a new value will be loaded/latched in the memory cell. The sensitivity of an SRAM

Figure 2.2: 6-transistor SRAM cell [20].

cell depends on factors like the node capacitance, the operating voltage and the speed of the feedback circuit [14]. The node capacitance together with the channel resistance acts as a low pass filter that may reduce the rising slope and magnitude of the induced current pulse. With down scaling of technology and feature sizes, the operational voltage of a device is also decreased. This means that less charge is needed to induce an SEU. Increasing the capacitive load is therefore a known design technique to reduce the sensitivity as the technology nodes gets smaller [17]. Combined, parameters like these define the amount of charge or energy needed to flip the bit of a memory cell. This is also referred to as the critical energy,  $E_{crit}$ , or

critical charge,  $Q_{crit}$ . That is, an SEU can be induced if a charge larger than the critical charge has been collected by the sensitive node. Critical charge and critical energy can be used interchangable, provided that one knows how to change the unit from one to the other. If silicon is assumed as the material of the charge collection volume, which is usually the case, then

$$Q_{crit}(\text{infC}) = 44.5 \cdot E_{crit}(\text{inMeV}) \quad [21]. \tag{2.1}$$

#### 2.2.3 Single event upsets in the FPGA configuration memory

The main building blocks of a modern SRAM based FPGA are a number of programmable logic blocks structured in a large matrix. In an FPGA, a function is implemented by mapping it into this pre-existing and programmable logic. This mapping is referred to as its configuration [22] and is stored in a large array of SRAM cells. If an ionizing particle causes one or multiple SRAM cells to change its value during normal operation, this is referred to respectively as an SEU or an MBU. If this corrupted bit controls a logical resource utilized in the implemented design, this may cause a malfunction in the operation of the FPGA. For example, look-up tables are used to implement Boolean functions in SRAM based FPGAs. The content of the look-up table is stored as part of the configuration memory, and if the stored value is corrupted due to an SEU it will no longer store the correct Boolean function. This can result in unwanted and incorrect behaviour. Similarly, other programmable logic such as for example routing multiplexers are controlled by the content of one or several SRAM cells. An SEU can therefore cause a broken connection between two logical blocks and consequently corrupt the flow of data in the FPGA. These types of malfunctions are referred to as functional failures or functional errors in the following.

An FPGA can contain millions of configuration bits and the larger part controls the complex routing network interconnecting all the logic blocks. For a typical FPGA design only a fraction (90-98%) of the configuration bits are used [20]. An SEU in an unused bit will have no effect on the normal operation of the device. This effect was seen during both the accelerated beam tests and fault injection tests presented in chapter 4 and 5. During irradiation several of the SEUs detected did not seem to have any influence on the operation of the FPGA. Thus, making prediction on the expected functional failure rate of the RCU, the relationship between SEUs and functional failures must first be established. This ratio is highly dependent on the implemented design due to how the utilization of logical resources may vary from one design to another. In combination with accelerated beam tests to determine the SEU sensitivity of a device, fault injection is a well suited method to further determine the average number of SEUs per functional failure. Fault injection is therefore discussed in chapter 5.

An SEU in the configuration memory of an FPGA can only be corrected by reconfiguring the device. A standard mitigation technique is therefore to regularly reconfigure the full device to correct any accumulated SEUs. This approach is implemented for the RCU main FPGA and is further described in chapter 3.

#### 2.2.4 The physics of single event upsets

The dominant mechanism of energy loss by a charged particle passing through a material is Coulomb scattering by the atomic electrons of the material. Due to the small size of the nucleus compared to the size of an atom, a collision with the nucleus is far less probable. Nevertheless, nuclear interactions play an important role prior to the creation of an SEU and will be discussed in this section.

#### Stopping power and range

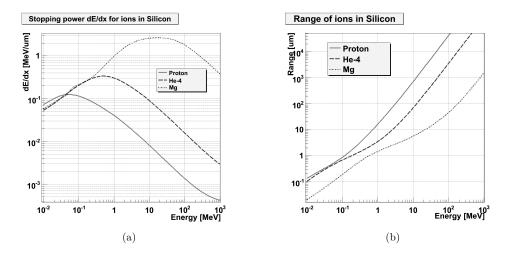

A measure for the energy loss of a particle per unit length is the stopping power. The stopping power can be related to the number of electron-hole pairs produced per unit length along the particle's track. For silicon, the conversion factor is 3.6 eV per electron-hole pair [21]. The stopping power is usually expressed in MeV cm<sup>2</sup> mg<sup>-1</sup>. If multiplied by the material density it becomes MeV/cm, energy per unit length.

Figure 2.3(a) shows the stopping power of a proton, an  $\alpha$ -particle and a magnesium ion in silicon. As can be seen, the stopping power is dependent on the kinetic energy and charge of the particle. Except for very low energies, the higher the charge of the ion the higher is the stopping power. Thus a magnesium ion is more ionizing than the  $\alpha$ -particle, and the  $\alpha$ -particle more than the proton. The stopping power increases with decreasing energy until it reaches a maximum and then starts to decrease. At low energies the ion has a tendency to pick up electrons which lowers its effective charge and thus its stopping power.

After travelling a certain distance in the material, the ion eventually loses all its energy and comes to rest. This distance is referred to as the range of the ion. For comparison the range of protons,  $\alpha$ -particles and magnesium ions in silicon is plotted as a function of energy in figure 2.3(b).

In section 2.2.2 the critical charge was introduced as the amount of charge needed to induce a bit flip in a memory cell. In addition a memory cell is associated with its sensitive volume. That is, charge which is deposited within this volume can be considered to be collected by the sensitive node. Knowing its size and shape, and the particle direction and stopping power in the material, the amount of deposited

Figure 2.3: Stopping power for various ions in silicon. The plots are generated by data from SRIM 2006 [23].

charge within the sensitive volume can be estimated. To a first order the sensitive volume can be defined by the area and depth of the NMOS or PMOS transistor of the SRAM cell. For a 0.13  $\mu$ m technology such as the Xilinx Virtex-II Pro, the maximum track length through the sensitive volume is probably<sup>2</sup> in the order of 1  $\mu$ m and below. The maximum stopping power of a proton is 0.14 MeV/ $\mu$ m which corresponds to approximately 6 fC/ $\mu$ m. This is below the average critical charge of 12 fC [24] for for the Xilinx Virtex-II Pro. Because direct ionization from protons is not expected to be the cause of SEUs, a different mechanism must therefore be responsible.

#### SEUs from non-elastic interactions

In the case of highly energetic neutrons and protons, they can collide with the nucleus of the target material and induce a nuclear reaction. Compared to the Coulomb interactions nuclear reactions are rare events. However, due to the large number of SRAM cells in modern devices, significant particle fluxes, and the lengthy exposure times, the contribution from non-elastic interctions can not be disregarded.

Interactions between a nucleon (i.e. a proton or neutron) and a nucleus can be either elastic or non-elastic. In an elastic reaction the incident and outgoing particles are the same. Due to the small amount of momentum transfer in an elastic

$<sup>^{2}</sup>$ See section 6.2.

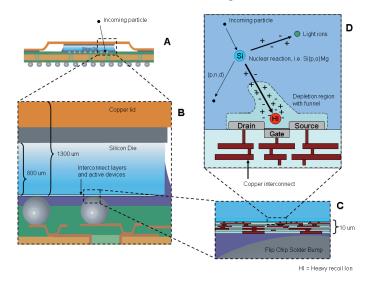

collision they are considered to only play a minor role of SEU rates [21]. For future applications, when the feature size is further downscaled and the critical charge is decreased, this assumption may no longer hold and elastic interactions may have to be reconsidered. In a non-elastic interaction on the other hand, additional particles can be created and emitted from the reaction. Figure 2.4 shows an example of how

Figure 2.4: Cross section schematic showing the structure of the device. A particle entering from the top may travel through both the copper lid and silicon substrate before it creates a non-elastic interaction nearby a sensitive node. The resulting fragments may have enough energy to induce and SEU if their paths traverses the sensitive node.

an energetic particle can enter a device and create a non-elastic interaction in the silicon substrate. One or several of the fragments produced may be emitted with the right direction and enough energy to reach a sensitive transistor. It is typically the recoil ion or an  $\alpha$ -particle that possesses enough stopping power to induce an SEU. An example of a reaction channel for a 100 MeV p + Si reaction is given in equation 2.2.

$$p + {}^{28}_{14} Si \to p + 2\gamma + {}^{4}_{2} He + {}^{24}_{12} Mg$$

(2.2)

This produces a 5.4 MeV  $\alpha$ -particle and a 4.9 MeV magnesium ion. Their ion energies are similar, but due to the higher charge of the magnesium, its stopping power is approximately 2.3 MeV/ $\mu$ m compared to approximately 0.14 MeV/ $\mu$ m for the  $\alpha$ -particle. At the production location, the stopping power of a 5.4 MeV  $\alpha$ -

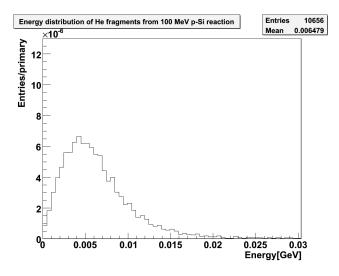

Figure 2.5: Energy distribution of  $\alpha$ -particles produced by Fluka simulations of 10<sup>8</sup> protons of 100 MeV on a 100  $\mu$ m thin silicon target.

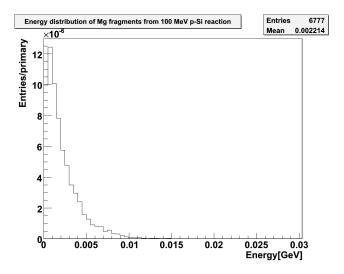

particle may not be large enough to cause an SEU. However, as it starts to move its kinetic energy will decrease and consequently its stopping power will increase. With a range close to 28  $\mu$ m it therefore has potential to cause an SEU at a certain distance from its production location. Figures 2.5 and 2.6 shows the energy distribution of  $\alpha$ -particles and magnesium ions produced in a Fluka [25] [26] Monte Carlo simulation of a 100 MeV proton beam on a thin silicon target. The mean energy of the magnesium ions is approximately 2.2 MeV while it is 6.5 MeV for the  $\alpha$ -particle. Because a 2.2 MeV magnesium ion has a range of approximately 2.3  $\mu$ m in silicon, it must be created in close proximity to a sensitive transistor in order to pose a reliability risk. On the other hand,  $\alpha$ -particles can potentially contribute even if they are produced as far away as 25-50  $\mu$ m.

### 2.3 The TPC radiation environment

When high energetic beams of lead ions collide in the central point of the ALICE experiment, a high primary particle production rate is expected. Many of these particles produce secondaries through hadronic and electromagnetic cascades in absorbers and structural elements of ALICE [2]. This leads to particle fluxes which may pose a reliability risk to the front-end electronics of the TPC detector. An understanding of the TPC radiation environment is therefore important in order to

Figure 2.6: Energy distribution of magnesium recoil ions produced by Fluka simulations of  $10^8$  protons of 100 MeV on a 100  $\mu$ m thin silicon target.

make predictions of failure rates due to single event upsets.

#### 2.3.1 Particle multiplicity

The event rate for Pb-Pb collisions at the LHC nominal luminosity of  $10^{27}$  cm<sup>-2</sup>s<sup>-1</sup> will be about 8000 minimum-bias collisions per second, of which only 5% corresponds to the most central ones [2]. At present the estimates for the multiplicity density  $(dN/d\eta)$  in a central Pb-Pb collision range from 1500-4000 charged particles per unit of pseudorapidity<sup>3</sup> at mid-rapidity. This corresponds to 40000 particles in the worst case scenario. The average particle multiplicity for minimum-bias runs is roughly 1/5 of the multiplicity of a central event [27], [28]. When running simulations of particle fluences in Fluka the result is normalized to the number of primary particles transported and square centimetre,  $particles/(cm^2 \cdot primary)$ . The particle flux can then be calculated according to equation 2.3

$$Flux = \Phi_{Fluka} \cdot R_{col} \cdot \frac{N_{central}}{5},$$

(2.3)

where  $\Phi_{Fluka}$  is the fluence result from Fluka,  $R_{col}$  is the collision rate, and  $N_{central}$  is the particle multiplicity of a central Pb-Pb event.

<sup>&</sup>lt;sup>3</sup>Pseudorapidity  $\eta$  describes the angle of the particle momentum relative to the beam axis.  $\eta = -\ln[\tan(\theta/2)]$ .

#### Total dose

One month of the year will be dedicated to Pb-Pb collisions, and in [29] the total dose for 10 ALICE years is estimated to approximately 6 Gy<sup>4</sup> at the TPC locations. For the rest of the year, p-p collisions will run at an interaction rate of 200 kHz [2]. This is a factor 25 higher than for Pb-Pb collisions. Assuming that the particle multiplicity roughly scales with the number of participants (2 for protons and 416 for lead), the total number of particles from 10 ALICE years of p-p collisions is approximately a factor 1.2 compared to Pb-Pb collisions (25 x 10 months x 2/416). The total dose is therefore not expected to be higher than a few kRad.

#### 2.3.2 Previous work

Particle transport simulations have already been carried out to estimate the radiation environment in the TPC detector. In [29] the particle fluence was scored in a 1 mm thick silicon disc representing the front-end electronics. It was divided in four cylindrical scoring regions to study the fluence at different radial distances from the beam line. The results of the simulations are summarized in tables A.1 and A.2 of appendix A.

#### 2.3.3 Updated simulations with new geometry description

In [29] the geometry description of the experiment and detectors was based on  $ALIFE^5$  [30]. It did not contain a description of the actual front-end electronics. The front-end electronics of the TPC detector consist of 216 RCU nodes controlling 4356 front-end cards equally divided between both sides of the TPC. All of these cards are encapsulated in copper envelopes for water cooling and make up extra material between the beam collision point and the RCU main FPGA. Thus it was desirable to implement a more detailed description of the front-end electronics to study whether this would have any impact on the hadron fluence in the locations of the different RCUs. Also, since the present most updated geometry description of the ALICE experiment is available in the AliRoot framework [31], the updated simulations are based on this description. Applying the Virtual Monte Carlo interface (VMC) [32], AliRoot can be combined with Fluka for particle transport.

$<sup>^41~\</sup>mathrm{Gy} = 100~\mathrm{Rad}$

<sup>&</sup>lt;sup>5</sup>ALIFE is an editor and parser for the Fluka geometry and detector definition.

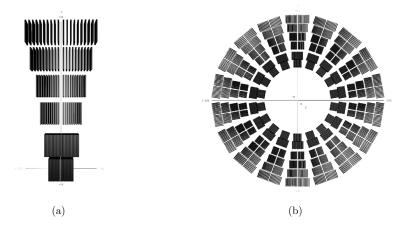

#### Geometry description and scoring regions

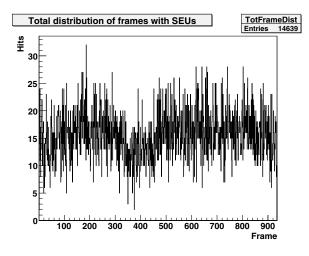

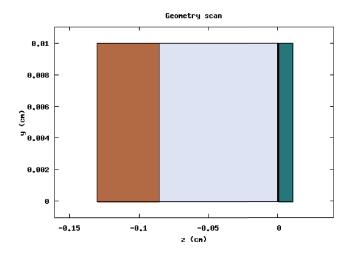

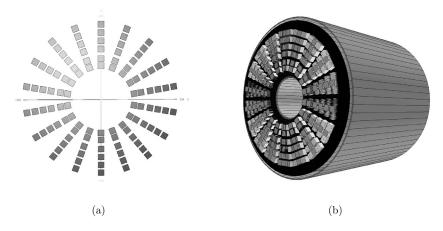

Figure 2.7 shows how the front-end electronics has been implemented in the geometry description of the TPC detector. The front-end cards are represented by the yellow volumes while the RCUs are represented by the green volumes. A more

Figure 2.7: A view of the TPC geometry with the added front-end cards (yellow) and RCUs (green).

detailed description of the geometry can be found in appendix A.2. Compared to the scoring scheme in [29], using the RCUs as scoring regions gives a more accurate fluence versus location information. To increase statistics, the RCUs are grouped in 6 rings of 18 cards for each side of the TPC. The RCU scoring rings are labeled 1 through 6, where ring 1 consist of the 18 innermost RCUs (closest to the beam line), and ring 6 the 18 outermost RCUs. Figure 2.8 shows how the location of the 6 scoring rings compares to the scoring scheme used in [29].

#### Results of the preliminary simulation run

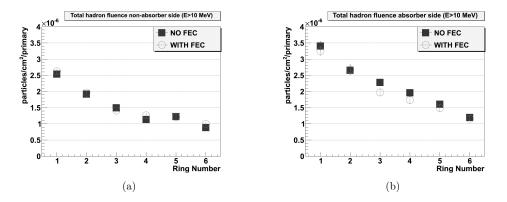

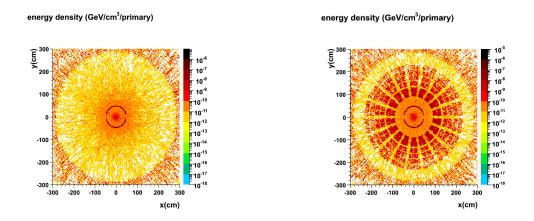

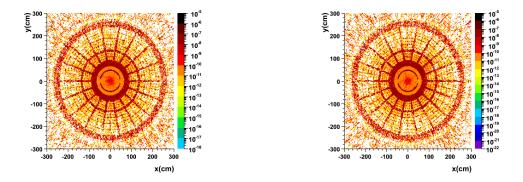

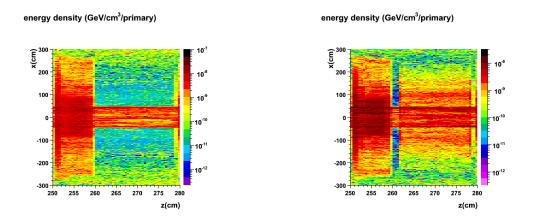

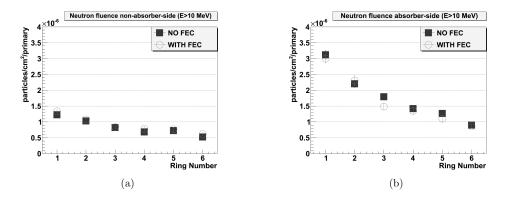

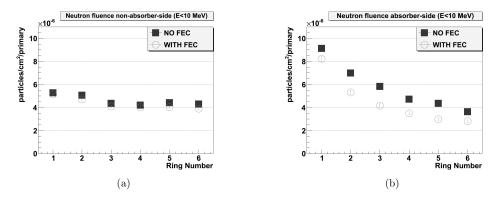

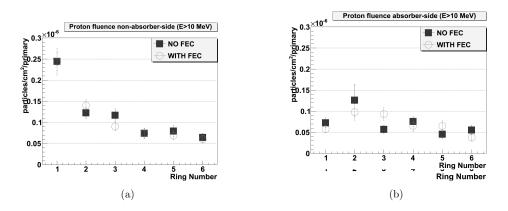

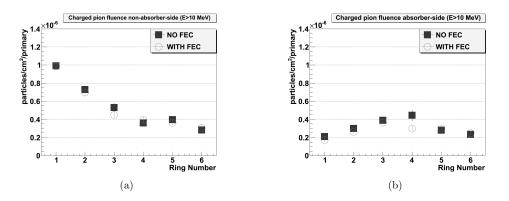

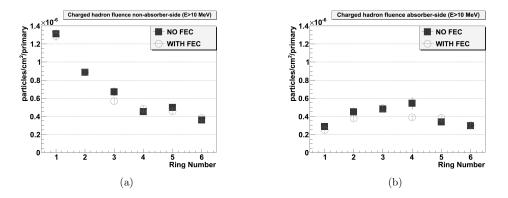

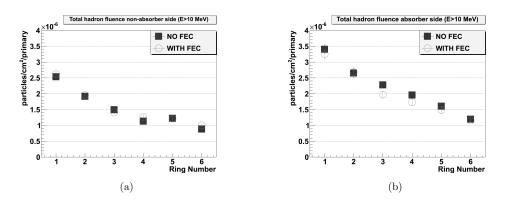

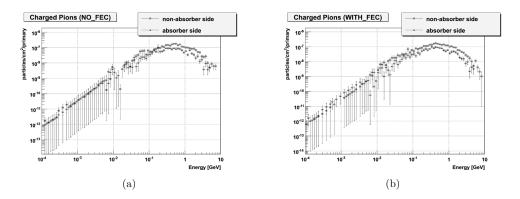

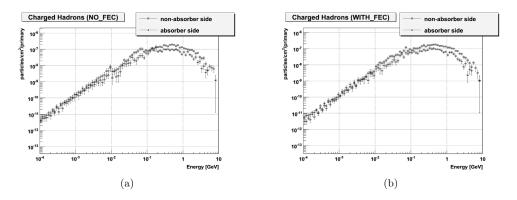

In total 15 independent simulations were carried out for the geometry implementation without the front-end cards, and 18 for the geometry implementation with the front-end cards included. For each simulation 10000 primary particles were requested to be transported. The results in figures 2.9(a) and 2.9(b) show that the hadron fluence was not significantly changed by adding the extra geometry. It can be argued whether a tiny shielding effect is observed on the absorber side.

Location of scoring regions in radial distance from beam line [cm]

Figure 2.8: A comparison showing the location of the RCU scoring rings compared to the scoring scheme used in [29].

Figure 2.9: Total fluence of energetic hadrons  $(E_{kin} > 10 MeV)$  for the non-absorber (a) and absorber (b) side as a function of radial distance from the beam line. Error bars represent the standard deviation between the individual runs as produced by Fluka.

This shielding effect is more evident for the low energy neutrons (E<10 MeV) for the absorber side as can be seen in figure A.7. Appendix A also shows additional plots and detailed tables of all the scored particles.

Good agreement is found when comparing the results of the overlapping scoring rings/regions with the previous simulations in [29]. The absorber side has a slightly higher hadron fluence than the non-absorber side, and both sides show the same trend of decreasing hadron fluence with increasing distance from beam line.

Applying equation 2.3, the total hadron flux for each RCU ring can be calculated based on tables A.5 through A.8 in appendix A. The results are shown in tables 2.1 and 2.2 for a particle multiplicity of  $N_{central}$ =40000, and can be used to calculated the expected SEU rate for all RCUs.

| Flux $[part/(cm^2s)]$                                                                  | Scoring ring absorber side (WITH FEC) |             |               |             |            |            |  |

|----------------------------------------------------------------------------------------|---------------------------------------|-------------|---------------|-------------|------------|------------|--|

| $\operatorname{Flux}\left[\operatorname{part}/\left(\operatorname{cm} s\right)\right]$ | 1                                     | 2           | 3             | 4           | 5          | 6          |  |

| р                                                                                      | $3 \pm 14\%$                          | $6\pm19\%$  | $5 \pm 17\%$  | $4\pm21\%$  | $4\pm19\%$ | $2\pm20\%$ |  |

| n                                                                                      | $191 \pm 4\%$                         | $147\pm7\%$ | $94\pm6\%$    | $86\pm7\%$  | $70\pm8\%$ | $55\pm7\%$ |  |

| $\pi^{\pm}$                                                                            | $11\pm13\%$                           | $16\pm7\%$  | $23 \pm 5\%$  | $19\pm7\%$  | $19\pm6\%$ | $15\pm7\%$ |  |

| $had^{\pm}$                                                                            | $15\pm10\%$                           | $24\pm7\%$  | $31 \pm 5\%$  | $24\pm6\%$  | $24\pm6\%$ | $19\pm6\%$ |  |

| Sum $(had^{\pm} + n)$                                                                  | $207 \pm 4\%$                         | $171\pm6\%$ | $126 \pm 4\%$ | $111\pm5\%$ | $94\pm6\%$ | $74\pm5\%$ |  |

Table 2.1: Estimated hadron fluxes (particles/cm<sup>2</sup>/s) for each scoring ring for a particle multiplicity of  $N_{central}$ =40000 (absorber side). The numbers are based on the simulation runs with the front-end cards implemented and for  $E_{kin} > 10 MeV$ .

| Flux $[part/(cm^2s)]$ | Scoring ring non-absorber side (WITH FEC) |              |              |              |            |            |  |

|-----------------------|-------------------------------------------|--------------|--------------|--------------|------------|------------|--|

| Flux [part/(cm s)]    | 1                                         | 2            | 3            | 4            | 5          | 6          |  |

| р                     | $15\pm12\%$                               | $8\pm9\%$    | $5\pm11\%$   | $4 \pm 15\%$ | $4\pm15\%$ | $3\pm16\%$ |  |

| n                     | $85\pm3\%$                                | $68 \pm 4\%$ | $53 \pm 4\%$ | $50\pm7\%$   | $48\pm8\%$ | $39\pm5\%$ |  |

| $\pi^{\pm}$           | $63\pm3\%$                                | $44\pm4\%$   | $28\pm5\%$   | $25\pm7\%$   | $23\pm6\%$ | $19\pm6\%$ |  |

| $had^{\pm}$           | $82 \pm 3\%$                              | $56\pm3\%$   | $36 \pm 4\%$ | $30 \pm 6\%$ | $29\pm5\%$ | $24\pm6\%$ |  |

| Sum $(had^{\pm} + n)$ | $167\pm2\%$                               | $125\pm2\%$  | $90\pm3\%$   | $81\pm5\%$   | $77\pm5\%$ | $64\pm4\%$ |  |

Table 2.2: Estimated hadron fluxes (particles/cm<sup>2</sup>/s) for each scoring ring for a particle multiplicity of  $N_{central}$ =40000 (non-absorber side). The numbers are based on the simulation runs with the front-end cards implemented and for  $E_{kin} > 10 MeV$ .

#### 2.3.4 Discussion

Assuming that only hadrons above 10 MeV are of concern, and further that these hadrons can be treated as the same particle, tables tables 2.1 and 2.2 can be used calculate the expected SEU rate. The basis of these assumptions is briefly discussed in the following paragraphs.

#### Neutron and protons

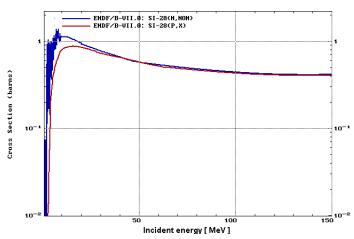

In [21] the characteristics of proton-nucleus and neutron-nucleus interactions are considered to be very similar for energies above 100 MeV. Figure 2.10 shows a

comparison of the non-elastic interaction cross section of protons and neutrons in silicon. In fact, the interaction cross sections are very similar down to 20-30 MeV. For lower energies the main difference between the neutron and proton is the Coulomb repulsion which decreases the non-elastic cross section of the proton. Lower incident

Non-elastic interaction cross section for proton and neutron in silicon

Figure 2.10: Non-elastic reaction cross section of protons and neutrons in silicon [33]. 1 barn =  $10^{-24} cm^2$ .

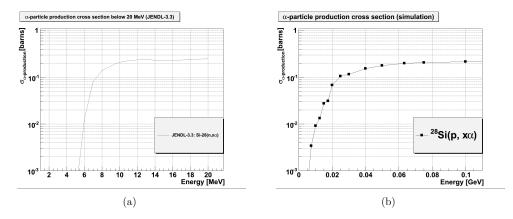

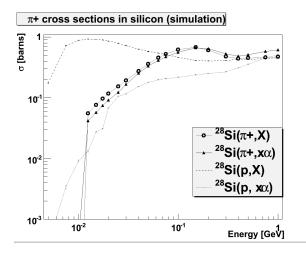

particle energies also reduce the probability of producing light secondary fragments such as the  $\alpha$ -particle. This is seen for both neutrons and protons in figures 2.11(a) and 2.11(b). For the p + Si interaction, the  $\alpha$ -particle production cross section is significantly reduced below 20-40 MeV. Because neutrons are not affected by Coulomb repulsion they are slightly more effective in producing  $\alpha$ -particles at energies below 40 MeV. However, below 10 MeV the  $\alpha$ -production from neutrons shows a sharp cut-off with a threshold close to 5-6 MeV. The contribution for neutrons in this energy region is therefore expected to be negligible due to the low fragment production cross section and possible energy transfer.

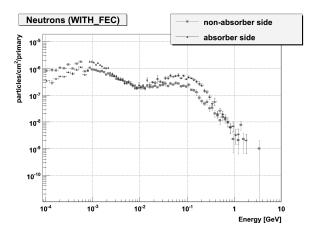

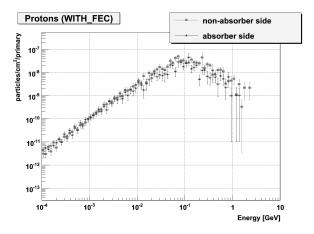

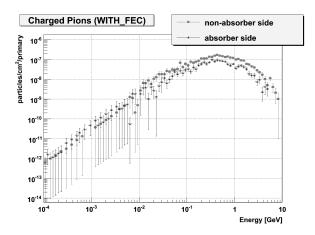

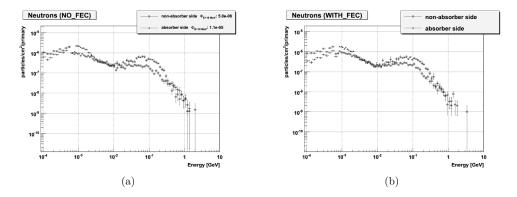

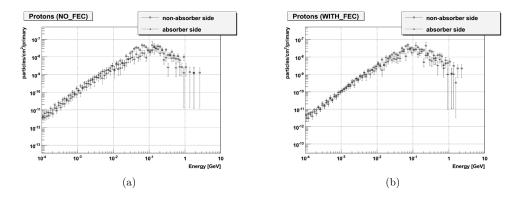

Figures 2.12 and 2.13 shows the simulated fluence for neutrons and protons as a function of energy summed over all the 6 RCU scoring rings. For both neutrons and protons a peak can be found around 100 MeV. However, while the proton fluence below 10 MeV is effectively negligible, there is a significant amount of lower energy neutrons. Thermal neutrons need to be considered only for the  ${}^{10}B(n,\alpha)^{7}Li$  reaction which has a high capture cross section. The result of this reaction is a  ${}^{7}Li$  ion of

Figure 2.11:  $\alpha$ -particle production cross sections for the n + Si(a) and p + Si(b) interactions. The neutron data is obtained from [33] while the proton result is obtained from a Fluka simulation with protons beams of different incident energies hitting a thin silicon target.

approximately 0.9 MeV<sup>6</sup> and an  $\alpha$ -particle of 1.47 MeV, both capable of inducing SEUs. Since <sup>10</sup>B has been effectively removed from all Xilinx technologies below 220 nm [17], thermal neutrons are not considered to be an issue for the Xilinx Virtex-II Pro used on the TPC readout control unit.

### Pions

While protons and neutrons have comparable cross section characteristics, pions show a slightly different behaviour. Figure 2.15 shows a comparison of cross sections for protons and pions in silicon. The plots are produced from Fluka simulations of proton and pion beams on a thin silicon target. For parts of the energy range of interest in the TPC radiation environment, the  $\alpha$ -particle production from pion interactions is a factor 2-3 higher than from proton interactions. Similarly, the  $\pi^+$ +Si non-elastic interaction cross section is also slightly higher in a certain energy range. It is therefore not obvious that pions can be treated similarly to protons and neutrons when considering their effectiveness in inducing SEUs. Unfortunately no pion beam SEU cross section data is available for the Xilinx Virtex-II Pro FPGA. Therefore the best approximation is currently to apply proton and neutron SEU

$<sup>^60.84~{\</sup>rm MeV}$  in 94% of the time and 1.014 MeV in 6% of the time.

Figure 2.12: Simulated fluence of neutrons as a function of energy. Summed over all scoring regions and showed for the non-absorber side and absorber side with the Front-end cards implemented.

Figure 2.13: Simulated fluence of protons as a function of energy. Summed over all scoring regions and showed for the non-absorber side and absorber side with the Front-end cards implemented.

cross section data when considering pions. Because the relative number of pions to the total hadron flux varies between 5-30%, the potential systematic error of using this approximation is reduced. Some research has been done by others to study the

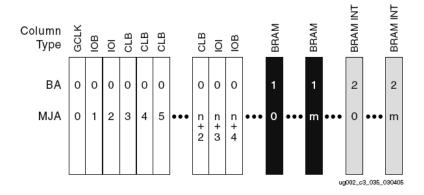

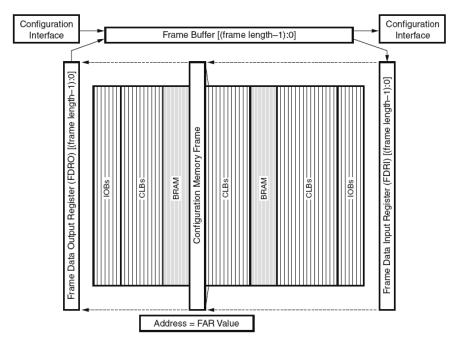

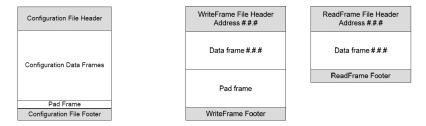

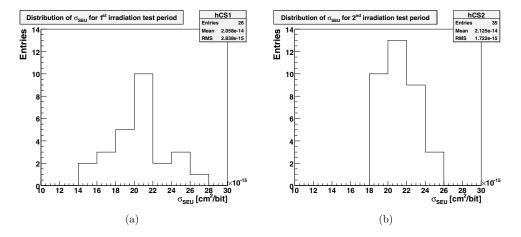

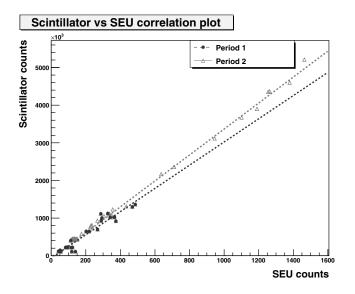

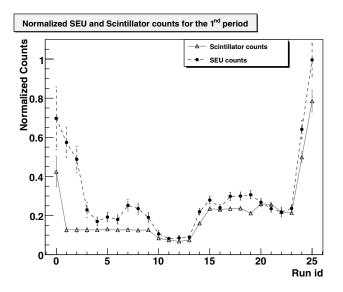

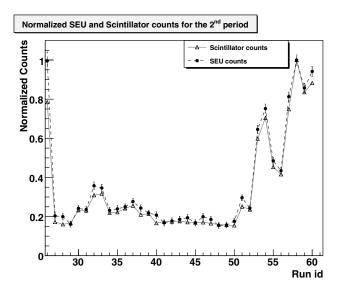

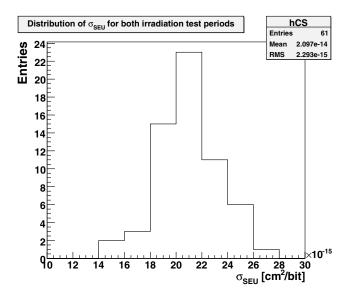

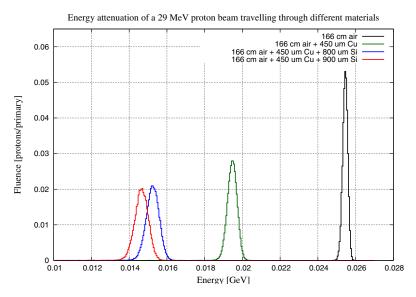

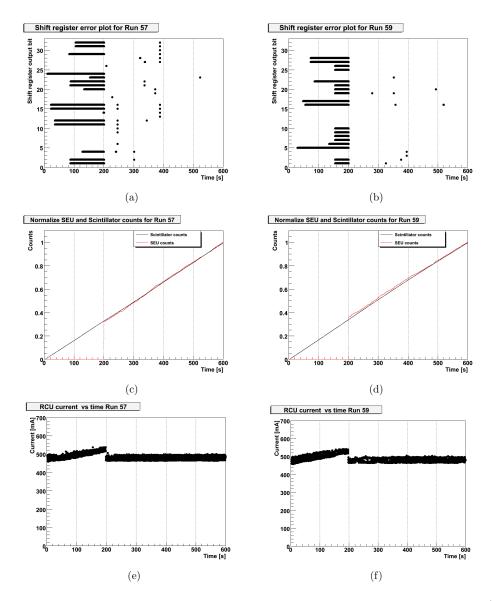

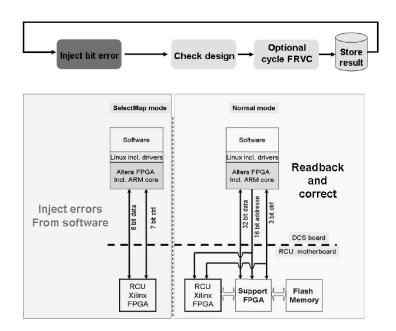

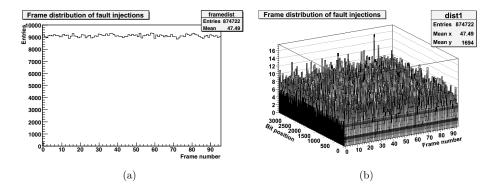

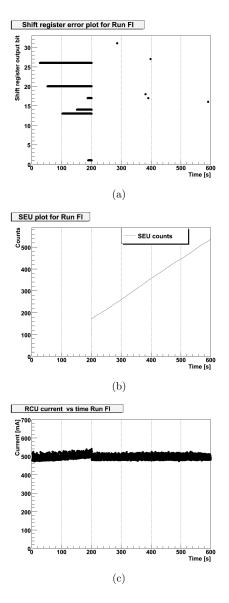

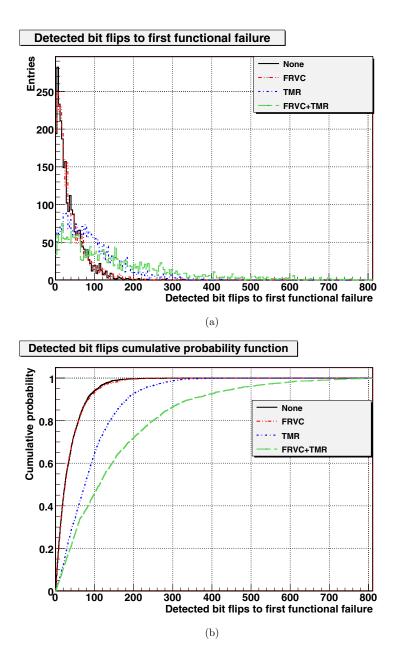

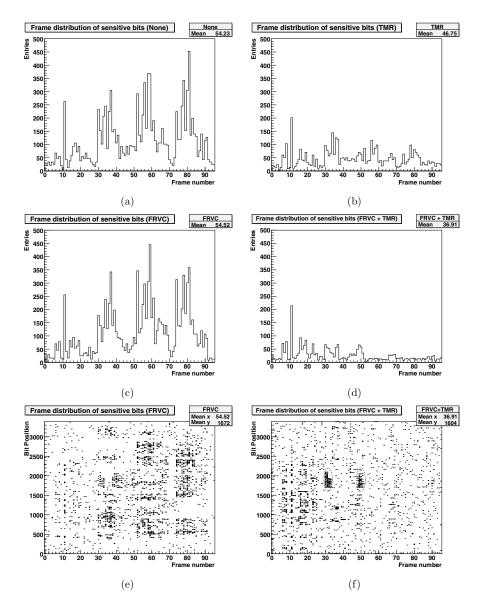

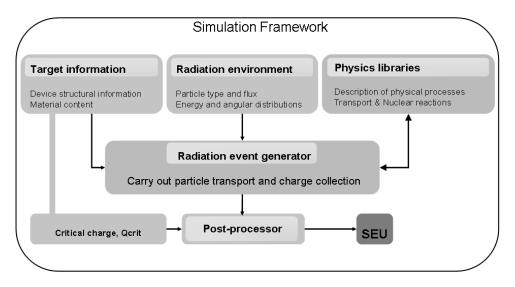

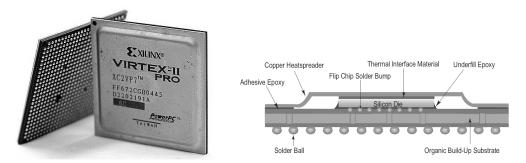

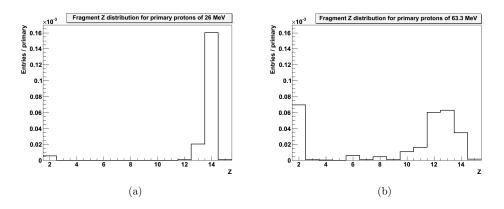

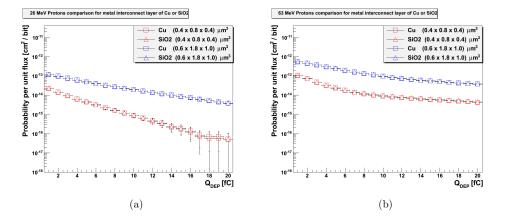

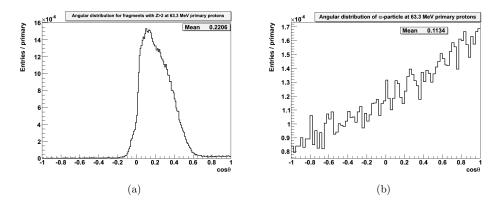

Figure 2.14: Cross sections for  $\pi^+$  and protons in silicon.