# Design and Implementation of a High-Speed Readout and Control System for a Digital Tracking Calorimeter for proton CT

### Ola Slettevoll Grøttvik

Thesis for the degree of Philosophiae Doctor (PhD) University of Bergen, Norway 2021

# Design and Implementation of a High-Speed Readout and Control System for a Digital Tracking Calorimeter for proton CT

Ola Slettevoll Grøttvik

Thesis for the degree of Philosophiae Doctor (PhD) at the University of Bergen

Date of defense: 18.02.2021

#### © Copyright Ola Slettevoll Grøttvik

The material in this publication is covered by the provisions of the Copyright Act.

Year: 2021

Title: Design and Implementation of a High-Speed Readout and Control System for a Digital

Tracking Calorimeter for proton CT

Name: Ola Slettevoll Grøttvik

Print: Skipnes Kommunikasjon / University of Bergen

#### Acknowledgments

For the last four and a half years, I have been deeply involved with the Bergen pCT project, of which the last three years have revolved around the work of this dissertation. I will consider this as one of the most demanding but important periods of my life. I am indebted to everyone I have had the chance to meet and get to know these last couple of years.

Thank you, Dieter Röhrich and Kjetil Ullaland, for believing in me and giving me the opportunity to work with the pCT project, and allowing me to take the role I eventually took. Thank you for always sticking up for me when it was needed and for the long and fruitful discussions.

A large thank you goes to Johan Alme for putting me on this path as early as the autumn of 2014 when you indicated that I had what it took to proceed with both an M.Sc. and a Ph.D. Thank you for supervising me on both my B.Eng. and M.Sc. thesis. But mostly, thank you for being a genuinely great guy with a terrific sense of humor that also shares my interests in beer and good music.

I would also like to thank many of the engineers at IFT. First of all, Shiming Yang, thank you for enduring all my stupid questions and some of my most gloomy days in the lab. Thank you also to Attiq Rehman and Bilal Hasan Qureshi.

One of the most exciting but also intimidating aspects of the last couple of years involved the collaboration with international partners. However, I can not be more grateful for the patience and the guidance I've received. First of all, thank you, Ton van den Brink and Rene Barthel, at Utrecht University in the Netherlands. You are honestly both some of the most knowledgeable and friendly people I have met to date. Thank you both for your hospitality when Tea and I visited Utrecht. Thank you also, Marcel Rossewij, Naomi van der Kolk, Jody Wisman, and Thomas Peitzmann. A huge thank you for the fruitful and friendly collaboration, Ihor Tymchuk and Viatcheslav Borshchov, at LTU Ltd in Kharkiv, Ukraine.

Several people involved with the pCT group deserve considerable recognition. Thank you, Viljar Eikeland, for continually being available for working together on frustrating issues and socializing afterward. Thanks to Matthias Richter, Helge Pettersen, Jarle Sølie, Ganesh Tambave, Shruti Mehendale, Håvard Helstrup, Boris Wagner, and Pierluigi Piersimoni.

The last couple of years would have been quite dull without the company of my colleagues at the institute. I'm grateful for all the fun we had together, especially Magnus Ersdal, Simon Voigt Nesbø, Lucas Altenkämper, Shiming Yuan, and Are Haslum.

I had the pleasure of co-supervising several M.Sc.-students. Thank you all for your hard work — especially the star, Tea Bodova. Also, thanks to Karl Emil Sandvik Bohne, Alf Herland, and Håkon Underdal.

This work would've never been completed without the support from my family and all the friends I love. Thanks to my sisters, Ida and Kristin, you guys give the best pep-talks and support. My parents have been helpful with both proofreading and any other help when it was urgently needed. Thanks to Jenny for the nights out, Eva for hygge, and a huge thanks to Signe for getting me to the finish line. Finally, thank you, guys. You know who you are.

Ola,

Bergen, November 2020

#### Abstract

Particle therapy, a non-invasive technique for treating cancer using protons and light ions, has become more and more common. For example, a particle treatment facility is currently being built, in Bergen, Norway. Proton beams deposit a large fraction of their energy at the end of their paths, i.e., the delivered dose can be focused on the tumor, sparing nearby tissue with a low entry and almost no exit dose. A novel imaging modality using protons promises to overcome some limitations of particle therapy and allowing to fully exploit its potential. Being able to position the so-called Bragg peak accurately inside the tumor is a major advantage of charged particles, but incomplete knowledge about a crucial tissue property, the stopping power, limits its precision. A proton CT scanner provides direct information about the stopping power. It has the potential to reduce range uncertainties significantly, but no proton CT system has yet been shown to be suitable for clinical use. The aim of the Bergen proton CT project is to design and build a proton CT scanner that overcomes most of the critical limitations of the currently existing prototypes and which can be operated in clinical settings.

A proton CT prototype, the Digital Tracking Calorimeter, is being developed as a range telescope consisting of high-granularity pixel sensors. The prototype is a combined position-sensitive detector and residual energy-range detector which will allow a substantial rate of protons, speeding up the imaging process. The detector is single-sided, meaning that it employs information from the beam delivery system to omit tracker layers in front of the phantom. The detector operates by tracking the charged particles traversing through the detector material behind the phantom. The proton CT prototype will be used to determine the feasibility of using proton CT to increase the dose planning accuracy for particle treatment of cancer cells.

The detector is designed as a telescope of 43 layers of sensors, where the two front layers act as the position-sensitive detector providing an accurate vector of each incoming particle. The remaining layers are used to measure the residual energy of each particle by observing in which layer they stop and by using the cluster size in each layer.

The Digital Tracking Calorimeter employs the ALPIDE sensor, a monolithic active pixel sensor, each utilizing a  $1.2\,\mathrm{Gb/s}$  data link. Each layer of  $18\times27\,\mathrm{cm}$  consists of 108 ALPIDE sensors, roughly corresponding to the width and height of the head of a grown person. The sensors are connected to intermediary transition boards that route the data and control links to dedicated readout electronics and supply the sensors with power. The readout unit is the main component of both the data acquisition and the detector control system. The power control unit controls the power supply and monitors the current usage of the sensors. Both of these devices are mainly implemented in FPGAs.

The main purpose of this work has been to explore and implement possible design solutions for the proton CT electronics, including the front-end, as well as the readout electronics architecture. The resulting architecture is modular, allowing the further scale-up of the system in the future. A major obstacle to the design is the high amount of sensors and the corresponding high-speed data links. Thus, a large emphasis has been on the signal integrity of the front-end electronics and a dynamic phase alignment sampling method of the readout electronics firmware. The readout FPGA employs regular I/O pins for the high-speed data interface, instead of high-speed transceiver pins, which significantly reduces the magnitude of the data acquisition system.

A consistent design approach with detailed and systematic verification of the FPGA firmware modules, along with a continuous integration build system, has resulted in a stable and highly adaptive system. Significant effort has been put into the testing of the various system components. This also includes the design and implementation of a set of production test tools for use during the manufacturing of the detector front-end.

# Contents

| A            | ckno  | wledgments                                 | iii          |

|--------------|-------|--------------------------------------------|--------------|

| A            | bstra | act                                        | $\mathbf{v}$ |

| $\mathbf{C}$ | onter | nts                                        | vii          |

| Li           | st of | Abbreviations                              | ciii         |

| 1            | Intr  | roduction                                  | 1            |

|              | 1.1   | Particle Therapy                           | 2            |

|              | 1.2   | Proton CT                                  | 4            |

|              | 1.3   | Digital Tracking Calorimeter               | 6            |

|              |       | 1.3.1 Single-sided proton CT               | 8            |

|              |       | 1.3.2 Particle Energy Calculations         | 9            |

|              | 1.4   | Primary Objective and Main Contributions   | 9            |

| <b>2</b>     | Sys   | tem Design and Electronics Components      | 11           |

|              | 2.1   | Detector Requirements and Considerations   | 12           |

|              | 2.2   | Detector Overview                          | 14           |

|              | 2.3   | Monolithic Active Pixel Sensor             | 16           |

|              |       | 2.3.1 The ALICE Pixel Detector             | 17           |

|              |       | 2.3.2 Data Interface                       | 19           |

|              |       | 2.3.3 Slow Control                         | 20           |

|              |       | 2.3.4 Other interfaces                     | 21           |

|              |       | 2.3.5 Power Supply                         | 21           |

|              | 2.4   | Layer Design                               | 23           |

|              | 2.5   | Front-end Electronics Bonding and Mounting | 25           |

viii Contents

|   |                                             | 2.5.1 Chip Cable and String Flex            | 26 |  |  |  |  |  |  |  |  |  |  |  |  |

|---|---------------------------------------------|---------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|--|

|   | 2.6                                         | Transition Card                             |    |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.7                                         | pCT Readout Unit                            | 29 |  |  |  |  |  |  |  |  |  |  |  |  |

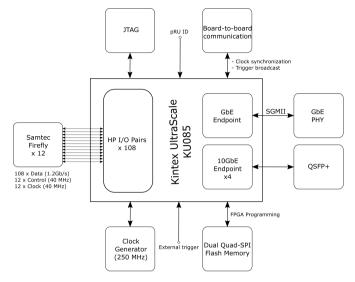

|   |                                             | 2.7.1 Board Overview                        | 29 |  |  |  |  |  |  |  |  |  |  |  |  |

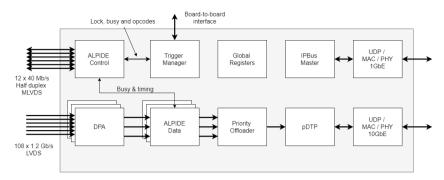

|   |                                             | 2.7.2 FPGA Firmware Overview                | 80 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.8                                         | Power Supply and Control                    | 31 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.9                                         | Other Prototypes                            | 32 |  |  |  |  |  |  |  |  |  |  |  |  |

| 3 | String Design and Performance Evaluation 35 |                                             |    |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1                                         | Introduction                                | 35 |  |  |  |  |  |  |  |  |  |  |  |  |

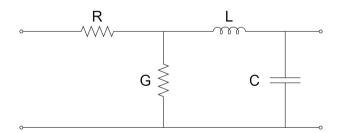

|   |                                             | 3.1.1 Transmission Line Model               | 86 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 3.1.2 Characteristic Impedance and Mismatch | 86 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 3.1.3 Conductive and Dielectric Loss        | 37 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2                                         | Front-End Design                            | 8  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 3.2.1 Chip Cable                            | 39 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 3.2.2 String Flex                           | 12 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 3.2.3 Simulation                            | 18 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 3.2.4 Experimental Verification             | 19 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 3.2.5 Conclusion                            | 52 |  |  |  |  |  |  |  |  |  |  |  |  |

| 4 | FP                                          | GA Design Considerations 5                  | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.1                                         | Introduction                                | 53 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.2                                         | High-Speed I/O                              | 64 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.3                                         | Resource Planning                           | 66 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.4                                         | Clocking Strategy                           | 67 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 4.4.1 Clock Domain Crossings                | 69 |  |  |  |  |  |  |  |  |  |  |  |  |

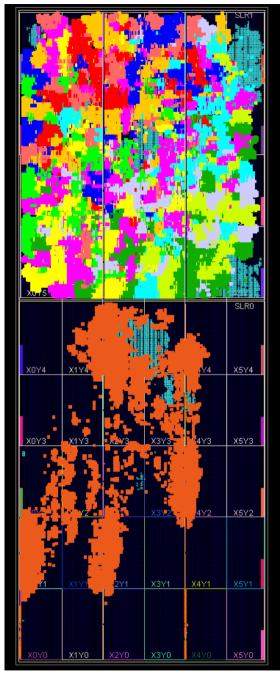

|   | 4.5                                         | Resource Utilization                        | 31 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.6                                         | Radiation Environment of the pCT            | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 4.6.1 Radiation Mitigation Resources 6      | 66 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |                                             | 4.6.2 Radiation and the Data Link           | 57 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.7                                         | Conclusion                                  | 57 |  |  |  |  |  |  |  |  |  |  |  |  |

| 5 | Det                                         | sector Data Readout 6                       | 9  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.1                                         | Data Sampling Methods                       | 69 |  |  |  |  |  |  |  |  |  |  |  |  |

Contents ix

|   |     | 5.1.1  | Static Phase Alignment                                                      | 70  |

|---|-----|--------|-----------------------------------------------------------------------------|-----|

|   |     | 5.1.2  | Clock Data Recovery                                                         | 71  |

|   |     | 5.1.3  | Asynchronous Data Recovery                                                  | 71  |

|   | 5.2 | Semi-l | Dynamic Phase Alignment                                                     | 72  |

|   | 5.3 | Dynar  | mic Phase Alignment                                                         | 74  |

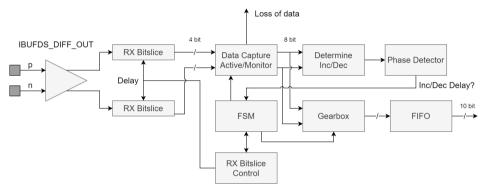

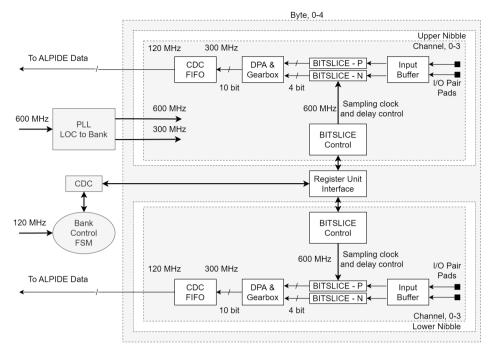

|   |     | 5.3.1  | DPA Implementation                                                          | 75  |

|   |     | 5.3.2  | $\label{eq:high-Performance} \ I/O \ \ \dots \ \ \dots \ \ \dots \ \ \dots$ | 77  |

|   |     | 5.3.3  | DPA Sequence                                                                | 80  |

|   |     | 5.3.4  | Block Architecture                                                          | 82  |

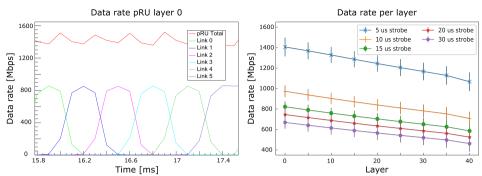

|   | 5.4 | DTC    | Data Rates                                                                  | 84  |

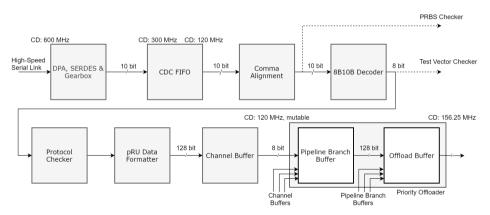

|   | 5.5 | ALPII  | DE Data Protocol                                                            | 86  |

|   | 5.6 | Data 1 | Flow                                                                        | 87  |

|   |     | 5.6.1  | Word Alignment and Decoding                                                 | 88  |

|   |     | 5.6.2  | PRBS Checker                                                                | 89  |

|   |     | 5.6.3  | Protocol and Error Checking                                                 | 89  |

|   |     | 5.6.4  | The pRU Data Format                                                         | 91  |

|   |     | 5.6.5  | Data Formatter                                                              | 96  |

|   |     | 5.6.6  | Priority Offloader                                                          | 98  |

|   | 5.7 | Data   | Offloading                                                                  | 100 |

|   |     | 5.7.1  | 10 Gb/s UDP Stack                                                           | 101 |

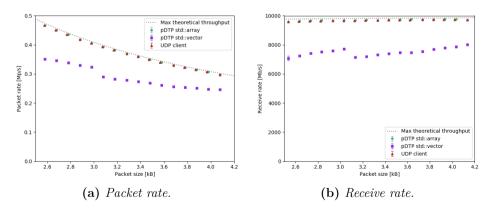

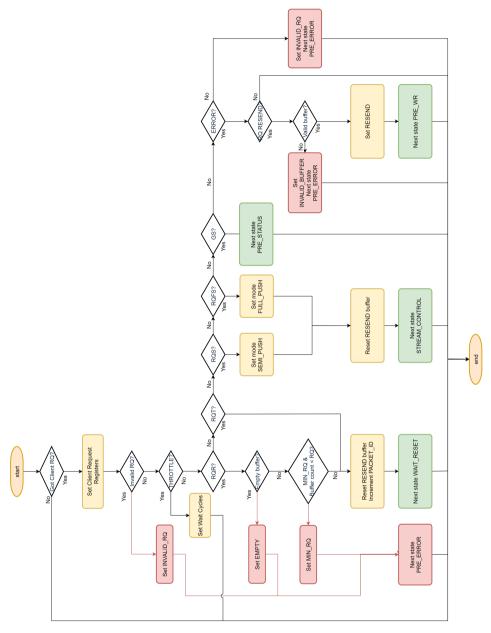

|   |     | 5.7.2  | pCT Data Transfer Protocol                                                  | 103 |

|   |     | 5.7.3  | Addressing                                                                  | 106 |

|   |     | 5.7.4  | pDTP Client Software                                                        | 107 |

|   |     | 5.7.5  | pDTP Server Emulator                                                        | 108 |

|   | 5.8 | Concl  | usion                                                                       | 108 |

| c | D-4 | 4      | Control on J. Manitanina Control                                            | 109 |

| 6 |     |        | 3 2                                                                         |     |

|   | 0.1 |        | Architecture                                                                |     |

|   |     | 6.1.1  |                                                                             |     |

|   | c o | 6.1.2  | Pure FPGA-based DCS with IPBus                                              |     |

|   | 6.2 |        |                                                                             |     |

|   | 0.0 | 6.2.1  | Clock Domain Crossings                                                      |     |

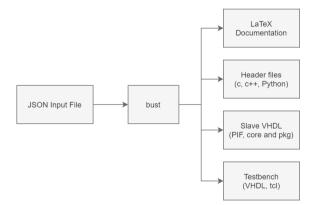

|   | 6.3 | Bus T  | 'ool                                                                        | 116 |

x Contents

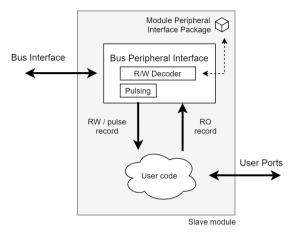

|   |     | 6.3.1      | Register Types                           |

|---|-----|------------|------------------------------------------|

|   | 6.4 | DE Control |                                          |

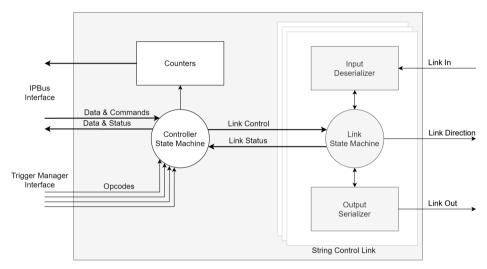

|   |     | 6.4.1      | Half-Duplex MLVDS Bus Interface          |

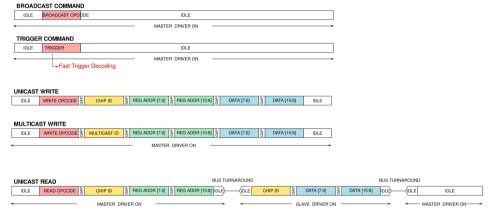

|   |     | 6.4.2      | Transactions                             |

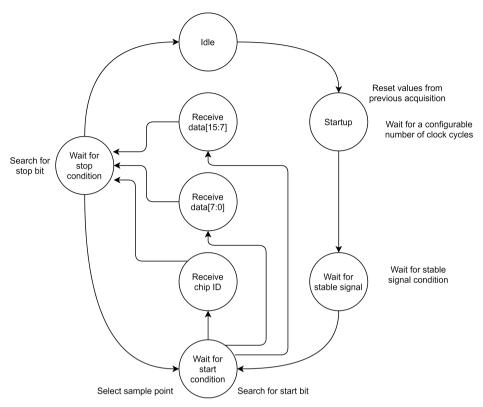

|   |     | 6.4.3      | Input Deserializer                       |

|   | 6.5 | Trigge     | er and Clock Synchronization             |

|   |     | 6.5.1      | Synchronization Parameters               |

|   |     | 6.5.2      | Frame ID and Absolute Time Issues        |

|   |     | 6.5.3      | Synchronization Levels                   |

|   |     | 6.5.4      | Synchronization Architecture             |

|   |     | 6.5.5      | Board-to-Board Interface                 |

|   |     | 6.5.6      | Trigger Manager                          |

|   | 6.6 | DCS '      | Гіme Budget                              |

|   |     | 6.6.1      | ALPIDE Configuration                     |

|   | 6.7 | Concl      | usion                                    |

| 7 | Ver | ificatio   | on and Testing 141                       |

|   | 7.1 | Funct      | ional Verification                       |

|   |     | 7.1.1      | Verification using Testbenches           |

|   |     | 7.1.2      | Test-Driven Development                  |

|   |     | 7.1.3      | Bitvis Verification Library              |

|   |     | 7.1.4      | Design Correctness                       |

|   | 7.2 | pRU l      | Firmware Module Verification             |

|   |     | 7.2.1      | Bus Interface                            |

|   |     | 7.2.2      | Data Flow                                |

|   |     | 7.2.3      | Priority Offloader                       |

|   |     | 7.2.4      | ALPIDE Control                           |

|   |     | 7.2.5      | Power Control                            |

|   |     | 7.2.6      | UDP Stack and Data Transfer Protocol 149 |

|   | 7.3 | Integr     | ation Tests and Top-level Verification   |

|   | 7.4 | Hardy      | vare Verification                        |

|   |     | 7.4.1      | FireFly FMC                              |

|   |     | 7.4.2      | High-Speed Links                         |

Contents xi

|              |      | 7.4.3   | Slow   | v Con  | itrol        |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 156 |

|--------------|------|---------|--------|--------|--------------|------|-------|------|-------|------|------|-----|----|---|---|-------|---|---|-------|-----|

|              |      | 7.4.4   | GbE    | E and  | IPE          | 3us  |       |      |       |      |      |     |    |   |   |       |   |   |       | 156 |

|              |      | 7.4.5   | 10G    | bE a   | nd p         | DΤ   | ГР    |      |       |      |      |     |    |   |   |       |   |   |       | 157 |

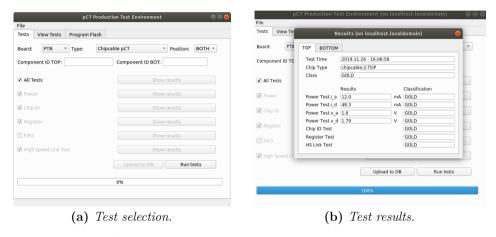

|              | 7.5  | Produc  | ction  | Test   | ing          |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 158 |

|              |      | 7.5.1   | Pro    | ductio | on T         | est  | Box   | х.   |       |      |      |     |    |   |   |       |   |   |       | 158 |

|              |      | 7.5.2   | Min    | i-TC   |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 160 |

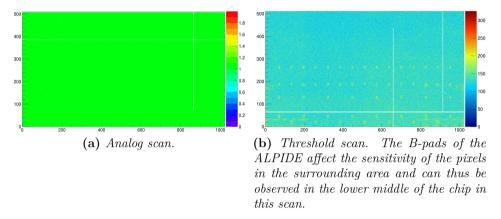

|              |      | 7.5.3   | ALF    | PIDE   | Clas         | ssif | icati | ion  |       |      |      |     |    |   |   |       |   |   |       | 160 |

|              |      | 7.5.4   | Pro    | ductio | on T         | est  | Sof   | twa  | re    |      |      |     |    |   |   |       |   |   |       | 162 |

|              | 7.6  | Version | n Coi  | ntrol  | and          | Со   | ntin  | uou  | ıs Iı | nteg | grat | ior | ı. |   |   |       |   |   |       | 163 |

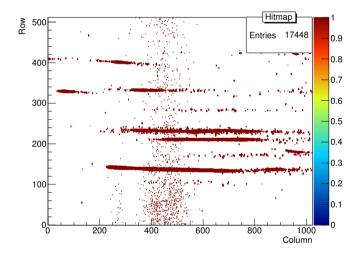

|              | 7.7  | Beam 7  | Tests  | 3      |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 164 |

| 0            |      | , .     |        | 1.0    | . 1          | ,    |       |      |       |      |      |     |    |   |   |       |   |   |       | 105 |

| 8            |      | clusion |        |        |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 167 |

|              | 8.1  | Conclus | _      |        |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       |     |

|              | 8.2  | Outloo  | ok .   |        |              |      |       |      |       |      | •    |     |    | ٠ | • | <br>٠ | • | • | <br>• | 169 |

| $\mathbf{A}$ | List | of Pub  | blica  | tions  | $\mathbf{s}$ |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 171 |

|              | A.1  | As Prir | mary   | Aut    | hor          |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 171 |

|              | A.2  | Publica | ation  | s Sig  | nific        | ant  | ly C  | Cont | rib   | uteo | łТ   | о.  |    |   |   |       |   |   |       | 171 |

|              | A.3  | Master  | s's Tl | neses  | as (         | Co-S | Supe  | ervi | sor   |      |      |     |    |   |   |       |   |   |       | 171 |

|              | A.4  | All Pul | blica  | tions  |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 172 |

| ъ            | DI   | I D-4-  | TD     |        |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 173 |

| В            | -    | J Data  |        |        | 1            |      |       |      |       |      |      |     |    |   |   |       |   |   |       |     |

|              | B.1  | The HE  |        |        |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       |     |

|              | B.2  | The TR  |        |        |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       |     |

|              | B.3  | The EM  |        |        |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       |     |

|              | B.4  | Examp   | ole of | a pB   | ₹U fi        | ram  | ie .  |      |       |      | •    |     |    | ٠ | • |       | • |   | <br>• | 178 |

| $\mathbf{C}$ | рСТ  | Data    | Tra    | nsfer  | Pr           | oto  | ocol  | l    |       |      |      |     |    |   |   |       |   |   |       | 179 |

|              | C.1  | pDTP    | Clie   | at .   |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 179 |

|              | C.2  | pDTP    | Serv   | er .   |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 180 |

|              |      | C.2.1   | Serv   | er St  | atus         | 3.   |       |      |       |      |      |     |    |   |   |       |   |   |       | 181 |

| D:           | ել:- |         |        |        |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 105 |

| Ы            | onog | raphy   |        |        |              |      |       |      |       |      |      |     |    |   |   |       |   |   |       | 187 |

xii Contents

# List of Abbreviations

$\mu$ C Microcontroller

$10{

m GbE}$   $10{

m Gb}$  Ethernet

ADC

ALICE A Large Ion Collider Experiment

Analog-to-Digital Converter

ALPIDE ALICE Pixel Detector

ALWM ALPIDE Lightweight Model

API Application Programming Interface

ARP Address Resolution Protocol

ASIC Application-Specific Integrated Circuit

AXI Advanced eXtensible Interface

AXIS AXI Stream

BER Bit Error Rate

BFM Bus Functional Model BTBI Board-to-Board Interface

BTMR Block triple modular redundancy (TMR)

CAD Computer-Aided Design CDC Clock Domain Crossing

CERN The European Organization for Nuclear Research

CMOS Complementary Metal-Oxide-Semiconductor

CPU Central Processing Unit CT Computed Tomography

DAQ Data Acquisition

DCS Detector Control System

DDR Double Data Rate

List of Abbreviations

DMAPS Fully Depleted Monolithic Active Pixel Sensor

DPA Dynamic Phase Alignment

DTC Digital Tracking Calorimeter

DTMR Distributed TMR

ELT Enclosed Layout Transistor FEC Focused Expression Coverage

FEE Front-End Electronics

FIFO First In First Out

FMC FPGA Mezzanine Card FPC Flexible Printed Circuit

FPGA Field Programmable Gate Array

FSM Finite-State Machine

GbE Gigabit Ethernet GBT GigaBit Transceiver

HAL Hardware Abstraction Layer

HDL Hardware Description Language

HEH High Energy HadronHEP High Energy Physics

IP Internet Protocol

IP Intellectual Property

ITS Inner Tracking System LHC Large Hadron Collider

LSB Least Significant Bit

LTMR Local TMR

LUT Look-up Table

LVDS Low-Voltage Differential Signaling

MAC Media Access Control

MAPS Monolithic Active Pixel Sensor

MGT Multi-Gigabit Transceiver

MLVDS Multi-point LVDS

MMCM Mixed-Mode Clock Manager

PCB Printed Circuit Board

pCT Proton CT

List of Abbreviations xv

PCU Power Control Unit

pDTP pCT Data Transfer Protocol

PHY Physical Layer

PLL Phase-Locked Loop

PPM Parts Per Million

PRBS Pseudo-Random Binary Sequence

pRG Proton Radiography pRU pCT Readout Unit

PSD Position-Sensitive Detector

PTB Production Test Box

QSFP Quad Small Form-factor Pluggable

RAM Random Access Memory

RERD Residual Energy-Range Detector

RIU Register Interface Unit RMW Read-Modify-Write

RSP Relative Stopping Power

RTL Register Transfer Level

SBI Simple Bus Interface

SEL Single Event Latch-up

${\bf SerDes} \qquad {\bf Serializer/Descrializer}$

SEU Single Event Upset

SEUPI Single Event Upset Probability Impact

SFP Small Form-factor Pluggable

SGMII Serial Gigabit Media Independent Interface

SMD Surface-Mount Device SNR Signal-to-Noise Ratio SOBP Spread-Out Bragg Peak

SoC System-On-Chip

SpTAB Single point Tape Automated Bonding

SRAM Static Random Access Memory

TC Transition Card

TCP Tape Carrier Package

TCP Transmission Control Protocol

TDD Test-Driven Development

TID Total Ionizing Dose

TMR Triple Modular Redundancy

UART Universal Asynchronous Receiver/Transmitter

UDP User Datagram Protocol

UI Unit Interval

ULTM Ultra-Light Test Modules

UUT Unit Under Test

UVVM Universal VHDL Verification Methodology

VHDL Very High Speed Integrated Circuit Hardware Description

Language

VVC VHDL Verification Component

XGMII 10 Gigabit Media-Independent Interface

ZIF Zero Insertion Force

#### Introduction

This chapter begins with a brief introduction to particle therapy for cancer treatment. Imaging for particle treatment dose planning is then concisely discussed. Furthermore, proton CT is introduced as a concept. Subsequently, the Bergen proton CT prototype, the Digital Tracking Calorimeter, is outlined. Finally, the primary objective and the major contributions of this work are concisely presented.

Cancer treatment research is an important and active field. Millions of people worldwide get diagnosed with cancer every year, and the disease is the second leading cause of death, trailing only cardiovascular diseases. Based on the cancer type, the stage of the disease, and the risk for critical organs, various types of therapy are offered to the patient: (1) chemotherapy, (2) surgery, and (3) radiation treatment. The purpose of radiation treatment, also known as radiotherapy, is to control or kill cancerous cells using ionizing radiation. It is important, however, to also avoid damaging the healthy tissue surrounding the cancer cells. The most common type of radiation treatment utilizes X-ray photons, yet, in the last couple of decades, the use of charged particles for radiation treatment has increased.

By the end of 2016, more than 170 000 patients had been treated with particle therapy [1], most of whom with protons. Carbon ions are also used at some facilities like the HIT facility in Heidelberg. In 2018, it was decided that Norway should provide particle therapy as an option to cancer patients in the form of

proton therapy and that two treatment centers would be built, one in Oslo and one in Bergen [2].

#### 1.1 Particle Therapy

Particle therapy is distinguished from conventional X-ray therapy in that it utilizes massive particles rather than massless photons [3]. Although both neutral and charged particles can be employed, neutral particles are not often used [1]. Particle therapy promises several advantages compared to X-ray therapy. The advantages stem from the fact that a charged particle interacts with matter in a fundamentally different way than photons. Contrary to photons, protons and other charged particles stop. While traversing through matter, a charged particle will interact with orbital electrons, and in each of these collisions, it will lose a tiny amount of energy and slow down. Eventually, close to the stopping point, the particle will release most of its energy. This is called the Bragg peak.

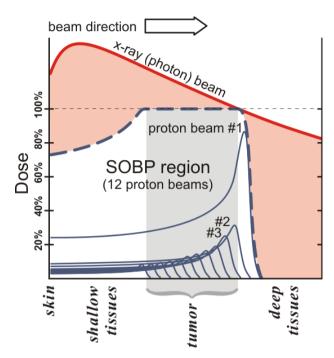

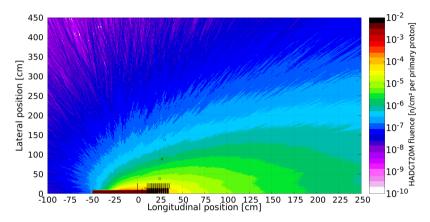

The relative depth dose distributions of photons versus protons are given in Figure 1.1. A photon beam, as shown by the red line, delivers a large dose to the healthy tissue. A harmful dose bath is shown both in front of and behind the tumor. A proton will deposit only about 30 percent of the Bragg peak maximum dose to the area in front of the Bragg peak [3]. Beyond the Bragg peak, the dose deposited falls to virtually zero. It is clear, however, that a mono-energetic proton beam will deliver most of its dose to only a small portion of the tumor. This is illustrated by the multiple blue lines, each representing a beam with a certain energy. A therapeutic proton beam needs to cover the entire tumor area illustrated by the grey box. Thus the beam distribution is artificially expanded by using protons with varying energies. The dotted blue line shows the expanded beam's depth dose distribution. The combination of protons with different characteristics produces a Spread-Out Bragg Peak (SOBP); the area of the accumulated Bragg peaks of many protons. Bear in mind that some broadening of the Bragg peak also occurs when combining protons in a mono-energetic beam. This broadening is due to the statistical nature of the energy loss process and is called range straggling [4].

**Figure 1.1:** Comparison of relative depth dose distributions of photons versus protons. From Filipak [5]. Licensed under CC BY-SA 3.0.

Particle therapy treatment has several potential advantages compared to conventional X-ray therapy:

#### (1) Less total dose to healthy tissue

A photon beam delivers a much larger dose to healthy tissue than a proton beam. Any reduction of dose entails that secondary radiation effects may also be reduced [6]. There is an increasing number of studies indicating that this will translate into clinical advantages [7]. Because of this, particle radiotherapy can be considered for the treatment of pediatric tumors in the hope of reducing complications later in life for child patients.

#### (2) Finite range and sharp dose cut-off

Since charged particles stop and because healthy tissue behind a tumor will receive next to no dose, it is appealing to consider particle treatment for tumors next to critical structures. There is some clinical evidence that patients 4 1.2. Proton CT

with tumors close to critical structures are benefiting the most from proton treatment [8].

#### (3) Increased tumor control

Because the dose delivered to healthy tissue is dramatically lower, it is possible to increase the dose to the tumor. The sharp dose cut-off following the Bragg peak also contributes. A higher dose to the tumor helps to control the tumor.

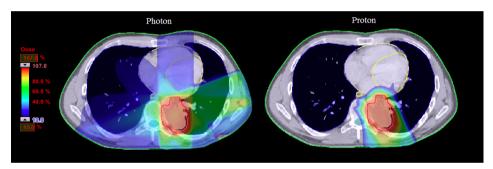

In Figure 1.2 we clearly see how some of these advantages are manifested in the dose plans for treatment. The photon treatment has a sizeable low-dose bath behind the tumor, shown in blue, while the proton treatment virtually leaves no dose trailing the tumor.

**Figure 1.2:** A comparison between two dose plans for irradiation of a paravertebral sarcoma in the lung, overlaid on CT images [4]. Left: (conventional) Intensity Modulated Radiation Therapy with photons. Right: Intensity Modulated Proton Therapy.

#### 1.2 Proton CT

A single proton's range is uncertain because of the range straggling. Even in simple water phantoms, predicting where a proton will stop is a statistical process. Nevertheless, range straggling is an unavoidable uncertainty and is not a significant problem for particle treatment. However, the tissue in front of the tumor is a mixture of muscles, bones, and fat, and the incomplete knowledge of the chemical composition and density of this and the tumor itself can become a significant source of range uncertainty [7]. When creating dose plans for particle treatment, sharp gradients of the dose distribution are generated around the

tumor. Even a small uncertainty about the range of the beam can cause drastic changes to the dose deposited to healthy tissue [7]. This can be detrimental to patients that have a tumor that lies close to critical structures, i.e., one of the patient groups which can potentially benefit the most from particle radiotherapy. Although it is impossible to remove the range uncertainty completely, one can strive to diminish it compared to the values used in the clinic today.

Every type of radiation treatment is preceded by the calculation of a treatment or dose plan that indicates the dosage delivered to various tissue of the treatment volume. Today, one obtains information from conventional X-ray computed tomography (CT) imaging to prepare dose plans for particle treatment. CT imaging provides the so-called Hounsfield units, or the CT number, of the volume in question. This number describes how the intensity of an X-ray beam is attenuated by the volume. Particle treatment, however, uses the relative stopping power (RSP) of the volume to calculate the beam's range. It is possible to convert Hounsfield units to RSP, but this conversion is not a one-to-one mapping [9]. The conversion introduces range uncertainties of up to a total of 2 to 3 percent. Most of this uncertainty comes from the table lookup of the ionization potential [4].

By directly measuring the proton RSP of the tissue, this uncertainty is minimized to the uncertainty of the measurement. One way to do this measurement is by using protons or other charged particles for imaging. This involves transmitting high-energy protons through the volume and measure how the volume in question affected the energy of the particles. Since the 1960s, several types of proton radiography (pRG) and proton computed tomography (pCT) have been proposed. Some of the systems are proton integrating systems that calibrate a signal in a detector with the length traversed, averaging over multiple protons. This approach has some significant negative implications in terms of image quality [10]. Thus, the field of pCT research has mostly started to focus on proton tracking devices.

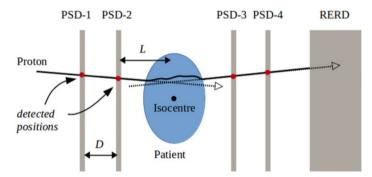

The proton tracking method involves the measurement of individual protons and the calculation of the residual energy of each particle. The residual energy is the particle's remaining energy after passing through the volume to be measured. This way, one can reconstruct estimates of the particles' trajectories or tracks through the patient. The tracks are estimated based on advanced most-likely path algorithms, that also minimizes the effect of the multiple Coulomb scattering on the spatial resolution [11]. Based on these tracks the proton's average energy loss along the path is calculated. Finally, by transmitting a large number of protons from different angles, the average RSP of each voxel of the volume can be calculated [4]. Proton tracking pCT systems typically consist of multiple position-sensitive detectors (PSD), two in front of the patient, and two behind the patient [10]. These detectors obtain crucial information about the particles' position and direction at both entrance and exit of the measured volume. In addition, a residual energy-range detector (RERD) is used to obtain the particles' residual energy. In Figure 1.3 we see how the different detectors obtain the information about each particle.

**Figure 1.3:** A typical double-sided proton-tracking proton radiography/proton CT system. Consists of four PSDs layers and a RERD. Figure from Poludniowski [10]. Licensed under CC BY 4.0.

### 1.3 Digital Tracking Calorimeter

Several of the suggested pCT prototypes make use of a crystal-based RERD. For instance, a collaboration of Loma Linda University (LLU) and others have presented a head-scanner prototype that employs CsI crystals for the RERD [12]. The use of a crystal-based calorimeter significantly reduces the proton rate capabilities of the device, and for the LLU-prototype, this leads to a CT scan time of several hours [10]. To use protons for clinical imaging the scan time

must be reduced. Not only because it is unreasonable to keep a patient still for so long, but also because the anatomy of the patient is susceptible to change over time. This change might potentially dramatically increase the proton range uncertainty [13]. To increase the proton rate, and thus reduce the imaging time, the use of a range telescope-system to construct a RERD has been proposed by Esposito et al. (with silicon strip detectors) [14] and by Pettersen et al. (with pixel detectors) [15]. Specifically, Pettersen et al. introduces the concept of a Digital Tracking Calorimeter (DTC) that:

- (1) is digital in that it only detects energy depositions over a certain threshold, i.e. either a 0 (no hit) or a 1 (hit).

- (2) tracks the path of individual particles through the detector medium.

- (3) calculates the energy of each particle based on the particle range.

In the proposed DTC by Pettersen et al., the RERD is constructed by several layers of high-granularity pixel detectors. In fact, it is constructed the same way as the PSD in the same system. Therefore, the entire prototype is simply several layers of pixel detectors. Between each layer of the RERD, metal sheets are installed to gradually absorb energy, and eventually, stop the particles within the detector. These sheets are also used to obtain structural stability for the sensor chips. For the RERD, aluminum is the metal of choice based on the proton stopping and scattering power, durability, secondary neutron production, and more [16]. To minimize the uncertainty of the measurement, physics simulations with different thicknesses of the energy-absorbing aluminum layers between each sensor layers were done. The study concluded that an absorber thickness of 3.5 mm both minimizes the uncertainty of the measurement and restricts the total number of sensor layers required to provide sufficient tracking and range resolution. A total of 41 sensor layers are needed for the RERD-part of the DTC to make sure protons with an energy range of 35 MeV to 245 MeV will stop in the detector, and thus, be appropriately measured.

The PSD layers must be very thin and should contain as little mass as possible to reduce multiple Coulomb scattering while measuring the position and angle of the incoming particle track. Thus, the absorber is replaced with a low-mass stabilizer that the sensors are mounted on. A 0.2 mm thick carbon fiber sheet

is chosen based on its low mass and its structural properties.

#### 1.3.1 Single-sided proton CT

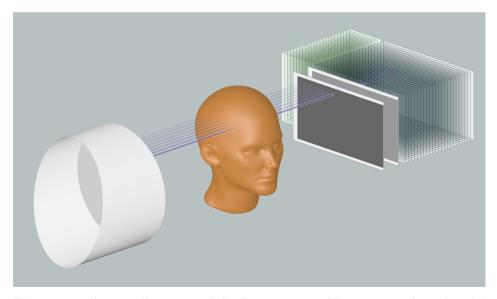

Sølie and Voltz et al. investigated the feasibility of proton imaging without front trackers and instead rely on the information given by the beam delivery system [11]. Avoiding the use of front trackers has several benefits, especially during the design and assembly stages. First, it significantly reduces the cost of sensor layers, but one can also increase the particle rate as the pairing of hits on the front and the rear trackers are avoided [17]. Furthermore, in a clinical setting, one avoids the complexities involved in aligning the set of front and rear trackers. Critically, one will not be required to move the front trackers away before starting proton therapy operations, which allows the DTC to be used as an online treatment dose deposition monitor via online in-vivo imaging. Single-sided pCT simulations indicate a somewhat reduced spatial resolution, but Sølie and Voltz suggest the development of dedicated reconstruction algorithms for this type of detector setup [11]. See Figure 1.4 for an illustration of the single-sided pCT prototype.

**Figure 1.4:** Artistic illustration of the Bergen proton CT prototype. A single-sided scanner does not use tracking layers in front of the measured object.

#### 1.3.2 Particle Energy Calculations

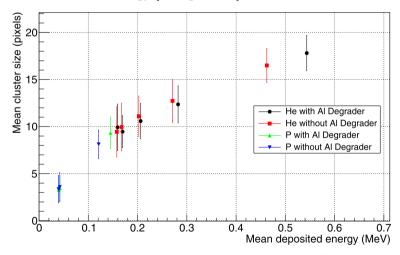

The residual energy of a particle can be calculated by observing in which layer of the RERD the particle stops. This calculation is derived from the Bethe range-energy relationship. Several analytical models are investigated by the Bergen pCT group [18]. One can further improve the residual energy calculation by employing more information from the pCT detector. Even though the DTC only provides digital pixel hit data, each particle that moves through the detector will deposit energy relative to its velocity/energy. Tambave et al. showed how the mean cluster size changes relative to the energy loss of the particle using the same sensor as the DTC, the ALPIDE, as seen in Figure 1.5 [19]. The ALPIDE is further discussed in Section 2.3. Fitting a Bragg peak curve to the combined information of cluster size and particle range will provide an accurate measure of the residual energy [4, Figure 5.5].

**Figure 1.5:** The mean cluster size versus the energy loss of the <sup>4</sup>He ions and protons in the ALPIDE chip [19].

#### 1.4 Primary Objective and Main Contributions

In this introductory chapter, we have introduced some of the motivation for developing a proton CT detector. Note that the development of such a detector is a big collaborative effort, of which this thesis is an integral part. The Bergen pCT group started the initial work in 2012 and received funding for the design

and the construction of the DTC prototype in late 2016. The proof-of-principle of using a digital tracking calorimeter for pCT was based on experiments with an electromagnetic sampling calorimeter containing MIMOSA23 sensor chips as sensitive layers [15].

The work to develop the pCT readout electronics, however, was built upon the development of the readout electronics of the ALICE Inner Tracking System (ITS). As is discussed later in this thesis, it became evident that the pCT electronics had different requirements, and therefore, the development efforts were separated. Nevertheless, several components from the ITS development remain in the pCT system.

At the time of writing, the Bergen pCT prototype, although delayed by COVID-19, is getting close to the start of production of the front-end electronics. I have been involved with many parts of the detector development, including design and testing of (1) system design (Chapter 2), (2) front-end electronics (Chapter 3), (3) readout and control electronics and field programmable gate array (FPGA) firmware (Chapter 4, 5, 6 and 7), and various other tasks. The prime objective of this thesis is to present a near-complete technical electronics solution to the Bergen pCT prototype. Although I have been involved with many parts of the detector development, most of my focus has been on the data acquisition and detector control electronics FPGA firmware, of which I have been the sole developer. The thesis reflects this since most of Chapter 4, 5, 6 and 7 are concerned with the FPGA firmware development. Parts of this work have been presented at an international conference and have been subject to peer review for publication in journals (see Appendix A).

## System Design and Electronics Components

In this chapter, the requirements of the proton CT DTC system are discussed in detail before an overview of the system electronics design is provided. The individual parts of the system are then presented in more detail. As the work of this thesis focuses on the electronics of the system, the chapter emphasizes the various parts of the front-end electronics and the readout system. Finally, some other prototypes related to the development of the project are mentioned.

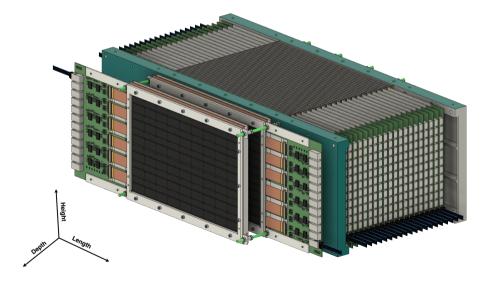

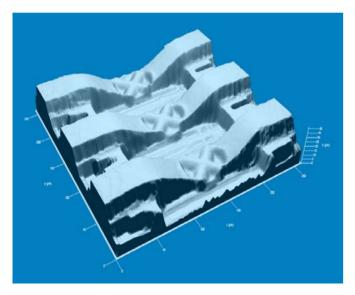

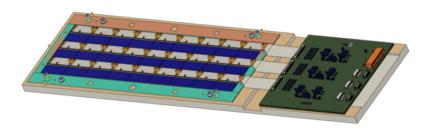

**Figure 2.1:** 3D design of the pCT Digital Tracking Calorimeter. The figure is provided by courtesy of Anthony van den Brink. The two tracking layers are shown in front, with the calorimeter layers behind. The detector is shown without the cooling plate and fans.

#### 2.1 Detector Requirements and Considerations

The goal of the pCT prototype is to prove that a DTC can be used for CT imaging with protons and overcome most of the critical limitations of the already existing prototypes. This will improve the dose planning accuracy for particle radiation therapy. Although both the conceptual and the technical requirements have been subject to revision during the research project period, a few major requirements are regarded as the most important. Note that the following requirements are focused mainly on the most basic physics requirements for particle tracking, and subsequently, the electronics requirements needed to fulfill the former. The following list of requirements is in addition to the specifications of the number of layers and absorber thickness already described in Section 1.3.

- (1) pCT is most likely to be beneficial for tumors close to critical structures, because particle treatment of such tumors requires high accuracy. Consequently, the detector must be large enough to construct an image of a human head. The width and height of the detector are presented in Section 2.4. To verify that the DTC can be used to improve dose planning for radiation treatment, the detector will be tested using so-called phantoms. Phantoms are representations of an actual physical object and are often made to resemble a part of the human body. Phantoms are used both in the testing of new types of detectors and to calibrate existing detectors' real-world data to the data from advanced simulations.

- (2) The DTC must be able to handle clinical beam settings so that it can be tested and used in a clinical facility like HIT in Heidelberg, Germany. This requirement entails that the DTC must withstand a particle flux within the nominal values of clinical proton beams. Also, the pCT will operate with a scanning pencil beam. The detector must be able to handle a rate of 10<sup>7</sup> particles/s. This number is in the upper range of protons required to construct a 2D-projection of a human head and is also in the lower range of the typical flux of the clinical proton beam machines like the one at HIT. To opt for a flux that is rarely used in these facilities might have consequences for the information that is possible to acquire from the beam optics of the facilities.

As mentioned in the introductory chapter, most pCT implementations are using

a crystal-based RERD, limiting the rate of particles that can be concurrently tracked. By replacing this approach with silicon-pixel detectors, one of the main goals of the Bergen pCT prototype is to drastically increase the rate of particles. The increased particle rate will speed up the imaging process to the point where each 2D-projection is completed in a matter of seconds, and a complete 3D-tomography is completed in a matter of minutes [17]. A full 3D-tomography is necessary to generate a full RSP voxel map of the measured volume.

- (3) The calculation of a particle's residual energy is mainly based on its track through the detector and where it stops. The track can be used together with knowledge of the detector design to accurately estimate how much material the particle has traversed. Monte Carlo simulations provide information about how particles are expected to behave in a precise model of the detector, and what the residual energy of particles should be if they stop in a particular layer. However, it is complicated to construct a reasonable model and simulation of the detector if the detector is built in an inhomogeneous way. This is the reason why one must strive to build the detector as homogeneous as possible and avoid intricate structures.

- (4) A DTC needs to be able to track individual particles, but due to the high rate, it can be challenging to differentiate between particles. For this reason, the detector needs to have a high spatial resolution. This means that the size of each sensor-pixel needs to be small. Furthermore, there should be hardly any dead area between the pixels.

- (5) It is an advantage for clinical use if the detector can be designed without the use of gas or high voltage. The complete detector should also be compact and have a simple air/water cooling system. Details about the mechanics and cooling can be found in [17].

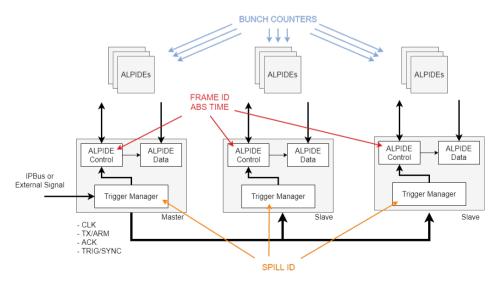

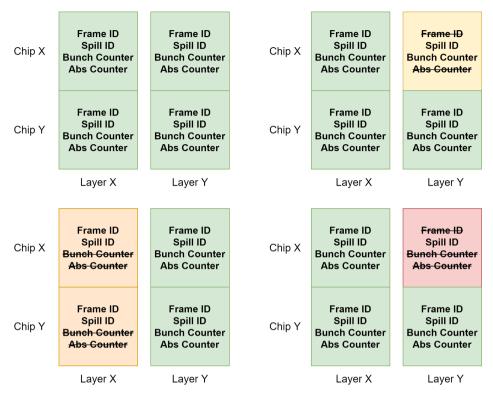

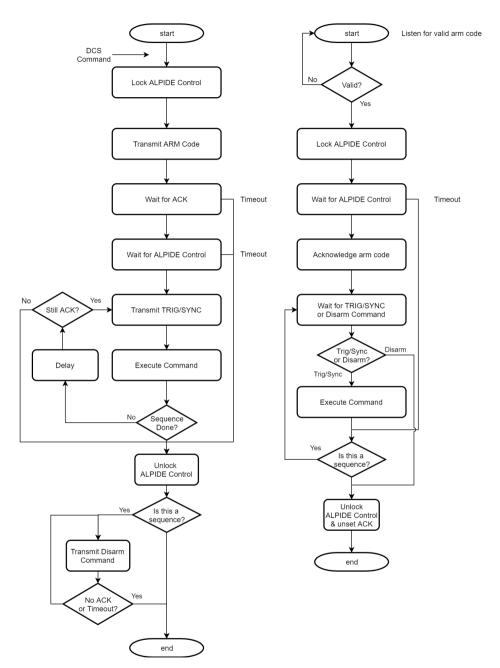

- (6) To be able to construct the track of each particle through the detector, the pixel address information from all the layers combined with the time of each hit must be collected. It is crucial that all sensors in all layers adhere to the same time-domain so that the particles hit in two different layers are marked with the same timestamp and/or frame ID. Hits in two layers with different

parameters will not be combined to form a track as this indicates that they do not emanate from the same particle. To ensure that all sensors in all layers adhere to the same time-domain, a deterministic and accurate synchronization system is needed.

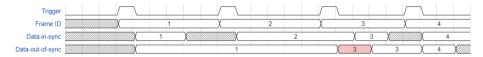

- (7) The pCT detector must continuously sample data with minimal dead-time or integration time. The detector data will be captured by a nominal trigger rate of  $10\,\mu\text{s}$ , and a sampling window of  $9.75\,\mu\text{s}$ , meaning a sampling window gap of  $250\,\text{ns}$ . However, these settings can be configured to optimize for certain conditions, for instance, to reduce the number of double hits (see Section 2.3.1). The detector electronics must handle the resulting data with minimal data loss. The data rate calculations are done with the worst-case trigger rate of  $5\,\mu\text{s}$  (see Section 5.4).

- (8) In addition, the system should have a trigger-less readout architecture. This means that the data acquisition should be made possible without any external nor any high-level trigger system implemented. Note that this does not exclude the use of sensors that require low-level trigger signals as these can originate and be controlled from the data acquisition (DAQ) system itself. This simplifies both the design and the operation of the detector system.

- (9) Although the primary objective of the pCT scanner is to investigate imaging with protons, the prototype can in principle be used to investigate CT with any charged ions, e.g., carbon or helium.

#### 2.2 Detector Overview

The DTC prototype consists of the parts listed below.

Front-end High-granularity pixel sensors with high-speed data

readout bonded to custom glue electronics providing

an interface to the external detector electronics.

**Transition Card** A simple printed circuit board (PCB) that supplies

power to the sensors, as well as providing the electrical connections between the sensors and the DAQ system.

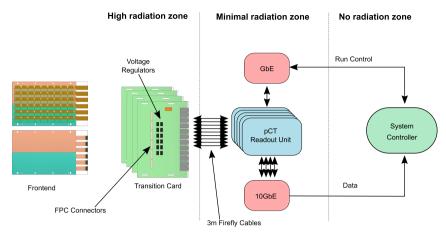

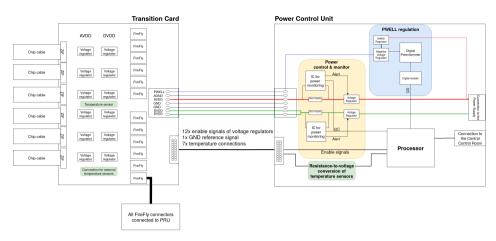

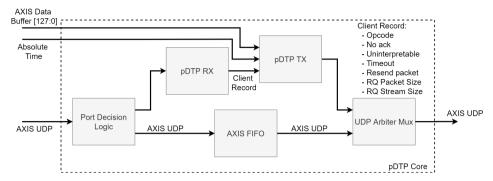

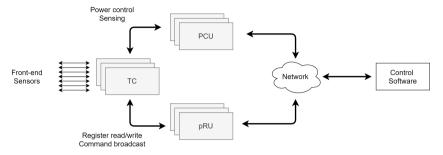

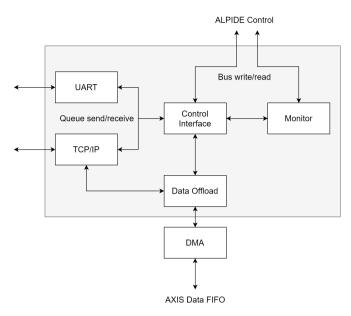

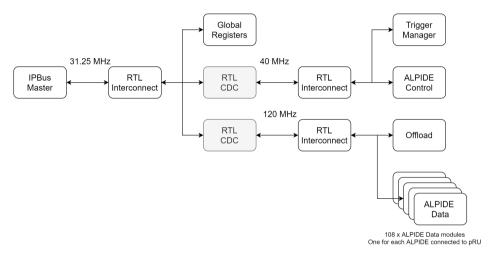

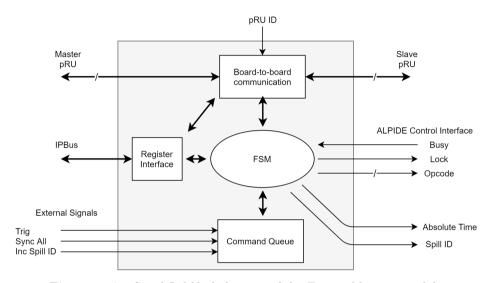

Figure 2.2: The Proton CT readout and control architecture. Notice the different radiation zones of the different aspects of the system. The PCU is not depicted in the figure, but is placed within the same radiation zone as the readout unit.

| Readout Unit | The pCT Readout Unit (pRU) is the interface to     |

|--------------|----------------------------------------------------|

|              | the sensor chips and acts as the communication hub |

|              | between the sensors and the control room. The pRU  |

|              | is the main component of both the DAQ and the      |

|              | control system.                                    |

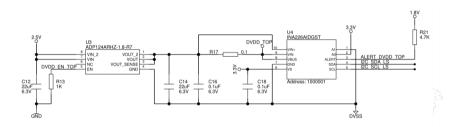

Power Control Unit

The Power Control Unit (PCU) and the power net-

work provides power to the front-end electronics and

is also part of the control system.

**Server Farm** One or more computers are serving to handle the data

stream (DAQ) from the sensors, as well as controlling

the operation of the detector (DCS).

Network Infrastructure for connecting the readout units and the power control units to the control server form

the power control units to the control server farm.

The pCT readout and control architecture is shown in Figure 2.2. The frontend components are connected to the Transition Card (TC), which is further connected to the pRU. Note how these parts are located in zones with different radiation levels. In Section 4.6 the radiation environment of the pCT system is discussed. The pRUs are connected to the system controller via two separate Ethernet-based networks; one for run control and one for data readout.

The control server farm and the network components are not discussed further

in this thesis. The PCU is only briefly mentioned in Section 2.8. The other parts of the system are discussed in detail below.

#### 2.3 Monolithic Active Pixel Sensor

In general, monolithic active pixel sensors (MAPS) have a pixel matrix where each pixel has a dedicated signal amplifier and an ADC or a simple threshold discriminator. Often, the detector chip also incorporates a digital transmission unit combined with the pixel matrix integrated on the same piece of silicon. One can differentiate between high-voltage CMOS technology and MAPS [20]. MAPS generally have a very low power consumption and can be made radiation tolerant [21]. Low power consumption and radiation tolerance are often two of the most crucial requirements for sensors used in high energy physics (HEP) experiments and are also required for the pCT detector.

Several MAPS have been developed specifically to be used in HEP and similar applications. For instance, the Ultimate-2 sensor for the STAR experiment [22]. Generally, for MAPS, charge collection is dominated by diffusion, but by drift near the electrode [23]. However, for high-voltage monolithic CMOS sensors and fully depleted MAPS (DMAPS), for instance, the MuPix7 developed for the Mu3e Experiment [24], drift is the driving force of the charge collection. The drift component of the charge collection is an important variable of the signal-to-noise ratio of the sensor [20]. A DMAPS is considered used in the high-luminosity Large Hadron Collider (LHC) upgrade of the ATLAS detector in 2025 [25, 26]. Most of the DMAPS alternatives that would be usable for the pCT detector are still under prototyping or testing and were not available for consideration during the early stages of pCT development.

The selection of a MAPS for the pCT detector was made based on three main considerations: (1) data readout speed, (2) pixel size, and (3) availability. The University of Bergen is involved with the ALICE experiment at the LHC at The European Organization for Nuclear Research (CERN), and thus had experience with the ALPIDE, which was developed for the ALICE ITS detector. The ALPIDE was the first MAPS to implement a zero-suppression architecture to increase readout speed and reduce readout power usage [25]. Below, we provide

the properties and characteristics that demonstrate that the ALPIDE is a valid sensor choice for the pCT detector.

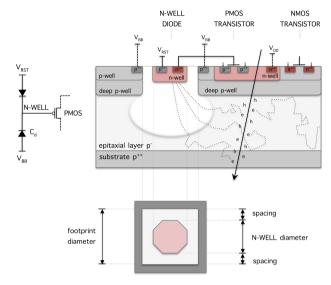

**Figure 2.3:** Equivalent circuit schematic, cross-section and footprint of the ALPIDE pixel [27]. Notice how electron-hole pairs are produced in the epitaxial layer by the ionizing particle.

#### 2.3.1 The ALICE Pixel Detector

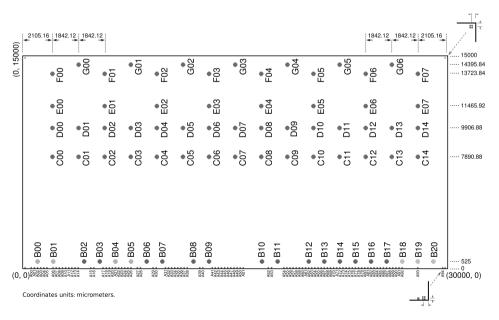

The ALPIDE consists of  $512 \times 1024$  pixels, and the size of each pixel is only  $29.24 \,\mu m \times 26.88 \,\mu m$  [28]. The chip measures  $15 \,mm(H) \times 30 \,mm(W)$  of which  $1.2 \times 30 \, \text{mm}^2$  is a digital periphery region devoted to control and readout functions. The pixel itself is constructed as a charge collection diode, indicated as  $C_d$  in equivalent circuit schematic in Figure 2.3. A particle hitting the chip will cause electron/hole-pairs as the particle ionizes the material along its path. These electrons diffuse in the epitaxial layer and can be collected by the diode when the force of the depletion region causes the electrons to drift towards the n-well. When electrons are collected the sensing diode experiences a change of potential of a few tens of mV relative to the number of electrons collected [29]. The electrons can also diffuse to nearby pixel diodes, causing several pixels to fire, causing so-called clusters. The size of the depletion region of the diode versus the drift volume can be controlled by supplying a negative bias voltage to

the chip. An increased depletion region increases the granularity of the sensor by restricting the number of pixels affected by a particle but will also cause a reduction of the cluster sizes, which in turn yields a lower energy resolution. In any case, the ALPIDE is considered to be a high-granularity pixel sensor, which was mentioned as a requirement in Section 2.1.

The ALPIDEs can be produced with different substrate thicknesses. Specifically 100 µm and 50 µm. Employing a thin chip will reduce the multiple Coulomb scattering of the particles when they pass through the sensor material. Also, less energy is lost in the sensor itself. A very thin chip can be more difficult to handle during the bonding and mounting process, therefore the RERD layers, also called the calorimeter layers, of the detector will employ the 100 µm version. As discussed in Section 1.3, the position-sensitive detector (PSD) layers, also called the tracking layers, need to be very thin, thus the 50 µm version will be utilized in these layers.

MAPS can be constructed to be radiation tolerant. Previously, the ASICs used in the LHC often employed enclosed layout transistors (ELT) and guard rings to achieve the required radiation tolerance [30]. ELTs help keeping the leakage current at a low level after irradiation [31]. On the other hand, ELTs introduce several behavioral differences compared to standard linear MOS transistor models. Most critically limiting the W/L ratio to large values, thus severely constraining the designs [32]. With smaller CMOS technology nodes, one has observed a reduced total ionizing dose (TID) sensitivity, in turn making the ELT approach redundant and complicated [30]. The ALPIDE achieves sufficient TID tolerance by using the TowerJazz 0.18 µm CMOS technology with a gate oxide thickness of roughly 3 nm [33, 34]. To protect the sensitive digital control circuits of the sensor from radiation-induced failures (see Section 4.6), mitigation techniques like triple modular redundancy (TMR) are employed [29, 28, 35]. Also, a deep p-well, as seen in Figure 2.3, is shielding the digital logic and preventing the n-well from collecting signal charge [20, 36].

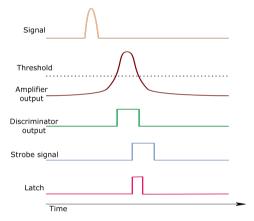

The charge collection diode is connected to an analog amplifier circuit. The amplifier uses a slow shaping time, between 1-2 µs, to save power [36]. In Figure 2.4 the pixel timing diagram is shown. A global threshold level is used

to discriminate the signal, reducing the number of fake hits, i.e., signal changes caused by noise. The discriminator outputs a digital signal indicating a hit. Thus, the sensor only indicates whether there is a signal or not. The digital nature of the pixel electronics means that no information regarding the strength of the signal is stored, causing loss of information about the particle type and energy. However, as indicated in Section 1.3.2, some information about the deposited energy can be extracted from the cluster size. Also, because of the digital nature of the pixel, meaning that a signal below the global threshold level is ignored, we say that the data is naturally zero-suppressed.

**Figure 2.4:** ALPIDE Pixel Timing Diagram [37]. The latch signal is high when the discriminator output and the global strobe signal is asserted at the same time.

Each pixel has a 3-bit memory called the multi-event buffer. For a hit to be stored the discriminator output must coincide with the global strobe window signal. The strobe signal usually originates from an external trigger signal, and the strobe window length can be configured globally. The use of a global strobe signal also implies that the ALPIDE has a global-shutter readout architecture. This contrasts with the rolling-shutter architecture of the Ultimate-2 sensor [22]. The slow shaping time of the analog pixel circuit means that the signal might be captured by several strobe windows if the gap between them is short.

#### 2.3.2 Data Interface

The ALPIDE can be set in different modes depending on expected data rates and operation. The mode names are based on where in the ALICE ITS detector the specific mode is used. The inner barrel mode is used in the three innermost layers of the ITS, where the expected data rates are the highest. Outer barrel mode, however, is used in the middle and outer layers of the detector, where the data is low enough to combine the data outputs of multiple chips without buffer overflows and data loss. Because of the expected data rates of the pCT, see Section 5.4, all ALPIDE chips of the DTC are configured in inner barrel mode.

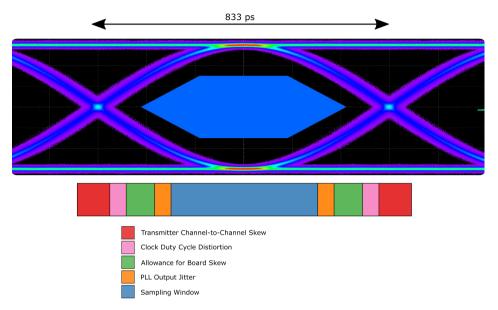

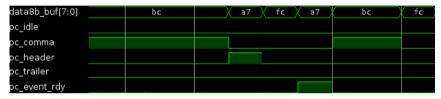

The use of the inner barrel mode entails that the chip utilizes a high-speed low-voltage differential signaling (LVDS) link with a maximum speed of 1.2 Gb/s to offload the pixel hit data. The data is 8B/10B-encoded by default to minimize data errors. This encoding scheme is standard in high-speed electronics and ensures link DC-balance, allows for checking for single-bit errors in an 8-bit word, and provides special control words for word alignment [38]. Thus, the maximum data throughput of the chip is 960 Mb/s. After configuration, the data link is always on, transmitting comma words when there is no data. The ALPIDE employs the K28.5 comma control word. As no clock is transmitted alongside the data, the comma word is used by the FPGA firmware for clock/data recovery and to align the first bit of the word.

Experience while handling the chip in different implementations has shown that the ALPIDE data link is susceptible to jitter, and careful considerations must be made at multiple levels of the electronics implementation. The on-chip phase-locked loop (PLL) must be very stable to ensure the optimal data link performance. This is further discussed in Section 2.3.5, 2.5, and 3.2.4.3.

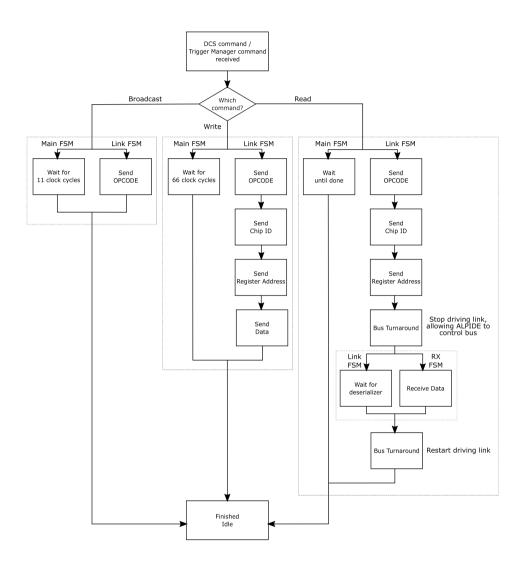

#### 2.3.3 Slow Control

A slow control link is used for non-data communication between the ALPIDE and the readout electronics. A multi-point LVDS (MLVDS) interface is used for this purpose so that multiple ALPIDEs may share the same slow control link. This interface enables the external reading and writing of the internal on-chip status and configuration registers. In addition, the interface acts as a command distribution channel for transmitting triggers to initiate the global strobe signal and synchronizing the clock counter, and more. The ALPIDE has

multiple registers that control the operation of the chip, as well as report the current status. Communication via the slow control link is done with a set of opcodes. As multiple chips share the same link, one can communicate with multiple chips at the same time. By default, the output from the ALPIDE is Manchester encoded to ensure DC-balance.

#### 2.3.4 Other interfaces

To separate the ALPIDEs sharing the same slow control link, a 7-bit chip ID field is used. Note that the ALPIDE has a bug that causes ID 7 to be interpreted as a broadcast ID. Therefore, this ID is skipped in the DTC implementation. Chips configured in inner barrel mode only uses CHIPID[3:0], allowing the remaining pins to be connected to ground.

The ALPIDE is designed to use the LHC system master clock of roughly  $40 \,\mathrm{MHz^1}$ . The clock input expects an MLVDS signal so that multiple chips can share the same clock.

One of the chip interfaces are unused, the reset pin. The power-on-reset functionality of the chip does not function properly. Whether to supply a dedicated reset signal to the chip was discussed, but eventually dismissed. The space needed for a separate trace on the front-end (see Section 2.5), as well as the infrastructure required for the readout electronics, were ultimately the reasons why the use of a reset connection was abandoned. A proper reset procedure can instead be achieved by powering up the digital and analog power supplies in a certain sequence, and then provide reset commands on the slow control interface.

# 2.3.5 Power Supply

The ALPIDE power supply is separated into two domains: the digital and the analog supply. The analog domain is connected to the pixel-matrix analog front-end electronics, the analog biasing circuits, and the ADC block. The digital domain is connected to the pixel-matrix readout circuits, configuration

<sup>&</sup>lt;sup>1</sup>This frequency is associated with the bunch crossing rate of the LHC.

registers, the peripheral readout circuits, as well as the input and output buffers and transceivers. In addition, a separate supply exists for the on-chip PLL for the data transmission unit. As noted above, the PLL supply integrity is vital to ensure the optimal performance of the high-speed data link. Furthermore, one must also supply a bias voltage reference for the substrate and the p-type wells of the pixel matrix region. These two nets are electrically connected via the conductance of the die substrate [29].

The nominal voltage supply of both the analog and digital domain is 1.8 V. However, by increasing this voltage slightly, one has observed better high-speed link performance. Therefore, the DTC system aims to supply roughly 1.9 V to all the sensors. The possible values for the p-well and substrate voltage are ranging from 0V to -6V. A larger negative voltage increases the depletion region of the pixel diode and effectively increases the drift component of the charge collection.

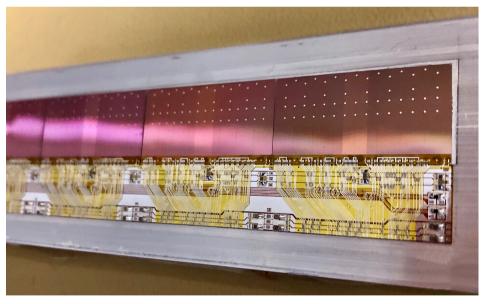

**Figure 2.5:** Photograph of the manufactured string flex mounted on aluminum carrier with ALPIDEs and SMD-components bonded. The ALPIDEs are on the upper part of the image, while the chip cable and the string flex are visible in the bottom part of the image. The chip cable dielectric is shown with a slightly yellow color.

# 2.4 Layer Design

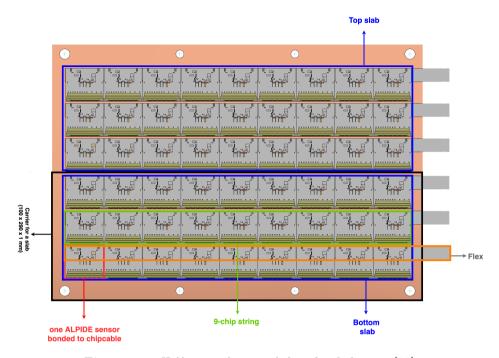

The size of the layer area ( $width \times height$ ) is a major contributor to the cost of the detector, both in terms of the cost of each sensor and the complexity of the surrounding system. A size of  $27 \, \mathrm{cm} \times 18 \, \mathrm{cm}$  is chosen, as this size roughly corresponds to the width and the height of a grown man's head. A layer consists of several submodules:

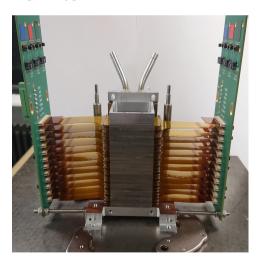

A string is the collection of 9 ALPIDE sensor chips mounted next to each other. The sensors are oriented with the short side facing the other. As the width of an ALPIDE is 3 cm, the total width of the string is 27 cm. On a string, all chips share the clock and slow control signal, and have unique IDs to separate them. Figure 2.5 shows parts of the finished string with ALPIDEs mounted.

Slab A slab is three strings combined to build height. The height of an ALPIDE is 1.5 cm, and the height of the flexible cable is slightly less than that. The total height of a slab is slightly less than 9 cm.

**Half-layer** A half-layer consists of a top and a bottom slab.

As illustrated by Figure 2.6, the sensitive area of a half-layer only covers about 50 % of the total area. This is caused by the need for the power supply and communication interface traces that must reach the sensors from the outside of the detector, and also because the ALPIDE itself has a digital periphery. However, it is crucial that all particles that penetrate the detector are registered by all layers. To ensure that a layer is completely covered with sensitive material, a type of double-module is constructed by flipping a slab to face another slab. From Figure 2.7 one can see the cross-section of multiple layers, and that the sensitive side of one slab covers the non-sensitive side of the other, and vice versa. This type of construction causes an air-gap of about 1.6 mm inside a layer, but also provides space for the required decoupling capacitors. Nevertheless, as the gap is relatively thin compared to the absorber, it is considered to have a minimal effect and constitutes a valid trade-off to ensure full layer coverage. A

24 2.4. Layer Design

total of 108 ALPIDE sensors are needed to construct a complete layer. Thus, a layer consists of a total of  $\sim 56\,\mathrm{Mpx}$ .

Figure 2.6: Half sensor layer and the related glossary [39].

**Figure 2.7:** Cross-section of two layers seen from the side of the DTC, rotated 90 degrees [39]. Note how the ALPIDEs of two corresponding half-layers are positioned at different locations, and that the sensitive area (marked in green) is slightly overlapping. The figure also illustrates how the 3.5 mm absorber layer is constructed of two 1 mm carrier layers, and a 1.5 mm absorber layer placed in between.

# 2.5 Front-end Electronics Bonding and Mounting

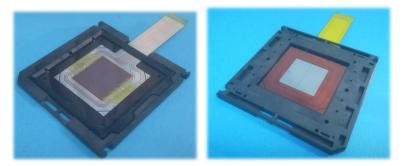

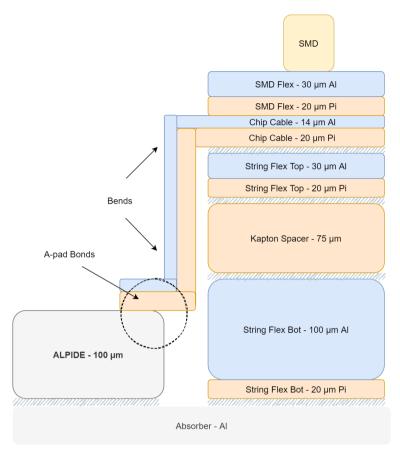

Several types of bonding techniques exist to connect an ASIC's interfaces to back-end electronics. The ALPIDE has two types of bonding pads with different geometries. The type A pads are located on the south side of the chip, and the type B pads are scattered on top of the chip, as shown in Figure 2.8. The B-pads have rounded edges and are 290 µm wide. The A-pads are significantly smaller in size, 88 µm², and are electrically closer to the digital periphery of the chip. The two pad types were added to provide support for different bonding methods. The ALICE ITS adopted a traditional wire-bonding approach using the B-pads and carefully adding small wire bonds to a thin flexible printed circuit (FPC). This is a relatively simple method, but the wire bonds are susceptible to breaking if exposed to the wrong temperature and humidity. Quite extraordinary measures must be taken to make sure no damage is done to the wire bonds that will impede the operation of the sensor.

For this reason, the pCT group decided to opt for a different type of bonding

Figure 2.8: The ALPIDE bonding pads [29]. Significantly smaller A-type bonds on the south side of the chip.

technique. Single point tape automated bonding (SpTAB) is an alternative technique with several advantages compared to both wire and laser bonding [40]. The technique uses ultrasonic point welding, which involves an ultrasonically applied pressure and heat that connects a thin conductive material to the pad of the device. This type of bond is shown in Figure 2.9 and is considered to ensure a highly reliable and mechanically stable connection. Compared to wire-bonding, SpTAB also requires fewer interconnects to ensure reliability. Another reason for selecting SpTAB is to avoid the use of heavy metals since aluminum can be used as the conductive material. It is beneficial for the homogeneity of the detector that the metal used in the front-end is consistent with the absorber layer material.

Figure 2.9: Laser microscope image of SpTAB bonds from a related project [41].

# 2.5.1 Chip Cable and String Flex

The chip cable and the string flex are both thin FPCs made of adhesive-less aluminum and polyimide [40]. Polyimide is a polymer that acts as a dielectric and a carrier for the conductive aluminum traces. The technology is specially developed for detector modules in HEP experiments by LTU Ltd. in Kharkiv, Ukraine. The manufacture process of the chip cable is based on precision

photolithography and chemical wet etching. This approach has been utilized and tested and verified with the ALICE ITS silicon strip detectors [42]. The pCT front-end components must, however, be designed for significantly faster data readout and lower supply voltage compared to the ITS [41].

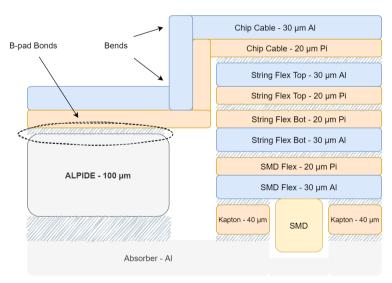

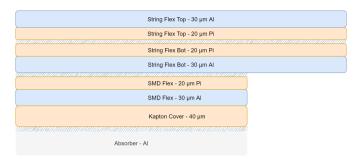

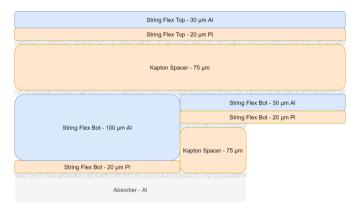

The chip cable serves as an interconnect between the ALPIDEs and the string flex. See Figure 3.9 for the transverse cross-section of the interconnection between the ALPIDE and the chip cable. A hole is etched in the polyimide dielectric and ultrasonic welding pushes the aluminum trace of the chip cable down onto the ALPIDE pad.

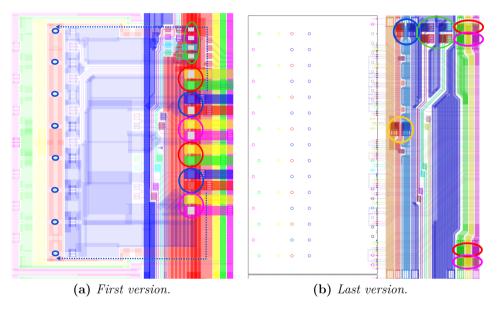

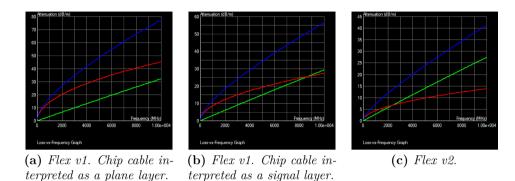

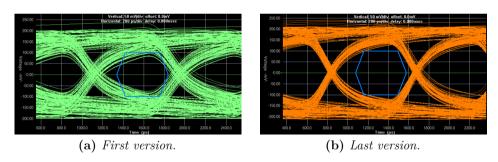

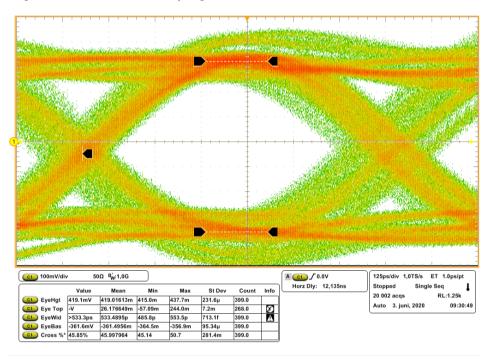

The string flex is an FPC based on the same principles as the chip cable. However, contrary to the chip cable, the string flex consists of two conductive layers. This is to deliver power to the sensors and to provide a proper ground plane for the high-speed links. The traces of the flex run perpendicular to the chip cable traces, and end a couple of centimeters outside of the detector area. A stiffener is added to the end of the FPC enabling connection in a Zero Insertion Force (ZIF)-connector. The height of the string flex is constrained. The height of the six-string flex in a half-layer cannot exceed the height of the detector. Several iterations of the chip cable and string flex FPCs have been produced and tested (see Section 3.2).

One could question the reasoning behind having two distinct parts in the front-end glue electronics: the chip cable and the string flex. It inevitably increases the material budget and complexity of the front-end. However, the choice is considered to improve the yield of the production as each production step can be tested. E.g., the bonding of a chip is deemed to be a critical process where many problems can occur. Thus, it is critical to test each chip after bonding. The bonding to the chip cable makes it possible to test the bonding of each chip before bonding to the string. If problems occur during the bonding to the string, this can be fixed without interfering with the chip bonds. The chip cable is designed to fit into a specific test-frame as discussed later in Section 3.2.1. A special tool was developed for testing the chips and the bonding, the Production Test Box (PTB) (see Section 7.5.1). This is also used to test the string as each of the chips are bonded, simplifying the debug process during production

28 2.6. Transition Card

and again increasing the yield. The string flex, with the chip cables and the ALPIDEs connected, are glued to the absorber metal sheet.

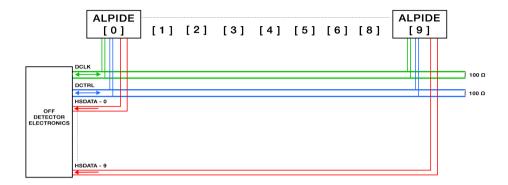

Figure 2.10: Simplified schematic diagram of the interconnections between the string and the off-detector electronics [39]. The diagram also indicates that ID 7 is not used.

A simplified schematic diagram of the signal interconnections between the string and the off-detector electronics is shown in Figure 2.10. All nine sensors share the clock and control signals, while each sensor embodies an exclusive high-speed data link. Note the  $100\,\Omega$  resistors used for the clock and control signals. These resistors are placed on the far-end of the string to terminate the transmission lines. The termination of the high-speed links is done on the readout electronics.

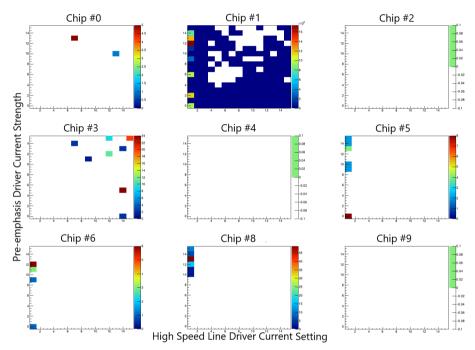

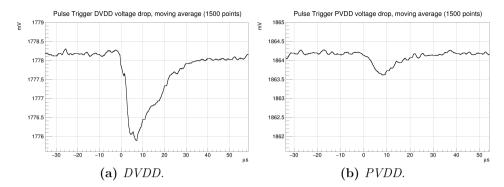

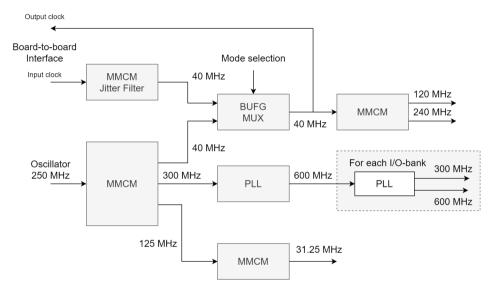

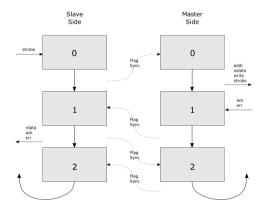

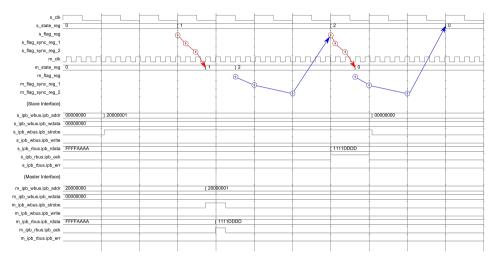

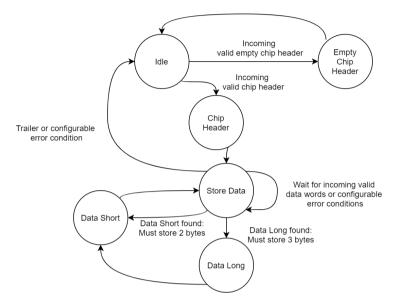

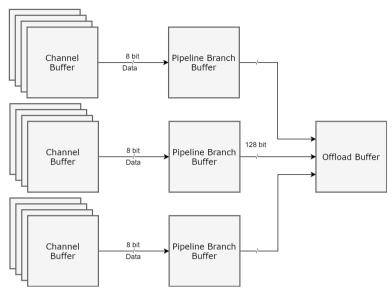

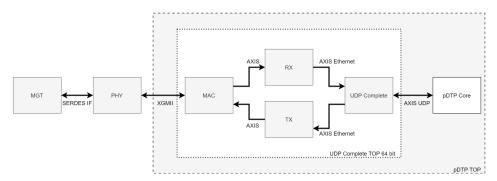

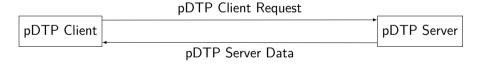

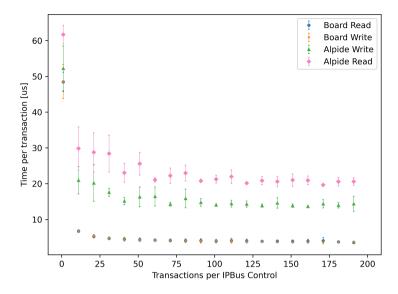

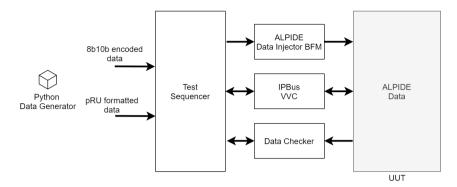

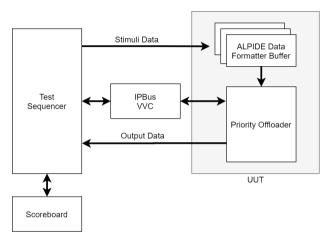

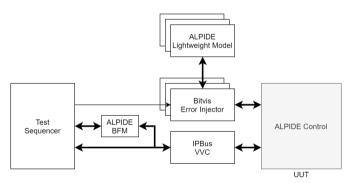

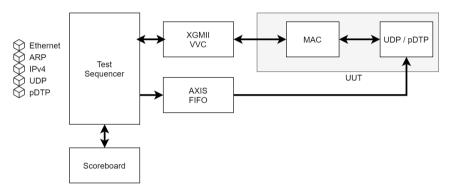

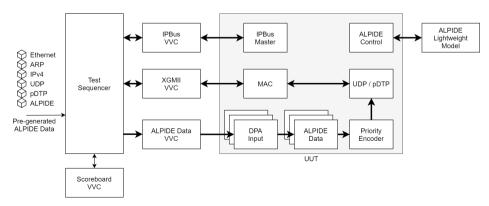

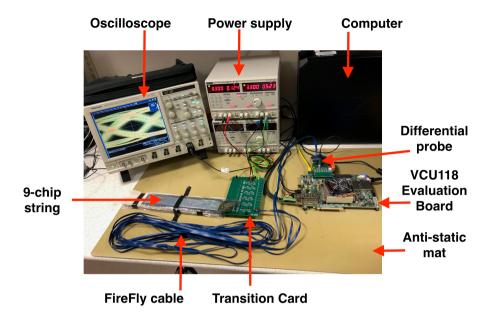

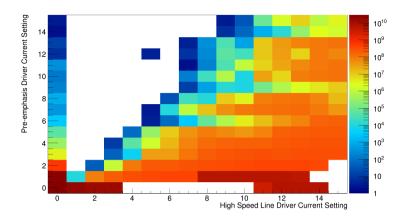

# 2.6 Transition Card