# Evaluation and design of readout electronics for electron and proton detectors

A thesis by Aleksander Kårstad Nes for the degree of Master of Science in Physics

Department of Physics and Technology

University of Bergen

June 2017

#### Abstract

Researchers at Birkeland center of space science have initiated a project where the precipitating flux of energetic electrons and protons into the middle atmosphere will be measured. An instrument will be attached to a low earth orbit (LEO), polar satellite. At the start of this thesis, only the radiation detectors were specified. It was also determined that the detector readings would be oversampled by an analog to digital converter (ADC), and processed on a field programmable gate array (FPGA). Finding an ADC that can be used in this project, and creating interfaces and an evaluation system to it are the main goals of this thesis.

A block diagram overview is made for the entire measurement system. The discussion around this proved helpful to define tasks needed in this project, and it will continue to be helpful for future work. A potential candidate for an ADC is identified after an extensive search. Potential reliability concerns are discussed, as well as the analog signal processing that might be necessary with the ADC in question. FPGAs that are potential candidates for this project are considered. Digital design methods for ADC data acquisition and ADC control are discussed in relations to the project and the FPGA alternatives. All methods are at various levels realized and tested.

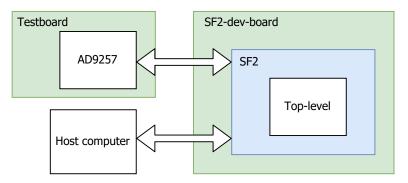

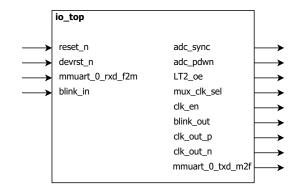

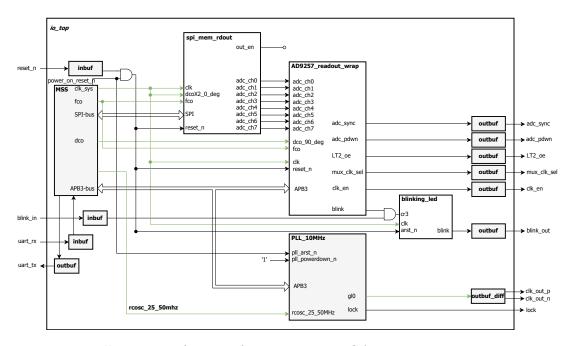

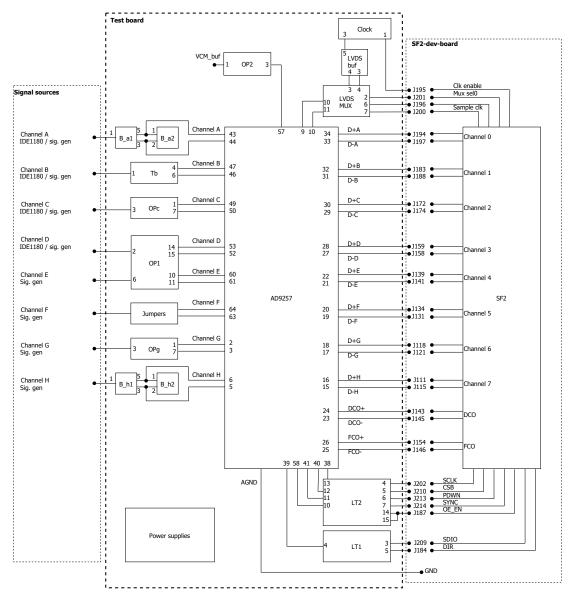

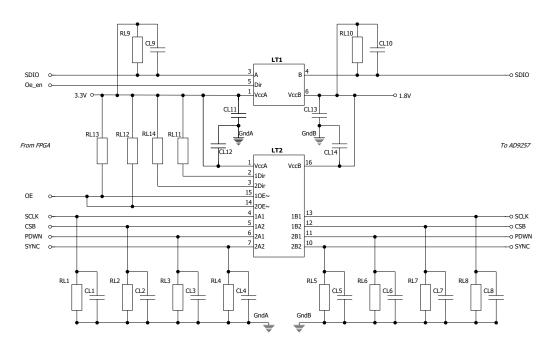

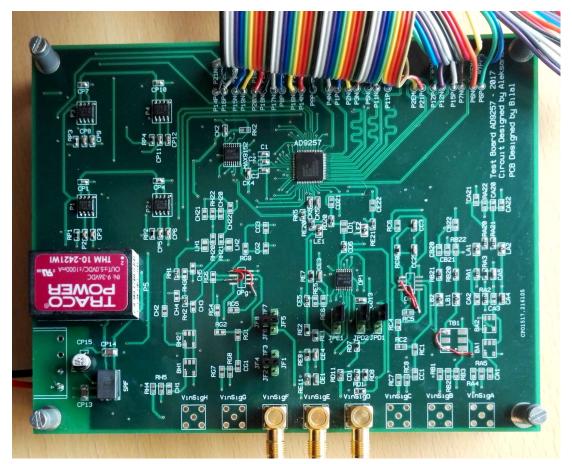

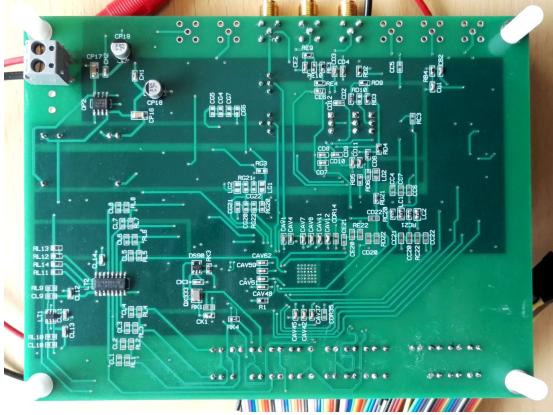

A synthesizable VHDL model of the ADC is made to test the digital designs close to the real-life application. To test against the actual ADC, a testboard is made. This testboard also contains electronics for differential conversion, electronics that enable having multiple sample-clock sources, as well as voltage level mitigation circuitry. A VHDL testbench is made to verify the digital designs in the development phase. A system on chip (SoC) is made to interface with the ADC testboard. The functionality of the SoC includes setting various output data from the ADC and checking readout data automatically, accessing ADC configuration memory, testboard-component control, ADC sample-clock generation, "real-time" monitoring of readout data, and error tracking and error alerts for long term testing.

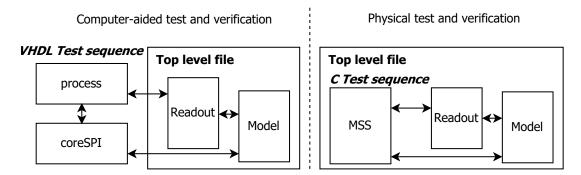

The SoC is tested and verified in all design stages before implementation. A system is made where the SoC is internally connected to the ADC model. This is tested and verified in a computer-aided testbench in the pre-synthesis-, post-synthesis-, and post-layout- stage. After implementation, the SoC is tested in a physical, software-based testbench. A similar system is made where the signals between the digital designs and the model are looped back through I/Os on the FPGA. This is also tested in computeraided- and physical- testbenches. The testboard SoC is also tested and verified in a computer-aided testbench. The testboard is realized at a late stage in this thesis. It was not enough time to properly test the testboard SoC and testboard together. Some issues are found, but it is possible that the first version of the testboard is fully functional. If so, further testing can commence. ii

# Acknowledgments

First and foremost, I would like to give special thanks to my supervisors **Johan Alme** and **Kjetil Ullaland** for giving me support and perspective, as well as always being available when help was needed.

I would also like to thank **Hilde Tyssøy** and **Johan Stadsnes** for the help they gave me regarding the project background.

I would like to thank **Bilal Hasan Qureshi** for designing the PCB for my circuit designs, and for performing measurements on it post-assembly. I must also thank **Shiming Yang** for supervising the entire testboard process, and **Per Heradstveit** for assembling the components on the testboard.

My fellow students deserve thanks for a great environment at our office these two years at UiB.

Last but not least, I would like to thank my friends, and especially my family, for supporting me throughout my studies, and in general.

# Contents

| 1        | Intr | oducti  | on                                                                         | 1  |

|----------|------|---------|----------------------------------------------------------------------------|----|

|          | 1.1  | DEEP    | background and motivation                                                  | 1  |

|          | 1.2  | About   | this work                                                                  | 3  |

|          | 1.3  | Thesis  | outline                                                                    | 3  |

|          | 1.4  | Citatio | ons                                                                        | 4  |

| <b>2</b> | Bac  | kgrour  | nd and related work                                                        | 5  |

|          | 2.1  | Radiat  | tion                                                                       | 5  |

|          | 2.2  | Electro | onics in space                                                             | 5  |

|          | 2.3  | Measu   | rement system                                                              | 6  |

|          |      | 2.3.1   | Radiation measurement                                                      | 7  |

|          |      | 2.3.2   | Charge sensitive amplifier and pulse shaping $\ldots \ldots \ldots \ldots$ | 10 |

|          |      | 2.3.3   | Analog to digital conversion                                               | 11 |

|          |      | 2.3.4   | FPGA                                                                       | 12 |

|          |      | 2.3.5   | Data storage                                                               | 12 |

|          |      | 2.3.6   | FPGA-implemented system                                                    | 12 |

|          |      | 2.3.7   | Other functionality                                                        | 16 |

|          | G    |         |                                                                            |    |

| 3        | Con  | nponer  | nt selection and considerations                                            | 17 |

|          | 3.1  | Genera  | al consideration                                                           | 17 |

|          | 3.2  | FPGA    |                                                                            | 17 |

|          | 3.3  | ADC     |                                                                            | 18 |

|          |      | 3.3.1   | AD9257-EP                                                                  | 19 |

|          | 3.4  | Analog  | g front-end of AD9257                                                      | 22 |

| 4 | Dig  | ital de | sign                                                                                                       | <b>24</b> |

|---|------|---------|------------------------------------------------------------------------------------------------------------|-----------|

|   | 4.1  | AD925   | 57 readout logic                                                                                           | 24        |

|   |      | 4.1.1   | Readout source considerations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                    | 24        |

|   |      | 4.1.2   | Specifications                                                                                             | 25        |

|   |      | 4.1.3   | Serializer/deserializer interface                                                                          | 25        |

|   |      | 4.1.4   | Custom logic                                                                                               | 26        |

|   |      | 4.1.5   | Preliminary conclusion                                                                                     | 31        |

|   |      | 4.1.6   | Realized readout design $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$     | 32        |

|   | 4.2  | AD925   | 57 control logic $\ldots$ | 33        |

|   |      | 4.2.1   | SPI slave considerations                                                                                   | 33        |

|   |      | 4.2.2   | SPI master specifications                                                                                  | 34        |

|   |      | 4.2.3   | Custom SPI master in fabric                                                                                | 34        |

|   |      | 4.2.4   | CoreSPI                                                                                                    | 37        |

|   |      | 4.2.5   | MSS SPI peripheral                                                                                         | 38        |

|   |      | 4.2.6   | Preliminary conclusion                                                                                     | 39        |

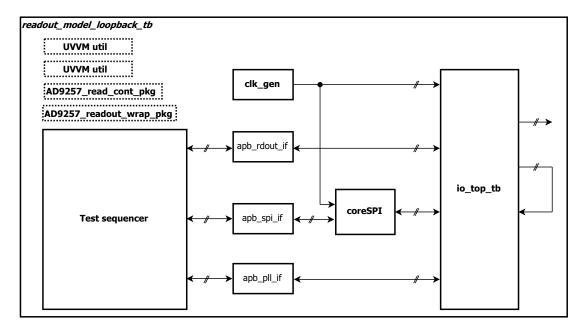

|   |      | 4.2.7   | Realized SPI master                                                                                        | 39        |

| 5 | Test | t and v | verification systems                                                                                       | 40        |

|   | 5.1  |         | uction                                                                                                     | 40        |

|   | 5.2  |         | opment testbench                                                                                           | 42        |

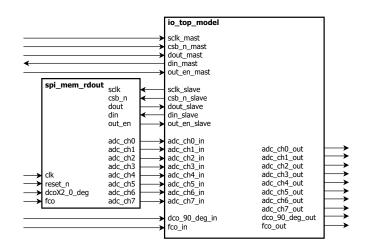

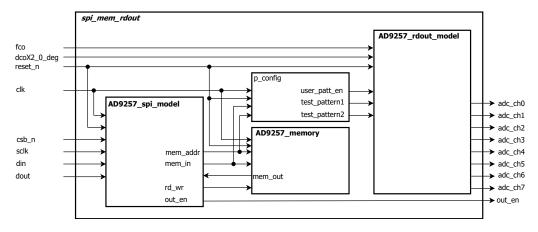

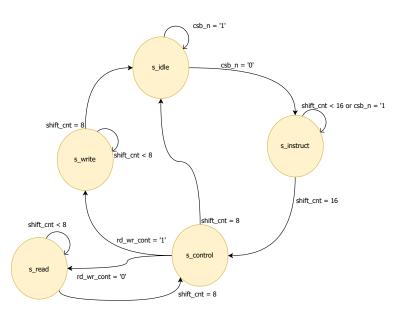

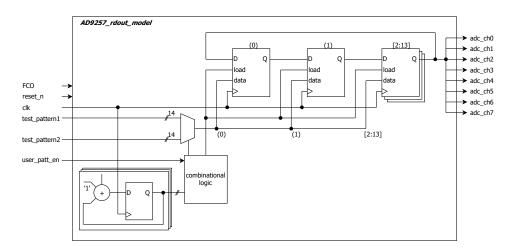

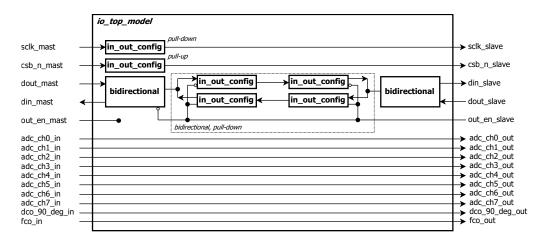

|   |      | 5.2.1   | HDL model of AD9257                                                                                        | 43        |

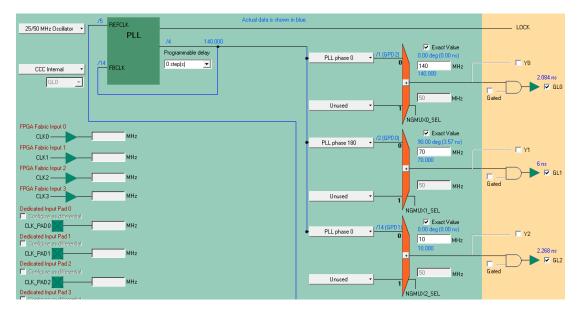

|   |      | 5.2.2   | Clock generation                                                                                           | 49        |

|   |      | 5.2.3   | Readout wrapper                                                                                            | 49        |

|   |      | 5.2.4   | Dynamic PLL                                                                                                | 50        |

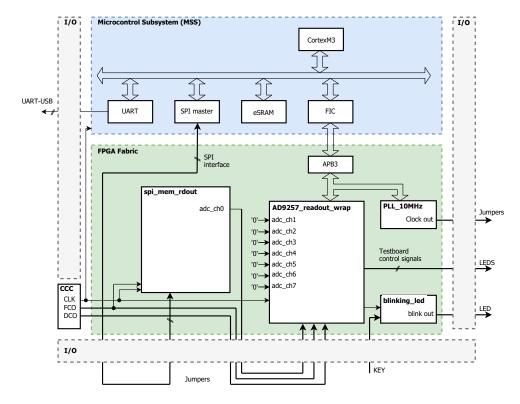

|   | 5.3  | FPGA    | -internal SoC                                                                                              | 51        |

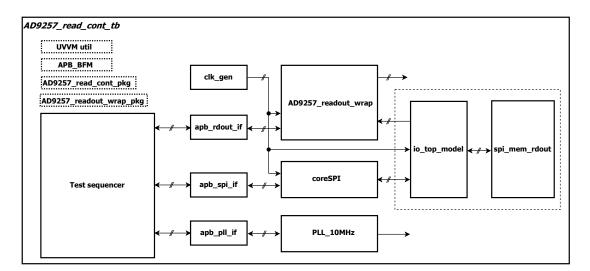

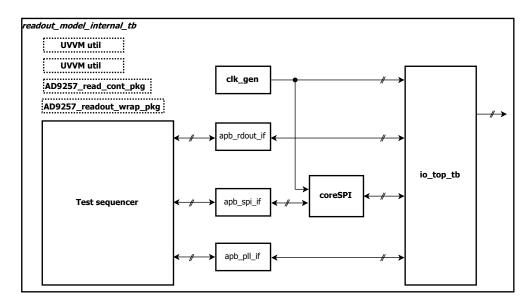

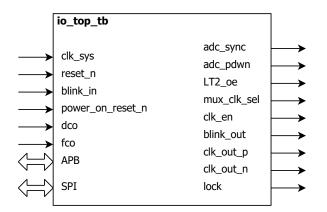

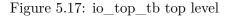

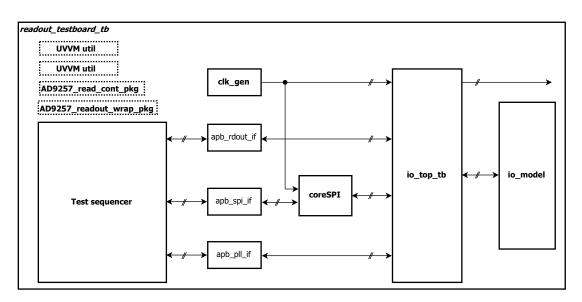

|   |      | 5.3.1   | Computer-aided-verification system                                                                         | 53        |

|   |      | 5.3.2   | FPGA-internal SoC structure and design process                                                             | 54        |

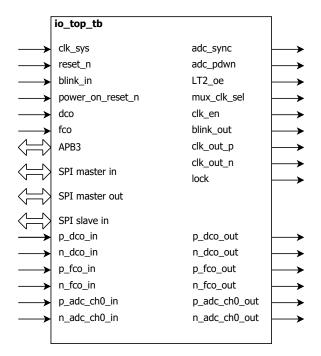

|   | 5.4  | FPGA    | -loopback SoC                                                                                              | 57        |

|   |      | 5.4.1   | Computer-aided verification                                                                                | 57        |

|   |      | 5.4.2   | Implemented FPGA-loopback SoC                                                                              | 60        |

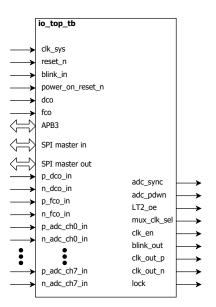

|   | 5.5  | AD925   | 57-testboard SoC                                                                                           | 60        |

|   |      | 5.5.1   | Computer-aided verification                                                                                | 61        |

|   |      | 5.5.2   | Implemented AD9257-testboard SoC                                                                           | 61        |

|   | 5.6  | AD925   | 57 testboard $\ldots$                                                                                      | 62        |

|   |      | 5.6.1   | Practical considerations                                                                                   | 62        |

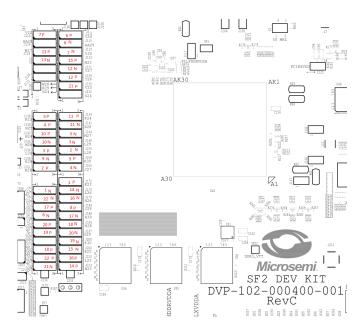

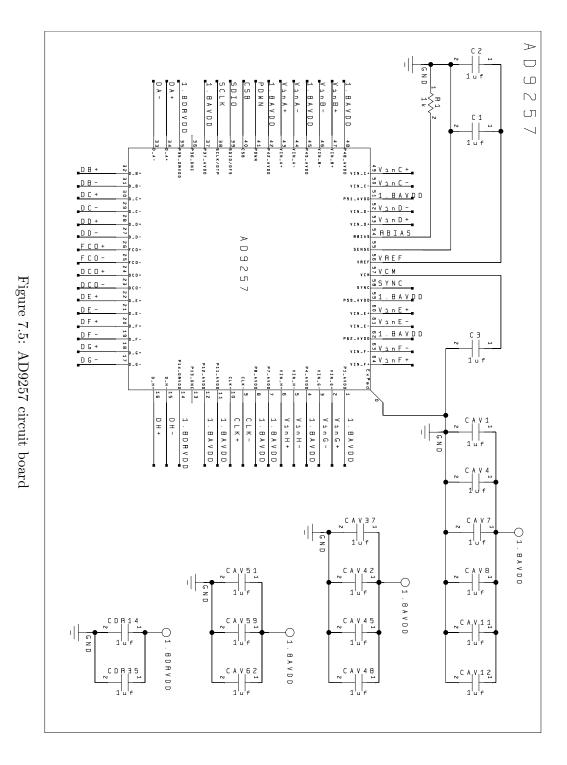

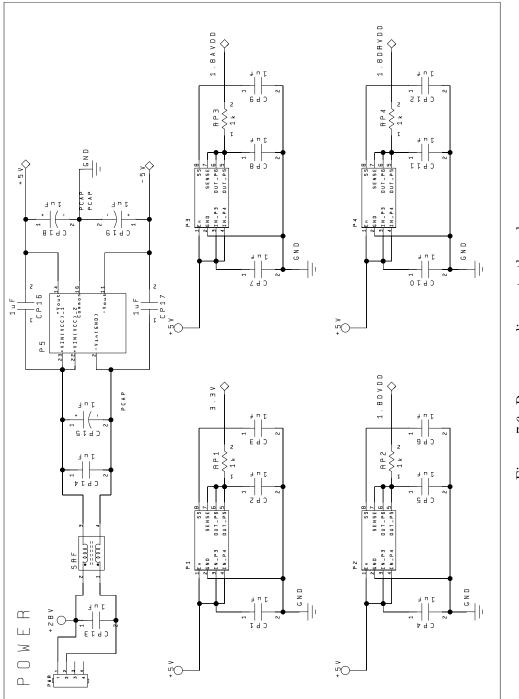

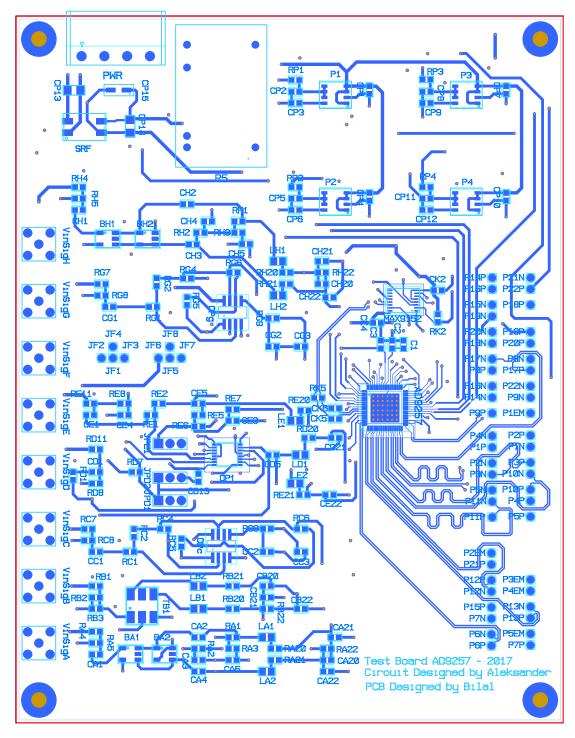

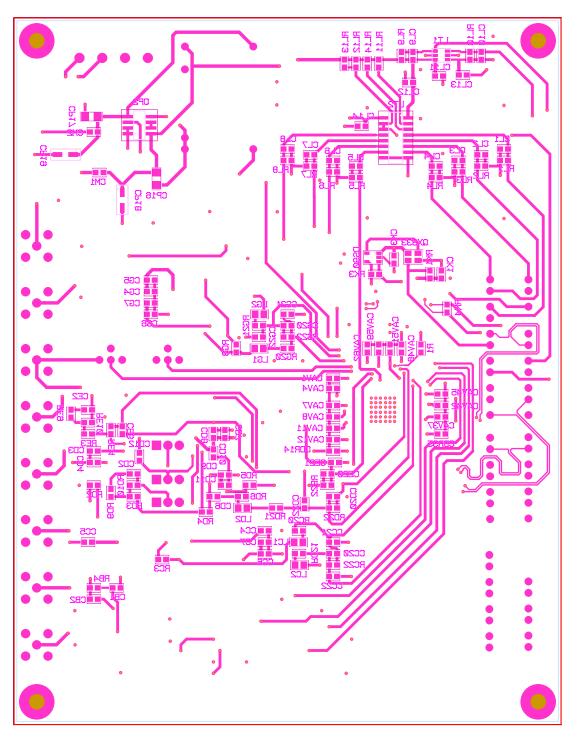

|   |       | 5.6.2                 | Design of the AD9257 testboard   | . 64 |

|---|-------|-----------------------|----------------------------------|------|

|   |       | 5.6.3                 | PCB layout                       | . 71 |

|   |       | 5.6.4                 | 1st board configuration          | . 71 |

|   | 5.7   | Embe                  | dded software                    | . 73 |

| 6 | Tes   | ts and                | results                          | 78   |

|   | 6.1   | Tests                 |                                  | . 78 |

|   |       | 6.1.1                 | Computer-aided test sequence     | . 78 |

|   |       | 6.1.2                 | Physical test sequence           | . 81 |

|   | 6.2   | Result                | .s                               | . 82 |

|   |       | 6.2.1                 | Custom SPI-master                | . 82 |

|   |       | 6.2.2                 | Readout methods                  | . 82 |

|   |       | 6.2.3                 | Development testbench            | . 82 |

|   |       | 6.2.4                 | FPGA-internal SoC                | . 84 |

|   |       | 6.2.5                 | FPGA-loopback SoC                | . 84 |

|   |       | 6.2.6                 | AD9257 testboard SoC & testboard | . 85 |

| 7 | Dis   | cussior               | h & conclusion                   | 88   |

|   | 7.1   | Future                | e work                           | . 90 |

| A | Me    | $\operatorname{thod}$ |                                  | 91   |

| B | Too   | ols                   |                                  | 99   |

| C | Pro   | ject se               | etup                             | 102  |

| D | : AD  | 9257 t                | estboard extras                  | 110  |

| A | crony | $\mathbf{yms}$        |                                  | 123  |

# CHAPTER 1

# Introduction

This chapter gives an introduction to the background of the distribution of energetic electrons and protons (DEEP) project. The goals of this thesis are also defined, and an overview of the thesis structure is given.

# 1.1 DEEP background and motivation

The content in this section is mostly based on relevant work performed by Linn-Kristine Glesnes Ødegaard [1], and on the conceptual design report of the project [2].

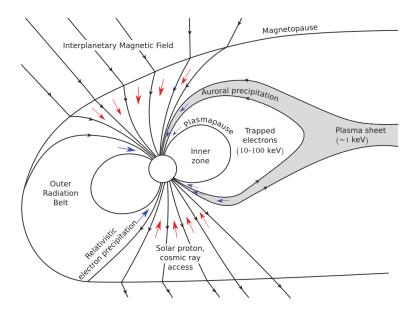

In the simplest way, the earth can be seen as a dipole magnet. A magnetic field resides from the south hemisphere (magnetic north) to the north hemisphere (magnetic south). It protects the earth from charged particles coming from the sun, also known as the solar wind. This is mostly composed of electrons and protons. The magnetic field deflects most of these particles and effectively shields the earth and its atmosphere from the direct impact of this radiation [3]. Figure 1.1 shows an illustration of the magnetic environment around the earth. This is generally called the magnetosphere [3].

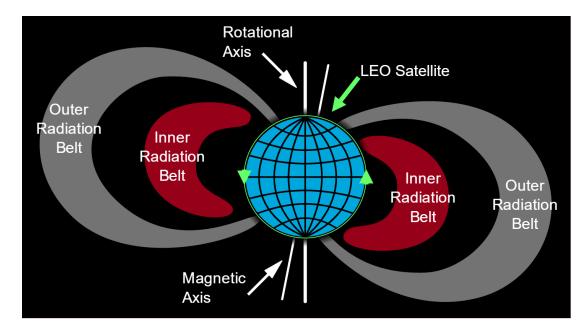

Some of the radiation gets trapped in belts that surround the earth and its atmosphere. These are called Van Allen belts, named after their discoverer. Figure 1.2 shows an illustration of the belts. It is generally believed that the solar wind is the source of the particles in these belts [3]. The inner belt mostly contains protons, while the outer belt mainly contains electrons. The energy range in the outer belt is depicted in figure 1.1.

The belts are caused by interactions between charged particles and the magnetic field. One process causes particles to move between the magnetic poles in a bouncing motion. This depends on the angle between the particle velocity vector and the magnetic field. This angle is defined as the pitch angle. The pitch angle grows larger when the particle approaches one of the poles. If it becomes 90° at some point, it mirrors. Hence the bouncing motion. However, if this does not happen before the particle has entered the atmosphere, it can lose its energy to atmospheric atoms. This is called particle precipitation.

Some of the precipitating particles have energies that allow them to travel into the middle atmosphere before their energy is lost. This transfer of energy can affect the

Figure 1.1: Illustration of the magnetosphere [4]

Figure 1.2: Illustration of Van-Allen radiation belts. [5]. Satellite trajectory of an LEO satellite has been added.

atmosphere in different ways. One effect is the creation of certain gasses that destroy ozone gas. Ozone gas has the well known function, amongst others, of absorbing harmful ultraviolet radiation from the sun. To accurately quantify the effects, the number of particles, their energy, and where in the atmosphere they precipitate should be measured globally and continuously. Results from the satellites NOAA POES with the particle detector MEPED provide the closest match to these criteria. However, the measurements have insufficient pitch angle coverage, proton contamination effects of measured electron data, and vice versa. This complicates reliable use of the obtained data.

By using newly designed detectors, it is possible to obtain the data that is needed to correct the pitch-angle uncertainties. Birkeland centre of space science has initiated the creation of an instrument that measure, process and transfer the measurement data to earth. The instrument will be attached to an LEO satellite in a polar orbit, as illustrated in figure 1.2. The launch is expected to be in 2019. Starting the development of this instrument is the focus in this thesis.

## 1.2 About this work

At the time of writing, the detectors are the only specified parts in the system. The functionality of the system is decided, but specifications on how to achieve it are not entirely specified. In this thesis, a general overview of the necessary parts in the measurement system is made. The primary objectives are however to find a way to convert the detector readings into a digital format, create and implement interfaces for the digitized data, and test against the device. Testing it imply that a test system must be made as well.

## **1.3** Thesis outline

**Chapter 2** provides a basic understanding of the challenges microelectronics face in space, as well as for radiation mitigation techniques. It also provides a basic overview of the functionality that needs to be implemented in the measurement system.

**Chapter 3** contains information about components that were found to be possible alternatives in the measurement system. This concerns an ADC with necessary analog circuitry and an FPGA which is used as the platform for digital functionality.

**Chapter 4** discusses methods of interfacing from the FPGA to the ADC. Different alternatives are discussed, and considerations are made towards the measurement system.

**Chapter 5** describes the test and verification systems that were made in order to evaluate the digital designs that were made, as well as the actual ADC.

Chapter 6 presents an overview of the testing that was performed and the test results.

**Chapter 7** contains a discussion and conclusion about the work that is done in this thesis, and a discussion about future work of the project.

**Appendices** contain information about methodologies used in this thesis, tools that were used, details about components that were considered, and how to set up the FPGA systems that were made.

## 1.4 Citations

It was chosen to deviate from standard citation-placement rules in certain cases. The following rules apply, in falling order: If the citation is before the punctuation, it applies to statements in the sentence. If it is after the punctuation, it applies to all statements made before the citation. If citations are made at the top of a section, it applies to all the statements in the section.

# Background and related work

This chapter goes through some aspects of the environment for a LEO satellite, and challenges of electronics in space. It also introduces a basic overview of the different parts of the instrument that will measure the radiation, and process the information.

# 2.1 Radiation

In this project, radiation is a source of information, as well as a source of concern. Thus, a brief explanation should be made. Radiation is a term used to describe mass and energy transportation through space. Examples of such radiation are electrons, protons, heavy ions, neutrons, and gamma. These different types of radiation have different properties. Radiation may interact with matter, i.e. a medium composed of an atomic nucleus and extranuclear electrons. The interaction process depends on properties of the radiation, as well as properties of the medium. The common factor is that if an interaction occurs, energy is transferred to the medium. This absorption of energy may influence the medium. As will be discussed in 2.3.1, this transfer of energy can be utilized so that the energy of the radiation can be measured. As will be discussed in section 2.2, this energy transfer can cause problems in microelectronic devices. [6, 7]

## 2.2 Electronics in space

As mentioned in section 1.1, the instrument will be attached to a low earth, polar orbit satellite [2]. The trajectory will be at a height of about 600 km above the surface of the earth. Each orbit will take around 100 minutes. Most of the mass of the atmosphere is below 100 km, and thus, this is where space begins [1]. Due to the low density of mass and low pressure, regions above this altitude can be considered a vacuum. The environment is quite different compared to the environment experienced on the surface of the earth. Some of the challenges are: [8, 9]

• The experienced temperature will cycle between -20° C to+60° C [2].

- The heat generated in the electronic circuits can only be dissipated through radiation.

- The absence of an atmosphere provides no shielding against the high-energy radiation present in this region.

Charged-particle-radiation effects deserve some extra attention because of its effects on integrated circuits (IC). In a low earth orbit, the electronics will be exposed to electrons and protons in the inner radiation belt, and solar energetic protons and galactic cosmic rays in the polar regions [2]. Long term exposure to these sources will cause degradation of the electrical properties. At some point, the device will fail to function. It is important that the device can handle the expected radiation over the entire operation lifetime. Single event effects (SEE) is a term that covers multiple effects caused by a single particle strike. Examples of these are single-event latchup and single-event upset (SEU). Latchup can cause a short circuit in CMOS transistors, which will lead to device malfunction if not detected in time [10]. SEU causes data corruption as it changes the content stored in a memory element, such as a D-flip-flop (DFF) or an SRAM-cell. [11, 12]

Shielding around the electronic device can decrease the effects of charged-particle radiation, but it can not prevent them entirely. Microelectronic devices can be made more radiation tolerant by using different techniques. Radiation-hardening by design implies using specialized architectures on memory elements. By increasing the area, and applying feedback, an SEU error can be corrected [10]. Error detection-and-correcting codes is a method where control bits are added to memory data. By including logic circuitry, an eventual error can be detected, and in some cases corrected. Scrubbing is a method where content in a memory is read often and checked for errors. Tripple-majority voting (TMR) is a method where a logic path is implemented three times in different areas, where their outputs are connected to a majority voter. Thus, if an SEU happens in one path, it will be neglected as the data in the other two paths have the majority [10, 13]. The problem of latchup can be removed by using silicone-on-insulator (SOI)-transistors, which are immune from latchup [10]. By employing these mitigation techniques, reliable operation of microelectronics in space can be achieved.

# 2.3 Measurement system

This section presents a high-level overview of the functionality that should be included in the system. Some parts of the system are discussed in more depth than others. The idea behind this is to provide support for the decisions that are made in this thesis, as well as a visual representation for the future work. The content is mostly based on the project design report [2].

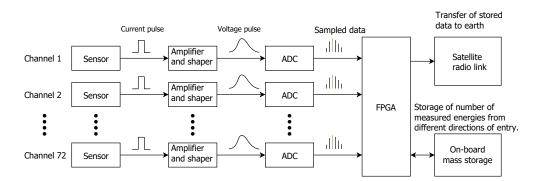

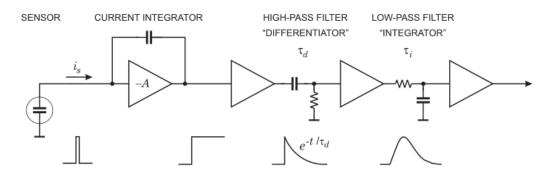

Figure 2.1 shows the block diagram of the main circuit-board-mounted components in the measurement system. Charged-particle detectors composed of multiple sensors are the sensing elements of the system. When a sensor is struck by a particle, an electrical signal that is proportional to the absorbed energy is generated. The signal magnitude and duration are often too small for further use. Therefore, the magnitude is amplified. This is followed by circuitry that changes the shape of the signal, and consequently, increases the duration of the pulse. [14]

Figure 2.1: Conceptual measurement system

The processed signal is sourced to an ADC. The pulse magnitudes are converted from a continuous signal to a set of digital codes. These codes are transferred into an FPGA, which contains functionality specific to this project. The main functionality of the implemented system is to determine particle energies, the number of particles with said energies, and from which direction the particle came from. This information is then stored in a digital storage unit. After each orbit, stored data is wirelessly transferred to a ground station on earth via a satellite radio link.

#### 2.3.1 Radiation measurement

In this project, the primary scientific objective is to measure electrons that precipitate into atmospheric heights between (50-100) km. The particle energy corresponding to this is (30-500) keV. This is the energy range of the electron sensors. Proton measurement is mandatory because protons will contaminate electron data. Thus, these data can be used to correct the electron measurement data. The range of energies that is monitored for protons is 30 keV-10 MeV. The extended range also allows measurements of other phenomena, but this is not discussed further.

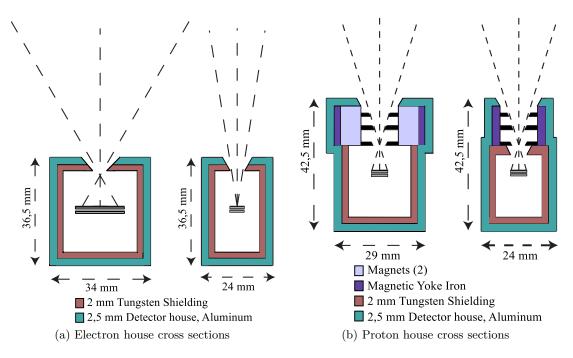

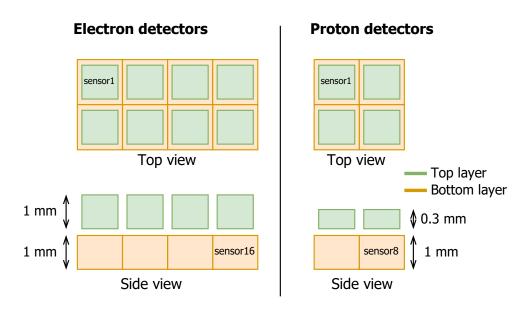

Figure 2.2 shows the detector houses. Electrons and protons will be measured by three houses each. The houses will point in different directions so that the combined field of views cover the angles of interest. A combination of aluminum and tungsten forms a house around the detectors to stop electrons of energies less than 6 MeV and protons of less than 45 MeV. The opening has a nickel foil shield to reduce light sensitivity, and to stop low energy protons. The proton housing is made from the same materials to prevent unwanted particles in the same energy range. Unlike the electron-detector housing, a magnetic field of 0.2 Tesla is applied at the entrance of the collimator. This prevent electrons of energies less that 1 MeV from reaching the sensors.

Figure 2.3 shows the structure of the detectors. An electron house consists of 16 sensors divided evenly in two layers, while a proton house has 8 sensors. Each sensor has its own readout electronics, which gives a total of 72 readout channels. The setup makes it possible to determine the direction of entry. As a first order explanation, a particle that enters through the hole will strike two vertically adjacent sensors. Thus, the total particle energy is the combination of both sensor outputs. If only one sensor in a pair provides an output, the particle did not enter through the hole. If this is the case, the measurement is not valid.

Figure 2.2: Illustration of detector houses with incoming radiation [2]

Figure 2.3: Illustration of detector configurations

Figure 2.4: Semiconductor detector [14]

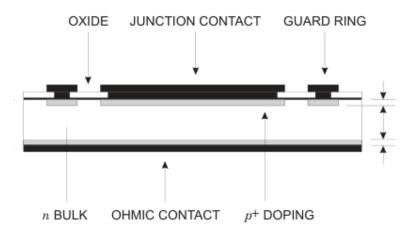

#### 2.3.1.1 Sensors

The detectors are made from a solid-state, semiconducting material. N-doped semiconductors have mobile, negatively charged electrons in the material. P-doped semiconductors have too few electrons in the crystal structure, which is commonly referred to as having mobile, positively charged holes in the material. When a p-type and an n-type semiconductor are connected, a pn-junction is formed. Electrons from the n-type material will diffuse into the p-type material, and vise versa. This causes a region between the two junctions where there are no mobile charge carriers. [6] Figure 2.4 shows a version of a semiconductor detector. A silicon wafer is made to have a lightly n-doped bulk. A heavily p-doped layer is made on the wafer top to create a pn-junction. A metallic contact is placed on top of this layer. [14]

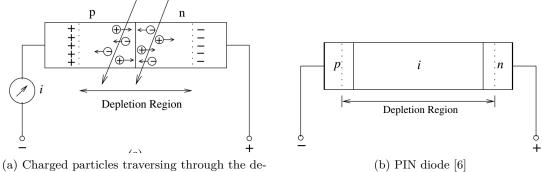

The depleted pn-junction in the diode, commonly called the depletion region, is quite narrow. By applying a reverse bias voltage, this region increases. This is the area that is sensitive to radiation. If a particle traverses through it, electron-hole pairs are created. The number of generated pairs are proportional to the incident particle energy. Because of the reverse-bias potential, the electrons are pulled toward the positive terminal, while the holes are pulled to the negative terminal. [14] Thus a current is flowing. The described process is illustrated for a pn-junction in figure 2.5a.

The depletion region should be as large as possible to have a large, radiation-sensitive area. In a pn-diode, this must be done by increasing the reverse-bias voltage. If the voltage is greater than a certain magnitude, the structure of the crystals will breakdown. Therefore, it can be difficult to get a sufficient depletion region in this type of detector. A way of mitigating this is to insert an undoped layer between the p-and n- type materials, called an intrinsic layer. Figure 2.5b illustrates this. This reduces the need for a large reverse-bias voltage. This is a common method, and this is the type of sensor that will be used in this project. [6]

As shown in figure 2.3 the thickness of the sensors in each layer is equal in the electron houses. A thickness of 1000 µm is specified for these sensors. The thickness of the sensors in the proton houses is different in each layer. The top layer is specified to be 300 µm, while the bottom layer is 1000 µm. Electrical contact is enabled through a 20 µgcm<sup>-2</sup> thick aluminum film. The pn-junction is going to be totally depleted,

pletion region of a pn-junction[6]

Figure 2.5: PN and PIN radiation detectors

meaning that the thickness of the depletion region extends to the negative terminal of the sensor [2, 14].

### 2.3.2 Charge sensitive amplifier and pulse shaping

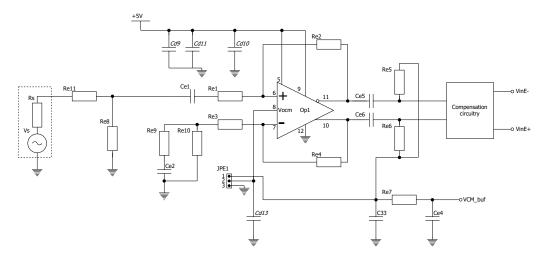

Figure 2.6 shows the amplifier and shaping circuitry, as well as the shape of the electrical signal in different stages.

Figure 2.6: Charge sensitive amplifier with pulse shaping [14]

The input stage is a charge sensitive amplifier (CSA). The current signal from the detector is injected into the feedback capacitor which acts as a charge integrator. The resulting output is a voltage step with a short rise time and long decay time. The voltage amplitude depends on the amount of charge that is injected into the feedback capacitor. Thus, it is proportional to the particle energy. [14]

If another particle strikes the detector before the voltage has returned to the baseline voltage, the amplitude of the output voltage from the CSA will represent a combination of multiple particle energies. This is called pile up. To avoid this, a high-pass filter is used to decrease the decay time to a suitable value. The resulting voltage signal is a narrow pulse. As the amplitude is of interest, an increase in the time where the amplitude is present is practical for further use as this reduces the sample rate requirements of the following ADC. The high-pass- and low-pass- filters change the rise time and decay time, and as a result of this the shape of the pulse. In the frequency domain, this translates to a reduction in the bandwidth of the signal. This improves the signal-to-noise (SNR) ratio as the thermal noise contribution is reduced. [14]

A maximum shaping time of 1 µs has been determined to be necessary to avoid pile up. It is wished to use an application specific integrated circuit (ASIC) where both CSA and pulse shaping is integrated. At the time of writing, this part has not been determined. Finding a suitable ASIC was not a part of this thesis, and will not be discussed any further.

#### 2.3.3 Analog to digital conversion

An ADC converts the time- and amplitude- continuous signal from the previous stage into a discrete set of values that represent the magnitude of the sampled analog signal. A general ADC operation begins by sampling the input signal at fixed time intervals. The value is held between each sample. It is then quantized, i.e. rounded to the nearest value of a finite set of discrete values. The value is then encoded, i.e. converted to a number format such as the binary number system. [15]

In order to get a proper representation of the sampled signal, the sampling frequency must be  $F_s \ge 2F_{max}$ , where  $F_{max}$  is the highest signal frequency component [15]. The resolution of the ADC is a combination of a reference voltage and the number of bits of the output code, or:

$$V_{res} = \frac{V_{ref}}{2^n}$$

where n is the number of bits. If the input signal  $V_{p-p}$  is larger than the reference voltage, the ADC will saturate. [16]

Fluctuations in temperature, supply voltage and atmospheric pressure amongst others, affect the transfer function of an ADC. These can however be compensated for. Intrinsic non-linearities will also create transfer-function deviations. Unlike environmental effects, these cannot be compensated for. In certain cases, this can result in missing output codes, which can be severe for low-resolution converters. [16, 15]

The non-linear transfer function causes harmonic frequency products, which consequently causes distortion. The noise that is present in the signal paths will decrease SNR. Signal-to-noise-and-distortion (SINAD) is a term that combines the effects of distortion and noise, as a measure of the total dynamic performance of the device. It is common to convert this to the effective-number-of-bits (ENOB). ENOB and the specified number of bits should be as close as possible. [16, 17]

Finding applicable ADCs was the starting point in this thesis. This is discussed further in section 3.3.

## 2.3.4 FPGA

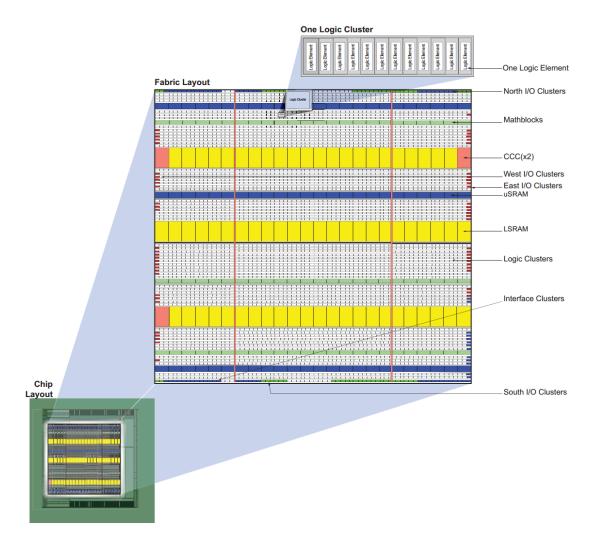

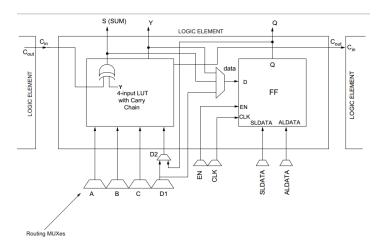

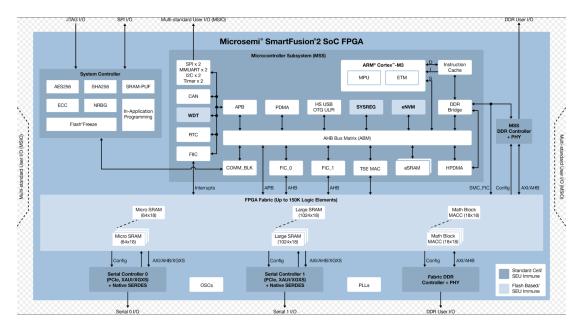

An FPGA is chosen as the platform where digital processing and system control will be implemented. FPGAs are ICs that can be configured to perform any logical function. Figure 2.7 shows the architecture of IGLOO2 (IG2), which is an FPGA from Microsemi. Naming convention differs between vendors, but the implementation is similar. The fabric, which is the programmable section, is composed of multiple logic clusters. The clusters can be connected together through an interconnecting array, which is also programmable. Each logical cluster contains multiple logical elements, as shown in figure 2.8. A lookup table (LUT) is the programmable element. It can be configured to act as any combinational element of up to 4 variables [10]. If more variables are needed, multiple LUTs can be connected. The logical elements also contain a sequential element. Both can be used separately or together. [18]

To configure an FPGA, the logic functionality must be described in a hardware description language (HDL). In this thesis, the language very high speed integrated circuit HDL (VHDL) is used. Syntactically, it has resemblances to software languages such as C. However, where software is sequential instructions of what a microprocessor will do, VHDL describes the implementation of digital hardware. Examples are combinational logic, sequential elements, and memory cells.

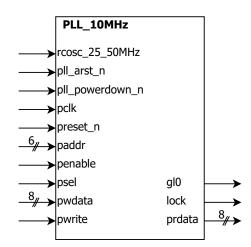

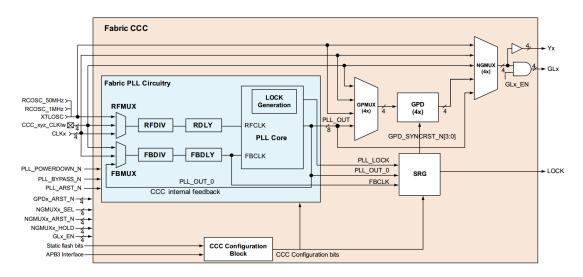

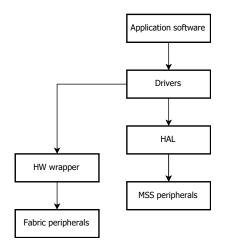

Special purpose sub-systems are often also included in the device as hard components. Typical examples are phase locked loops (PLL) for clock conditioning, storage memory, and mathblocks. A microprocessor, i.e. a CPU, can be implemented in the fabric. This is referred to as a soft implementation. However, certain devices contain a hard CPU to increase performance. Such a system-on-chip, or SoC, gives the possibility to implement functionality in both hardware, and software.

For the system that will be implemented, it will most likely be necessary to use the SEU mitigation techniques that were presented in section 2.2.

### 2.3.5 Data storage

Storage of data between each satellite orbit is necessary. In applications where the data amount is small, the internal FPGA memory could have been used. Most likely, this does not apply for this project. An external, higher capacity data-storage unit must be used to store the data of interest. The required memory capacity will depend on the number of incoming particles in the energy ranges and directions of interest. It is crucial that the memory is not corrupted by radiation. Therefore, the memory must be radiation hardened, or at least made radiation tolerant by employing the radiation-mitigation techniques mentioned in section 2.2.

## 2.3.6 FPGA-implemented system

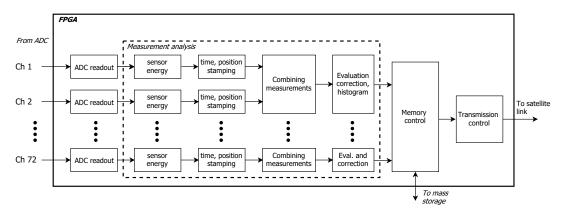

Figure 2.9 shows a conceptual block diagram of the application-specific system that needs to be implemented on the FPGA.

Figure 2.7: Smartfusion2/IGLOO2 fabric architecture [18]

Figure 2.8: Smartfusion2/IGLOO2 LUT [18]

Figure 2.9: FPGA internal system

#### 2.3.6.1 ADC readout

The first stage consists of logic that acquires the data from the ADC. The functionality of this block depends on the ADC output format. Data can be transferred serially or on a parallel bus. The transfer standard can be differential, such as low-voltage differential signaling (LVDS), or single-ended such as LVCMOS. The transfer protocol can be a common protocol such as serial peripheral interface (SPI), or it can be custom to the device. Independent on how it is transferred, data must be captured correctly for further processing.

#### 2.3.6.2 Measurement analysis

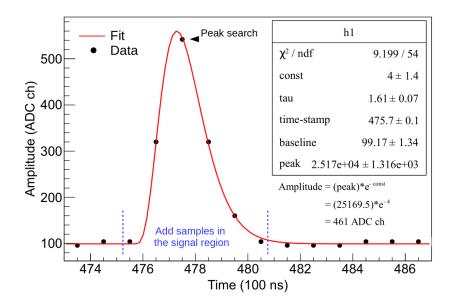

As discussed in 2.3.2, the voltage amplitude of the output from the amplifier-and-shaping circuitry is proportional to the particle energy. As illustrated in figure 2.10, there are several methods that can be applied to extract information about such a signal. Peak search is the process of searching for the peak value in the sampled data set. Curve fitting calculates the amplitude by using an equation that describes the signal shape [19]. The third method calculates the area of the pulse by integrating the sample-data set.

As the ADC samples data at a fixed interval, data that does not contain information about particle energies will be captured as well. Ideally, the voltage input to the ADC should be at a fixed level between particle hits. In reality, noise from circuit-board components and electromagnetic interference can cause the voltage to fluctuate. It is necessary to include circuitry that evaluates if the readout data is caused by noise, or if it is an actual measurement.

The previously mentioned voltage fluctuations will mix with the signal voltage. As this influences the amplitude of the signal, it corrupts the energy information. Thus, filtering of this noise must be done. Instead of using the methods mentioned to extract the needed information, an averaging filter can be used. This will not give an accurate representation of the energy, but it will filter away the noise. If all details about the transfer function and uncertainties are known, it should be possible to determine the actual energy. The advantages of this method are that the needed logic uses a small area, and it is not complex. This reduces the probability of SEU, and the chances of

Figure 2.10: Different methods of analyzing a semi-gaussian pulse: peak detection (arow), curve fitting (red line) and area calculation (integrating samples between blue lines) [19]

something going wrong due to inadequate testing, respectively. A proper study of the methods mentioned in this section were beyond the scope of this thesis.

As mentioned in section 2.3.1, the detectors are composed of two layers, where the energy of a particle is the sum of the outputs of two vertically adjacent sensors. Protons will contaminate electron measurements and are amongst other reasons also measured. Functionality that adds the sensor-pair-measurement data to get the total particle energy must be included. Before this can be done, it must be determined that both sensor pairs give an output. Adding a time stamp to the measurement data can be used to determine if the measurements are valid. If the two sensors provide data that is close in time, it is likely that they originated from the same particle hit. One method is to create logic that only evaluates the belonging pairs. If both sensors provide valid data that are close in time, the values are added. An evaluation of proton contamination must then be performed. If so, a correction must be made to get the actual electron energy. As the input angles of particles also are of interest, this information must be added. Each sensor pair in each detector cover certain angles. Therefore, the angle can be measured by adding a stamp that tells which sensors provided the data.

The determined particle energy with angle information can be used as inputs to circuitry that counts the occurrence of different energies, for different input angles. Keeping track of all measured energies for each input angle require a huge amount memory. Therefore, using histograms with bins of certain energy ranges is a more likely solution. Some energies might be more interesting than others. Hence, the size of the bins should be programmable, so that it is possible to alter the bin sizes. Another parameter can be how long data is collected before a histogram is stored, as some phenomena depend on time. The data that will be stored after analysis is done, is thus a factor of input angle, energy ranges, and data-collection time. A tag that makes it possible to identify what the data represents must therefore be added.

#### 2.3.6.3 Memory control

A controller for the storage unit must be implemented. This controls where the analyzed data is stored, as well as read and write operations to the memory. Read and write operations depend on what type of memory is used, and the transfer protocol of the chosen memory. Multiple memories might be used, so multiple RW-controllers might be necessary. To ensure that all data is stored, the operations must be sufficiently fast. Including memory buffers might be necessary to store data temporarily before it is written to the memory. Error detecting and correcting circuitry as mentioned in section 2.2 must be implemented to correct any potential SEU.

### 2.3.7 Other functionality

Each satellite orbit takes approximately 100 minutes. After each orbit, the stored data will be sent to earth via radio transmission. This will be achieved by a satellite radio link, which is a module that handles the radio communication between the satellite and a ground station on earth. Once transmission is due, the module will receive a stream of data. Internally on the FPGA, logic that controls when data will be transferred must be added. This logic must also initiate the transfer of the data stream from the storage unit. Thus, a timer could control when data transfer must occur. This, however, would require that the orbit time is exact for each orbit. Further investigations on how this can be done in a reliable way were not done.

So far, only the measurement-related functionality has been mentioned. The measurement system will have a default setup, I.e. all components will have a default configuration that assures optimal functionality. This can change after the satellite is deployed. Therefore, it must be possible to reconfigure all the components in the system. This includes resetting digital devices, power cycling analog devices, and altering the content in devices with internal memories. Environmental effects such as temperature and supply-voltage fluctuations can change the transfer function characteristics of components. This must be measured so that it is possible to correct the deviations. Current must be measured in case latchup occurs, so that the charge in the component can be drained before it causes permanent damage. To have the possibility of doing all this, a control system must be implemented on the FPGA. It must monitor the entire measurement system , and perform the necessary operations once an event occurs.

# Component selection and considerations

In this chapter, general specifications are set for electronic components that are alternatives in the project. A discussion is made about what types of FPGA that might be used in the project. One of the goals in this thesis was to find an applicable ADC based on some predefined requirements. The ADC that was found to be the best alternative is presented. Some considerations about the reliability of the ADC is also discussed. The signal might have to be processed before the ADC input. This is also discussed.

# **3.1** General consideration

Certain manufacturers produce space qualified electronics. There are strict requirements concerning manufacturing and testing of such ICs. The resulting components are expensive, and often outdated compared to commercial products because the process is time consuming. While finding components in this thesis, performance, capability and cost of the parts had priority over reliability. Electronics made for commercial use were not considered as it is unlikely that they would work in a space environment. Space qualified electronics were not considered as they generally are to expensive. The alternative option is to acquire a component which is not space qualified and test it, i.e. upscreen it to the requirements set for space operation. The latter is the preferred method in this project. The initial general requirement that was set was that the device must be able to operate in the expected temperature range of  $-20^{\circ}$  C to  $+60^{\circ}$  C [2].

# 3.2 FPGA

Memory-based FPGAs are alternatives to fuse-based FPGAs and ASICs. An issue with memory-based FPGAs is the possibility of radiation-induced upsets in the configuration data. This can change the intended functionality, and power-cycling or re-configuration must be done. Configuration-memory technologies used in modern FPGAs are generally SRAM or FLASH. Standard 6-transistor SRAM cells are more susceptible to SEU than FLASH-transistors. The energy transfer that is necessary to flip a bit in the latter is large, so FLASH cells are often referred to as SEU immune. The mitigation techniques mentioned in section 2.2 can be employed to make SRAM more radiation tolerant. This can however increase the cost, reduce performance, etc. On this basis, flash-based FPGAs will be considered for this project. [20, 21, 13].

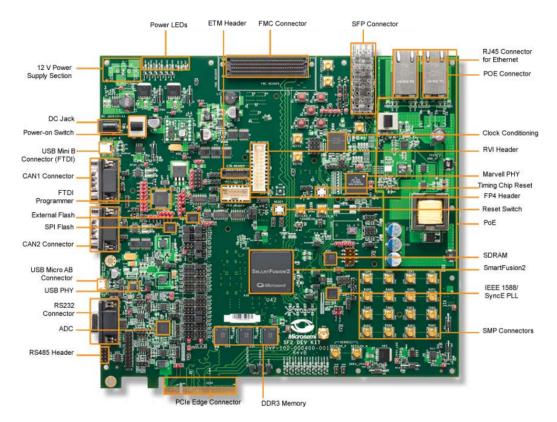

The main vendor of these types of FPGA is Microsemi. They deliver FPGAs for many applications, ranging from commercial to space applications. Differences lie in specialized features. Examples are integrated high-bandwidth transceivers, integrated microcontroller system, double-data-date (DDR) memory systems and number of inputs/outputs (I/O). Other factors are number of logic clusters, number of PLLs, power consumption, etc. Table 3.1 lists FPGA alternatives. Although all of the listed devices are options for this project, SmartFusion2 (SF2) and IG2 are mostly treated as the FPGAs of interest in the remaining sections. These and PolarFire can be delivered with military classification. PolarFire was however announced in the midst of this thesis, and was not evaluated beyond the contents in table 3.1. RTG4 is a radiation-hardened, space qualified FPGA.

|                      | RTG4   | SF2/IG2  | PolarFire |

|----------------------|--------|----------|-----------|

| Logic clusters       | 151824 | 146124   | 481000    |

| DSP                  | 462    | 240      | 1480      |

| PLL                  | 8      | 8        | 8         |

| High speed interface | 24     | 16       | 24        |

| Hard CPU             | No     | Yes/no   | No        |

| Class                | Space  | Military | Military  |

Table 3.1: Microsemi FPGA comparison

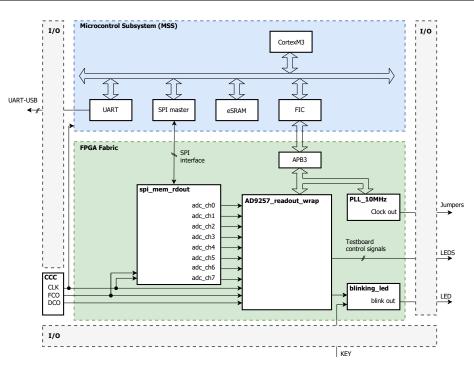

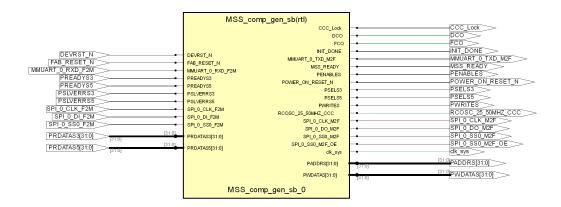

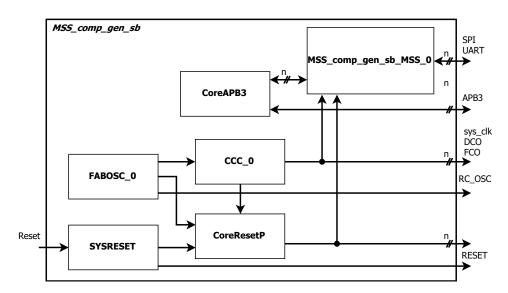

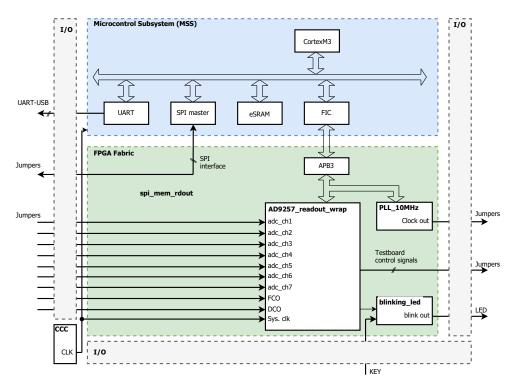

SF2 and IG2 have the same fabric, as shown in figure 2.7. The difference between the two is that SF2 has a hard microcontroller subsystem (MSS). Figure 3.1 shows an internal overview. It contains an ARM Cortex-M3 CPU which connects to hard peripherals through a bus matrix. The logic implemented in the fabric can be connected to the MSS trough fabric interface controllers (FIC). Thus, custom logic can be accessed and controlled by a software program.

## 3.3 ADC

Specifications listed in table 3.2 applies for the ADC. The sample rate requirements of the ADC is set so that the signal is oversampled by a factor of 5-10. This should be enough to detect the peak voltage of the signal with a tolerable uncertainty. A resolution of 10-12 bit is specified for the same reason. Multiple channels in one package reduce the printed circuit board (PCB) footprint. A serial output interface is desired as a parallel interface requires a vast amount of inputs on the FPGA. Based on the CSA-and-shaper ASICs that were previous alternatives, the ADC should expect a single-ended input. No power budget is specified for the ADC. The power consumption should however be as small as possible. Details regarding the process of finding an ADC, and the alternatives that were considered, is presented in "A.1: Finding an applicable ADC" in "Appendix A: Methods".

Figure 3.1: Smartfusion2 overview [22]

| Table $3.2$ : | ADC | specifications |

|---------------|-----|----------------|

|---------------|-----|----------------|

| Sample rate           | $5$ - $10~\mathrm{MSPS}$ |

|-----------------------|--------------------------|

| Bit resolution        | 10 - 12                  |

| Input phys interface  | Single-ended             |

| Output phys interface | Serial                   |

| Power usage           | Low                      |

| Nr. of channels       | 16                       |

| Rating                | Military                 |

|                       |                          |

## 3.3.1 AD9257-EP

Information is this section is obtained from the datasheets of AD9257-EP [23] and AD9257 [24].

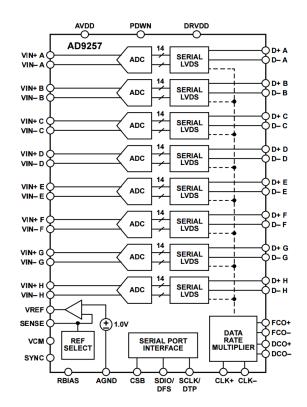

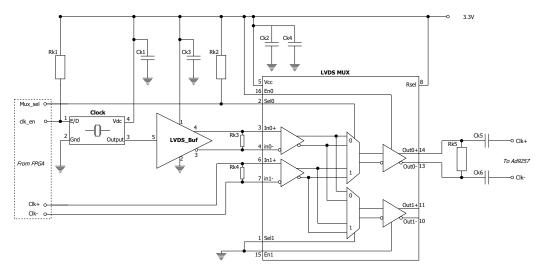

AD9257-EP, hereby referred to as AD9257, was determined to be the best alternative. This was based on its high number of channels per package, low power consumption, and serial output interface. It is evaluated in the military temperature range, but not classified as a military device. Figure 3.2 shows a block diagram of the converter.

AD9257 is a 14-bit ADC with a sample rate of 10-65 MSPS. It has eight individual channels which are composed of multiple pipelined stages. All stages but the last are low-resolution flash ADCs in combination with a DAC. The final stage is a flash ADC, delivering the final digitized data to the output stage. The output stage aligns and corrects errors in the data before it is passed to the output buffers. Here, data is serialized and aligned to a frame clock output (FCO), and a data clock output (DCO). [24, p.18] These clocks can be used by the readout system to capture and deserialize data. Sampled data is coded into a 14-bit word with a reference of +1V. Table 3.3

Figure 3.2: Block diagram of AD9257

Table 3.3: AD9257 output coding format[24]

| Input (V)       | Condition(V)           | Offset binary             | Twos complement   |

|-----------------|------------------------|---------------------------|-------------------|

| (VIN+) - (VIN-) | > (+VREF) - (0.5 LSB)  | 11 1111 1111 1111         | 01 1111 1111 1111 |

| (VIN+) - (VIN-) | = (+VREF) - (1.0  LSB) | 11 1111 1111 1111         | 01 1111 1111 1111 |

| (VIN+) - (VIN-) | = 0                    | $10 \ 0000 \ 0000 \ 0000$ | 00 0000 0000 0000 |

| (VIN+) - (VIN-) | = (-VREF)              | 00 0000 0000 0000         | 10 0000 0000 0000 |

| (VIN+) - (VIN-) | < (-VREF) - (0.5 LSB)  | 00 0000 0000 0000         | 10 0000 0000 0000 |

shows the available output coding formats. Twos complement is default.

The converter can be configured through a three-wire SPI-bus. One particularly helpful feature for testing and verifying the readout logic is the ability to set output data to built-in- or user-defined-patterns. The configuration memory is loaded with default values if the device is reset. The operating state can be toggled via SPI or via a dedicated input PDWN. If multiple devices are used in a system, as would be the case in this project, synchronous sampling can be achieved by asserting the dedicated input SYNC. More detailed considerations regarding the outputs and the control section are presented in chapter 4, where the digital designs are discussed.

## 3.3.1.1 Reliability considerations

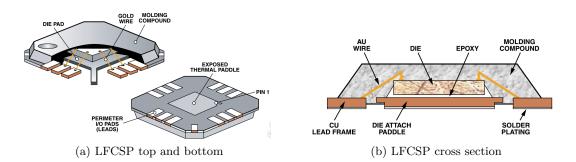

This device is an enhanced version of a commercial AD9257. It is rated in the military temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C. Leadframes are coated with SnPb or NiPdAu to prevent the growth of tin whiskers, which can happen with RoHS-compliant, i.e. lead-

Figure 3.3: LFSCP package overview [29]

free, devices. Wire-bonds are of a non-copper material. There are stricter requirements for manufacturing as one assembly site, one test site and one fabrication site are used for all enhanced products. Manufacturing is done via a single processing flow baseline. Qualification data can also be provided by request. [23, 25, 26]

The device has a plastic, LFCSP package which is displayed in figure 3.3. It has I/O pins beneath the package, i.e. it has no leads. Packages that have leads are more robust if the circuit board is exposed to mechanical shocks. This is because the leads offer some mechanical flexibility. [27] Vibrations will ripple through the circuit board during satellite launch [28], and thus directly to the package, and can therefore pose a reliability problem.

Hermetically sealed ceramic- or metal- packages are often used in high-reliability applications. The use of plastic packages poses many reliability concerns, such as outgassing, and thermal-cycling-induced degradation of the molding compounds. However, parts with plastic packages have been used in space before. Though not as reliable, they offer advantages in areas such as size, weight, and cost. There is an abundance of components that use these packages. Consequently, there are more available options. [28, 30] Screening this device to ensure reliable operation in the LEO environment must be done. An in-depth analysis of what to test, and how to upscreen this device to higher reliability requirements were beyond the scope of this thesis.

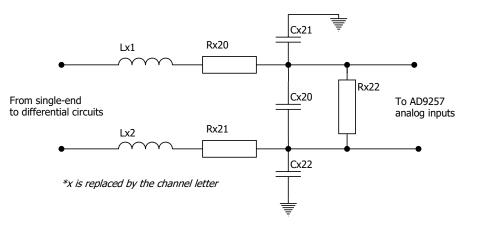

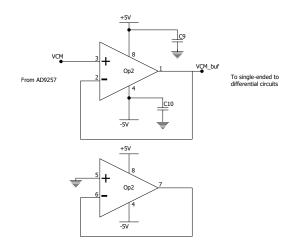

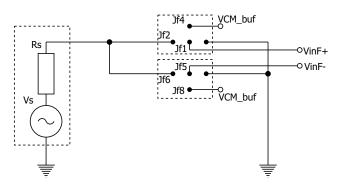

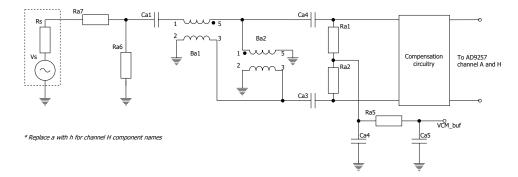

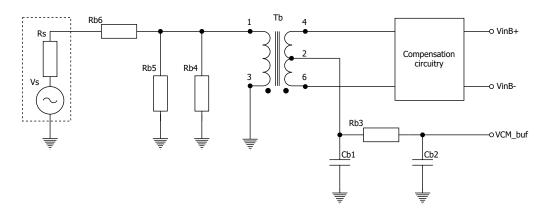

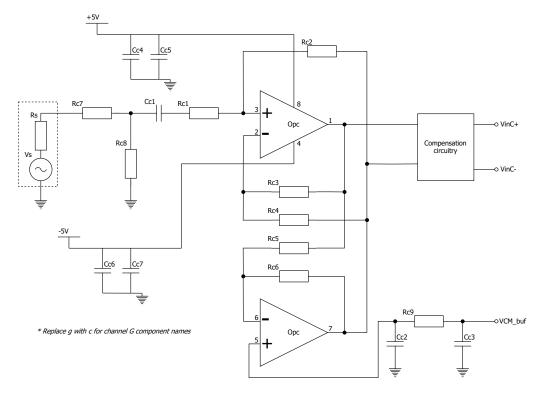

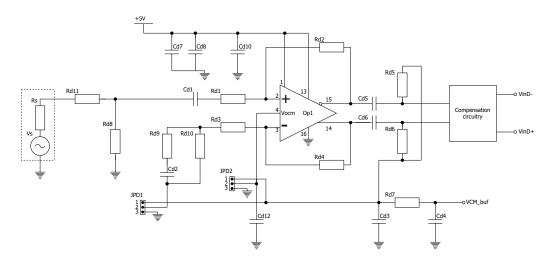

## 3.4 Analog front-end of AD9257

AD9257 has differential, switched capacitor inputs. The signals applied to the inputs should therefore also be differential. The input voltage on each pin on the differential input must not exceed 2 V, and a common-mode voltage of 0.9 V must be present. The differential signal voltage-span should not be greater than  $2V_{p-p}$  as this equals the full-scale output. As shown in table 3.3 this would result in a differential voltage greater than  $\pm V_{ref} = \pm 1 \text{ V}$ . [24]

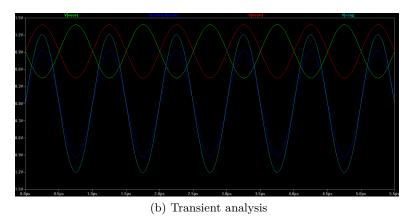

At the time of writing, it is believed that the signal from the CSA-and-shaper has to be converted from a single-ended signal to a differential signal and that it must be attenuated. This depends on the ADC front-end circuitry that is used for the project, which is not yet decided. Table 3.4 lists different elements that perform single-end-todifferential (SED) conversion. The generated differential signals should ideally have the same magnitude, and have a 180° phase relationship. The differential output voltage is (+V) - (-V). Mismatches in either magnitude or phase of one or both of these causes distortion, which in turn will degrade the overall accuracy of the system.

| Converting element                    | Category |

|---------------------------------------|----------|

| transformer coupling / flux coupling  | passive  |

| balun / transmission line transformer | passive  |

| Two operational-amplifiers (opamp)    | active   |

| Fully differential opamp (FDO)        | active   |

Table 3.4: Single-ended to differential conversion

The passive devices have advantages when it comes to high-frequency operations, noise contribution, and power consumption. Having other gains than unity will however complicate the circuit design. [31, 32, 33] This is a relatively easy process when using active devices, as attenuation can be achieved by setting the gain to < 1. There are many factors that must be considered to determine which method suits this project the best. A thorough comparative study was however beyond the scope of this thesis. To have the possibility to test the different methods, they were included on a test-and-verification circuit-board. This is presented in section 5.6.

The switched-capacitor front-end can be modeled as a resistor and capacitor in parallel. This makes the impedance frequency dependent. The value of the capacitor also changes depending on if the ADC tracks the input signal, or if it is in hold mode. To ensure proper signal integrity, and optimal performance of the ADC, an impedance compensation network should be included between the SED converter and AD9257. A proper compensation network will minimize the effects of the imaginary part, and also set the real part to a value that matches the source output, and PCB trace impedance. [34]

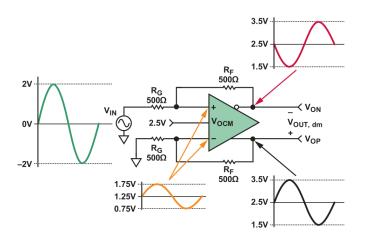

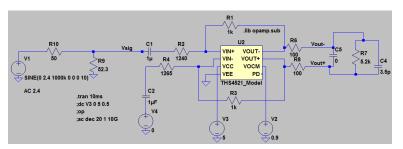

Figure 3.4: Fully differential amplifier, single-end to differential conversion [36].

FDOs are made to produce differential output signals, while the two-opamp configuration simulates such an architecture. Based on this, the FDO was given some extra attention. Figure 3.4 shows an FDO and the signal propagation with unity gain. This is achieved by setting  $R_G = R_F$  in both feedback paths. The signal will be attenuated if  $R_G > R_F$ . The resistor values must be closely matched to avoid phase unbalance. A common and practical feature on FDOs is the inclusion of an input that sets the output common-mode voltage. Thus, the required 0.9V can be set via this input. An FDO that could be an alternative in this project is THS4524-EP [35]. As AD9257-EP, this is an enhanced commercial product.

# Digital design

In order to capture data from AD9257, as well controlling it, systems that match the transfer protocols of the device must be made. This chapter discusses different methods, and which methods can be used in the final project. To fully understand the structures of the VHDL designs that are presented in this chapter, "A.2: VHDL design" and "A.3: Design flow" in Appendix A: Method should be read.

# 4.1 AD9257 readout logic

In order to capture the data from AD9257, a readout system must be designed. In this section, several readout methods are considered. Table 4.1 gives an overview of the methods that are discussed.

| Readout method | Implementation |

|----------------|----------------|

| SERDESIF       | Hard           |

| DDR-MSIO       | Hard/soft      |

| DDR-fabric     | Soft           |

Table 4.1: AD9257 data-capture methods

#### 4.1.1 Readout source considerations

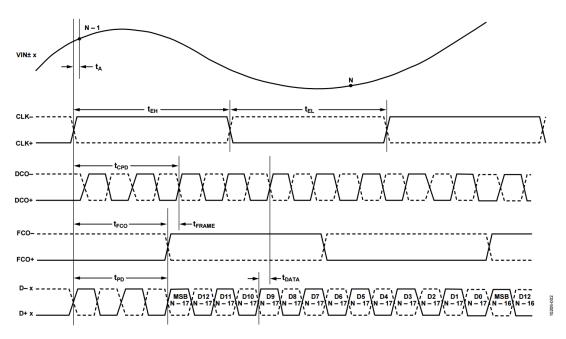

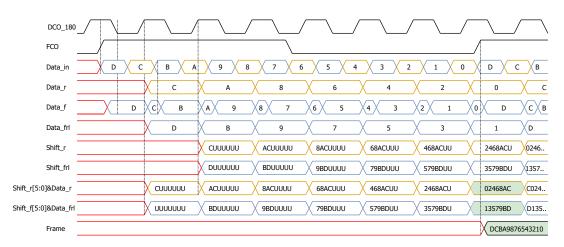

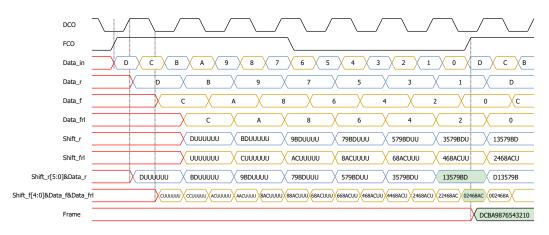

Information in this section is obtained from the datasheet of AD9257 [24]. Figure 4.1 shows the timing diagram of the ADC outputs.

$CLK\pm$  is the sample clock. After an input has been sampled and digitized, data is serially loaded onto the output. FCO $\pm$  is asserted each time the first bit of the 14-bit word is put on the output. FCO $\pm$  has the same frequency as  $CLK\pm$ . This clock can be used to separate the captured words in the readout system. DCO $\pm$  has a frequency of  $7 \times CLK\pm$ , and is aligned to the center of the data output D $\pm$ . Both edges of this clock can be used to capture each bit in the 14-bit word. All of the outputs are differential and conform to the ANSI-644 LVDS standard.

Figure 4.1: AD9257 sampled data output.[24]

#### 4.1.2 Specifications

#### ю

The IOs must be configured to receive LVDS signals. To get data from all 72 sensors, 9 AD9257 must be used. This yields 8 data outputs and 2 clock outputs per ADC, for a total of 90 differential inputs.

#### DDR data capture

The minimum sampling rate of AD9257 is 10 MHz. In regards to the specifications of the project, this is closest to the desired sample frequency. This means that the minimum capture clock frequency is 70 MHz, as DCO is  $7 \times CLK$ . The data from all channels, per AD9257, will be captured using this clock.

#### Deserialization

The data rate with minimum sampling is 140 Mbps. After 14 consecutive bits have been captured in each channel, data must be deserialized. This puts the data on a 14-bit parallel bus for further processing.

## 4.1.3 Serializer/deserializer interface

SF2 has hard serializer/deserializer interface (SERDESIF) blocks with dedicated inputs that can be used for capturing and deserializing data of differential signals. The block can be configured to work with standard serial protocols, as well as custom protocols through an external physical codings sub-layer mode. It is however not fully customizable. The data bus widths from the deserializer can only be set to predefined widths. 14 bits is not an alternative. The minimum input reference clock is 100 MHz. This is beyond the target 70 MHz. The minimum supported data rate is 1 Gbps. The target data rate in this project is 140 Mbps. Neither of the FPGAs discussed in section 3.2 have enough SERDESIFs to cover all detector outputs.[37] Using SERDESIF, if possible,

would require multiple FPGAs, and sampling the data inputs at a much higher rate than what is required.

### 4.1.4 Custom logic

Custom-made readout logic can be implemented in the fabric of the FPGA. The outputs from the ADC will in this case connect to the fabric through multi-standard I/Os (MSIO). These can be configured to accept differential LVDS inputs by connecting the input signal to compatible N- and P-inputs. Versions of SF2 and IG2 with enough I/Os to capture data from all sensors are also obtainable. [18]

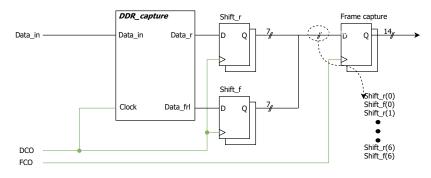

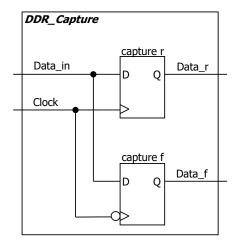

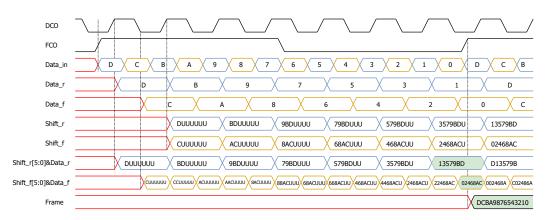

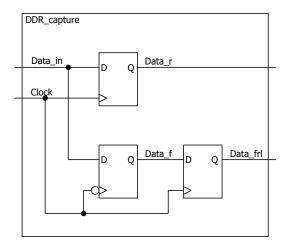

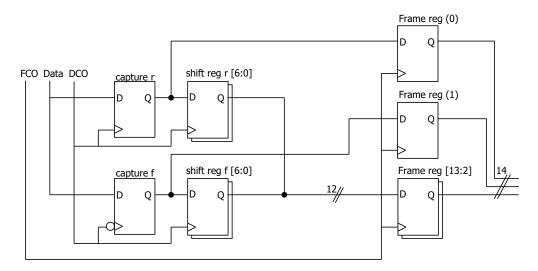

Figure 4.2 shows a 14-bit capture- and deserialize-circuit. The circuit is based on the 12-bit circuit in [38]. The data input and DCO connect to a DDR capture block. In this block, data is captured by DFFs on both edges of DCO. The outputs are connected to two separate serial in, parallel out, shift-registers: one for rising-edge data, and one for falling-edge data.

Data is subsequently shifted through the two shift registers. The entire word should be shifted in by the time data from a new word is present on the input. This is signaled by the rising edge of FCO. Content stored in the two shift-registers is latched into a 14-bit, frame capturing register that is triggered by FCO. The now deserialized data which is stored in this register must match the serial input data. This can be achieved by connecting the outputs from both shift registers in an interleaved manner, as pictured in the figure. The data on the outputs of this register can be used for further processing.

Clocks should be distributed to the register elements with minimum delay between clock edges. Routing through the fabric is not necessarily uniform, so the length of the wires between DFFs can differ. This can result in a skew between the clock edges on subsequent flip-flops, and timing margins could be worsened. For this reason, global or local clock nets should be used. Usage of such is indicated by the green wires in figure 4.2.

Figure 4.2: Readout circuit

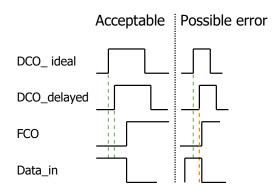

#### 4.1.4.1 DDR-MSIO

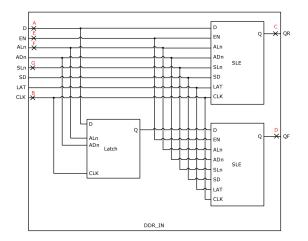

MSIOs can be configured to perform DDR capture by instantiating a DDR-macro in the VHDL design [18]. Figure 4.3 shows the schematic of the macro<sup>1</sup>. Rising-edge data is captured directly by the top-right flip-flop. Falling-edge data appears on data input D while CLK is high, as shown in figure 4.1. Since the latch is transparent when the clock is high, the state of D is stored on the output of the latch once the clock goes low. Data is then transferred to the output QF on the following rising-edge of DCO.

Figure 4.3: DDR\_IN macro[39]

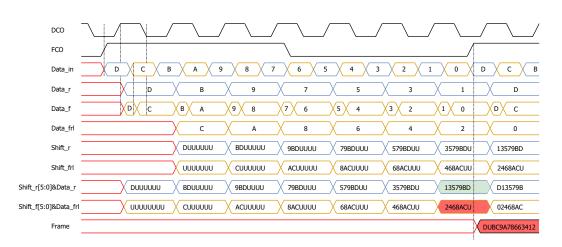

Timing when using DDR\_IN in place of DDR\_capture in figure 4.2 is shown in figure 4.4. When FCO is asserted, all bits must be captured. The blue lines represent data captured on the rising edge, while the orange lines represent data captured on the falling edge. As the diagram shows, it is not possible to latch all of the data bits into the frame register when FCO is asserted. The reason for this is that the first capture edge of DCO, as shown in figure 4.1, is a rising edge. This creates a skew between the two capture paths, where the data captured on falling edge trails behind the data captured on rising edge by one clock cycle. When FCO is asserted, rising-edge data is present on the outputs of shift\_r and data\_r. Because of the skew, the last captured falling-edge data will not be present on data\_frl. Data\_f is not reachable. The data latched into the frame capture register is for this reason not valid.

It is however possible to use MISOs configured for DDR if the phase of DCO is shifted by 180° before it is connected to the clock inputs in figure 4.2. This removes the skew that caused the non-valid readout. Timing in this case is shown in figure 4.5. The phase shift can be achieved with an inverter or a PLL.

Using an inverter to shift the phase is possible. It will however add delay to DCO, which results in a change in the timing relationship between it, FCO and the data. The significance of this increases with increased frequency, as illustrated in figure 4.6. This is true assuming the delay contribution from the inverter is independent of the clock frequency. As the target frequency of DCO is 70 MHz in this project, the added delay might not be critical.

$<sup>^1 \</sup>rm{In}$  the timing diagrams, signals in the DDR macro: D = Data\_in, Q on the latch = Data\_f, QR = Data\_r, QF = Data\_frl

Figure 4.4: DDR capture using DDR\_IN macro timing.

The blue lines represent data captured on rising edge. Falling edge is represented by orange lines. Green fill marks that all bits are captured before FCO is asserted. Red fill marks the opposite.

Figure 4.5: DDR capture when DCO is skewed 180 degrees timing.

The orange lines represent data captured on rising edge. Falling edge is represented by blue lines. Green fill marks that all bits are captured before FCO is asserted.

Figure 4.6: Significance of skew on DCO in relations with FCO and data.

By using a PLL, both a phase shift and/or a delay can be added to DCO. The advantage of a PLL is that it corrects the output if a change is detected between the output and the conditions that were set. Thus, the PLL can be configured so that DCO is inverted without any change in the relationship between DCO, FCO and the data. Using PLLs would however require two FPGAs as none of the alternative FPGAs mentioned in section 3.2 have more than 8 PLLs. The final alternative is to use input delay elements. These are configurable through I/O-constraining. The delay can be set to D+6.3 ns where D is the intrinsic delay in the I/O [18]. For the target frequency of DCO, the delay needed to invert the signal would be:

$$\frac{1}{2 \times f_{DCO}}$$

which is about 7.1 ns. Hence, this option depends on D.

## 4.1.4.2 DDR-fabric

Figure 4.7 shows an alternative way of performing DDR capturing without inverting DCO. Rather than configuring the MSIOs to do the capturing, they are used as ordinary inputs. Two DFFs are implemented in place of the DDR\_capture block in figure 4.2. The timing is shown in figure 4.8. This works by combining the shifted data with the latest data on the DDR capture block outputs. An inverter is used on the DFF that captures falling-edge data. This will worsen the timing margins between data\_f and shift\_f. The timing margin is already tight as the two DFFs are triggered by opposite clock edges. Unlike the previously discussed design with an inverter in section 4.1.4.1, this is the only path that is affected by the additional delay.

Another alternative is to create the circuit shown in figure 4.9. Compared to the DDR-macro, the latch is replaced by a falling-edge DFF. As the timing shows in figure 4.10, this implementation will work by combining the shift registers with all sequential outputs. This also uses an inverted version of DCO on only one DFF. It does not have any advantages timing-wise compared to the circuit in figure 4.7. In fact it has a slight disadvantage as it uses one additional DFF per capture block.

Figure 4.7: Alternative DDR capture logic

Figure 4.8: Alternative capture timing-

The blue lines represent data captured on rising edge. The falling edge data is represented by orange lines. Green fill marks that all bits are captured before FCO is asserted.

Figure 4.9: Macro circuit implemented in fabric

Figure 4.10: DDR\_macro circuit implemented in fabric timing. The blue lines represent data captured on rising edge. The falling edge is represented by orange lines. Green fill marks that all bits are captured before FCO is asserted.

# 4.1.5 Preliminary conclusion

Using SERDESIF<sup>2</sup> or PLLs require multiple FPGAs. This is of course an option, but it would increase the footprint of the PCB which should be as small as possible. Therefore, the other methods are considered to be better alternatives. The designs using DDR-MSIOs in combination with an inverted DCO, and the DDR-fabric using two flip-flops are considered to be the best of the custom methods. Their timing is depicted in figures 4.5 and 4.8 in the previous section.

Critical timing paths in figure 4.5 are on the bit capture in the DDR\_blocks, and the last captured bit before the frame is capured. Due to the skew on DCO from the inverter, this is worsened. In the DDR\_block, hold time violation is of concern for data\_r, and also the latch data\_f. This is caused by the delayed capture of their inputs. On the last bit before FCO is asserted, the delayed capture on data\_frl may cause a setup time violation on the frame capture register. This can be mitigated by delaying FCO by e.g  $T_{DCO}/2$ . The delay can be added either by buffers or input delay, as mentioned in section 4.1.4.1.

The design using two DFFs in fabric has its critical path on data\_f. This can cause a hold time violation in the falling-edge-capture DFF, and a setup violation in the frame capture register. The latter can be mitigated by delaying FCO by e.g  $T_{DCO}/8$  by the same means mentioned in the previous paragraph. Since the target frequency is relatively low, and by applying proper timing constrains, both designs will probably work.

It should be mentioned that the skew from the inverter is one of many variables that affect timing margins. Process variations will introduce random skews. Environmental changes in temperature can cause a drift where the skew changes over time. Highfrequency environmental variations can cause jitter on clock edges. All these variables must be accounted for. It is therefore important to verify that timing requirements are met. Microsemi provides a timing analysis tool that analyses timing with four-corner analysis, where process, voltage, and temperature are the variables. [10, 40]

<sup>&</sup>lt;sup>2</sup>Due to certain restrictions, it is not certain if this can be configured to work against AD9257.

# 4.1.6 Realized readout design

The custom made DDR-fabric, two-DFF design was used in all systems that will be explained in later chapters. This section describes the structural design of the readout logic.

#### 4.1.6.1 Fabric DDR-capture and deserializer

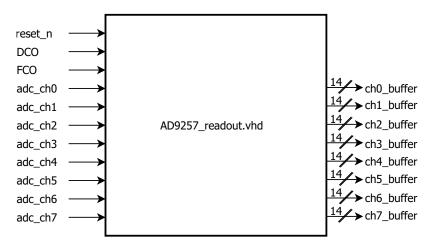

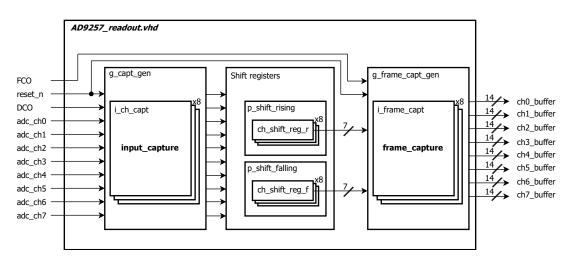

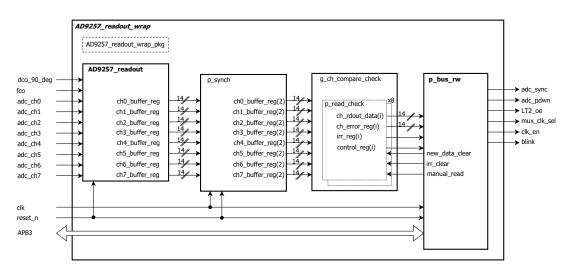

The top-level structure of the readout logic for one AD9257 can be seen in figure 4.11. In addition to the serial data and clock inputs, and the deserialized data outputs, a synchronous active low reset that can clear all the internal registers is included. For multiple ADCs, this structure can be instantiated multiple times in a top level file. The internal structure is shown in figure 4.12. It is comprised of three structures which are explained below.

Figure 4.11: Readout logic top

Figure 4.12: Readout logic internal

#### Input\_capture

Input\_capture is instantiated for all channels inside a generate statement. Each

instance contains the DDR capture logic in figure 4.7. If it is decided to change the method of DDR-capture at a later stage, it is only necessary to replace this instance.

## P\_shift\_rising/falling

P\_shift\_rising and p\_shift falling create shift registers for all channels by using for-loops. These processes are located in the top level.

#### Frame\_capture.

Frame\_capture is instantiated for all channels inside a generate statement. Each instance latches readout data from each channel into 14-bit parallel registers on the rising edge of FCO.

The combined register transfer level (RTL) structure is shown for one channel in figure 4.13.

Figure 4.13: Logic for input capture, shifting and frame capture

# 4.2 AD9257 control logic

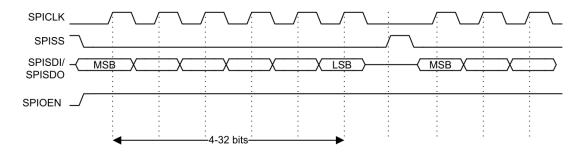

AD9257 has accessible registers which control certain settings. Having the possibility to change settings of the ADC can be useful. As an example: writing to register address 0x0D lets the user set test patterns on the ADC output. In this case, the analog front end is internally disconnected from the outputs. It is also possible to change the phase of DCO. If e.g. environmental variations cause the phase to change during operation, control logic that corrects this by adjusting the phase could be implemented. The register control section is accessed by a three wire SPI interface, where data in and data out are combined onto a single, bidirectional pin.[24] In the following sections, different methods of implementing an SPI master is discussed. Table 4.2 lists the methods that were considered.

# 4.2.1 SPI slave considerations

The general transfer protocol is divided into two phases: instruction phase and data phase. The instruction phase consists of transferring 16 bits from master to slave. The

| Control method       | Implementation |  |  |  |

|----------------------|----------------|--|--|--|

| Custom fabric master | Soft           |  |  |  |

| Microsemi CoreSPI    | Soft           |  |  |  |

| Microsemi MSS SPI    | Hard           |  |  |  |

Table 4.2: Methods of implementing an SPI master

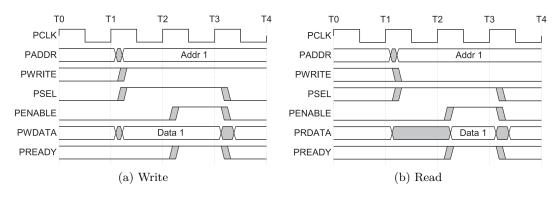

instruction contains data telling the slave whether the data phase is a master read- or write-operation, how many bytes of data to transfer, and the memory address. Once the instruction has been decoded, the data phase is executed.

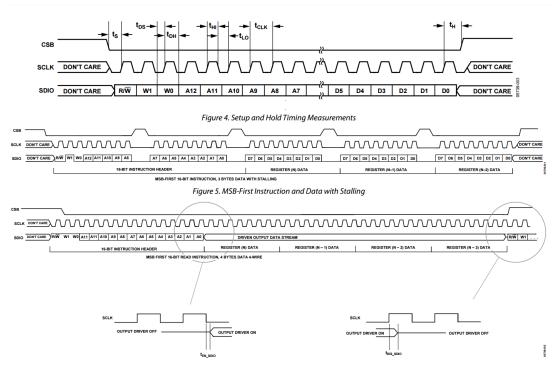

Data can be transferred to the ADC in different ways. A transfer is initiated by setting the chip select bar (CSB) signal low. This tells the state machine in AD9257 to process the signals on the serial clock pin (SCLK), and on the serial data I/O (SDIO). The slave captures data on the rising edge of SCLK, while it puts data on the bidirectional pin SDIO on the falling edge of SCLK. SCLK has a minimum period of 40 ns [24]. I.e. the maximum frequency is 25 MHz. If multiple SPI slaves are used, as is the case in this project, CSB must be stalled at logic 1 when there is no active transfer.

Two of the instruction bits decide the number of data bytes to transfer in the data phase. The options are one, two or three bytes, or streaming. The latter option transfers bytes continuously until CSB is asserted. For all but streaming, CSB can be set to 1 between each transferred byte, or remain low for the entire transfer. This also applies for the instruction phase. Between bytes, the register address is incremented automatically. The latter applies to all modes. Figure 4.14 shows the timing of different transfer modes.[41]

# 4.2.2 SPI master specifications

Changing settings or resetting AD9257 is not functionality where speed is critical. At this stage in the design process, this system will be used to characterize the controllability of AD9257. The minimum requirements of the SPI master is as follows:

- Transfer signals to and from the SPI slave at a rate of no more than 25 MHz.

- Load data onto SDIO on SCLK falling edge.

- Register data from SDIO on SCLK rising edge.

- Transfer of data between master and slave must support the minimum:

- Transfer one byte of data in the data phase.

- Transfer instruction and data one byte at the time, stalling CSB at logic '1' between each transferred byte.

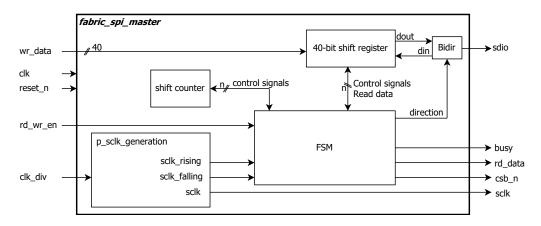

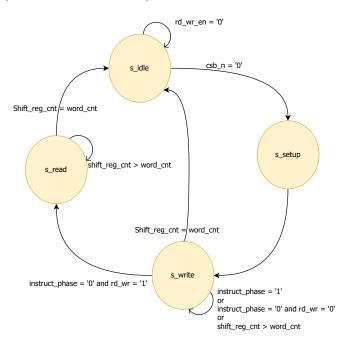

## 4.2.3 Custom SPI master in fabric

Figure 4.15 shows the internal structure of an SPI master that can be implemented in the FPGA fabric.

Figure 4.14: AD9257 SPI interface timing diagrams[41]

Figure 4.15: Fabric SPI master. Note that **bidir** must be an IO as high impendance can not be implemented in the fabric

Data input wr\_data is loaded with up to 40 bits. This is equivalent to one instruction and three data bytes. Clk\_div sets a factor that decides the frequency of SCLK, which is generated in p\_sclk\_generation. When these have received valid data, rd\_wr\_en can be asserted for at least one period of the system clock to enable a transfer. It must then be deasserted. A 40-bit shift register shifts data in from the din input when reading from the slave, or shifts data onto dout when writing data to the slave. A counter is used to keep track of the shifting process. When a transfer is in progress, busy is asserted to notify the master control system.

Figure 4.16: Fabric SPI master FSM

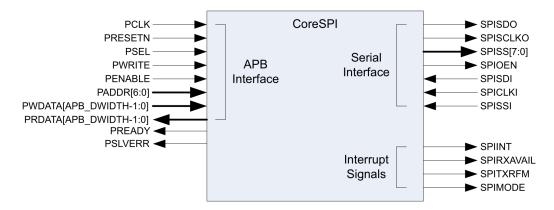

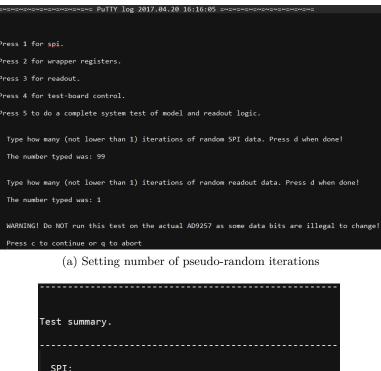

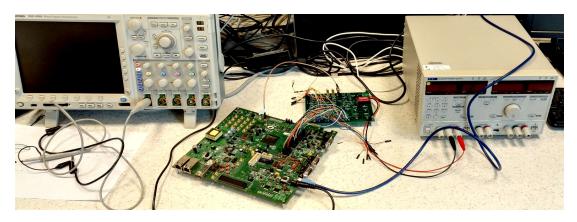

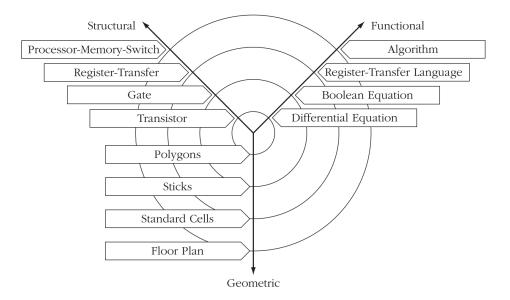

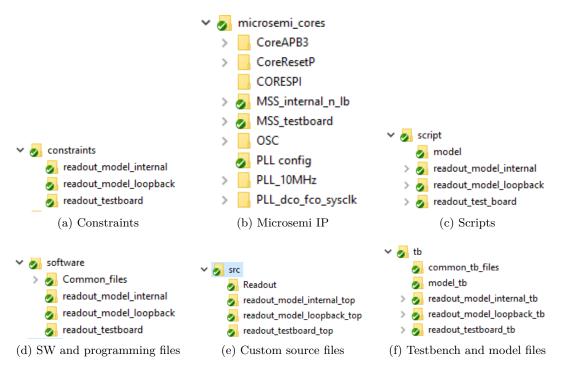

A finite state machine (FSM) is used to control all operations. It is implemented in one process which is sensitive to a system clock. The state diagram is shown in figure 4.16. The FSM is initially in the s\_idle state. In this state, no transfer is active. When rd\_wr\_en is asserted, the state is changed to s\_setup. In this state, data is loaded into the shift register, SCLK generation is enabled, CSB\_n is de-asserted and busy is asserted. Certain instruction bits are loaded into internal registers to be used in following states. An instruction signal is also asserted as the first operation is writing the instruction to the slave. The next state is then directly changed to s\_write.