# Design and implementation of fast and sparsified readout for Monolithic Active Pixel Sensors

Olav Torheim

Thesis for the degree of Philosophiae Doctor (PhD) at the University of Bergen

2010

## Contents

| A  | ckno | wledgr | nents                                                                               | v   |

|----|------|--------|-------------------------------------------------------------------------------------|-----|

| Sı | ımm  | ary    |                                                                                     | vii |

| 1  | Soli | d stat | e pixel detectors for high energy physics                                           | 1   |

|    | 1.1  | Opera  | ation principle of silicon detector                                                 | 2   |

|    | 1.2  | Types  | s of silicon detectors                                                              | 3   |

|    |      | 1.2.1  | Sensors of high-resistivity processes                                               | 3   |

|    |      | 1.2.2  | Sensors manufactured in low-resistivity processes                                   | 5   |

|    | 1.3  | Pixel  | detectors for CBM                                                                   | 14  |

|    |      | 1.3.1  | Requirements                                                                        | 15  |

|    |      | 1.3.2  | Limitations and advantages of standard pixel architectures .                        | 15  |

|    |      | 1.3.3  | Proposed solutions                                                                  | 16  |

| 2  | Rea  | d out  | architectures for particle trajectory detectors                                     | 21  |

|    | 2.1  | Physic | cal model - clusters                                                                | 22  |

|    | 2.2  | Reado  | out and data sparsification architectures                                           | 24  |

|    |      | 2.2.1  | Centralized readout with rolling shutter                                            | 25  |

|    |      | 2.2.2  | Data driven and triggered readout with timestamping                                 | 27  |

|    |      | 2.2.3  | Data driven and delayed readout with timestamping                                   | 28  |

|    |      | 2.2.4  | Architectures suitable for MAPS                                                     | 29  |

|    | 2.3  | Data   | reduction techniques                                                                | 30  |

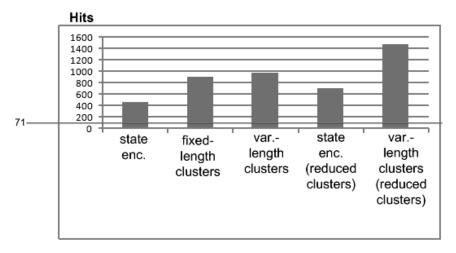

|    |      | 2.3.1  | State encoding                                                                      | 30  |

|    |      | 2.3.2  | Clusterization                                                                      | 33  |

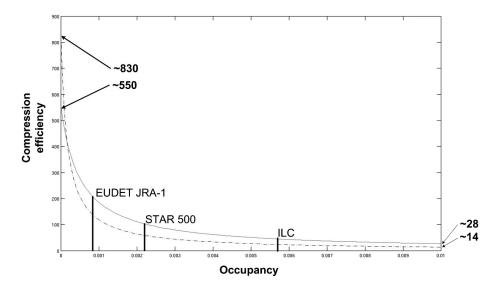

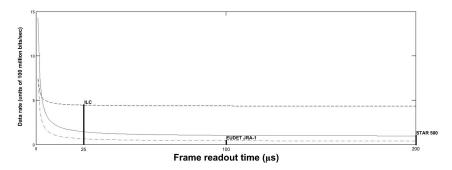

|    |      | 2.3.3  | Compression efficiencies in standard MAPS with moderate occupancies                 | 36  |

|    |      | 2.3.4  | Compression efficiencies with respect to multiplicity and matrix width              | 38  |

|    |      | 2.3.5  | Comparison of clusterization and state encoding with general compression techniques | 39  |

|   | 2.4 | Segme  | entation of pixel matrix into sparse scan banks          |

|---|-----|--------|----------------------------------------------------------|

|   |     | 2.4.1  | Necessity of segmentation                                |

|   |     | 2.4.2  | Calculating the width of the segments                    |

|   | 2.5 | Line a | address suppression and other data formatting issues 42  |

|   |     | 2.5.1  | Line address suppression                                 |

|   |     | 2.5.2  | Other data formatting issues                             |

|   | 2.6 | On-ch  | ip buffering and memory issues                           |

|   | 2.7 | Concl  | usion                                                    |

| _ |     |        |                                                          |

| 3 |     |        | 26 - Sensor with data sparsification 47                  |

|   | 3.1 |        | ved performances of MIMOSA series of pixel detectors 48  |

|   |     | 3.1.1  | Background                                               |

|   |     | 3.1.2  | The MIMOSA22 and SUZE prototypes                         |

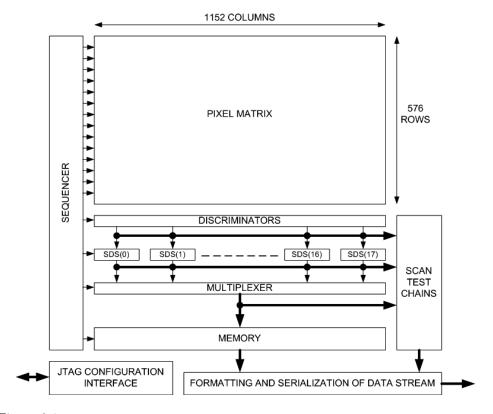

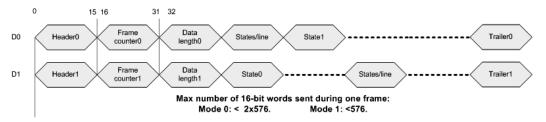

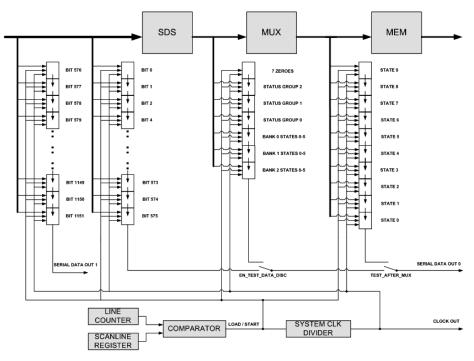

|   | 3.2 |        | tecture of MIMOSA26                                      |

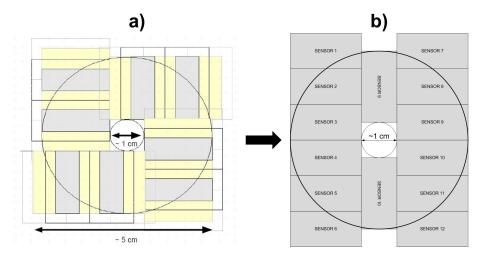

|   |     | 3.2.1  | Sensors part                                             |

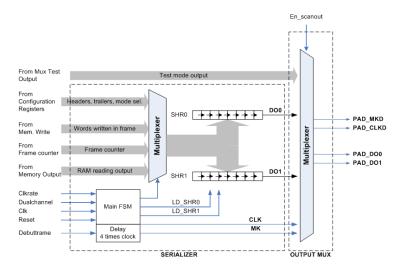

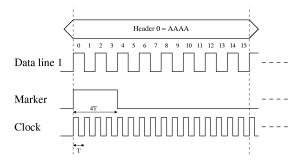

|   |     | 3.2.2  | Digital treatment part                                   |

|   | 3.3 |        | ation                                                    |

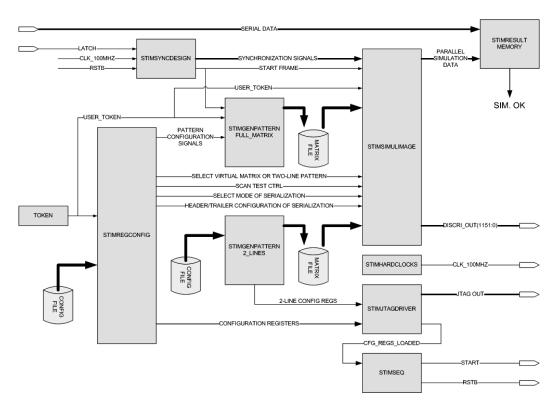

|   |     | 3.3.1  | Simulation environment                                   |

|   |     | 3.3.2  | Checking the datapath                                    |

|   |     | 3.3.3  | Checking the entire design                               |

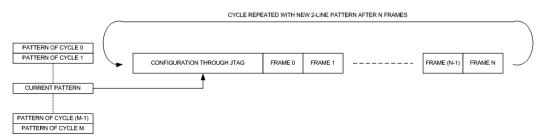

|   |     | 3.3.4  | Input patterns                                           |

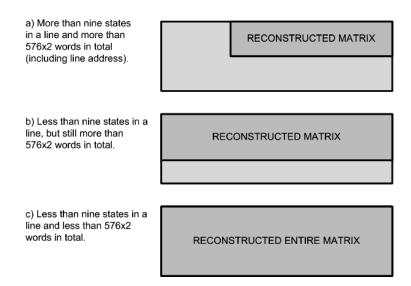

|   |     | 3.3.5  | Pattern reconstruction                                   |

|   |     | 3.3.6  | Pertinency and weaknesses of simulation                  |

|   | 3.4 |        | vare tests                                               |

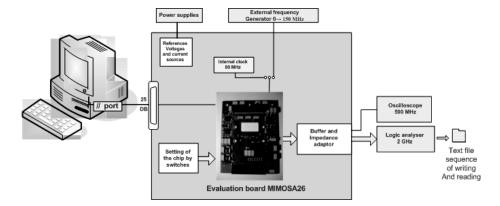

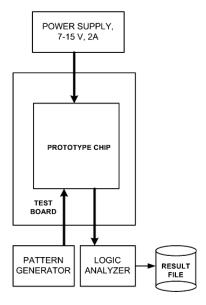

|   |     | 3.4.1  | Test environment                                         |

|   |     | 3.4.2  | Performed tests                                          |

|   | 3.5 |        | tectural improvements with respect to SUZE 83            |

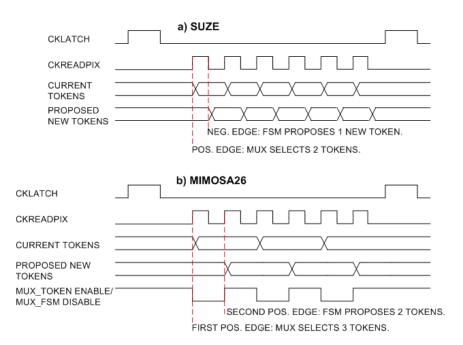

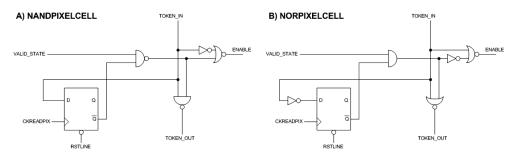

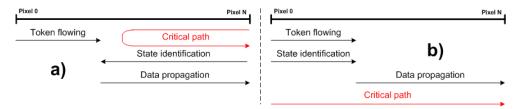

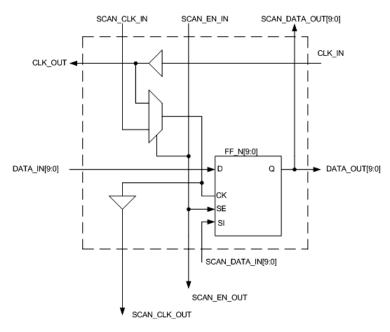

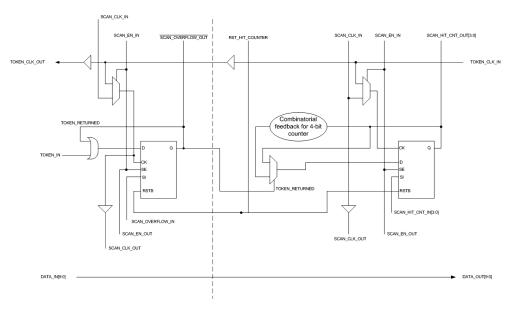

|   |     | 3.5.1  | Parallelization of operations                            |

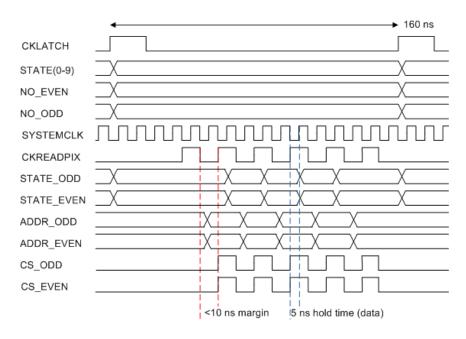

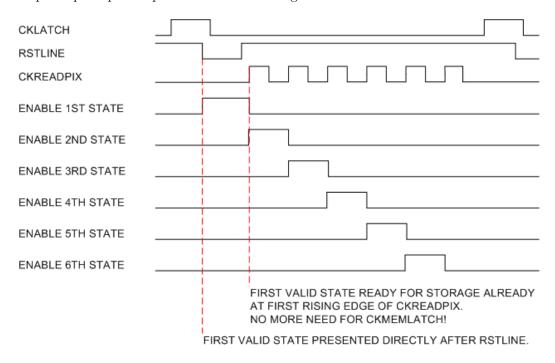

|   |     | 3.5.2  | Improved clocking scheme                                 |

|   | 3.6 |        | usion                                                    |

|   |     | 3.6.1  | Achieved performances                                    |

|   |     | 3.6.2  | Perspectives of improved timing                          |

|   | 3.7 | _      | ectives for STAR and CBM                                 |

|   |     | 3.7.1  | STAR: Twice as large matrix and higher data transmission |

|   |     |        | rate (Ultimate-1, Ultimate-2)                            |

|   |     | 3.7.2  | CBM: Twice as high frame readout rate (MIMOSIS-1) 92     |

| <b>4</b> | 3D         | ASIC        | s for pixel detectors                                              | 93  |

|----------|------------|-------------|--------------------------------------------------------------------|-----|

|          | 4.1        |             | vation for 3D integration in high energy physics                   | 94  |

|          |            | 4.1.1       | Requirements of future pixel detectors                             | 94  |

|          |            | 4.1.2       | Technological features offered by 3D integration                   | 94  |

|          |            | 4.1.3       | 3D integrated architectures for providing fast, intelligent small- |     |

|          |            |             | pitch pixels                                                       | 96  |

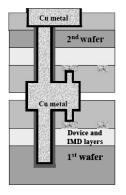

|          | 4.2        | Types       | s of 3D integration techniques                                     | 98  |

|          | 4.3        | 3D in       | tegration suppliers                                                | 100 |

|          | 4.4        | From        | hybrid detectors to 3D                                             | 101 |

|          | 4.5        | From        | MAPS to 3D - Internal IPHC prototypes                              | 103 |

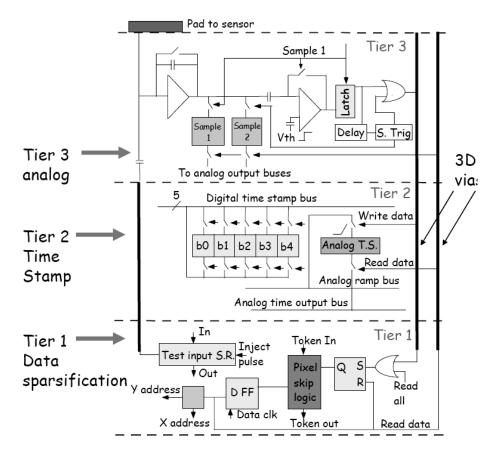

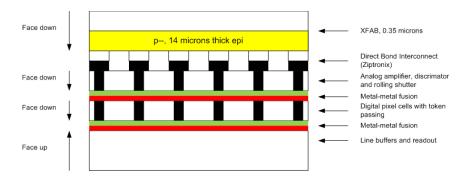

|          |            | 4.5.1       | 3-tier architecture: Strip-like                                    | 104 |

|          |            | 4.5.2       | 3-tier architecture: Rolling shutter with discriminator in every   |     |

|          |            |             | pixel                                                              | 106 |

|          |            | 4.5.3       | 2-tier architecture: Timestamping and delayed readout              | 107 |

|          | 4.6        | Concl       | lusion                                                             | 121 |

| _        |            | ,           |                                                                    | 100 |

| 5        |            | _           | all design for a CBM 3D integrated detector                        | 123 |

|          | 5.1        | _           | irements for a 3D integrated pixel detector for MVD                | 126 |

|          |            | 5.1.1       | Spatial and time resolution                                        | 126 |

|          |            | 5.1.2       | Radiation hardness                                                 | 127 |

|          |            | 5.1.3       | Power consumption                                                  | 128 |

|          |            | 5.1.4       | Data reduction                                                     | 129 |

|          | F 0        | 5.1.5       | Proposed architectures                                             | 130 |

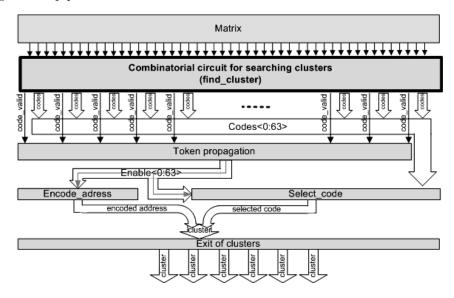

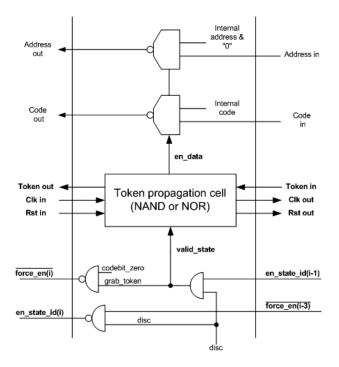

|          | 5.2        |             | driven readout with tokens and distributed state encoding          | 133 |

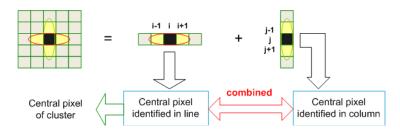

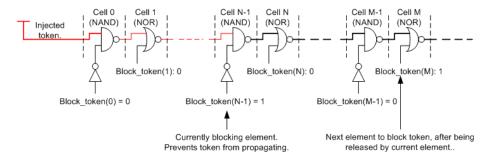

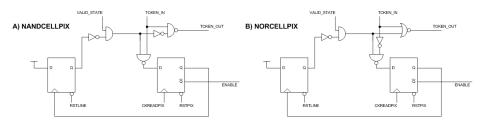

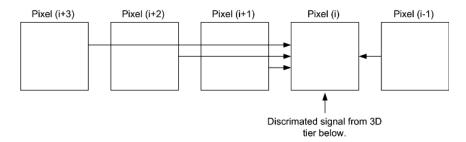

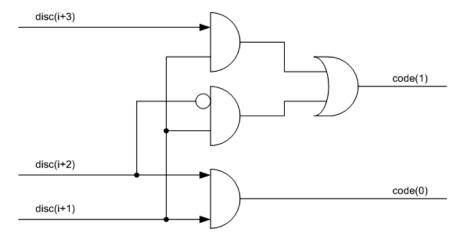

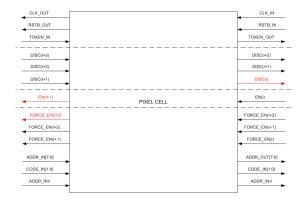

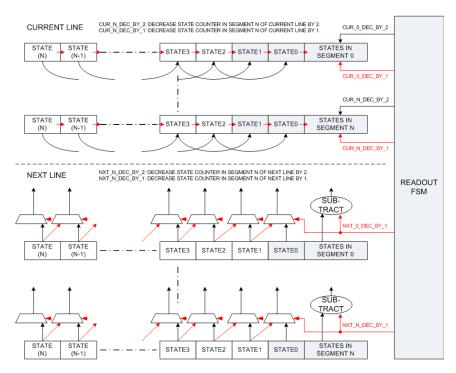

|          |            | 5.2.1       | Distributed state encoding and token passing between               | 100 |

|          |            | <b>5</b> 00 | pixels in each line                                                | 133 |

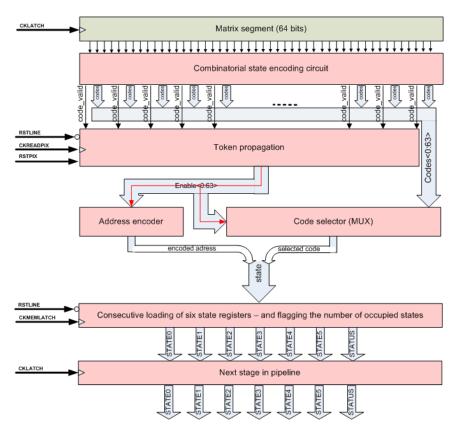

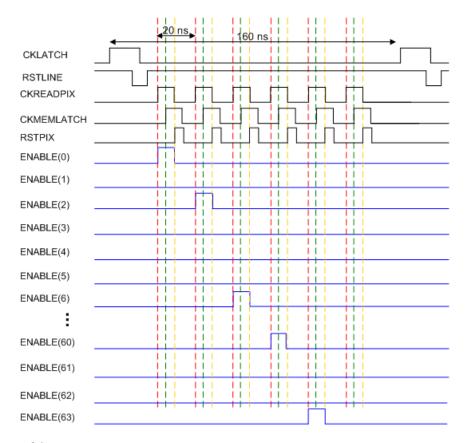

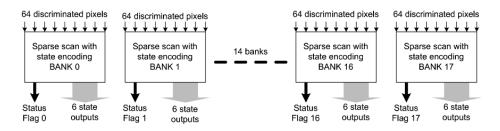

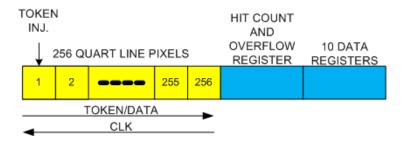

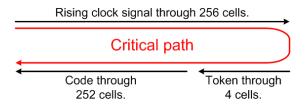

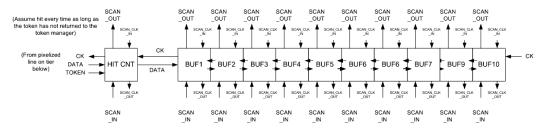

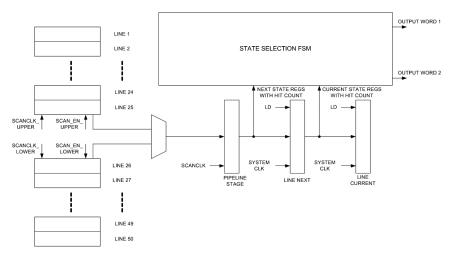

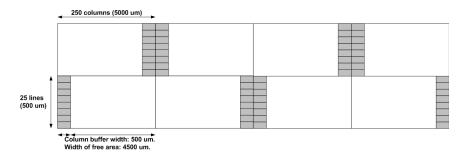

|          |            | 5.2.2       | Line segment structure                                             | 137 |

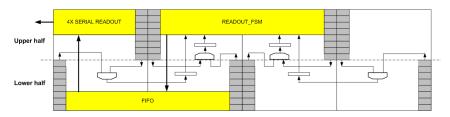

|          |            | 5.2.3       | Readout                                                            | 142 |

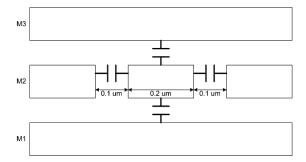

|          |            | 5.2.4       | Floorplanning and layout                                           | 146 |

|          |            | 5.2.5       | Serial output links                                                | 146 |

|          |            | 5.2.6       | Noisy pixel contribution to data stream                            | 150 |

|          |            | 5.2.7       | Power consumption                                                  | 151 |

|          | <b>F</b> 0 | 5.2.8       | Scalability of architecture                                        | 153 |

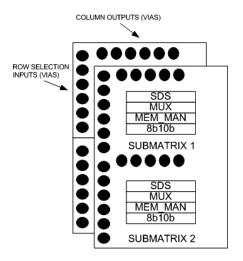

|          | 5.3        |             | E on top of the rolling shutter                                    | 157 |

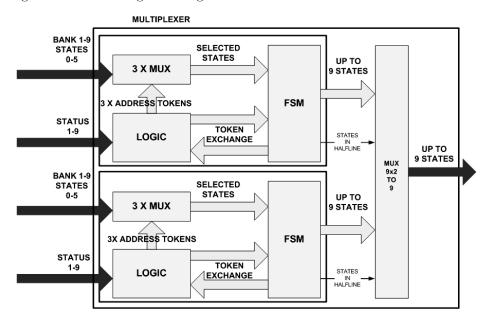

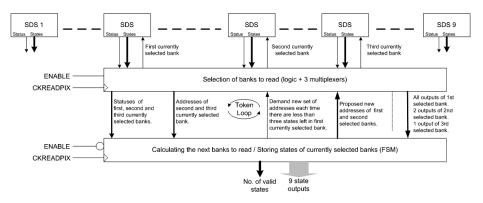

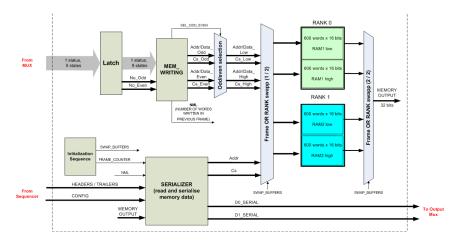

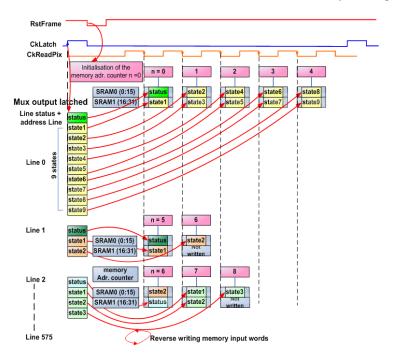

|          |            | 5.3.1       | Dimensioning SDS and multiplexer                                   | 158 |

|          |            | 5.3.2       | Dimensioning the memory                                            | 159 |

|          |            | 5.3.3       | Floorplanning and layout (area estimations)                        | 159 |

|          |            | 5.3.4       | Serial output links                                                | 160 |

|          |            | 5.3.5       | Power consumption                                                  | 160 |

|              | 5.4        | v                                                                                                                                                                                                                                                                                                                                                                      | 161<br>163                                    |

|--------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 6            | Sun        | nmary and outlook                                                                                                                                                                                                                                                                                                                                                      | 165                                           |

| A            | Pub        | olications                                                                                                                                                                                                                                                                                                                                                             | 169                                           |

| В            | Con        | nparison of clusterization and state encoding with JPEG                                                                                                                                                                                                                                                                                                                | 171                                           |

| $\mathbf{C}$ | Con        | trol registers for MIMOSA26                                                                                                                                                                                                                                                                                                                                            | 175                                           |

| D            | D.1        | Memory test structures                                                                                                                                                                                                                                                                                                                                                 | 1 <b>77</b><br>177<br>178                     |

| $\mathbf{E}$ | ILC<br>E.1 | 1 1                                                                                                                                                                                                                                                                                                                                                                    | <b>181</b><br>181                             |

|              |            | with clusterization                                                                                                                                                                                                                                                                                                                                                    | 181<br>182                                    |

|              | E.2        | ILC outer layers: Lower power and higher pixel accuracy  E.2.1 Requirements derived from physics experiment  E.2.2 Data sparsification with state encoding  E.2.3 Data sparsification with clusterization  E.2.4 Implementation and memory issues with state encoding  E.2.5 Implementation and memory issues with clusterization  E.2.6 Memory storage considerations | 184<br>184<br>185<br>186<br>188<br>188<br>191 |

| F            | F.1        | F.1.1 Redundant case, only seeing hits of nearest neighbors F.1.2 Nonredundant case, propagating hit information as long as necessary                                                                                                                                                                                                                                  | 193<br>193<br>194<br>195<br>198               |

| $\mathbf{G}$ |            |                                                                                                                                                                                                                                                                                                                                                                        | 190<br>201                                    |

### Acknowledgments

This work has been carried out within the Microelectronics Research Group at the Department of Physics and Technology, University of Bergen, and the IPHC at CNRS in Strasbourg, during the period of January 2008 to May 2010.

At the University of Bergen, I would like to thank my supervisor Kjetil Ullaland and my co-supervisor Dieter Röhrich for guidance and support throughout the period of work. Shiming Yang for helping me with the part of my thesis related to CBM conceptual design. I would also like to thank Kjell Brønstad, Arne Solberg, Nikolai Østgaard and Yngve Skogseide for good cooperation during the first year of my PhD scholarship when I was working with the SIR-2 spectrometer.

At IPHC in Strasbourg, I would like to thank Marc Winter and Christine Hu for providing me with interesting and challenging work. I would also like to thank Guy Doziere and Andrea Brogna for helping me with my work and with writing my thesis. Similarly I would also like to thank Abdelkader Himmi, Xiachao Fang, Yunan Fu, Andrej Dorokhov, Wojciech Dulinski, Claude Colledani, Rita De Masi, Jerome Baudot, Matthieu Goffe, and Yavuz Degerli (IRFU-Saclay). And I would like to thank to Michael Deveaux for guiding me in the right direction during my work with conceptual design for CBM and providing me with the simulation results of the CBM MVD.

Then I thank my friends Alexandre Thöne, Elodie Vinandy, Alexandre Junger, Emmanuel Rapp, and Yann Heintz, for motivating me to learn french and taking me to a lot of exciting adventures throughout France and Europe.

Finally, I would also like to thank my parents Henny and Per Torheim for their support. Also my daughter Marie Torheim for providing me with inspiration for finishing my studies as quickly as possible.

Olav Torheim, Bergen, September 2010.

### Summary

This thesis focuses on the development of smart pixel readout architectures that should ultimately be targeted for the Micro-Vertex Detector (MVD) of the CBM (Compressed Baryonic Matter) experiment. The technical challenge of building a pixel detector for this experiment is to design particle sensors capable of meeting at the same time very strict requirements on both spatial resolution, time resolution and radiation hardness.

The MVD is required to obtain data for the open charm physics programme of CBM. For a collision rate of  $10^6$  collisions/second, it can be shown that the required time resolution for the first MVD detector station, 5 cm away from the target, is around 2  $\mu$ s, while the required spatial resolution becomes 5  $\mu$ m (assuming a material budget of  $300 \,\mu$ m Si). The detector has to withstand a non-ionizing radiation of  $2 \cdot 10^{14} neq/cm^2$  and the material budget is about 0.2-0.3 % of radiation length.

While bump-bonded hybrid detectors meet the requirements on time resolution and radiation hardness, they do not provide the required spatial resolution and material budget. Detectors based on Monolithic Active Pixel Sensors (MAPS), on the other side, have sufficiently high spatial resolution and low material budget, but they do not meet the requirements on time resolution and radiation hardness. To obtain a detector that has the superior spatial resolution and material budget of MAPS while at the same time providing the fast readout rate and high radiation tolerance of hybrid detectors, new technologies must therefore be explored.

Increasing time resolution also means increasing the amount of raw data to transfer. With  $2\,\mu s$  frame readout time, and a typical pixel matrix size of 500,000 binary discriminated pixels, the raw data rate of each sensor becomes 250 Gbits/sec. To keep the amount of serial data links from the sensors at an acceptable level with respect to bonding and material budget, and to avoid overloading the data acquisition system, it is also necessary to embed data reduction or data compression functionalities within the sensor readout electronics.

Towards fulfilling the requirements of the needed intelligent pixel detectors, numerous steps have been taken. At the IPHC laboratories of CNRS in Strasbourg,

work has been done and is under progress to develop such detectors. The work is done step by step, starting with the most primitive and low bandwidth CMOS pixel sensors while making progress towards ever more complex and sophisticated detectors, with techniques like zero suppression and 3D integration - all techniques that will be explained in detail later in this thesis.

In the first generation of IPHC MAPS based pixel sensors, the individual pixels were externally addressed and the pixel matrix was read out entirely [1]. This means that even for detecting a few hits, the entire matrix had to be read out. In fact, as the pixel signal is at the same order as natural process variations, the pixel matrix had to be read twice and the hit signals extracted through offline correlated double sampling. In the second generation of chips, the frame readout time was reduced by embedding correlated double sampling and row-wise parallel readout, called rolling shutter operation. However, without any kind of data compression, such a reduction in the frame readout time comes at the expense of an ever increasing data rate. My contribution to the development of the MIMOSA26 sensor and the first 3D integrated detectors based on MAPS technology will be discussed in the following:

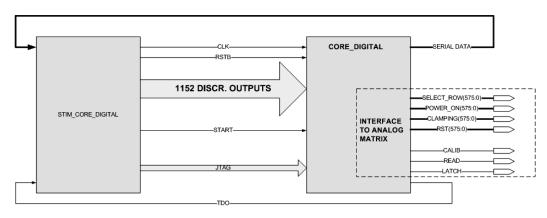

Starting my work at IPHC in march 2008, the first steps had been taken towards embedding data reduction micro circuits in the periphery of the active pixel matrix. A prototype circuit, SUZE, interfacing two programmable pixel rows of 128 columns, had been designed, manufactured, and tested, proving the principle of zero suppression. The next step, where I did my first contribution, was then to build the zero suppression into an actual sensor, the MIMOSA26. As MIMOSA26 had 1152 columns, nine times more as those interfaced by SUZE, one had to completely redesign core parts of SUZE for remaining at an operating frequency of 100 MHz.

MIMOSA26 was developed and manufactured for providing fast and sparsified readout for the EUDET-JRA1 beam telescope [2]. Although being a large step forward in terms of reduced frame readout time ( $100\,\mu s$ ), the row-by-row processing of the entire matrix becomes a bottleneck for further reduction in frame readout time. With dual-sided readout and smaller feature size, the architectures based on MI-MOSA26 are expected to provide frame readout times down to  $25\,\mu s$ . However, at some point it becomes difficult to decrease the frame readout time due to the inherited architectural limitations. The next step towards improving the time resolution of the monolithic active pixel detectors is therefore to develop a new architecture that utilizes the new degrees of freedom offered by 3D integration.

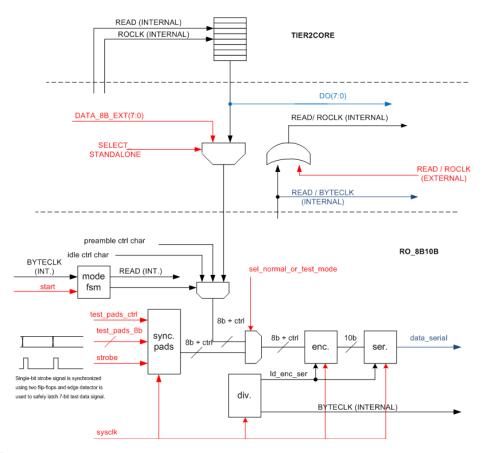

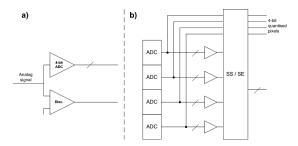

With the first 3D detector prototypes developed at IPHC, two architectural approaches were followed: The first one, targeted at the inner layers of the International Linear Collider (ILC), was to power on all the pixels and provide the analog pixels with a digital tier containing timestamp circuitry ( $\frac{950\,\mu s}{2^5} \approx 30\,\mu s$  time

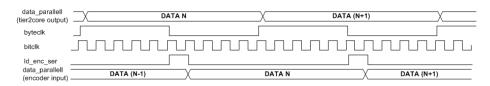

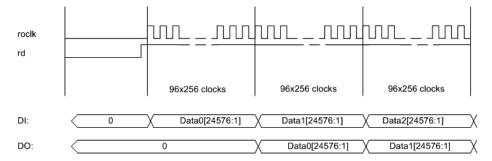

resolution) and to read out the timestamp information between the bunch train. The analog pixels could then be turned off completely during the dead time to save power. To provide this architecture with a faster data transmission using a minimum of bonded wires, a readout control circuit with 8b10b serial transmission was designed and implemented.

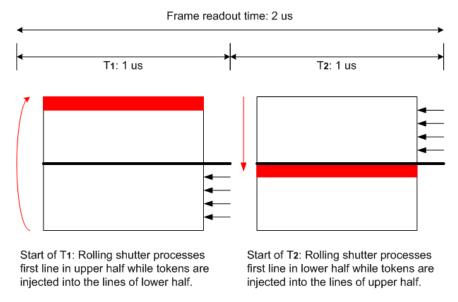

The other approach, required for continuous beam experiments like CBM, continues with rolling shutter operation, but the time for processing each row is reduced by taking advantage of 3D technology to embed a discriminator into each pixel. As the bottleneck of rolling shutter operation still is the fixed line processing time, the next measure to reduce frame readout time is parallellization by splitting into rolling shutter segments operated in parallel.

To arrive at a frame readout time as low as  $2\,\mu s$ , required for CBM, and two orders of magnitude lower than the so far achieved frame readout times, the recently submitted 3D integrated rolling shutter architecture was chosen as a starting point for continuing the 3D detector development in the direction necessary for this experiment. Already interfacing a binary discriminated rolling shutter circuit with excellent line processing time, an important part of this work would then be to prevent the digital readout from lagging behind this improved rolling shutter circuitry, and similar measures of parallellization were therefore proposed for the digital zero-suppression circuitry.

Instead of keeping the zero-suppression circuitry in the periphery, where it has to process lines one by one at the same speed as that of the rolling shutter, a new and pixelized structure is proposed, where the zero suppression is distributed to the individual pixels, and with the pixel rows extracting their hit information in parallel. To combine the sequential rolling shutter operation of a submatrix with a parallel search for hit patterns, each submatrix splits into two halves, where the rolling shutter injects hits in one half while the zero suppression circuitry extracts pattern information in the other half.

The proposed design has been verified through simulation. Compared to the zero suppression circuitry of MIMOSA26, the proposed new readout is superior with respect to scaling with a higher hit density, and it does not have the limitations of a maximum number of hits to extract from each row, only a maximum number of hits to extract from the entire matrix.

The thesis is organized into six chapters, with the last chapter containing a summary and an outlook:

Chapter 1 starts with a general description of different solid state detectors and their integration with electronics, like hybrid and monolithic, followed by a description of the MAPS architectures and the strategy chosen to provide these sensors with faster readout.

Chapter 2 gives a discussion on the state of the art of readout architectures for pixel detectors. It also gives a discussion on the readout electronics of the latest MAPS-based sensors and their requirements, especially focusing on the concepts of zero suppression and clusterisation.

Chapter 3 presents the MIMOSA26 pixel architecture, with its fast line processing and sparsified readout. It also presents the work that has been done with creating a test environment for verifying and validating the MIMOSA26 design prior to submission, and it presents the future perspectives of adapting this architecture to new experiments.

While chapter 3 presents the last achievements in 2D MAPS, chapter 4 introduces the new techniques of 3D integration. Vertical 3D integration offers the possibilities of using the best features from different processes, and to increase the amount of logic per pixel for providing functionalities previously available only in hybrid detectors. With 3D integration, it is also possible to split rolling-shutter operated MAPS into smaller segments that are operated in parallel, thus avoiding the rolling shutter from becoming a bottleneck for the time resolution.

The same chapter also introduces the three first 3D chips designed at IPHC. The first two chips are 3-tier designs with data driven readout or rolling shutter operated readout, respectively. The third chip, which is described in more detail, is a two-tier prototype chip, targeted for ILC, which is implemented with time stamping and delayed readout, and with an 8b10b readout interface for fast serial transmission.

In chapter 5, a conceptual design is presented for a 3D integrated detector that meets the requirements of CBM. In the proposed design, the zero-suppression techniques of the rolling-shutter based 2D MAPS is combined with the new features of the first 3D integrated circuits. Rolling-shutter operation is still utilized to save power, but the matrix is split into segments to meet the requirements of time resolution. The zero-suppression circuitry that was placed in the periphery of the 2D matrices has been distributed into the pixels. By splitting each submatrix at the digital tier into two halves that are read out at each their time interval, the sequential rolling-shutter operation of rows in the analog tier is combined with parallel token-injection in the rows of the digital tier.

Through segmentation and parallellization, the performance of the readout electronics is raised to a level where it is possible to arrive at  $2 \,\mu s$  frame readout time and thus meet the time resolution requirements of CBM.

## Chapter 1

## Solid state pixel detectors for high energy physics

High energy particle accelerators generate particle collisions at interaction rates up to 40 MHz, with around 1000 new particles coming out from each collision (Large Hadron Collider at CERN). As some of the rarest particles do not live more than a picosecond or less, they have to be indirectly identified by reconstructing their secondary vertices, indicated by the trajectories of their daughter particles. To be able to separate the daughter particles of the decay vertex from the background particles of the original collision vertex, it is necessary to detect these particles as close to the interaction point as possible, and with the highest possible spatial accuracy [3].

A pixel detector is composed of a planar two-dimensional array of particle sensing elements, where each individual element is called a pixel. Future high-energy projects, like the Compressed Baryonic Matter (CBM) experiment at FAIR and the International Linear Collider (ILC), have led to lots of efforts being put into developing solid state pixel detectors for particle trajectory reconstruction [4] [5] [6].

With CBM and ILC, it is intended to use pixel detectors for providing detection and identification of short lived hadrons, like for example D mesons. As such hadrons decay into daughter particles like kaons and pions long before they even reach the first detector element, they must be identified by reconstructing their decay vertices.

Although the daughter particles may travel through long distances during their lifetime, every interaction with matter results in scattering and thus a deviation from the original path. To be able to measure the original particle trajectories, the pixel sensors must therefore be located in the innermost layer of the detector, and

with a minimum of material budget for cooling and mechanical support <sup>1</sup>. And due to the very small radius of the innermost layer, these sensors must also be of very high spatial resolution.

#### 1.1 Operation principle of silicon detector

The silicon detector is a solid state crystal operated as a reverse biased p-n diode. The p-n diode is created by implanting acceptors and donors in the material, like boron and phosphorous. When the diode is reverse biased, only a small leakage current flows through the depletion zone in the p-n junction, but if an ionising particle traverses the sensor, it ionizes the medium and excites electrons from the valence band to the conduction band. Electron-hole-paires are thus created at a typical rate of 80 electron/hole pairs per micrometer, and electrons and holes are swept to each their side by the electrical field of the p-n junction.

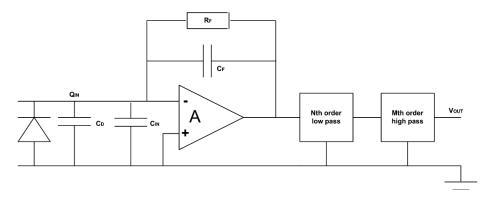

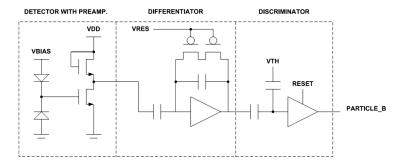

A block schematic of a general particle detection system is shown in Figure 1.1. A reverse-biased photosensitive p-n diode detects charged particles as electron-hole pairs are generated by ionizing particles inside the detector material. The generated electrons drift in the electric field towards the positively biased n-electrode of the detector. The total induced charge, Q, is integrated onto the feedback capacitor of a charge sensitive amplifier, thus giving rise to a voltage step of amplitude  $Q/C_f$  at the amplifier output.

Figure 1.1: Charge Sensitive Amplifier (CSA) with shaper. The detector sensing element is modeled as a reverse biased p-n diode with a parasitic capacitance  $C_D$ , while the shaper is modeled as a low pass filter followed by a high pass filter (RC-CR).

<sup>&</sup>lt;sup>1</sup>In detector development, material budget is a constraint on the detector thickness that is specified in percentage of radiation length.

The step signal from the charge sensitive amplifier is fed to a pulse shaping amplifier. The main purpose of pulse shaping is to optimize the signal-to-noise ratio (SNR) of the readout electronics and to provide a signal that is suitable for further signal processing. The shaper is especially beneficial for reducing the contribution of high and low frequency noise coming from the preamplifier and the detector. The shaper can be represented as a series connection of N first order low pass filters and M first order high pass filter.

Depending on the type of application, the stage following the pulse shaper could be a discriminator for event detection or a peak detect and hold circuit for pulse height measurement [7] - or a combination of both features, as in the n-XYTER chip that was used for high rate imaging neutron detection [8].

It can be shown that for a typical detector setup with charge sensitive amplifier and shaper, the equivalent noise charge increases more or less linearly with the detector capacitance and the preamplifier input capacitance [7]. The smallest possible detector capacitance and preamplifier input capacitance is therefore desired.

#### 1.2 Types of silicon detectors

Although solid state detectors have been known for more than 50 years, it was first in the beginning of the 1980s, with the search for short-lived particles in experimental physics, that their particle tracking capabilities were investigated.

The introduction of planar technology gave first rise to the one-dimensional devices, the strip detectors. The next devices in line were the two-dimensional planar devices, like double-sided strip detectors, and charge coupled devices (CCD). Another essential step came with the development of hybrid devices, where pixelized planar devices could be bump-bonded to pixelized readout ASICs [9], and the development of monolithic devices, where sensor and readout electronics are on the same device.

#### 1.2.1 Sensors of high-resistivity processes

#### Microstrips

With the strip detector, narrow strips of electrodes are implanted in parallell on a silicon substrate of high-purity bulk material. This configuration results in several long and narrow p-n diodes with the same properties as a single diode. By simply combining perpendicularly oriented strip detectors, or by implementing perpendicularly oriented strips on the sensor backside, a point-like p-n diode appears at every

strip intersection. In such case we get a two-dimensional position sensitive detector [10].

The strips of the silicon strip sensors are normally wire-bonded to their readout electronics. Example of such a sensor is the SCT microstrip sensor used in ATLAS [11]. In the research and development phase of the ATLAS detector, different kinds of options for strip detectors were prototyped and evaluated with respect to constraints like radiation hardness and manufacturability. Double-sided sensors were prototyped, and also sensors with  $n^+$  electrodes in an n-type substrate, but they were rejected at an early stage in favour of single-sided sensors with  $n^+$  electrodes in a p-doped substrate (largely because of system difficulties with readout at high voltage) [12].

#### Planar pixel sensors

The planar pixel sensor is a planar array of p-n or p-i-n diodes, whose electrodes are coupled to their pixelized readout electronics through bump-bonding. Their accompanying readout chips bring separate logic to every pixel cell, and such detectors are called hybrid detectors.

Compared to microstrip detectors, the segmentation of the electrodes reduces the capacitance and the leakage current per channel, thus improving the SNR. An example of such a sensor is the pixel sensor used in the innermost layer of the ATLAS particle tracking system [13].

The pixel sensors used in ATLAS collect signals on  $n^+$ -electrodes - the n-in-n sensor, where the p-n junction is fabricated on the backside [14]. As the type of silicon wafer inverts into p-type after irradiation, the n-in-n sensor becomes an n-in-p sensor, where the p-n junction is moved to the front side. An advantage of the n-in-p sensor is thus the possibility of continuing to operate the sensor in partial depletion prior to irradiation. The charge collection efficiency is also enhanced by collecting electrons in the  $n^+$ -electrode, instead of holes in a  $p^+$ -electrode, which are more prone to trapping due to their lower mobility.

#### DEPFET

The detector concept of DEPFET (DEpleted P-channel Field Effect Transistor) was developed in the late eighties [15]. The principle of DEPFET is to use an  $n^+$  doping implant - and appropriate biasing of bulk, source, drain and a  $p^+$  rear electrode - to establish a local potential minimum right underneath a p-channel field effect transistor. While holes created in the bulk material are drifting towards the rear electrode, electrons are collected in the local potential minimum underneath the

channel. The potential minimum will act as an internal gate for the transistor, and the electrons collected are thereby modulating the transistor current.

Due to small internal gate capacitance, absence of external connections to the first amplification stage, and a fully depleted bulk, an excellent SNR can be obtained with DEPFET devices. Pixel detectors based on DEPFET are to be installed in the vertex detector of the BELLE-2 experiment [16] and are also among the candidates for equipping the vertex detectors of ILC [17][18].

#### 3D

In the late nineties, a new architecture for silicon detectors was proposed, called the 3D detector [19]. In this detector, the electrodes are penetrating through the entire substrate. Since the width of the depletion region depends on the spacing between the electrodes, and not any more on the wafer thickness, it is possible to obtain low depletion voltage and fast charge collection times.

In heavily irradiated planar detectors, the increase of the depletion voltage and the reduction of the charge carrier mean drift length due to trapping effects are a major issue. In 3D detectors, a direct consequence of the low depletion voltage and short distance between electrodes is an increase of the radiation tolerance [20].

Unlike other detectors, which have a substantial dead area along their edges, 3D detectors have active edges, which are formed from electrodes in the third dimension, perpendicular to the top and bottom surfaces, with full sensitivity to within a micron of the physical border [21].

3D sensors with electrodes penetrating the entire substrate and with active edge were successfully tested with the ATLAS pixel readout electronics. This technology gives the possibility of constructing sensors with depletion voltages an order of magnitude lower than the depletion voltages of their corresponding planar sensors, and sensitivity to within a few  $\mu$ m of the physical edges. A drawback of 3D detectors is, however, the rather long and complex fabrication process, as methods of silicon micro-machining must be used. This could lead to the unfeasibility of mass production of these detectors [20]. Another problem is that the 3D electrodes are parallell to the particle tracks at normal incidence, and this leads to considerable signal loss in the cases where particles pass through the inside of electrodes, reducing the detection efficiency [22].

#### 1.2.2 Sensors manufactured in low-resistivity processes

Since both detector and readout electronics can be based on silicon, it is in principle possible to build sensor and electronics into the same wafer, with readout electronics

on the surface and the bulk material as the sensitive volume. Without wire bonding or bump bonding between sensor and electronics wafers, the total input capacitance is strongly reduced, and in this way excellent noise figures obtained - while at the same time avoiding the costly hybridization processes. And when no more limited by the minimum dimensions needed for bump bonding (see for example [23] and [24]), much smaller pixels can also be implemented.

However, while commercial CMOS processes for electronics need low resistivity substrates to fabricate small transistors, silicon detectors need high-resistivity substrate for depleting their active volume. A monolithic pixel detector with non standard CMOS on high-resistivity bulk material was successfully prototyped already in the early nineties [25], but no large scale detectors have been developed on this approach, due to the use of nonstandard processing technologies.

If standard CMOS processes are to be used for manufacturing monolithic pixel detectors, there are currently two different options. The first one is CMOS with charge collection in the epitaxial layer<sup>2</sup> (MAPS), and the second one is silicon on insulator (SOI), where the support wafer underneath the isolating oxide serves as detector layer for the amplification and readout electronics located on top.

The principle of using the epitaxial layer as active volume is the following:

Since the impurity level of the epi layer - and therefore also its resistivity - is lower than the impurity level of the bulk material, alignment of the different fermi levels in the two layers lead to a potential barrier being created at the boundary between the epi and the bulk material. When electron-hole paires are generated by impinging particles in the epitaxial layer, the generated holes will therefore quickly disappear into the lower-potential substrate, while the generated electrons remain within the higher-potential epitaxial volume.

In pixel detectors based on CCD, the epitaxial volume is patterned into potential wells where the electrons are stored until being transferred out of the pixel matrix with a three-phase clock. In pixel detectors based on MAPS, the electrons diffuse thermally around until reaching the charge collecting diode of the pixel.

#### Charge coupled devices (CCD)

The operating principle of charge coupled devices is to create an array of gates where potential wells for trapping electrons are formed underneath them. A basic CCD cell is comprised of a photogate to provide the potential well and two isolation gates to provide isolation to the neighbouring wells. When the content of the potential

<sup>&</sup>lt;sup>2</sup>An epitaxial layer is a thin single crystal layer grown on top of an underlying crystal, with the latter providing the desired lattice structure. A variety of methods can be used to provide the appropriate atoms to the surface of the growing layer, like liquid-phase epitaxy or molecular beam epitaxy.

wells is to be read out, a three-phase-clock is used to shift the potential wells from one cell to another. With this behavior, the rows of accumulated charges may be moved one by one to the periphery of the chip, where they are converted to voltages by a sense amplifier.

The active area of a charge coupled device is in the epitaxial layer of the chip, normally of around 20 µm depth. Since most of the chip volume does not contribute to the electrical signal, CCD circuits for particle trajectory detection can be thinned down without losing signal to meet the requirements of material budget [26].

A main disadvantage of using CCD circuits in particle physics experiments is their long readout times. The charge has to be shifted serially under one gate to the next one, across the rows and columns of pixels, and due to the slow three phase clock and the large number of rows, the readout time of the whole detector may reach hundreds of milliseconds. For example, with the VXD3 CCD chips installed in the SLD detector, the readout time was 200 ms [27]. However, as part of the R&D for ILC, CCD prototype chips aiming at a time resolution as low as 50 µs have been developed. The prototypes have been based on two parallell approaches. With the first approach, sequential readout has been replaced with column parallell readout. With the second approach, each pixel cell is equipped with 20 different charge storage elements, with each element collecting the charge deposited under the pixel photogate at each their 50 µs time interval - followed by delayed readout between the 1 ms bunch trains [28].

Poor radiation hardness is another weak point of CCD devices, as charge trapping occurs in numerous bulk transfers, resulting in the deterioriation of the charge transfer efficiency. Even very small charge transfer inefficiency can lead to significant losses and signal smearing, and the possible number of rows of a CCD matrix is thus limited due to post-irradiation effects [29].

#### Monolithic Active Pixel Sensors (MAPS)

With monolithic active pixel sensors, the generated electrons released by an ionising particle are kept in the epitaxial layer by potential wells at the boundary until they reach an n-well collection diode by thermal diffusion. Due to the thin active volume, with typical epitaxial depths from 10 to 20  $\mu$ m, the total signal charge of MAPS is very small ( $< 1000e^-$ ) compared to fully depleted high-resistivity devices, and the charge collection time is in the order of 100 ns due to the slow thermal diffusion transport in the epi potential well. Development of very low noise electronics is therefore required for this kind of detector.

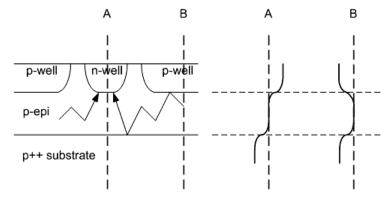

The operating principle of a monolithic active pixel sensor (MAPS) is shown in Figure 1.2. The n-well acts as charge collecting diode, while the p-wells contain

the transistors required for preamplification. In cross section B, there is a positive contact potential difference on each side that prevents the generated charge from escaping the epi volume. In cross section B, the lightly doped p-epi sees two negative contact potentials, one on the bottom and another one on top. The negative contact potentials are due to the much larger doping concentration of both the p++ substrate on bottom and the p-well on top. Electrons diffusing around in the p-epi are therefore prevented from escaping the epi volume. In cross section A, the p-epi sees a positive contact potential on top and a negative contact potential on bottom. The positive contact potential is due to the p-n junction between the epi and the n-well, and eletrons diffusing into this depletion region are swept across the electrical field and collected by the n-well.

Figure 1.2: MAPS operation principle. A cross sectional view showing the charge diffusion to the left, and with the corresponding potential distribution of the two cross sections A and B shown to the right.

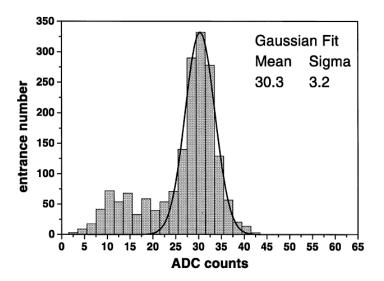

Figure 1.3 shows the response of a MAPS structure to X-ray photons from a  $^{55}Fe$ -source at energies of 5.9 keV. The MAPS structure is depleted only directly under the n-well collection diode where full charge collection is obtained, and the peak corresponds to photons absorbed in the small depleted region of the n-well. However, the main part of the spectrum corresponds to the absorption of photons in the undepleted part of the epitaxial layer, where the charge collection is incomplete due to recombination of the diffusing electrons and holes [1].

In principle, it is also possible for electrons generated in the bulk to diffuse to the boundary and become captured in the epitaxial potential, contributing to the signal. But since the life time of charge carriers inside a heavily doped  $p^{++}$  substrate is so short, this contribution is in practice negligible, and the active volume is thus limited to the epi layer. With an epi layer of thickness in the order of

Figure 1.3: Distribution of collected charge for 5.9 keV photons [1].

$10\,\mu m$  one can expect to collect close to thousand electrons created by a minimum ionising particle. However, a moderately doped substrate without epitaxial layer has also been tried with excellent minimum ionizing particle tracking performance. These results open a much larger choice of possible CMOS processes in the future, which are important due to the observed tendencies of either removing or drastically reducing the epi thickness in very deep submicron technologies. Still, the absence of electrons reflected by the epitaxial/substrate barrier and the deeper origin of the substrate electrons results in a wider and less peaked charge distribution of clusters. With the MIMOSA-4, manufactured with  $20\,\mu m$  pitch in non-epitaxial process, a single-point resolution of approximately  $4\,\mu m$  was observed in the beam tests, compared to approximately  $1.5\,\mu m$  for its epitaxial-manufactured counterparts [30].

Normal MAPS chips cannot utilise both the n- and p-types of transistors at the same substrate, since competing n-wells required for p-type transistors would draw charges away from the charge collecting diode. All parts of electronics that require both kinds of transistors must therefore be replaced with structures that only utilise n-type transistors - or they have to be moved to the periphery of the matrix. Pixel cells that follow the traditional configuration with CSA, shaper, PDH and discriminator are therefore difficult to implement. CSA and shaper are instead replaced with a low gain amplifier and source follower, with the corresponding requirements for low noise design.

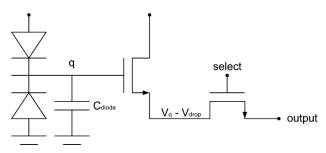

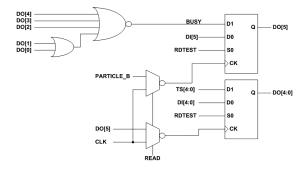

Figure 1.4 shows a block diagram of a basic MAPS pixel cell, each being composed of three transistors - a self biasing diode  $^3$ , a source follower and a pass transistor for connecting to pixel cell to the column line. As charge is collected on the diode, a voltage corresponding to  $v_q = \frac{q}{C_{diode}}$ , is generated, and with  $C_{diode}$  being the diode capacitance. All the amplification circuitry of the pixel cell can be switched off during charge acquisition, with the purpose of saving power. This circuitry is instead only switched on for the small period when the row of this pixel is processed for readout.

Figure 1.4: Block schematic of a basic MAPS pixel cell.

The current passing through the self biasing forward diode is very low, and hence, its  $1/g_m$  impedance<sup>4</sup> seen from the charge collection electrode is very large. A time constant in the order of seconds before returning to the DC operating point is therefore obtained <sup>5</sup>.

The amplitudes of the pixel signals are in the millivolt range, which is within the voltage deviations caused by process variations. It is therefore necessary to individually correct the pixel signals for variations in offset through correlated double sampling. With correlated double sampling, the pixel is sampled twice: First, the pixel signal is sampled and stored onto a capacitor, then a global reference value is sampled onboard the pixel cell and stored on another capacitor. The potential difference between the two signals can then be A/D converted or discriminated.

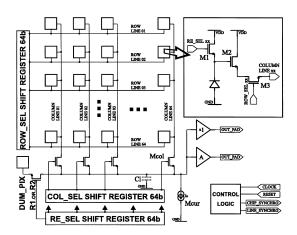

At IPHC, the MIMOSA (Minimum Ionizing Particle MOS Active Pixel Sensor) series of MAPS based pixel sensors have been developed for several years. Figure 1.5 shows a block diagram of a basic MIMOSA matrix, where a column shift register

<sup>&</sup>lt;sup>3</sup>An alternative configuration is to replace the self-biasing diode with a switch that is used to reset the pixel to a reference value after each read cycle.

<sup>&</sup>lt;sup>4</sup>The transconductance of a transistor,  $g_m$ , is its small-signal current amplification,  $\frac{d_{i_{out}}}{d_{v_{in}}}$

<sup>&</sup>lt;sup>5</sup>Such a long time constant could in some cases be considered a source of possible pill-cup problems. However, as the charge signal is within the order of millivolts, there has to be a very high number of hits before the pile-up voltage exceeds the valid range

and a row shift register is used to select individual pixels for readout. The logic for controlling the readout is located in the peripheral area of the active pixel matrix.

Figure 1.5: Simplified block diagram of a single array of a MIMOSA circuit [31].

As a direct consequence of one of their basic operation principles, CMOS sensors offer very high spatial resolution. Since the charges liberated when a minimum ionizing particle traverses the epitaxial layers diffuse thermally and get distributed over several pixels, the resulting charge sharing allows to reconstruct hit positions with a spatial resolution much better than the binary resolution associated with the pixel pitch (which is the pixel pitch divided by the square root of twelve).

Since only the epitaxial layer contributes to the charge collection, the pixel detectors based on MAPS can similarly to CCD be thinned down to improve material budget, without losing signal. Several MAPS-based MIMOSA chips, like MIMOSA18[32] and MIMOSA26, have been thinned down to  $50\,\mu\mathrm{m}$  using commercially available post-processing techniques. Such sensors are therefore particularly suitable for low material budget operation in the vertex region of a detector.

#### Deep n-well MAPS

A drawback of using the MAPS detectors is the fact that only NMOS transistors can be used in the active area of the pixel matrix. Deep n-well MAPS (DNW-MAPS), which is another emerging MAPS-based technology, overcomes this problem by using a buried n-type layer as the charge collection diode. If the deep n-well electrode is made sufficiently large, smaller and shallower n-wells can be allowed in the vicinity

of the larger and deeper charge collecting electrode with rather moderate, but still significant, degradation of the charge collection efficiency.

The availability of both transistors inside each individual pixel cell enables including more sophisticated functions inside the pixel cells, thus making the implementation of data sparsification and time stamping a viable solution. Examples of such designs are the SDR0 prototype chip (25  $\mu$ m pitch) for the ILC vertex detector, based on timestamping and delayed readout [33], and the APSEL3D and APSEL4D prototype chips (50  $\mu$ m pitch) for the KEK Super B-Factory, based on data-driven, continuous readout [34].

Although improving pixel functionality, the deep n-well designs lag behind in terms of detection efficiency. Beam test results of APSEL4D show that the detection efficiency saturates at around 92% [35], compared to detection efficiencies above 99.5% in standard MAPS chips (see for example [36]).

#### Depleted epitaxial MAPS

Due to demands from industry on improving the CMOS photo-detection performance, processes with resistivity high enough to fully or partly deplete the epitaxial layer have recently become available. The charge collection mechanism of MAPS sensors implemented in this technology will then be drift instead of diffusion.

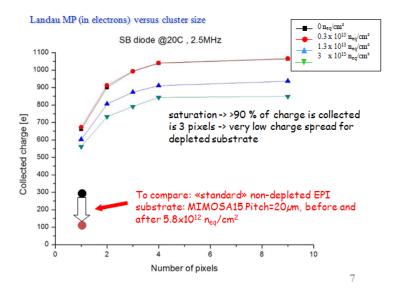

The fully or partly depleted epitaxial layer is available in the XFAB-0.6 process, and a prototype chip in this process, MIMOSA25, has already demonstrated good results. The benefits of having a depleted epitaxial layer is that the released electrons will immediately drift towards their collecting electrode, instead of slowly diffusing like they do in the standard MAPS chips. Dependent on the radius of the depletion region around the charge collection diode, the charge collection time can be reduced by an order of magnitude or more, improving the radiation tolerance.

With standard MAPS, the tolerable amount of non-ionizing radiation is around  $10^{12} \ neq/cm^2$ . MIMOSA25 (20 µm pitch and 15 µm deep epitaxial layer) has been tested in beam with excellent results up to  $3 \cdot 10^{13} \ neq/cm^2$ , which has been considered promising for extending the radiation tolerance up to  $10^{14} \ neq/cm^2$  [37].

Since the electrons are directly drifting towards their nearest collection electrode, instead of diffusing in the substrate, the cluster multiplicity of the hit signal becomes much less than in standard MAPS diodes (clusters are further described in Chapter 2). This concentration of charge in fewer pixels (90% of collected charge in 3 pixels) increases the SNR, and makes it therefore possible to increase the discrimator threshold to suppress noisy pixels (especially important after irradiation) without significant loss in hit detection efficiency. Measurements from MIMOSA25 show that the collected charge in the seed pixel is at least twice larger for the sensor with

depleted layer than for an undepleted one, translating into an SNR of around 60 before irradiation (and remaining above 30 after being exposed to  $3 \cdot 10^{13} neq/cm^2$ ).

While nondepleted MAPS typically have fake hit rates below  $10^{-4}$  for detection efficiencies above 99.5% [38], the doubled SNR of depleted MAPS a makes it possible to increase the threshold and reduce the fake hits rates by orders of magnitude while remaining at the same excellent detection efficiency.

#### SOI

Silicon On Insulator, SOI, is a process that has been used for many years in commercial electronics production. One of the advantages of the process is its immunity to latchup, as the individual transistors are isolated from each other, avoiding the parasitic bipolar structures.

The idea of utilizing SOI in a detector is to use the support wafer under the buried oxide as a fully depleted high-resistivity detector material. With this technique, the entire underlying substrate contributes to the charge collection, and one can therefore obtain a much larger active volume than that of MAPS, where only the thin epitaxial layer contributes to the charge collection (and with epitaxial thicknesses varying from process to process, like the  $7\,\mu m$  epitaxial depth of MIMOSA8, fabricated in TSMC-0.25, compared to the 14-20  $\mu m$  epitaxial depth of the later chips fabricated in AMSC35 [39]).

SOI also gives the full freedom of implementing both PMOS and NMOS transistors above the buried oxide layer, with the entire support wafer functioning as a fully sensitive detector without dead area.

SOI detectors are formed by connecting a top wafer of low resistivity and a bottom wafer of high resistivity through a silicon oxide bond. Thus, a buried oxide is formed between the wafers, and after bonding the top wafer is thinned to only a few  $\mu$ m. Later, vias can be etched right through the buried oxide, and in this way detector and readout electronics are connected together.

Although SOI has many advantages compared to MAPS, it also introduces disadvantages like the back gate effect of the underlying support wafer [40]. Due to charge trapping in the buried oxide, which both affect the threshold voltage in the transistors, the detectors based on SOI are also highly sensitive to ionizing radiation. Analog designs in SOI technology are also difficult due to self-heating effects, poor transistor matching and poor transistor bulk contact quality compared to bulk counterparts [41].

#### 1.3 Pixel detectors for CBM

This work focuses on the development of sparsified readout architectures for MAPS-based pixel sensors that ultimately should be targeted for the Micro Vertex Detector (MVD) of the CBM (Compressed Baryonic Matter) experiment. The technical challenge of building pixel architectures for this experiment is to design architectures capable of meeting at the same time very strict requirements on both spatial resolution, time resolution and radiation hardness.

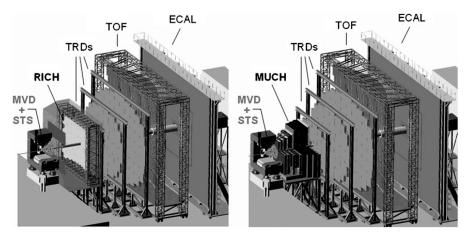

The CBM detector is composed of the Micro Vertex Detector (MVD), a Silicon Tracking System (STS), a Ring Imaging Cherenkov detector (RICH), replaced with a Muon Chamber (MUCH) when performing muon measurements, a Transition Radiation Detector (TRD), a Time Of Flight spectrometer (TOF), and an elecomagnetic calorimeter (ECAL) [42]. Figure 1.6 shows the detector setup.

Figure 1.6: CBM detector setup. Left: Configuration for electrons. Right: Configuration for muon measurements [42].

At the energies obtained during the CBM experiment, charmed mesons are produced close to threshold. Consequently, the multiplicity of these particles is extremely small, with about  $2 \cdot 10^{-4}~D_0$  mesons per central Au+Au collision at 25 AGeV. These signals must be measured via the decay into charged hadrons, and to separate these daughter particles from a background of several hundreds of other charged particles created in the primary collision, it is necessary to reconstruct the displaced decay vertices with a spatial resolution of 50  $\mu$ m or better.

The heart of the CBM detector is the STS, composed of silicon strip detectors and responsible for reconstructing the particle tracks. To refine the spatial resolution of

the particle tracks to the level required for the secondary vertex reconstruction of charmed mesons, the STS is preceded by two or three detector stations of MAPS-based pixel detectors, which make up the Micro Vertex Detector (MVD).

#### 1.3.1 Requirements

## Time resolution, spatial resolution, radiation hardness, and material budget

The MVD is required to collect data for the open charm physics programme of CBM, and we intend to run the experiment at  $10^6$  collisions/second. For such a collision rate, it can be shown that the required time resolution for the first MVD detector station, 5 cm away from the target, is  $2 \,\mu s$ , while the required spatial resolution becomes  $5 \,\mu m$ . The detector has to withstand a non-ionizing radiation of  $2 \cdot 10^{14} neq/cm^2$  and an ionizing radiation of approximately 34 MRad, and the material budget of one detector station is just a few 0.1 % of the radiation length.

Currently there is no pixel detector that is able to meet all these requirements at the same time. To obtain a detector that has the superior spatial resolution and material budget of MAPS while at the same time providing the fast readout rate and high radiation tolerance of hybrid detectors, new technologies must be explored.

#### Data flow

Increasing time resolution also means increasing amounts of raw data to transfer. With  $2\,\mu s$  frame readout time, and a typical pixel matrix size of 500,000 binary-output pixels, the raw data rate of each sensor becomes 250 Gbit/sec. With such an enormous amount of data to read, it will, even with fast a differential series transmission protocol, be difficult to bond the sufficient amount of wires to each sensor. The large amount of wires will also make it difficult to meet the requirements of material budget.

To keep the number of serial data links from the sensors at an acceptable level, and to avoid overloading the data acquisition system, it is necessary to develop some kind of online data reduction or data compression within the sensors.

#### 1.3.2 Limitations and advantages of standard pixel architectures

Where bump-bonded hybrid detectors provide excellent time resolution and radiation hardness, they do not provide the required spatial resolution and material

budget<sup>6</sup>. MAPS based detectors, on the other side, have sufficient spatial resolution and material budget, but they do not meet the requirements on time resolution and radiation hardness<sup>7</sup>.

#### 1.3.3 Proposed solutions

#### **Technological**

For MAPS pixels, high spatial resolution and fast readout are conflicting requirement, since high spatial resolution requires small pixels while a fast readout architecture requires more logic to fit into each pixel. And as we are limited to NMOS transistors, the pixel functionalities must either be suboptimally implemented with only one type of transistors, or the pixel signal must be routed to the periphery for sequential or column parallell processing. However, 3D integration of electronics is an emerging technology providing new degrees of freedom to overcome the limitations in standard MAPS:

- Vertically integrating several wafers of pixelized chips, the detector part and

the readout electronics can be separated. The limitation of NMOS-only pixels therefore no more apply. And with proper partitioning, one can design

3D stacks where different functionalities are implemented in each their most

optimal technologies.

- As the available pixel area is multiplied with the number of stacked wafers, 3D integration allows pixelized readout architectures with progressively more logic per pixel, and with features similar to the readout ASICs of hybrid pixel detectors.

- Distributing the previously peripheral readout circuitry into the individual pixels, the readout electronics can be put on top of the pixel matrix, instead of being located in the periphery where it contributes to an inactive dead area.

And by replacing standard MAPS with depleted epitaxial MAPS, the charge collection time may be reduced by an order of magnitude, strongly improving the radiation hardness of the sensing element. The next step towards improving the time

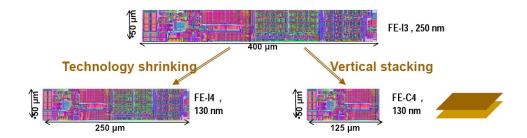

<sup>&</sup>lt;sup>6</sup>Like the ATLAS FE-I3 readout ASIC, with 25 ns timestamp resolution, and with modules proven to withstand  $10^{15}neq/cm^2$ , but with pixel pitch of 400 μm x 50 μm and interfacing a planar sensor of 250 μm thickness, [43] [13]

<sup>&</sup>lt;sup>7</sup>Like the MIMOSA26, that has pixel pitch of  $18.4 \,\mu\text{m}$  and has been thinned down to  $50 \,\mu\text{m}$ , but with time resolution of  $100 \,\mu\text{s}$  and a standard epitaxial substrate where charge collection efficiency is strongly degraded after  $5 \cdot 10^{12} neq/cm^2$  [44]

resolution and radiation performance of monolithic pixel detectors could therefore be to develop 3D integrated pixel detectors, with depleted epitaxial MAPS serving as the sensor layer.

#### Architectural

In the first prototypes of the MAPS based pixel sensors, the MIMOSA chips, each individual pixel was externally addressed individually and the pixel matrix read out in its entirety [1]. This means that even for detecting a few hits, the entire matrix had to be read out, pixel by pixel. Since then, there has been an evolution in processing capabilities, where sequential processing of pixels has been replaced by parallell processing at row level (rolling shutter operation), and embedded correlated double sampling and data reduction microcircuits have been built into the sensor.

The parallell processing of rows means, however, that the frame readout time is limited by the number of rows and the time to process each row. The frame readout time can be reduced by reducing the number of rows that are processed by the rolling shutter. However, as material budget limits the number of overlapping sensor chips to two, the minimum height of the pixel matrix is equal to the height of the readout electronics in the periphery, and it has been shown in [39] that the minimum frame readout time achievable with standard MAPS is in the order of  $10 \,\mu s$ .

The ultimate goal should therefore be to replace the sequential processing of lines with an architecture where each pixel is able to detect that is has been hit and initiate its own sparsified readout.

Even with sparsified readout, the amounts of data to transfer per sensor will be on the order of gigabits per second, and fast serial transmission interfaces must be developed. With differential signaling and 8b10b encoding, where both clock, control and data are embedded into the same data stream, the data rate is increased while at the same time the number of wires to bond is reduced. Fewer wires facilitates bonding and gives lower material budget.

#### Means of development

Towards fulfilling the requirements of pixel detectors for CBM, different applications and experiments with less demanding requirements are targeted for the current MAPS based sensor designs. The requirements for three such applications are depicted in Table 1.1.

EUDET JRA-1 stands for a beam telescope developed as part of the EUDET project for detector research and development towards the international linear col-

lider [45]. While the STAR experiment (Solenoid Tracker at RHIC) is an experiment built at the RHIC collider at Brookhaven with the purpose of studying the formation and characteristics of the Quark-Gluon-Plasma (QGP), a state of matter assumed to exist at sufficiently high energy densities [46].

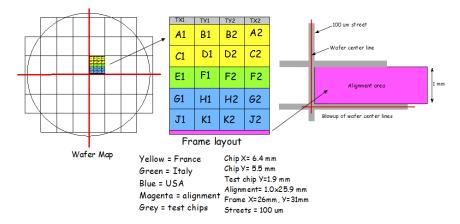

The detector development is done step by step, starting with the most primitive and low bandwidth CMOS pixel sensors while making progress towards ever more complex and sophisticated detectors. The first step is to integrate data sparsification and serialized readout in a standard MAPS pixel matrix. Such a readout ASIC (MIMOSA26) was developed for the EUDET beam telescope. The second step is to construct an architecture that takes advantage of 3D technology to provide more intelligent pixels and to implement 8b10b encoding for fully taking advantage of serialization. Such a readout ASIC was developed in a technology exploration prototype for ILC.

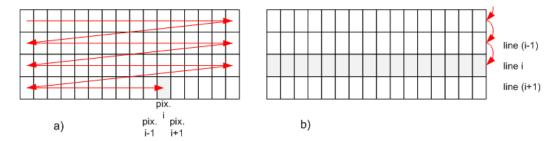

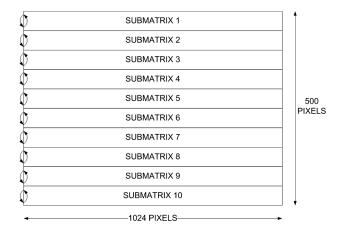

The MIMOSA26 architecture was based on reading out the pixel matrix row by row and performing zero suppression by encoding groups of neighbouring hit pixels in each row. The parallell processing at row level, and the embedded zero suppression, has lead to both smaller frame readout time and smaller amount of data to read out per frame, ending at processing speed of 576 rows/100  $\mu$ s. By increasing the clock frequency to 110 MHz, the frame readout time has been reduced further down to 83  $\mu$ s.

However, this architecture is hardly scalable with the time resolution requirements of CBM. If the 576 row wide chip was replaced with two 256 row wide structures operating back to back, the readout time could be reduced to 42  $\mu$ s. And by increasing the pixel pitch from 18.4  $\mu$ m to 23.0  $\mu$ m for the same fixed matrix size, one intends to reach 35  $\mu$ s. Then finally by changing process technology from 0.35  $\mu$ m to 0.18  $\mu$ m and by using elongated pixels at one side of a detector station, one can come close to 10  $\mu$ s frame readout time. But at some point, architectural

Table 1.1: Expected hit densities for the sensors of EUDET, STAR and inner layer of ILC. For STAR, two different hit densities have been modeled, each leading to two different sets of requirements.

| Requirements            | EUDET JRA-1 | STAR 200            | STAR 500            | ILC        |

|-------------------------|-------------|---------------------|---------------------|------------|

| Hits per chip per frame | 100         | 200                 | 500                 | 300        |

| Pixel columns           | 1152        | 1024                | 1024                | 1024       |

| Pixel rows              | 576         | 1088                | 1088                | 256        |

| Hits per row (line)     | 2           | 3                   | 4                   | 6          |

| ADC bits                | 1           | 1                   | 1                   | 1          |

| Frame readout time      | 100 μs      | $200\mu \mathrm{s}$ | $200\mu \mathrm{s}$ | $25~\mu s$ |

limitations make it too difficult to further reduce the frame readout time, and 3D technologies must be utilized for taking the frame readout time to even smaller values.

At IPHC, three different 3D architectures have so far been developed:

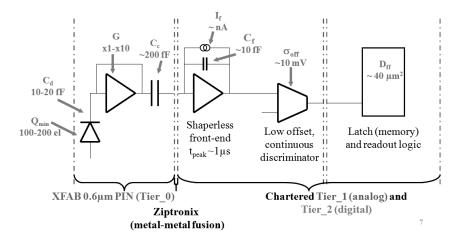

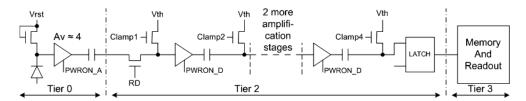

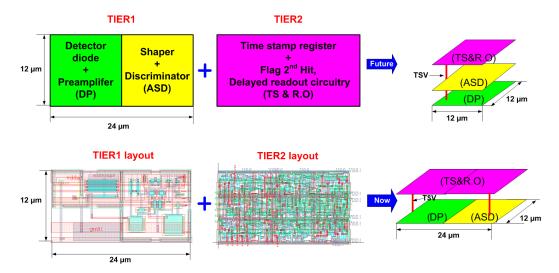

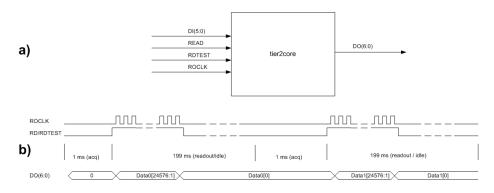

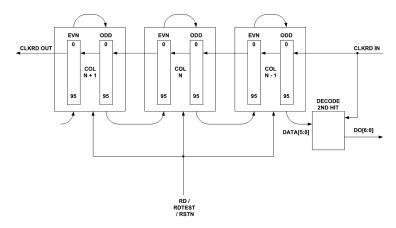

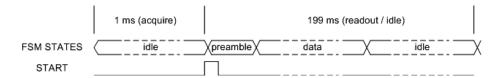

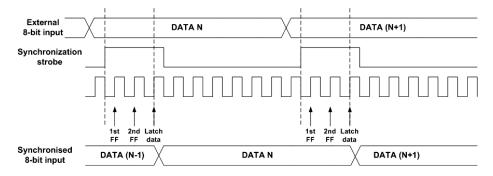

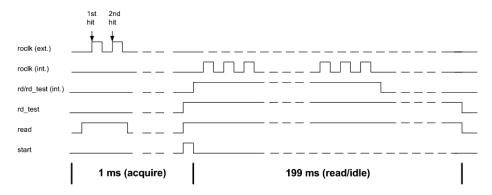

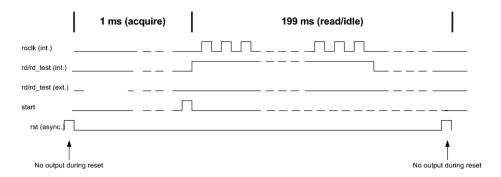

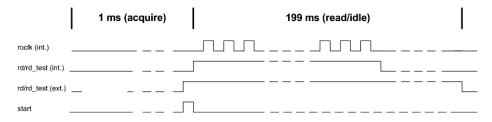

The first architecture resembles that of a strip detector, and therefore with a usability limited to applications with low multiplicity - like a beam telescope. In the second architecture, targeted for ILC, individual particles trigger the latching of timestamp information in the individual pixels, and the timestamp information is read out of the chip in the 199 ms dead time between the 1 ms bunch trains of ILC. In the third architecture, a rolling shutter operated pixel matrix has been 3D integrated with the purpose of providing a binary discriminator inside every pixel cell - instead of the shared column-level discrimators used in previous rolling shutter chips. Removing the shared discriminator improves the performance and may reduce the row processing time from 160 ns in MIMOSA26 down to 40-80 ns. However, it requires a new kind of readout architecture to interface the pixelized matrix of discriminator outputs.

For a high luminosity experiment like CBM, where continuous readout is required as there is no dead time between bunch trains, neither the first nor the second architecture are suitable. However, the third architecture, which results from a cooperation between IRFU in Saclay and IPHC in Strasbourg, has become the starting point for a conceptual design targeted at CBM.

## Chapter 2

## Read out architectures for particle trajectory detectors

In the previous chapter, different types of pixel detectors were presented. And it was concluded that MAPS currently is the only kind of technology that is able to meet the CBM and ILC requirements of both high spatial resolution and low material budget - although technological and architectural improvements are necessary to meet the requirements on time resolution and radiation hardness.

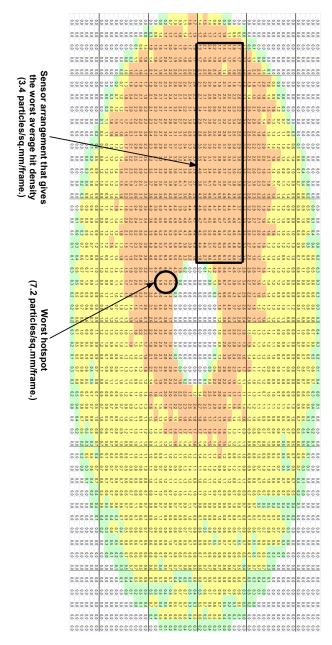

The frame readout time is the time required to electronically read out all the samples of a pixel matrix. The readout rate requirements are ideally governed by the physical interaction rate, usually the rate of hard collisions in the experiment. However, in many detectors, like with the ILC, the intense beamstrahlung makes it necessary to read out the accumulated charges at a much higher rate than the actual interaction rate - otherwise, the interesting physics is drowned in all the background. The same case applies for the CBM experiment, where heavy ions collide with a target representing  $\approx 1\%$  interaction length, and where the largest hotspots are due to delta electrons and not due to actual heavy ion collisions.

With CBM, a frame readout time of typically  $2\,\mu s$  is desired for keeping the occupancy at an acceptable level. Due to the reduced frame readout times required for ILC and CBM, and the correspondingly increased raw data rates, it is necessary to develop faster, sparsified readout architectures for MAPS.

In this chapter, we start by presenting clusterization as a way of modeling hits due to particles, and how these clusters appear in a MAPS based pixel detector with binary discrimination. Then different kinds of sparsified readout architectures are presented and their compliance with MAPS is discussed.

#### 2.1 Physical model - clusters

The purpose of using pixel detectors in projects like ATLAS, ILC, and CBM, is to measure the trajectory of minimum ionising particles coming out from the interaction point of the experiment. If the pixel detectors are built up layer by layer around the interaction point, the tracks of the particles can be reconstructed by making a fit of the different impacts in the pixel matrix where the particles have passed. As the detector is supplied with a magnet to provide magnetic deflection of the particles, it is even possible to obtain the momentum of the particles using this approach.

As long as the charge collection electrodes are able to collect a number of electrons that is significantly above the equivalent noise charge (ENC) of a pixel, a hit may be detected. With MAPS sensors, the most probable value of the SNR for a minimum ionising particle ranges from 15 to 30, depending on the pixel size. Detection efficiencies exceeding 99.5 percent have been demonstrated even in the case of a pitch as large as  $40 \,\mu m$  [36].

With the simplest pixel architecture, a single bit is used to indicate if a pixel cell has been hit. We may therefore model the pixel detector as a binary matrix where each element in the matrix has a zero value if no particle has passed through it and a binary one value if a particle has passed through it.

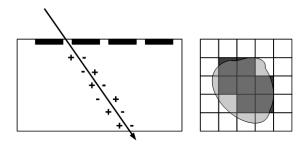

In Figure 2.1, we see a particle passing diagonally through the substrate of a planar pixel detector. For a planar and fully depleted silicon device, with an active volume that typically could be  $300\,\mu\mathrm{m}$  thick, we could assume that the energy deposited by the particle was roughly identical to the mean energy given by the Bethe-Bloch formula, and that the number of generated electrons would correspond roughly to one electron per 3.6 eV of deposited energy. We could also assume that the induced charges would drift vertically in the electric field and become captured by the pads located above.

The number of pixels affected by an impinging particle depends on the pitch of the pixel cell. If the pads are small, one might assume that the charge of a particle will spread on a number of neighbouring pixels - how many is dependent on the pixel pitch. But even if the pads are relatively large, there will always be cases where the charge of a particle is spread onto two neighbouring pixels.

We can therefore consider the binary matrix to be an ocean of zeroes, but with with islands composed of neighbouring ones at the locations where there has been a hit by a particle. These islands will be of varying size and they are called clusters. In addition to the clusters, there will also be randomly distributed ones due to noisy pixels.

With pixel sensors based on MAPS, the active volume consists of a maximally

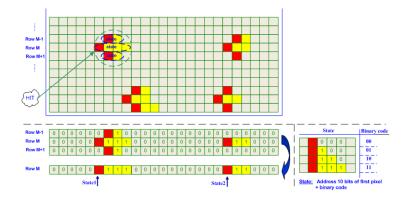

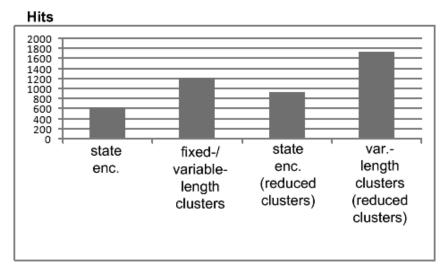

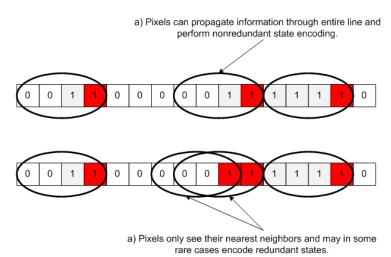

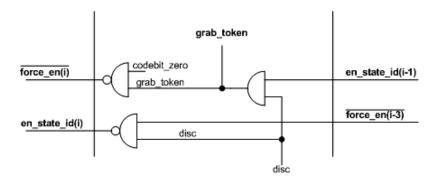

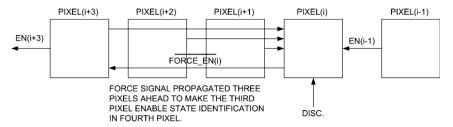

Figure 2.1: Particle passing through substrate of a planar pixel sensor. Side view to the left, showing the particle passing below different pads, and top view to the right, showing the clusterised manifestation in the pixel matrix. We also notice that one of the pixels in the cluster is neighbour to all the other pixels in the clusters - the central pixel.