## University of Bergen

Faculty of Mathematics and Natural Sciences

## Masters Thesis

# Design of a Rectifier for Electric Vehicle Chargers

Author: Omes Bajwa

### **Preface**

This thesis was submitted in partial fulfilment for the degree of Master of Science in the field of electrical power engineering at the University of Bergen. The work was carried out for the duration of two semesters, from fall 2020 to spring 2021. The necessary resources and facilities were provided by the Western University of Applied Sciences.

The process of writing this thesis has been quite a fruitful endeavour. It has introduced me to many fascinating concepts and also allowed me to immerse myself in a field that I find highly interesting. However, it has not been a bed of roses all through. There have been many challenges along the way, and the completion of this thesis could not have been possible without the help and encouragement from the people involved in both my personal and academic life.

I would like to acknowledge the help and counsel received from my supervisor, Associate Professor Shujun Zhang, who also gave me the idea for this research project. Many thanks to my co-supervisor, Associate Professor Mostafa Paskyabi, for his invaluable feedback. I would also like to thank Senior Engineer Lars Manger Ekroll for providing me with the necessary laboratory equipment. Finally, I would like to extend my deepest gratitude to my friends and family, whose kind words and support have spurred me along to complete this work.

### Abstract

Bidirectional Electric Vehicle (EV) chargers are becoming a more popular research topic in regard to overcoming the predicted increase in electricity demand from the decarbonization of the transportation sector. With a bidirectional charger, the energy stored in an EV battery can be transferred back to the grid in a grid-to-vehicle configuration, or power the home in a vehicle-to-home configuration. Conventional EV chargers are predominantly unidirectional and lack the necessary technology for bidirectional flow. This thesis investigates several rectifiers and control schemes with the aim of proposing an appropriate topology capable of being implemented in a bidirectional EV charger. The derived topology consists of a voltage-oriented controlled active front-end rectifier. Several topics related to the design are presented. Among these are the phase-locked loop, space vector modulation, voltage-oriented control, and filter design for mitigating harmonics.

The system is simulated in MATLAB Simulink during various load conditions to investigate the design and test the DC-link response of the controller. The results show that the system is capable of transitioning from rectification during a resistive load, to inversion during a regenerative load. The results also suggest that the system is capable of withstanding an increasing load, well over the intended application. This demonstrates the flexibility of the controller during off-nominal operation. A fast Fourier transformation analysis is conducted for all the load tests to verify the performance of the LCL filter. During nominal conditions, the results from the analysis show that the filter is able to attenuate the harmonics to an acceptable level in accordance with the IEEE standards.

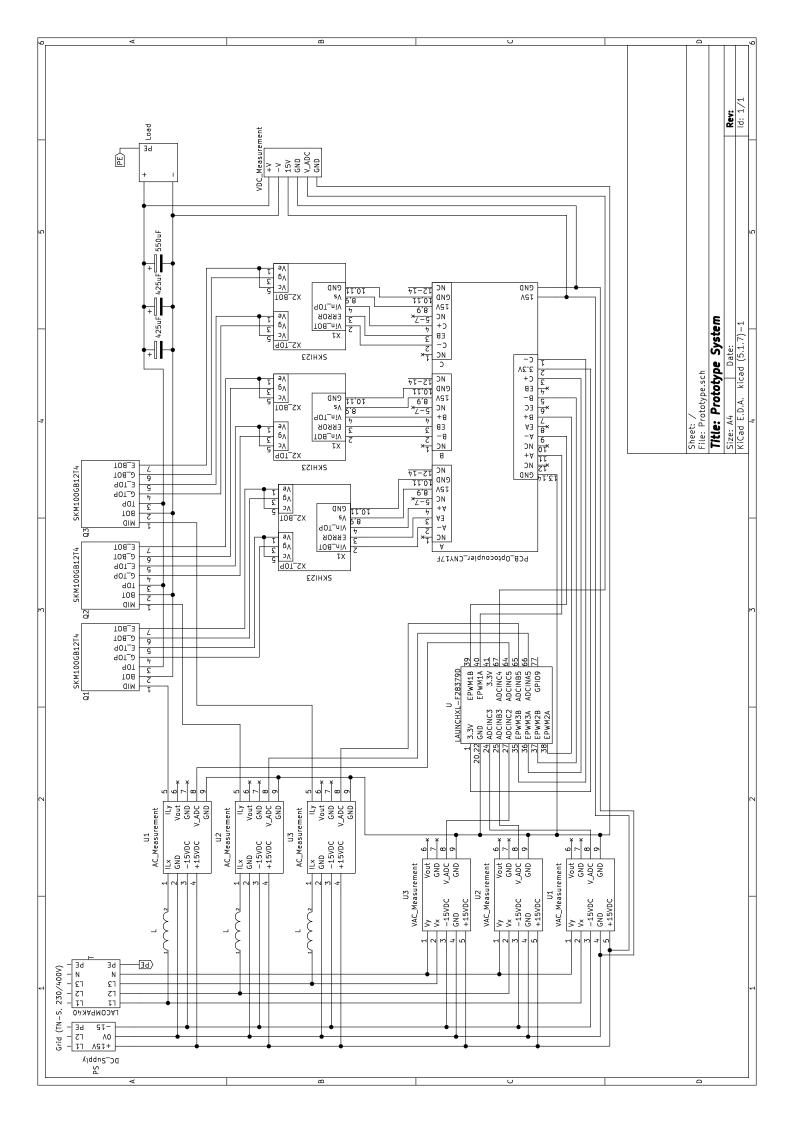

An experimental prototype is designed for the purpose of investigating the simulated results. The design methodology and working principle behind all the components in the prototype are presented. This includes the process of programming the microcontroller unit, which is used to implement all the control algorithms. Tests are conducted to verify the performance of the hardware components and software algorithms. Results from tests suggest that more work needs to be done in order for the prototype system to work as designed.

# Glossary

**bandgap** energy difference between the valence band and conduction band in insulators and semiconductors. 6

**commutation** transfer of current between semiconductor devices in a converter.

fundamental frequency lowest or base frequency of a complex waveform. 33

Hall effect named after Edwin Hall, who discovered that a magnetic field induces a transverse voltage in a conductor. 71

microprocessor peforms arithemtic and log operation. 60

**Nyquist frequency** named after Harry Nyquist, who discovered that a signal must be sampled at atleast twice its frequency to avoid alaising. 51

transducer converts one form of energy to another. 71

# Nomenclature

| Components                     |                                    |                         | $oldsymbol{v}^*$ Reference vector      |  |  |

|--------------------------------|------------------------------------|-------------------------|----------------------------------------|--|--|

| $C_d, C_{dc}$ Output capacitor |                                    | $oldsymbol{v}_c^{dq}$   | Filter capacitor voltage vector in     |  |  |

| $L_r$                          | Rectifier inductor                 |                         | dq frame                               |  |  |

| $L_s$                          | Gridside inductor                  | $oldsymbol{v}_r^{dq}$   | Rectifier voltage vector in $dq$ frame |  |  |

| $L_a, L_b$                     | $, L_c$ Line inductors             | $oldsymbol{v}_s^{dq}$   | Grid voltage vector in $dq$ frame      |  |  |

| R                              | Arbitrary resistor                 | $oldsymbol{v}_k$        | Switching vector w.r.t SVM state       |  |  |

| $R_m$                          | Measurement resistor               |                         | k                                      |  |  |

| $R_p$                          | Input resistor                     | $oldsymbol{v}_r$        | Rectifier voltage vector               |  |  |

| $R_{load}$                     | Load resistor                      | $oldsymbol{v}_s$        | Grid voltage vector                    |  |  |

| Electrical                     |                                    | $x_{abc}$               | Arbitrary vector in $abc$ domain       |  |  |

| $i_r$                          | Rectifier current vector           | $\Delta i_{max}$        | Max ripple current                     |  |  |

| $oldsymbol{i_s}$               | Grid current vector                | $\Delta V_{dc}$ ,       | $v_{rip}$ Ripple DC voltage            |  |  |

| i                              | Current vector                     | $\Delta v_d$ , $\Delta$ | $\Delta v_q$ Voltage regulator outputs |  |  |

| $m{i}_c^{dq}$                  | Filter capacitor current vector in | $i_d^*, i_q^*$          | Reference currents                     |  |  |

| c                              | dq frame                           | $i_{rd}^*, i_{rq}^*$    | Reference currents in $dq$ frame       |  |  |

| $oldsymbol{i}_r^{dq}$          | Rectifier current vector in $dq$   | $I_d$                   | DC current                             |  |  |

|                                | frame                              | $I_s$                   | RMS line current                       |  |  |

| $m{i}_s^{dq}$                  | Grid current vector in $dq$ frame  | $I_{\alpha}, I_{\beta}$ | Currents in $\alpha\beta$ frame        |  |  |

| $oldsymbol{i}_s$               | Grid current vector                | $i_{lpha},i_{eta}$      | Currents in $\alpha\beta$ frame        |  |  |

| $v_c$                          | Filter capacitor voltage vector    | $I_{\mathrm{sat}}$      | Inductor saturation current            |  |  |

| $v_r$                          | Rectifier voltage vector           | $I_a, I_b,$             | $I_c$ RMS phase currents               |  |  |

| $v_s$                          | Grid voltage vector                | $i_a, i_b, i_b$         | $i_c$ Phase currents                   |  |  |

| $oldsymbol{v}$                 | Voltage vector                     | $i_{ca}, i_{cb}$        | $i_{cc}$ Filter capacitor currents     |  |  |

| $i_{dcc}$ Capacitor current                             | $V_{dcmin}$ Minimum DC voltage                                    |

|---------------------------------------------------------|-------------------------------------------------------------------|

| $i_{dc}$ Rectifier output current                       | $V_{dc}, v_{dc}$ DC voltage                                       |

| $I_d, I_q$ Currents in $dq$ frame                       | $V_d, V_q$ Voltages in $dq$ frame                                 |

| $i_d, i_q$ Currents in $dq$ frame                       | $v_d, v_q$ Voltages in $dq$ frame                                 |

| $i_{load}$ Load current                                 | $V_{IN}$ Input voltage                                            |

| $I_{PN}$ Nominal primary current                        | $V_{LL}$ Line-to-line voltage                                     |

| $i_{ra}, i_{rb}, i_{rc}$ Rectifier phase currents       | $V_{offset}$ Offset voltage                                       |

| $i_{rd}, i_{rq}$ Rectifier currents in $dq$ frame       | $V_{PN}$ Nominal primary voltage                                  |

| $I_{rm}$ Maximum rectifier current                      | $V_{PWM}$ Voltage of PWM signal                                   |

| $i_{sa}, i_{sb}, i_{sc}$ Gridside phase currents        | $v_{ra}, v_{rb}, v_{rc}$ Rectifier phase voltages                 |

| $I_{sm}$ Grid current amplitude                         | $v_{rd}, v_{rq}$ Rectifier voltages in $dq$ frame                 |

| $p^*$ Active power reference                            | $v_{sa}, v_{sb}, v_{sc}$ Gridside phase voltages                  |

| $q^*$ Reactive power reference                          | $v_{sd}, v_{sq}$ Grid voltages in $dq$ frame                      |

| $v^*$ Reference voltage                                 | $V_{sm}$ Grid voltage amplitude                                   |

| $v_{dc}^*, v_{dc}^*$ DC reference voltage               | $v_{us}$ Undershoot voltage                                       |

| $v_{dq}^*$ Control signal vector                        | $x_a, x_b, x_c$ Signals in $abc$ domain                           |

| $v_d^*, v_q^*$ Control signals                          | $x_d, x_q$ Arbitrary $dq$ components                              |

| $V_d, V_{d\alpha}$ Average DC output                    | General                                                           |

| $V_m$ Mesurement voltage                                | $\alpha$ Firing anlge                                             |

| $V_P$ Primary voltage                                   | T Transformation matrix                                           |

| $V_{\alpha}, V_{\beta}$ Voltages in $\alpha\beta$ frame | $\mathbf{T}_c$ Clarke transformation                              |

| $v_{\alpha}, v_{\beta}$ Currents in $\alpha\beta$ frame | $\mathbf{T}_p$ Park transformation                                |

| $v_{ab}, v_{bc}, v_{ac}$ Line-to-line voltages          | $oldsymbol{S}_r$ Rectifier switching state                        |

| $V_{ADC}$ Analog voltage                                | $\boldsymbol{t_k}$ Duration of switching state $k$                |

| $v_a, v_b, v_c$ Phase voltages                          | $\boldsymbol{v}_1,,\boldsymbol{v}_6$ Active SVM switching vectors |

| $v_{ca}, v_{cb}, v_{cc}$ Filter capacitor voltages      | $\delta$ Attenuation constant                                     |

| $\omega$             | Angular frequency                          | $F_{RMS}$         | Fourier transformation              |

|----------------------|--------------------------------------------|-------------------|-------------------------------------|

| $\omega_n$           | Natural frequency                          | $f_{sw}$          | Switching frequency                 |

| $\omega_{res}$       | Angular resonance frequency                | Hp, E             | Iq Hysteresis bands                 |

| $\theta, \omega t$   | Instantenious phase-angle                  | $k_i$             | Intergral gain                      |

| $\theta^*$           | Angle of reference vector                  | $k_p$             | Proportional gain                   |

| $\theta_k$           | Angle of SVM sector $k$                    | L                 | Arbitrary inductor                  |

| $\theta_n$           | Angle of sector in DPC                     | $L_t$             | Total filter inductance             |

| ζ                    | Damping ratio                              | $L_{r\min}$       | Min rectifier inductance            |

| $a, a_{\mathrm{ma}}$ | x Constants used for filter calula-        | $L_{s\max}$       | Max grid inductance                 |

|                      | tion                                       | $L_{smin}$        | Min grid inductance                 |

| A                    | Area                                       | $L_{t\text{max}}$ | Max filter inductance               |

| $a_0, a_h$           | $,b_h$ Fourier coefficients                | $m_a, m_a$        | $n_f$ Modulation ratios             |

| $a_1, a_2$           | $a_3$ Constants used for filter calulation | P, p              | Active power                        |

| $A_{\alpha}$         | Commutation delay area                     | $P_L$             | Load power                          |

| $b_2, b_3$           | Constants used for filter calula-          | Q, q              | Reactive power                      |

|                      | tion                                       | $S_1, S_2$        | $S_3$ , Switching state             |

| C                    | Capacitor                                  | Sp, Se            | q Hysteresis controller outputs     |

| $C_{d\min}$          | Min DC capacitance                         | t                 | Time                                |

| $C_{f\max}$          | Max filter capacitance                     | $T_s$             | Sampling time                       |

| $C_{f\min}$          | Min filter capacitance                     | $t_0, t_7$        | Duration of SVM zero states         |

| dv                   | Voltage drop                               | $t_1,, t_n$       | $t_6$ Duration of active SVM states |

| $f_g$                | Grid frequency                             | $T_{sim}$         | Simulation time                     |

| $f_h$                | Frequency of harmonic order                | $T_{sw}$          | Switching time                      |

| $f_{res}$            | Resonance frequency                        | $v_{cr}$          | Carrier signal                      |

## Acronyms

**ADC** Analog to Digital Conversion. 62, 64, 72, 76, 77, 82–84, 88, 89

**AFE** Active Front End. 12–17, 20, 27, 28, 30, 32, 37, 54, 56, 57, 59, 100

**BJT** Bipolar Junction Transistor. 5, 13

CBPWM Carrier Based Pulse Width Modulation. 20, 22

**DPC** Direct Power Control. vi, 17, 30, 32, 37, 100

ePWM Enchanced Pulse Width Modulation. 64, 74, 75, 82, 83, 87

EV Electric Vehicle. 1–3, 76

**FFT** Fast Fourier Transform. 51

GaN Gallium Nitride. 6

GPIO General Purpose Input/Output. 64, 70, 81

**GTO** Gate Turn of Thyristor. 4

**HVL** Western Norway University of Applied Sciences (Høgskulen på Vestlandet).

IC Integrated Circuit. 75, 80, 88

**IEEE** Institute of Electrical and Electronics Engineers. 46, 51

**IGBT** Insulated Gate Bipolar Transistor. 5, 13, 60–62, 65, 66, 68, 74–76, 83, 87, 88, 101, 116

KVL Kirchhhoff's Voltage Law. 13, 39

**LED** Light Emitting Diode. 68–70

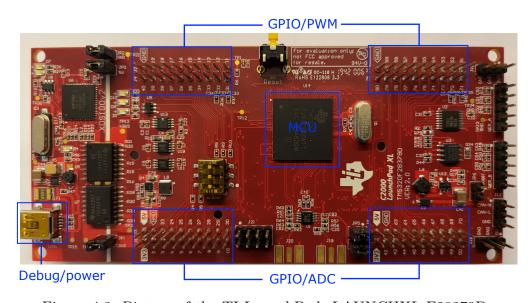

MCU Microcontroller Unit. 45, 60–64, 66, 68–71, 73–75, 80–83, 88, 101

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor. 5, 13, 66

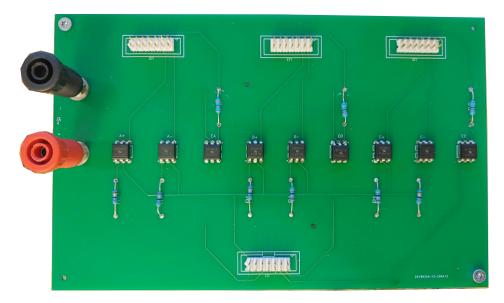

**PCB** Printed Circuit Board. 61–63, 68–72, 101

**PF** Power Factor. 2, 17, 51, 86

**PFC** Power Factor Correction. 2, 3

PLL Phase Locked Loop. 27, 28, 43, 44, 49, 50, 81, 82, 84, 85, 89, 100, 101

**PWM** Pulse Width Modulation. v, 12, 13, 17, 20–22, 27, 37, 50, 60, 62, 64, 66, 68–70, 74, 75, 83, 100, 101

**RMS** Root Mean Square. iv, 8, 33, 35, 78, 79, 88

SiC Silicon Carbide. 6

SVM Space Vector Modulation. iv-vi, 22, 26, 37, 44, 45, 49, 50, 83, 101

**TF** Transfer Function. 44

**THD** Total Harmonic Distortion. 3, 33, 35, 37, 43, 46, 51–53, 55, 86, 87

**UPF** Unity Power Factor. 29, 31, 40, 46, 51, 52, 86

V2G Vehicle-to-Grid. 1, 2

V2H Vehicle-to-Home. 1, 2

VBC Voltage Based Control. 17

VFBC Virtual Flux Based Control. 17

VOC Voltage Oritented Control. 17, 18, 20, 22, 27, 28, 37, 76, 100

## Contents

| P            | refac                       |                                           | i   |

|--------------|-----------------------------|-------------------------------------------|-----|

| $\mathbf{A}$ | bstra                       | et e                                      | ii  |

| $\mathbf{G}$ | lossa                       | у                                         | iii |

| N            | omer                        | clature                                   | iv  |

| $\mathbf{A}$ | crony                       | ms                                        | vii |

| $\mathbf{C}$ | ontei                       | ts (you are here)                         | ix  |

| 1            | Inti                        | oduction                                  | 1   |

|              | 1.1                         | Background                                | 1   |

|              | 1.2                         | Objectives                                | 3   |

|              | 1.3                         | Outline                                   | 3   |

| <b>2</b>     | $\operatorname{Th}\epsilon$ | oretical Framework                        | 4   |

|              | 2.1                         | Power Semiconductor Devices               | 4   |

|              |                             | 2.1.1 Comparison of Controllable Switches | 5   |

|              | 2.2                         | Three Phase Rectifiers                    | 6   |

|              |                             | 2.2.1 Diode Rectifier                     | 7   |

|              |                             | 2.2.2 Thyristor Rectifier                 | 9   |

|              |                             | 2.2.3 Active Front End Rectifier          | 12  |

|              |                             | 2.2.4 Comparison                          | 15  |

|              | 2.3                         | Control Strategies                        | 16  |

|              |                             | 2.3.1 Clarke and Park Transformation      | 18  |

|              |                             | 2.3.2 Pulse Width Modulation              | 20  |

|              |                             | 2.3.3 Voltage Oriented Control            | 27  |

|              |                             | 2.3.4 Direct Power Control                | 30  |

|              | 2.4                         | Harmonic Distortion                       | 33  |

| 3            | Des                         | gn and Simulation                         | 37  |

|              | 3.1                         | Proposed Topology                         | 37  |

|   |     | 3.1.1  | Mathematical Model                          | 38 |

|---|-----|--------|---------------------------------------------|----|

|   |     | 3.1.2  | Filter Design                               | 11 |

|   |     | 3.1.3  | Phase Locked Loop                           | 43 |

|   |     | 3.1.4  | DC Bus                                      | 44 |

|   | 3.2 | Simula | ation Model                                 | 45 |

|   |     | 3.2.1  | Clarke and Parke Transformation             | 47 |

|   |     | 3.2.2  | Phase Locked Loop                           | 48 |

|   |     | 3.2.3  | Space Vector Modulation                     | 49 |

|   |     | 3.2.4  | Proportional Integral Control               | 5( |

|   | 3.3 | Simul  | ation Tests and Results                     | 51 |

|   |     | 3.3.1  | Rectifier Operation                         | 52 |

|   |     | 3.3.2  | Inverter Operation                          | 54 |

|   |     | 3.3.3  | Bidirectional Operation                     | 56 |

| 4 | Exp | oerime | ntal Prototype 5                            | 56 |

|   | 4.1 | Techn  | ical Aspects                                | 61 |

|   |     | 4.1.1  | Microcontroller Unit                        | 33 |

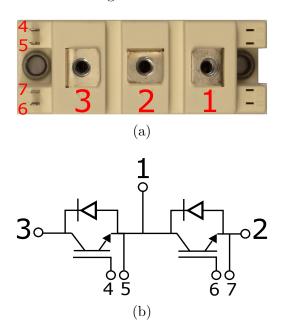

|   |     | 4.1.2  | Transistor Module                           | 35 |

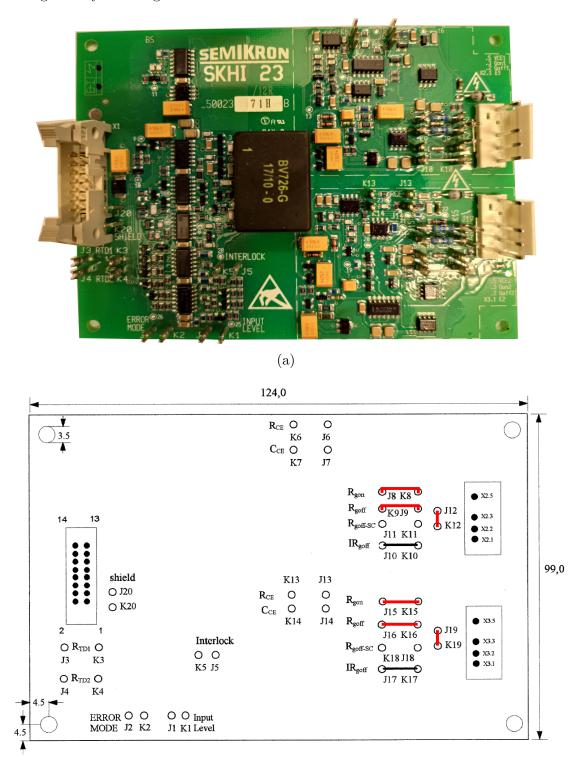

|   |     | 4.1.3  | Transistor Driver                           | 66 |

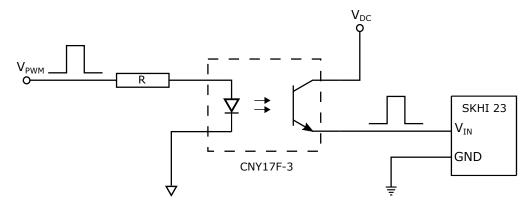

|   |     | 4.1.4  | Optocoupler Circuit                         | 38 |

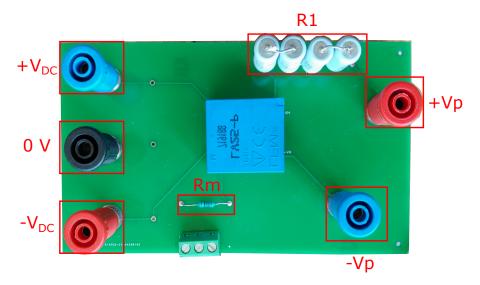

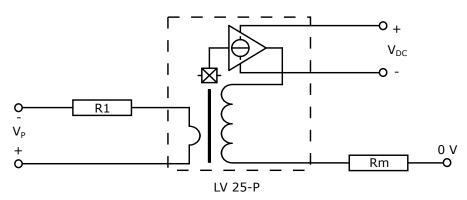

|   |     | 4.1.5  | DC Measurement Circuit                      | 71 |

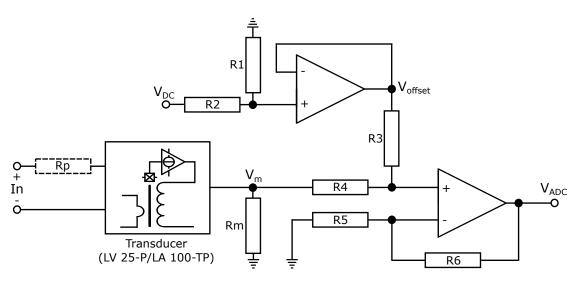

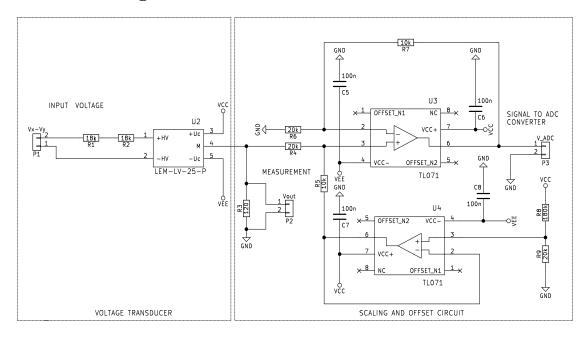

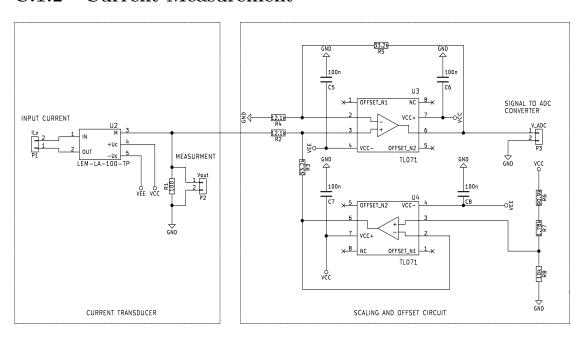

|   |     | 4.1.6  | AC Measurement Circuits                     | 72 |

|   | 4.2 | Hardv  | vare Tests                                  | 74 |

|   |     | 4.2.1  | Propagation of a Single Gating Pulse        | 74 |

|   |     | 4.2.2  | DC Voltage Measurement                      | 76 |

|   |     | 4.2.3  | AC Voltage Measurements                     | 77 |

|   |     | 4.2.4  | AC Current Measurements                     | 79 |

|   | 4.3 | Softwa | are Implementation and Tests                | 3( |

|   |     | 4.3.1  | Implementation                              | 31 |

|   |     | 4.3.2  | Sampling and Scaling of Measurements        | 33 |

|   |     | 4.3.3  | Grid Phase Angle Extraction                 | 34 |

|   |     | 4.3.4  | Coordinate Transformation                   | 35 |

| 5 | Dis | cussio | n 8                                         | 36 |

|   | 5.1 | Simul  | ation                                       | 36 |

|   | 5.2 | Exper  | imental Prototype                           | 37 |

|   |     | 5.2.1  | Propagation of a Gating Signal              | 37 |

|   |     | 5.2.2  | Measurement Circuits and Digital Sampling 8 | 38 |

| 5.2.3 PLL and Coordinate Transformation | 89  |

|-----------------------------------------|-----|

| 6 Conclusion                            | 90  |

| Bibliografi                             | 92  |

| List of Figures                         | 101 |

| List of Tables                          | 103 |

| Appendices                              | 104 |

| A Matlab Code                           | 104 |

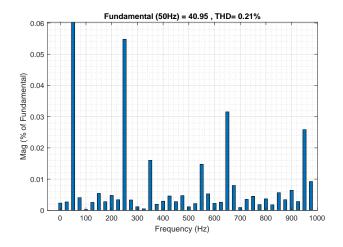

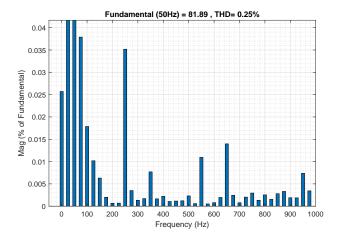

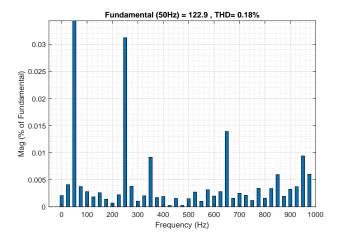

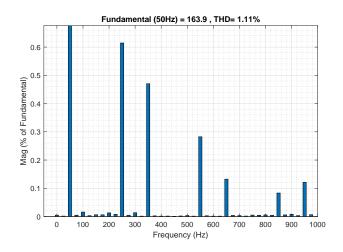

| B Fast Fourier Transform Analyses       | 111 |

| C Wiring Diagram                        | 114 |

| D Datasheet                             | 117 |

### 1 Introduction

### 1.1 Background

The reality concerning climate change and environmental degradation from carbon emissions has strengthened the global response in favour of using alternative energy in otherwise fossil dependent sectors. In particular, the transportation sector is highly dependent on fossil fuels, as almost all of the energy (95%) is derived from petroleum [1, 2]. Transportation is also responsible for 24% of direct CO2 emissions from fuel combustion [3]. As an effort to cut pollution, several nations have established a timeline for phasing out combustion engine vehicles [4]. This has caused a rise in development and sales of Electric Vehicles (EV), which has already been on an increasing trend globally and is expected to increase further [5]. The electricity demand is also expected to increase in parallel to the decarbonisation of the transportation sector. Furthermore, new infrastructure is being built to accommodate for the energy needs required by the increasing amount of EVs. However, with the current available technology, it can be difficult for the grid utility to meet the increasing energy demand. More specifically, as more charging stations are being installed in both private and public settings (e.g., filling stations and parking lots), balancing the electricity demand and supply will become an increasing challenge. This is partly due to EVs being a mobile and unpredictable load. Another reason is that the majority of EV chargers are uncontrolled, that is, unable to regulate the power consumption with respect to the capacity of the connected grid [6]. Furthermore, given that the majority of EVs are connected to the grid while idle [7] makes them an unnecessary load when fully charged. There has been several researches on the topic to overcome these challenges, and some emerging concepts are Vehicle-to-Grid (V2G), Vehicle-to-Home (V2H) and smart charger technology [8–12].

Smart charging implies that an algorithm is used to control and coordinate the charging of the EV, as opposed to uncontrolled charging, which, as mentioned earlier, means that charging of the EV occurs the instant it is connected to the utility. With smart charging, the total grid load during times of maximum energy consumption (peak load hours) can be reduced significantly. With an appropri-

ate algorithm, an EV charger can be programmed to charge with respect to the electricity price. This also creates an economic incentive for EV owners to adopt smart charger technology. Furthermore, there is also an economic incentive in adopting V2G technology. With V2G, the energy stored in the EV battery can be transferred back to the grid. In combination with smart charging, this allows EV owners to charge when the electricity is cheap and sell power back to the utility at a higher price during peak load hours (also called energy arbitrage). For EV owners living in self-sufficient smart homes, V2G can be especially profitable. In this case, surplus energy generated from intermittent energy sources (e.g., rooftop solar panels or small-scale wind turbines) can be sold to the utility. Aside for monetary gain, another advantage is that transferring power back to the grid can help compensate for larger intermittent energy sources, which can adversely affect the stability of the grid in terms of frequency, voltage, and Power Factor (PF). Otherwise, with a V2H configuration, the energy stored in the EV battery can be used to power the home. During a power outage, V2H can be quite useful as the EV battery can act as an backup supply. There are clearly many benefits with V2G and V2H technologies. However, for any of these to be possible, an appropriate EV charger is needed.

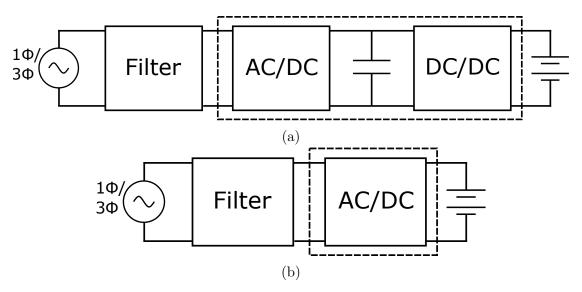

Figure 1.1: General architecture of a two-stage charger (a) and single-stage charger (b). The supply can be either single-phase  $(1\phi)$  or three-phase  $(3\phi)$ .

In general, EV chargers have a single or two stage architecture [13, 14], as shown in Figure 1.1. In a two-stage architecture, an active front-end rectifier provides Power Factor Correction (PFC) and steady DC voltage to a DC/DC converter. The DC/DC converter can be used to provide a galvanic isolation, but has the

main function of regulating the power flow. Most EV chargers use a two-stage configuration for higher efficiency and step-up capabilities. A single-stage configuration (no DC/DC converter) is often preferred for a cheaper and less bulky design. Either way, for V2G and V2H to be possible, it is essential that the converter(s) have bidirectional capabilities. Furthermore, a control algorithm is needed for maintaining the desired DC voltage and conducting PFC. With an appropriate design, a high efficiency can be achieved with a low Total Harmonic Distortion (THD). Moreover, the filter design is important for mitigating harmonics, which, if neglected, can cause overheating and have a degrading effect on the system [15].

### 1.2 Objectives

The aim of this thesis is to design and implement a 20 kW three-phase bidirectional AC/DC rectifier system. More specifically, the objectives are:

- Propose a topology and describe its operating principle.

- Construct a simulation model and produce results verifying its bidirectional capabilities.

- Construct a prototype and measure its output for verifying the simulation results.

### 1.3 Outline

In the following chapter, the theory behind various concepts, which are prerequisite for designing an appropriate rectifier are presented. In chapter three follows a complete presentation of the proposed rectifier, including results from simulations conducted for various load conditions. The process of building the experimental prototype system, and results from real-time tests are presented in chapter four. A discussion concerning the performance of the designed system, based on both simulation and physical results, is presented in chapter five. Finally, a conclusion is formulated in chapter six.

### 2 Theoretical Framework

This chapter serves to give an overview of the fundamental knowledge related to the design of a front end rectifier system capable of bidirectional flow. Various topics concerning power electronics and control are presented, with an emphasis on rectifier topologies used for three phase AC/DC converters.

### 2.1 Power Semiconductor Devices

In all converters, the power flows through semiconductor devices that are either in the off-state (reverse biased) or on-state (conducting). Ideally, these devices should not conduct current in the off-state. In reality, there will be a small leakage current during reverse bias until the device reaches its breakdown voltage. These characteristics are determined by the semiconductor material. Silicon (Si), Germanium (Ge) and Gallium Arsenide (GaAs) are traditionally used for manufacturing such devices [16].

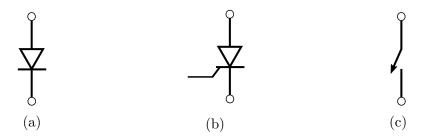

It is possible to classify all semiconductor devices in three main categories according to their degree of controllability, namely diodes, thyristors and controllable switches. Below is a figure showing the generic symbols for each category. There are of course many different variations of these devices, with their own characteristic symbols. However, they are all based on at least one of the working principles which defines the three categories.

In a diode, the on and off states are controlled by the power circuit. Depending on its predefined characteristics, it will ideally start conducting when forward voltage across the device is at rated value. For a thyristor, the on state can be triggered by applying a pulse of current at the gate terminal during its forward-blocking state. Once the device starts conducting, it cannot be turned off by the gate, and behaves like a diode until the anode current changes polarity. Afterwards the gate regains control with the possibility of triggering the device into its on state during its initial blocking condition. This latch-like behaviour differs from a controllable switch, which can be turned both on and off by the gate [17].

The Gate Turn of Thyristor (GTO) and various other transistors can be categorized as controllable switches. The GTO is similar to the thyristor in Figure 2.1b,

Figure 2.1: Generic symbol for a diode (a), thyristor (b) and controllable switch (c).

but can be turned off by applying a negative gate-cathode voltage, and is therefore classified as a controllable switch. Transistors have the same controllability, and due to major advances during recent years, there have been developed many different variations [18].

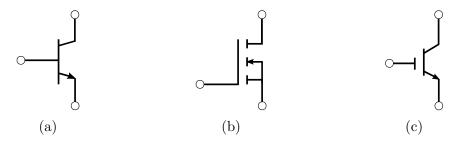

The most popular transistors are the Bipolar Junction Transistor (BJT), Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) and the Insulated Gate Bipolar Transistor (IGBT). Respective symbols representing each transistor is shown in Figure 2.2.

Figure 2.2: Symbols representing the BJT (a), MOSFET (b) and IGBT (c).

### 2.1.1 Comparison of Controllable Switches

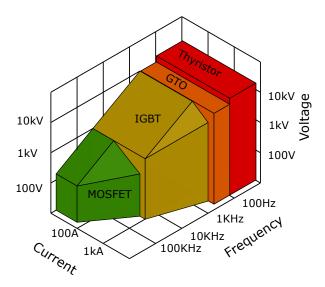

Due to structural differences and junction composition, all controllable switches have a nominal range of operation. This range can be defined by power capability and switching speed, as illustrated in Figure 2.3. This comparison is useful for selecting a device that meets the requirements of an arbitrary converter. However, other factors such as price and switching losses should also be considered.

Due to minor switching losses and high switching frequencies, the MOSFET is preferred in low- and medium-power applications (<500 kW). Furthermore, the IGBT is appropriate for high power applications (>500 kW) [18]. The nominal power rating is often limited by the semiconductor material used to manufacture the switch.

Figure 2.3 only compares Si devices. However, due to limitations on semiconductor properties (e.g power density and temperature), there have been developed two new alternatives which have attracted considerable attention in the last decade, namely Silicon Carbide (SiC) and Gallium Nitride (GaN). Their superiority stems from having a wide bandgap, which enables them to operate at temperatures above 600°, in addition to other properties as low leakage current and high breakdown strength [19–22].

Figure 2.3: Comparison of Si devices with respect to voltage, current and frequency. Adapted from [18].

### 2.2 Three Phase Rectifiers

Rectifiers are used for AC to DC conversion. They have a wide range of applications and are often found in DC power supplies. Other applications include: high voltage power transmission, electrochemical processes, motor drives, and traction equipments [19]. Depending on the power rating and application, rectifiers can have a three or single phase topology. Both utilize semiconductor devices (presented in section 2.1) for the conversion process.

In rectifiers, semiconductor devices form a bridge that connects the AC part of the topology to a DC bus, storage element or load. Capacitors are normally used to store the DC voltage. Conversion quality and other capabilities are determined by various factors, including capacitor size, controllability and characteristics of the devices used in the bridge. In reference to the three main categories of semiconductors from Figure 2.1, a rectifier can be classified as a diode, thyristor or a fully

controlled rectifier.<sup>1</sup> In high power applications, these types of rectifiers usually adopt three phase topologies.

In this section, the working principle of three different three-phase rectifiers are presented and compared [17]. For simplicity, only idealized circuits without grid side inductance, with constant DC voltage, and without load are analysed in section 2.2.1 and 2.2.2. In reality, grid side inductance affects the commutation process, causing a phase shift in the rectified current, which consequently forces more than one diode to conduct simultaneously with a continuously flowing current [17].

#### 2.2.1 Diode Rectifier

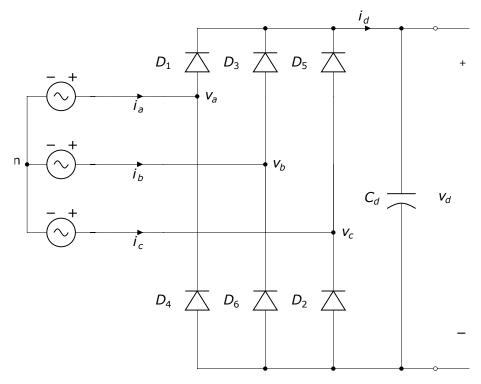

A circuit of a three-phase diode bridge rectifier is illustrated in Figure 2.4. The rectifier provides a DC current  $i_d$  and voltage  $v_d$  at the output, which is connected to a capacitor  $C_d$ . The instantaneous currents are denoted as  $i_a$ ,  $i_b$  and  $i_c$ . These currents flow through the diodes in a sequential order. More specifically, the diodes conduct in pairs and are numbered according to their respective sequence: D1-D2, D3-D2, D3-D4, D5-D4, D5-D6 and D1-D6. Each sequence lasts for 60°, where each diode conducts for  $120^{\circ}$ . This configuration gives a DC output with six ripple pulses over the course of one period (360°), and is therefore often called a six-pulse bridge rectifier.

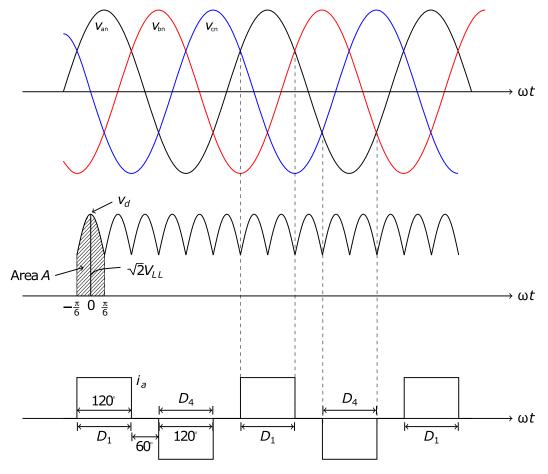

The conduction sequence depends on the difference in voltage between common anode and cathode for the top and bottom diodes, respectively. In other words, the diode with highest anode voltage among D1, D3 and D5, and lowest cathode voltage among D2, D4 and D6 will conduct simultaneously as a pair. This conduction scheme can be seen in Figure 2.5. The phase (i.e line-to-neutral) voltages are denoted as  $v_{an}$ ,  $v_{bn}$  and  $v_{cn}$ . The instantaneous DC side voltage is denoted as  $v_d$ .

The average value of the output DC voltage can be derived from one ripple pulse  $(60^{\circ})$ . For this purpose, the time origin t=0 in Figure 2.5 is set at a point where the line-to-line voltage  $v_{ab}$  is at its maximum. The instantaneous waveform of  $v_d$  can therefore be expressed as:

$$v_d = v_{ab} = \sqrt{2}V_{LL}\cos\omega t \qquad -\pi/6 < \omega t < \pi/6 \tag{2.1}$$

<sup>&</sup>lt;sup>1</sup>A fully controlled rectifier is also called an active or synchronous rectifier.

$<sup>^2</sup> For this to work, one diode must conduct for <math display="inline">60^\circ$  in the start.

Figure 2.4: Three-phase diode rectifier.

where  $V_{LL}$  is the RMS line-to-line voltage. Integrating this expression with respect to the sequence duration, gives the corresponding volt-second area:

$$A = \int_{-\pi/6}^{\pi/6} \sqrt{2} V_{LL} \cos \omega t \, d(\omega t) = \sqrt{2} V_{LL}$$

(2.2)

A simplified expression for the average DC output can now be derived by dividing A over the interval  $\frac{\pi}{3}$ :

$$V_d = \frac{1}{\pi/3} \int_{-\pi/6}^{\pi/6} \sqrt{2} V_{LL} \cos \omega t \, d(\omega t) = \frac{3}{\pi} \sqrt{2} V_{LL} = 1.35 V_{LL}$$

(2.3)

In this idealized case, the RMS value of the line current  $I_s$  can easily be derived with respect to the DC current  $I_d$ :

$$I_s = \sqrt{\frac{1}{\pi} \int_{\frac{\pi}{3}}^{\pi} I_d^2 d(\omega t)} = \sqrt{\frac{2}{3}} I_d = 0.816 I_d \qquad s \in \{a, b, c\}$$

(2.4)

Figure 2.5: Conduction scheme for the circuit in Figure 2.4 [23]

### 2.2.2 Thyristor Rectifier

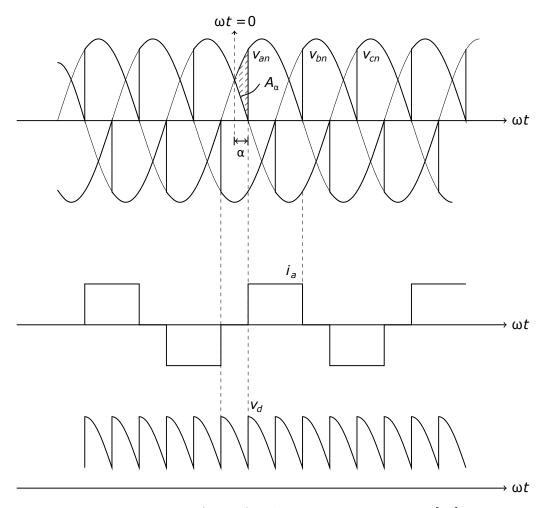

If the diodes (D1-D6) in Figure 2.4 are replaced by thyristors (T1-T6), the circuit will look like the one given below in Figure 2.7. The difference between using diodes or thyristors in a three phase rectifier topology lies in the controllability. As briefly discussed in section 2.1, thyristors can be turned on by an external gate pulse during forward bias. Using thyristors therefore gives the advantage of being able to control the output DC voltage. This is done by timing the gate pulse firing angle  $\alpha$ , relative to the AC voltage phase angle  $\omega t$ . This means that the rectified output voltage can be derived as a function of the thyristor firing angle.

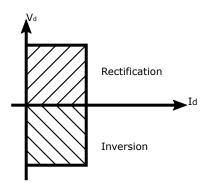

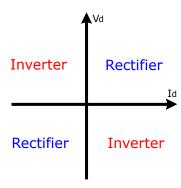

Being able to control the average DC output includes extended capabilities that surpasses traditional rectifier operation. In addition to outputting a positive DC voltage, the thyristors can also be controlled in a manner of inverting an arbitrary voltage DC source. Ideally, this transition is continuous, with the capability of changing the output from a positive maximum to a negative minimum. Although,

Figure 2.6: Active quadrants, adapted from [17].

during such a transition when the DC voltage changes its polarity, the DC current will maintain its direction. This means that the converter only operates in two of the four quadrants spanning the  $V_d-I_d$  plane, as illustrated in Figure 2.6. The DC limits are determined by the circuit configurations and input voltage, while the current is limited by the components' rating. However, for deriving a relationship between the average DC output and firing angle, an analysis of the converter in rectifier operation will suffice.

If gate pulses are continuously provided to the thyristors in Figure 2.7 without delay ( $\alpha = 0^{\circ}$ ), the output voltage will be the same as for the rectifier discussed in section 2.2.1. The respective formula has been derived in (2.3). By itself, this relation is not valid with a delayed firing angle ( $\alpha > 0^{\circ}$ ). In this case, a new equation can be derived from the waveforms illustrated in Figure 2.8.

When the gate pulse is sent, a pair of thyristors will start conducting until the sequence is done. Because this is a six pulse topology with a 120° conduction scheme similar to the diode rectifier, a new sequence will start every 60° from the first gate pulse at  $\omega t = \alpha + 60^{\circ}$ . In Figure 2.8, the thyristor firing angle is set at  $\alpha = 30^{\circ}$ , from  $\omega t = 0$ . This delay is marked on the voltage waveform as the area  $A_{\alpha}$ . The difference between the phase current and voltage can be given as  $\phi_1 = \alpha$ . From the waveform, it is also clear that the average DC output will be lower with a higher firing angle. The average DC output can therefore be expressed as:

$$V_{d\alpha} = V_d - \frac{A_\alpha}{\pi/3} \tag{2.5}$$

The volt-second area  $A_{\alpha}$  can be obtained through the integral of  $v_{an} - v_{cn}$  (= $v_{ac}$ ),

Figure 2.7: Three phase thyristor rectifier.

which is given as:

$$v_{ac} = \sqrt{2}V_{LL}\sin\omega t \tag{2.6}$$

Furthermore, the area can be found as:

$$A_{\alpha} = \int_{0}^{\alpha} \sqrt{2} V_{LL} \sin \omega t \, d(\omega t) = \sqrt{2} V_{LL} (1 - \cos \alpha) \tag{2.7}$$

By substituting  $v_d$  and  $A_\alpha$  in (2.5) with the expressions from (2.3) and (2.7), it is possible to derive a simplified statement for the average DC voltage:<sup>3</sup>

$$V_{d\alpha} = \frac{3\sqrt{2}}{\pi} V_{LL} \cos \alpha = 1.35 V_{LL} \cos \alpha \tag{2.8}$$

The line current is the same as for the diode rectifier:

$$I_s = \sqrt{\frac{2}{3}}I_d \tag{2.9}$$

<sup>&</sup>lt;sup>3</sup>If the firing angle is  $\alpha > 90^{\circ}$ , the converter will act as an inverter.

Figure 2.8: Waveforms for the circuit in Figure 2.7 [23].

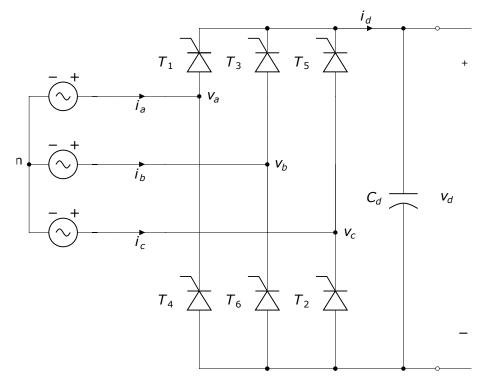

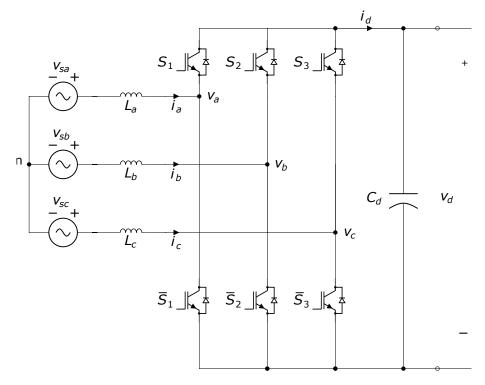

#### 2.2.3 Active Front End Rectifier

An Active Front End (AFE) converter utilizes controllable switches (usually transistors [24]) for converting voltage. Similar to the thyristor converter, both rectification and inversion is possible. However, as mentioned in section 2.1, controllable switches can be switched on and off whenever required. This allows for forced commutation independent of the line voltage, which depending on the device rating, can occur several hundreds of times during one period. With this increased control, it is possible to modulate the drawn current by means of timing the gating pulses relative to a reference signal. This method is called Pulse Width Modulation (PWM), and makes it possible for the converter to transfer power bidirectionally. PWM will be discussed more later in section 2.3.2.

In general, an AFE converter can operate in all four quadrants of the aforementioned  $V_d - I_d$  plane, as illustrated in Figure 2.9. However, the figure clearly shows

that there are two quadrants for rectification. This means that there are two scenarios where the AFE converter will operate as a rectifier: by DC voltage reversal with positive  $i_d$ , or the inverse – DC current reversal with positive  $v_d$ . Either way, the DC side can be built with a current-source (inductor) or voltage-source (capacitor). The latter is by far the most widely used topology [19], and will therefore be in focus for the following analysis. A circuit of the voltage-source rectifier can be seen in Figure 2.10. For the sake of example, the bridge consists of six IGBTs. However, other transistors like the BJT and MOSFET are also commonly used in AFE rectifiers. By combining these devices with a proper control scheme, it is possible to achieve the desired DC output.

Figure 2.9: Operational quadrants for the AFE converter.

The goal of a voltage-source rectifier is to keep the DC output voltage at a constant level. Depending on the specifications, the DC voltage can also be controlled to match a predefined reference value. This is done by combining the rectifier with a control circuit, forming a feedback loop. In such a configuration,  $V_d$  is compared with the reference value, generating an error signal. This difference is fed to a control block, which uses PWM to generate the appropriate gating signals, supplying the required DC current. There are of course various elements involved in such a control circuit, and due to the complexity it will be discussed separately in section 2.3. For now, a basic analysis of the voltage-source rectifier without a control circuit will be conducted.

In Figure 2.10, the inductors  $L_a$ ,  $L_b$  and  $L_c$  represent the line inductances. By assuming  $L_a = L_b = L_c = L_s$ , and using Kirchhhoff's Voltage Law (KVL), the voltage equations can be expressed as:

$$\begin{bmatrix} v_{sa} \\ v_{sb} \\ v_{sc} \end{bmatrix} = L_s \frac{d}{dt} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix}$$

(2.10)

Figure 2.10: Circuit of a voltage-source AFE rectifier.

Furthermore, the AC side voltages can be simplified into a space vector [25]:

$$\boldsymbol{v}_s = \frac{2}{3}(v_{sa} + \mathbf{a}v_{sb} + \mathbf{a}^2v_{sc}) \tag{2.11}$$

where  $\mathbf{a} = e^{j2\pi/3}$ . A vector equation for the grid dynamics can now be obtained by substituting (2.10) into (2.11):

$$\mathbf{v}_s = L_s \frac{d}{dt} (\frac{2}{3} (i_a + \mathbf{a}i_b + \mathbf{a}^2 i_c)) + \frac{2}{3} (v_a + \mathbf{a}v_b + \mathbf{a}^2 v_c)$$

(2.12)

The equation above can be further simplified by the following definitions:

$$\mathbf{i}_s = \frac{2}{3}(i_a + \mathbf{a}i_b + \mathbf{a}^2i_c) \tag{2.13}$$

$$\boldsymbol{v}_r = \frac{2}{3}(v_a + \mathbf{a}v_b + \mathbf{a}^2v_c) \tag{2.14}$$

where  $\boldsymbol{v}_r$  is determined by the switching state of the converter  $(\boldsymbol{S}_r)$  and DC voltage.

This relationship can be expressed as:

$$\boldsymbol{v}_r = \boldsymbol{S}_r V_d \tag{2.15}$$

The switching states for each of the converter's legs can be defined as  $S_1$ ,  $S_2$  and  $S_3$ . Considering that the switches can be either on or off, each state can be defined with a binary value (1 or 0). S can then be defined in a vector space as follows:

$$\mathbf{S} = \frac{2}{3}(S_1 + \mathbf{a}S_2 + \mathbf{a}^2S_3) \tag{2.16}$$

It is now possible to simplify (2.12) to:

$$L_s \frac{di_s}{dt} = \boldsymbol{v}_s - \boldsymbol{v}_r \tag{2.17}$$

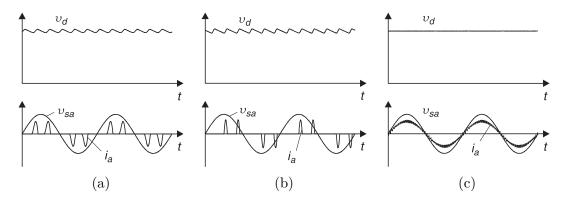

### 2.2.4 Comparison

The working principle of the diode, thyristor, and AFE rectifier has been explained in the previous sections. By comparing the three, it is clear that the diode rectifier has the simplest and cheapest topology. However, it also has a major disadvantage when it comes to control. Being a line-commutating rectifier and therefore entirely dependent on the line voltage, there is virtually no possibility for controlling the DC output. Using thyristors solves this issue by changing the firing angle to manipulate the flow of power. Although this makes the thyristor rectifier bidirectional, the controllability is still limited by the line voltage. Apparently, full controllability is achieved by forced-commutation, as implemented in the AFE rectifier. This allows for bidirectional flow and gives the opportunity for controlling the DC voltage according to a predefined reference value. However, aside from a more complicated control, its main disadvantage is the higher cost in comparison to the diode and thyristor rectifier [25].

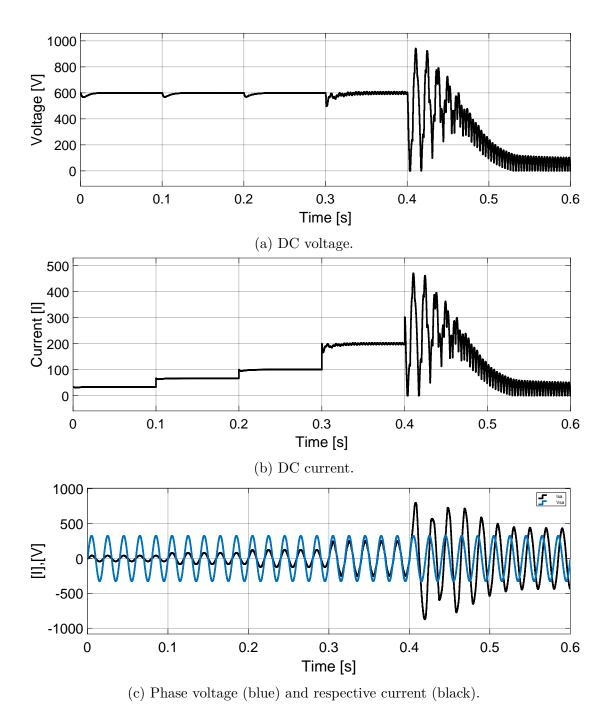

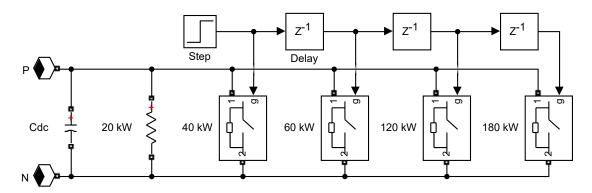

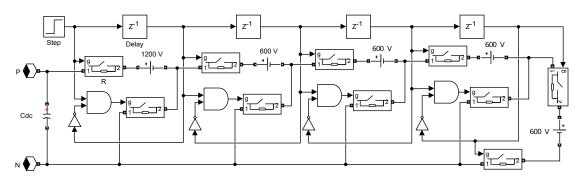

The AC inputs and DC output for each rectifier is presented in Figure 2.11. From observation, a connection between stability and current drawn from the grid can be made. Figure 2.11c represents the characteristics of an AFE rectifier, and has the most stable output. This is due to the gate turn-off capability of controllable switches that makes them able to switch on and off several times during one cycle, and therefore draw a current resembling a sinusoid. In reality, the current is never perfectly sinusoidal due to distortion. They are, however, lower in an AFE rectifier

compared to a diode and thyristor rectifier.

Figure 2.11: AC inputs and DC output for the diode (a), thyristor (b) and AFE rectifier (c) [25].

Distortion and efficiency are other important factors to consider when comparing the three topologies. Distorted current is often drawn from the grid, but is also affected by the process of power conversion in the converter (i.e. commutation and switching). The efficiency is also greatly affected by the ability to draw a perfectly sinusoidal current. These aspect have not been discussed previously, but from analysis conducted in the previous subsections, it follows that there is a relationship between the current distortion, and control of the converter. Therefore, it also follows that the diode rectifier will give the highest distortion and lowest efficiency, while an AFE rectifier has the potential of operating at a higher efficiency with the lowest distortion. This, of course, is a generalisation which in reality largely depends on the system in question. With this in mind, a general table comparing the different aspects discussed until now can be made, as presented in Table 2.1.

| Rectifier | Distortion            | Control | Efficiency |  |

|-----------|-----------------------|---------|------------|--|

| Diode     | Highest               | None    | Lowest     |  |

| Thyristor | $\operatorname{High}$ | Semi    | Low        |  |

| AFE       | Low                   | Full    | High       |  |

Table 2.1: General comparison of different rectifiers.

### 2.3 Control Strategies

In rectifiers, the term control is often used to describe the ability to somehow affect the conversion of power. In this section, the focus will be on different types of control circuits and the elements involved in manipulating the conversion process of three phase rectifiers. In view of the fact that controllability of the diode and thyristor rectifier is limited, there is no point in discussing this aspect for these particular topologies. The AFE rectifier, however, is of more interest due to its controllable switches.

The concept of applying a control scheme to an AFE voltage-source rectifier for maintaining a constant DC output voltage has been introduced in the previous section. This type of control can generally be classified as Voltage Based Control (VBC) and is being used in many different applications,<sup>4</sup> e.g., motor drives, wind power systems, and micro-grids [26–29]. There are many variations of VBC, and aside from keeping the DC output constant, they also aim to deliver a clean sinusoidal waveform with high Power Factor (PF). There are, however, principle differences in how they operate to achieve these goals.

The two main types of VBC are Voltage Oritented Control (VOC) and Direct Power Control (DPC). Both control strategies have the same inputs in terms of DC reference voltage and line measurements. The difference lies in the fundamental principles which are used to build the control circuits. In the case of VOC, the AC measurements are transformed into a rotating reference frame by the use of coordinate transformation. This way, the AC measurements can be treated as DC quantities, and easily regulated inside an inner current loop to generate the necessary reference signals for controlling the PWM (coordinate transformation will be discussed in detail later). This makes it possible for the AFE converter to operate as a rectifier by drawing a sinusoidal current in phase with the grid voltage, while maintaining a constant DC output. The key elements in VOC can therefore be defined as the current loop and PWM module. For DPC the strategy is quite different.

As opposed to VOC, DPC has no inner current control loop or PWM module. Instead, switching states are selected from a table based on the instantaneous errors between the commanded and estimated values of active and reactive power. The fundamental principle behind DPC is therefore efficient calculation of line power for determining the correct switching states. This makes the implementation of VOC far more complicated in comparison. Although VOC demands a current loop and PWM, it is still the most popular strategy [26]. This is in part because VOC has the ability to operate with a fixed switching frequency, and possibility of utilizing more advanced PWM techniques. However, for this to be possible, a

$<sup>^4{\</sup>rm The~term:}$  Virtual Flux Based Control (VFBC) is often used instead of VBC as an analogy to motor control

coordinate transformation and decoupling between active and reactive components is required.

#### 2.3.1 Clarke and Park Transformation

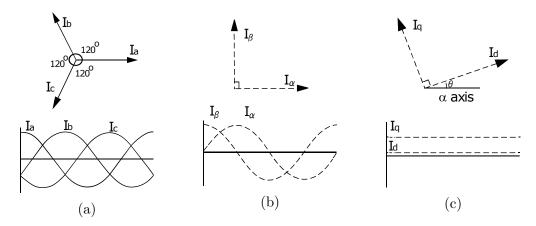

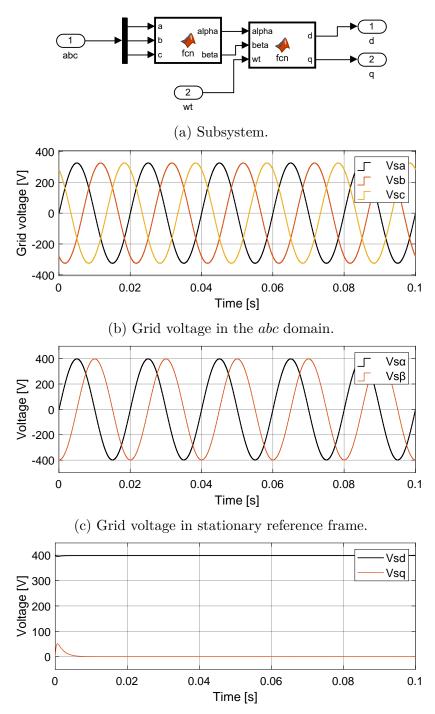

In VOC, coordinate transformation is used for simplifying three phase AC measurements into more manageable quantities which can be regulated inside control loops. After regulation, these quantities can be inverse transformed into AC values. There are specifically two types of transformations that can be implemented, Clarke and Park transformation. Clarke transformation is used to represent three phase values as two components in an orthogonal stationary frame, which is also called the  $\alpha\beta$  coordinate system [30, 31]. This transformation is illustrated in Figure 2.12b.

Figure 2.12: Three different reference frames, showing the abc (a),  $\alpha\beta$  (b) and dq (c) coordinate system with output signals [32].

By assuming a generic set of symmetrical and balanced three phase AC currents  $I_a$ ,  $I_b$  and  $I_c$  (120° displacement), the orthogonal components  $I_{\alpha}$  and  $I_{\beta}$  can be expressed as:

$$\mathbf{I}_{\alpha\beta0} = \mathbf{T}_{c} \mathbf{I}_{abc} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} I_{a} \\ I_{b} \\ I_{c} \end{bmatrix}$$

(2.18)

where the zero component is 0, due to balanced AC values. However, for calculating active and reactive power in the  $\alpha\beta$  domain, another variation of the Clarke transformation must be used instead. This is due to the transformation matrix  $\mathbf{T}_c$  not being unitary. For the preservation of power,  $\mathbf{T}_c$  must therefore be replaced

with another matrix that fulfils the general criteria:  $\mathbf{T}^*\mathbf{T} = \mathbf{T}\mathbf{T}^*$ . As derived in [33], the power invariant Clarke transformation can be expressed as:

$$\begin{bmatrix} I_{\alpha} \\ I_{\beta} \\ 0 \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} I_{a} \\ I_{b} \\ I_{c} \end{bmatrix}$$

(2.19)

The inverse Clarke transformation can then be given as:

$$\begin{bmatrix} I_a \\ I_b \\ I_c \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & 0 & \frac{1}{\sqrt{2}} \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} & \frac{1}{\sqrt{2}} \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} & \frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} I_\alpha \\ I_\beta \\ 0 \end{bmatrix}$$

(2.20)

The orthogonal  $\alpha\beta$  components represent two AC signals that rotate with a fixed frequency. By using Park transformation, these AC signals can be simplified to appear as DC quantities instead (Figure 2.12c). This is done by transforming the stationary  $\alpha\beta$  frame into a rotating reference frame, which is also called the dq coordinate system. By assuming that  $I_d$  and  $I_q$  are rotating with an arbitrary frequency, this transformation can be derived as:

$$\begin{bmatrix} I_d \\ I_q \\ 0 \end{bmatrix} = \mathbf{T}_p \mathbf{I}_{\alpha\beta} = \begin{bmatrix} \cos \theta & \sin \theta & 0 \\ -\sin \theta & \cos \theta & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} I_\alpha \\ I_\beta \\ 0 \end{bmatrix}$$

(2.21)

where the position is determined by  $\theta$ . Similarly to Clarke transformation, (2.21) has a zero component under the assumption of a balanced set of AC values. Clarke and Park transformation are often combined [34], so that a coordinate transformation from the *abc* time domain to the *dq* domain can be done in one step. This is possible by multiplying the transformation matrix in (2.20), with the one in (2.21). The resulting matrix  $\mathbf{T}_{cp}$ , can then be derived as:

$$\mathbf{T}_{cp} = \mathbf{T}_{p} \mathbf{T}_{c} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos \theta & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ -\sin \theta & -\sin(\theta - \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix}$$

(2.22)

The inverse transformation is:

$$\mathbf{T}_{cp}^{-1} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos \theta & -\sin \theta & \frac{1}{\sqrt{2}} \\ \cos(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{2\pi}{3}) & \frac{1}{\sqrt{2}} \\ \cos(\theta + \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) & \frac{1}{\sqrt{2}} \end{bmatrix}$$

(2.23)

For a coordinate transformation from the *abc* time domain to the dq domain,  $\mathbf{T}_{CP}$  from (2.22) can be used as:

$$I_{dq0} = \mathbf{T}_{cp} I_{abc} \tag{2.24}$$

In the case of VOC, (2.24) can be used directly to control AC signals as DC quantities in a dq synchronous reference frame. Afterwards, the transformation matrix in (2.23), is used to revert back to the AC domain. The goal of this entire process is to generate the desired AC signals to use as inputs in a PWM scheme.

#### 2.3.2 Pulse Width Modulation

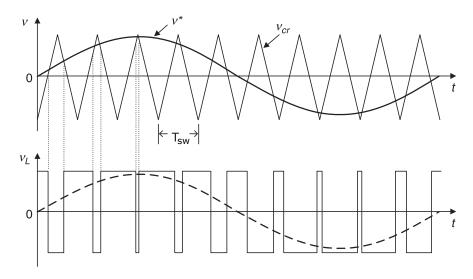

Previously, PWM has been described as a method of controlling the switching in an AFE rectifier. It has also been mentioned that the purpose of this is to ensure rectifier operation, by modulating the current drawn from the three phase AC source, in such a way that it stays in phase with the drawn voltage (Figure 2.11c). In VOC, this entire process is done inside a closed current control loop. Furthermore, the control loop utilizes Clarke and Park transformation to produce the necessary AC reference signals for the PWM module. Inside this module, the switching states are determined by comparing the input reference signals to triangular carrier signals. Due to the switching, the converter output current will have the shape of a pulsed waveform, with a fundamental component proportional to the reference signals. This type of PWM scheme is called Carrier Based Pulse Width Modulation (CBPWM) or sub-oscillation method [26, 35].

For simplicity, the characteristics of CBPWM can be analysed in a one phase inverter with an open loop topology. This allows for an easy presentation of the concept, by observing how PWM shapes a sinusoidal output from a DC voltage source. By picturing an arbitrary inverter with only two switches  $S_1$  and  $\overline{S}_1$ , the waveforms can then be illustrated as in Figure 2.13. In this case, a sinusoidal reference signal  $v^*$  is compared to a triangular carrier signal  $v_{cr}$ . The output is

Figure 2.13: Waveforms of carrier based PWM, showing the comparison of reference signal  $v^*$  and control signal  $v_{cr}$ , with resulting output  $(v_L)$  over an arbitrary RLC load [25].

a result of this comparison, where the complimentary switches are turned on or off (never simultaneously) based on the instantaneous values of the signals. From observing the waveforms, the on/off conditions can therefore be expressed as:

$$v^* > v_{cr}, \qquad S_1 \text{ is on}$$

or

$$v^* < v_{cr}, \quad \overline{S}_1 \text{ is on}$$

Due to the sinusoidal nature of the reference signal, the switching duty-cycle varies with the time period. This causes the pulsed output to have a varying thickness, effectively modulating a sinusoidal waveform. The smoothness of this sinusoid is dependent on the switching frequency, which is controlled by the triangular carrier signal. For a smoother sinusoidal output, the carrier frequency  $(f_{sw})$  must therefore be increased. In practice, this increases the density of the pulsed outputs, which shapes a sinusoid resembling signal. However, the actual output can never be a perfect sinusoid, and will always contain harmonic components of the fundamental frequency  $f_1$  [17].

The fundamental frequency of the sinusoidal output is the same as for the reference signal, i.e.  $f_1$  is determined by  $v^*$ . The ratio between the switching frequency and

$f_1$  is called the frequency modulation ratio  $m_f$ , and can be expressed as [17]:

$$m_f = \frac{f_{sw}}{f_1} \tag{2.25}$$

This ratio is used to describe the harmonic output components of  $f_1$ . In the frequency domain, they appear as side-bands centred around multiples of  $m_f$ . The amplitudes of these harmonics are connected to another important term used when describing PWM, namely the amplitude modulation ratio  $m_a$ . This is the ratio between the amplitude of  $v^*$  and  $v_{cr}$ , and can be expressed as:

$$m_a = \frac{\hat{v}^*}{\hat{v}_{cr}} \tag{2.26}$$

By observing the waveform, it is clear that this ratio should stay  $m_a \leq 1$ . Otherwise, due to the reference signal having a larger amplitude than the carrier, some switching cycles will be skipped. During  $m_a > 1$ , the PWM is operating in the overmodulation region. This region is characterized by the non-linear relationship between the fundamental-frequency and  $m_a$ . During overmodulation, the PWM will produce more output harmonics, and if  $m_a$  is high enough, the output will degenerate to a square wave [17].

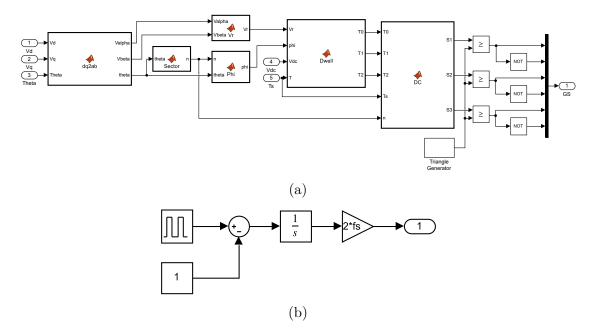

For a three phase topology, the basic principles for CBPWM remain the same. However, a more sophisticated PWM scheme is often utilized instead: Space Vector Modulation (SVM). This is due to its higher efficiency and ability to produce lower harmonics in comparison to CBPWM [36–39]. SVM is also a popular scheme to employ in VOC [40–42]. Given its superiority and wide application, it seems only natural to describe this method in more detail.

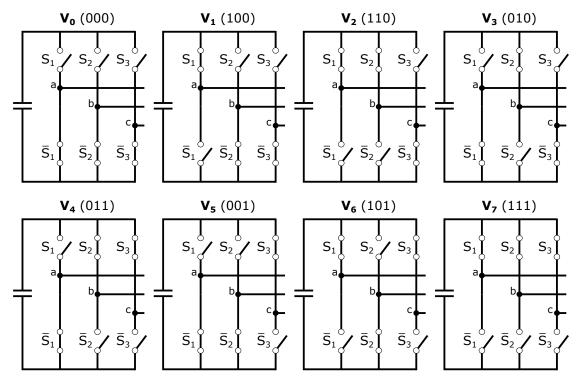

#### Space Vector Modulation

In SVM, the fundamental principle is based on representing each switching state in a converter as stationary space vectors, placed inside a  $\alpha\beta$  reference frame. For a three phase, two level converter, there are a limited amount of switching combinations. Considering that each half bridge (also called leg) must have one switch that is on while the other is off (complementary switches), the number of possible switching combinations are:  $2^3 = 8$  different combinations or specific converter states. For simplicity, an inverter is used to illustrate these states in Figure 2.14a. Every combination can be described with a three digit number,

where every digit represents the on/off state of the upper switch on each arm (1 or 0). Notice that there are two combinations where the bridge won't conduct any current, (000) and (111). These two are called zero states, while the remaining six are called active states. In Figure 2.14b, the angular position of each active state can be seen in reference to a three phase cycle.

(a) The eight switching states of an three phase, two level inverter.

(b) The switching states in relative posistion to the three phase voltages  $v_a(t), v_b(t)$  and  $v_c(t)$ .

Figure 2.14: Switching states in reference to the circuit (a), and angular position (b) [43].

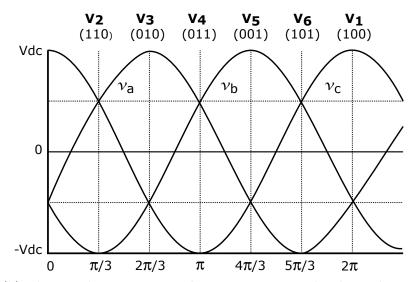

By knowing the angular position of each switching state, the voltages  $v_a(t)$ ,  $v_b(t)$  and  $v_c(t)$  at each instant can be represented as stationary vectors by using Clarke transformation. The equation for this transformation was presented in the previous

section. Equation (2.18) can in this case be applied as [25]:

$$\mathbf{v} = \frac{2}{3}(v_a(t) + v_b(t)e^{j2\pi/3} + v_c(t)e^{-j2\pi/3})$$

(2.27)

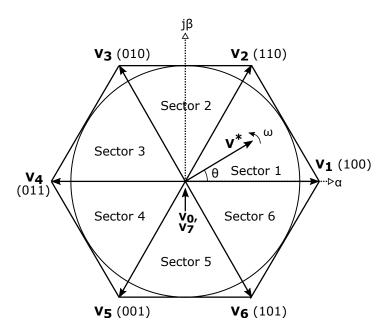

The resulting vectors are illustrated in Figure 2.15. The zero vectors  $\mathbf{v}_0$  and  $\mathbf{v}_7$  are located in the origin, while the active vectors  $\mathbf{v}_1$ - $\mathbf{v}_6$  point outwards with an angle of 60° between them. Two adjacent vectors form a sector, giving a total of six sectors. By connecting the tip of each active vector, the resulting shape forms a hexagon. This is due to the vectors being evenly spaced, with the same maximum amplitude of  $2v_{dc}/3$  [44].

Figure 2.15: Switching states represented as stationary vectors, and  $v^*$  formed by adjecent vectors.

To rotate through one 360° cycle during a time period, each sector must be activated in sequence. This can be done by alternating between two active vectors spanning the same sector, increasing the duty cycle of the vector neighbouring the next sector, while decreasing the other. This transition can be tracked with a reference voltage  $\mathbf{v}^*$ , which rotates counter clockwise with the angular speed  $\omega$ . This means that any reference vector can be synthesized using the adjacent vectors  $\mathbf{v}_k$  and  $\mathbf{v}_{k+1}$ , of the respective sector k.<sup>5</sup> In practice, this is done by sampling  $\mathbf{v}^*$  with a fixed clock frequency  $2f_{sw} = 1/T_s$ , where  $T_s$  is the sampling period. During sampling, the adjecent vectors are applied for a time  $t_k$  and  $t_{k+1}$ . However,

$<sup>^5</sup>$ For sector six the adjacent vectors will be  $\boldsymbol{v}_6$  and  $\boldsymbol{v}_1$

the allowable length of the reference vector is  $\mathbf{v}^*/\sqrt{3}$  [26]. Therefore, to control the modulation index, zero vectors must be applied for a time  $t_{0,7}$  during the sampling. Furthermore, the respective duty cycle for each vector is:  $t_k/T_s$ ,  $t_{k+1}/T_s$  and  $t_{0,7}/T_s$ . To summarize,  $\mathbf{v}^*$  and  $T_s$  can be expressed with the following equations [25]:

$$v^* = \frac{v_k t_k + v_{k+1} t_{k+1} + v_{0,7} t_{0,7}}{T_s}$$

(2.28)

$$T_s = t_k + t_{k+1} + t_0 (2.29)$$

By defining the angle of  $v^*$  as  $\theta^*$ , and  $\theta_k$  as the angle of  $v_k$ , application times can be expressed through trigonometric relations:

$$t_{k} = \frac{3T|\mathbf{v}^{*}|}{2v_{dc}}(\cos(\theta^{*} - \theta_{k}) - \frac{\sin(\theta^{*} - \theta_{k})}{\sqrt{3}})$$

(2.30)

$$t_{k+1} = \frac{3T|\mathbf{v}^*|}{v_{dc}} \frac{\sin(\theta^* - \theta_k)}{\sqrt{3}}$$

(2.31)

$$t_{0,7} = T_s - t_k - t_{k+1} = t_0 + t_7 (2.32)$$

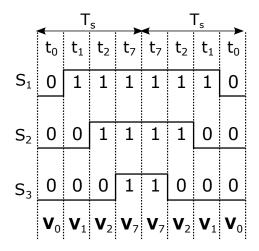

There are many variants of SVM, but (2.30), (2.31) and (2.32) are valid for all. The only difference between the various SVM techniques, is placement and duration of the zero vectors. However, the total duration of  $\mathbf{v}_0$  and  $\mathbf{v}_7$  must fulfil (2.32). The most common way to implement SVM, is with symmetrical zero states [26]. This implies that the remaining sampling time after one switching cycle, is distributed equally among the zero state durations. In this case, the relationship between  $t_0$  and  $t_7$  can be expressed as:

$$t_0 = t_7 = \frac{T_s - t_k - t_{k+1}}{2} \tag{2.33}$$

An example of SVM with symmetrical zero states is illustrated in Figure 2.16. This figure shows the relationship between vector placement, duration, and generation of gating pulses for sector one.

Figure 2.16: Conventional SVM with symmetrical zero states [26].

### 2.3.3 Voltage Oriented Control

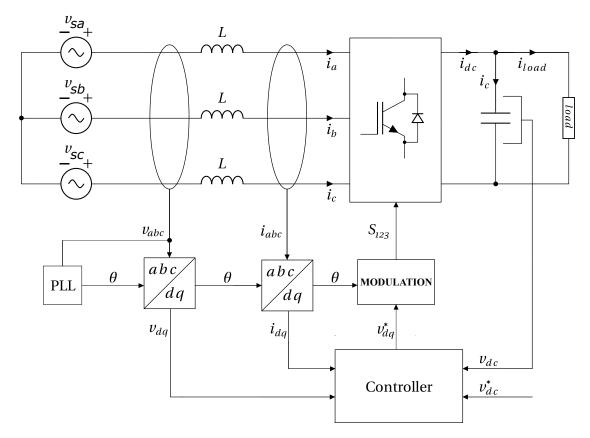

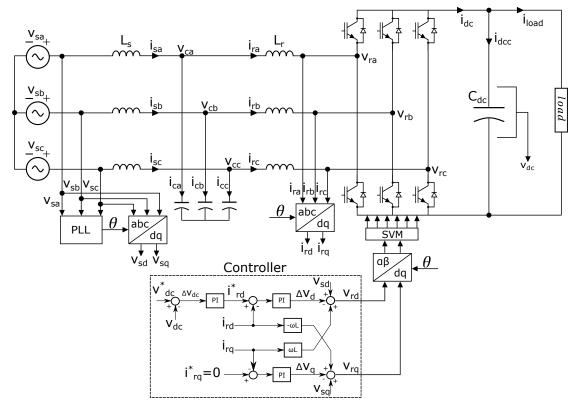

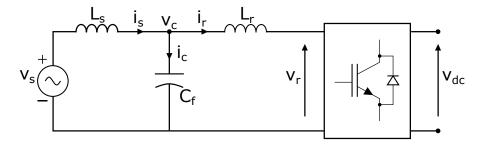

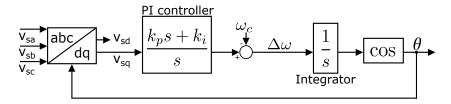

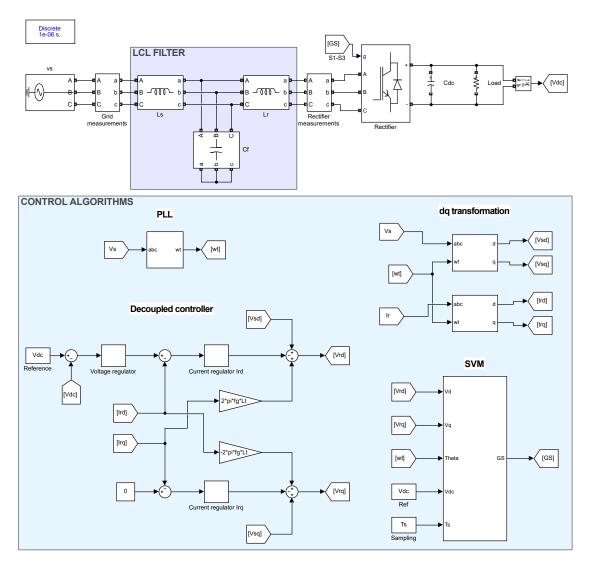

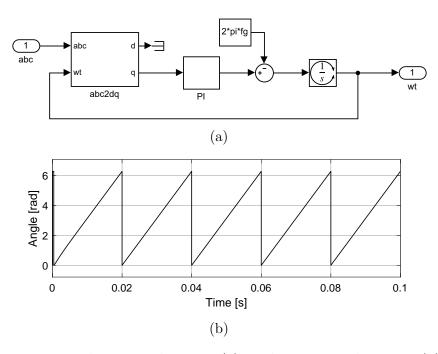

A block diagram of VOC applied to an AFE rectifier is illustrated in Figure 2.17. The blocks labelled abc/dq, transform the line voltage and current measurements from the abc domain to the dq synchronous reference frame. These dq values are then regulated by a controller with respect to the DC voltage measurement  $v_{dc}$  and reference  $v_{dc}^*$ . By utilizing feedback loops and PI regulators, the controller produces the desired control signals  $\mathbf{v}_{dq}^* = [v_d^*, v_q^*]$ . These are essentially templates for a PWM scheme. As explained in section 2.3.2, there are different PWM schemes. Therefore, depending on the scheme,  $\mathbf{v}_{dq}^*$  must be transformed to either the  $\alpha\beta$  or abc domain. For simplicity, the block containing a coordinate transformation and PWM module, is simply labelled "modulation". Six gating signals are produced from this block, one for each transistor. Given that current measurements are being taken continuously, the controller will adapt and produce the necessary control signals for maintaining rectification. This completes the control loop that makes up VOC. There are, however, more details concerning the controller, and the Phase Locked Loop (PLL) which has not been mentioned yet.

In Figure 2.17, a block labelled PLL can be seen connected to the voltage supply and various other blocks utilizing the Park transformation. As mentioned in the introduction, the grid measurements are to be controlled in the dq synchronous reference frame. For this transformation to be possible, an angle  $\theta$  is needed for positioning the dq reference frame. However, considering that this coordinate system is continuously rotating with a fixed frequency,  $\theta$  will also be constantly changing. It is therefore convenient to refer to the instantaneous angle in terms

$<sup>^6</sup>$ see section 2.3.1 for coordinate transformation

Figure 2.17: General block diagram of VOC applied to an AFE rectifier.

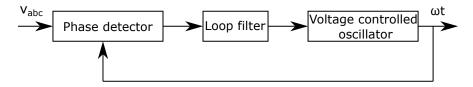

of angular frequency and time, so that  $\omega t = \theta$ . Furthermore, the PLL is used to extract this angle from the grid. More specifically, the PLL is a feedback circuit that generates a phase angle with the same angular frequency as the input signals. There are many variations of this type of circuit, but they all contain the three main components: a phase detector, loop filter, and voltage controlled oscillator [45–47]. A block diagram of a generic PLL can be seen in Figure 2.18. Due to the focus of this section, the process of each component will not be explained in detail.

Figure 2.18: Block diagram of a generic PLL.

By using a PLL to extract the phase angle from the three phase voltage source,  $\omega t$  can be used to transform the AC measurements to DC quantities. For this

transformation, the previously given (2.24) can be written as:

$$\begin{bmatrix} x_d \\ x_q \\ 0 \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos \omega t & \cos(\omega t - \frac{2\pi}{3}) & \cos(\omega t + \frac{2\pi}{3}) \\ -\sin \omega t & -\sin(\omega t - \frac{2\pi}{3}) & -\sin(\omega t + \frac{2\pi}{3}) \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} x_a \\ x_b \\ x_c \end{bmatrix}$$

(2.34)

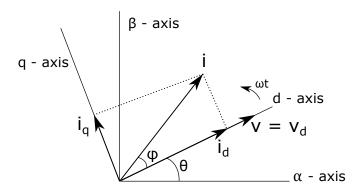

where  $\boldsymbol{x}_{abc}$  is voltage or current. By applying the transformation to both three phase measurements, the resulting dq components can be controlled independently as  $\boldsymbol{i} = [i_d, i_q]$  and  $\boldsymbol{v} = [v_d, v_q]$ . Both vectors are drawn inside an vector diagram in Figure 2.19. The  $\alpha\beta$  coordinate system is included in the diagram as a rotational reference for the dq coordinates. Considering that the phase angle  $\omega t$  is obtained from voltage measurements, the d-axis can be aligned with the voltage vector  $\boldsymbol{v}$ . This makes it easier to decouple the vector. The equations for  $v_d$  and  $v_q$  can then be given as in [26]:

$$v_d = L\frac{di_d}{dt} + v_d^* - \omega Li_q \tag{2.35}$$

$$v_q = L\frac{di_q}{dt} + v_q^* + \omega Li_d \tag{2.36}$$

Figure 2.19: Transformed voltage and current measurements, with respective vectors  $\boldsymbol{v}$  and  $\boldsymbol{i}$ .

To align the voltage vector with the d-axis,  $v_q$  must be set to zero so that  $\mathbf{v} = v_d$ . Furthermore, to ensure rectification with Unity Power Factor (UPF), the current vector i must be aligned with the voltage vector and d-axis. This is because of the relationship between the power and current dq components, which can be interpreted as  $i_d$  controlling the active power, and  $i_q$  determining the reactive power. It is therefore evident that  $i_q$  must be equal to 0. In reference to Figure

2.17, all these operations are done in the controller, i.e. (2.35) and (2.36) are manipulated inside a decoupled current controller. Assuming the q-axis current is regulated to zero, and voltage vector is aligned with both  $\boldsymbol{i}$  and  $\boldsymbol{v}$ , equation (2.35) and (2.36) can be reduced to:

$$v_d = L\frac{di_d}{dt} + v_d^* \tag{2.37}$$

$$0 = v_q^* - \omega L i_q \tag{2.38}$$

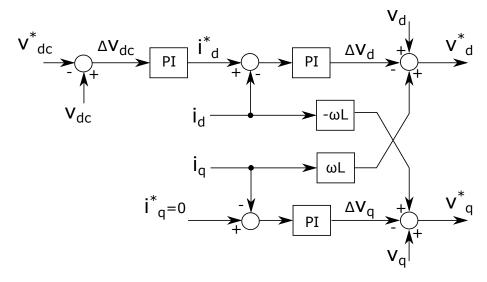

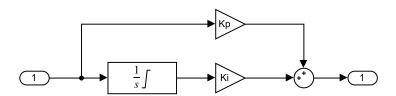

A block diagram of the controller can be seen in Figure 2.20. PI regulators are used to minimize the error signals over time by adjustment of the control variables [48]. For  $\Delta v_d$  and  $\Delta v_q$ , this relationship can be expressed as:

$$\Delta v_d = k_p (i_d^* - i_d) + k_i \int (i_d^* - i_d) dt$$

(2.39)

$$\Delta v_q = k_p (i_q^* - i_q) + k_i \int (i_q^* - i_q) dt$$

(2.40)

where  $k_p$  is the proportional gain and  $k_i$  is the integral gain. The resulting control signals from the current controller can be expressed as:

$$v_d^* = v_d + \omega L i_q - \Delta v_d \tag{2.41}$$

$$v_q^* = v_q - \omega L i_d - \Delta v_q \tag{2.42}$$

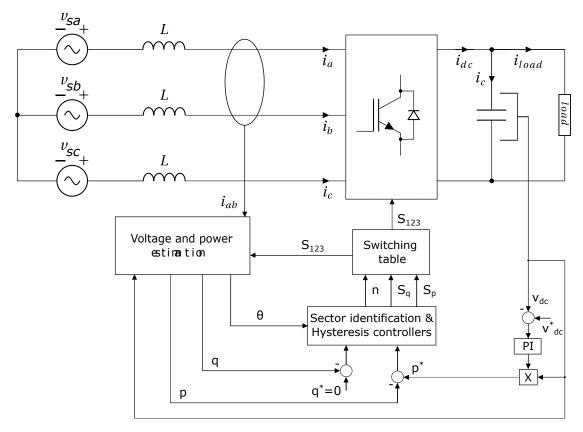

#### 2.3.4 Direct Power Control

The main principle behind DPC is to directly control the instantaneous active p and reactive q power flowing through the converter. This control scheme can be applied to an AFE rectifier as seen in Figure 2.21 [49, 50]. The switching states of the converter are selected from a table, which is, in essence, determined by the angular position of the terminal voltage vector and instantaneous power errors. To obtain these values, the power source voltages must first be calculated. However, considering that the system is without voltage sensors, an estimation technique

Figure 2.20: Block diagram of the current controller [26].

can be used to obtain the instantaneous power and then subsequently the line voltage in the  $\alpha\beta$  domain.

The line voltages can then be given as [49]:

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \frac{1}{i_{\alpha}^{2} + i_{\beta}^{2}} \begin{bmatrix} i_{\alpha} & -i_{\beta} \\ i_{\beta} & i_{\alpha} \end{bmatrix} \begin{bmatrix} p \\ q \end{bmatrix}$$

(2.43)

where the instantaneous active and reactive powers are given as [26]:

$$p = L(\frac{di_a}{dt}i_a + \frac{di_b}{dt}i_b + \frac{di_c}{dt}i_c) + v_{dc}(S_1ia + S_2i_b + S_3i_c)$$

(2.44)

$$q = \frac{1}{\sqrt{3}} \left\{ 3L \left( \frac{di_a}{dt} i_c - \frac{di_c}{dt} i_a \right) - v_{dc} \left[ S_1(i_b - i_c) + S_2(i_c - i_a) + S_3(i_a - i_b) \right] \right\}$$

(2.45)

The calculated power from the equations above are compared with the instantaneous reference values to produce errors. The active power reference  $p^*$  is obtained from the outer DC voltage loop while the reactive power command  $q^*$  is provided by an external signal. Furthermore, to obtain UPF,  $q^*$  is therefore set as  $q^* = 0$ . The error values from the comparison are quantised by hysteresis controllers as binary outputs defined as  $S_p$  and  $S_q$ . The controllers try to match the instantaneous power with the reference by limiting the error within hysteresis bands, defined as  $H_p$  and  $H_q$ . This means that the controller will give 1 as an output if the power

Figure 2.21: Block diagram of DPC applied to an AFE rectifier

goes beyond the lower band, or 0 if the power goes above the higher band. In the case of the active hysteresis controller, this can be expressed as:

$$S_q = \begin{cases} 1, & q < q^* - H_q \\ 0, & q > q^* + H_q \end{cases}$$

(2.46)

For the reactive hysteresis controller the binary states can similarly be given as:

$$S_p = \begin{cases} 1, & p < p^* - H_p \\ 0, & p > p^* + H_p \end{cases}$$

(2.47)

The hysteresis controller outputs are combined with the angle  $\theta = \arctan(u_{\alpha}/u_{\beta})$ , of the terminal voltage vector to determine the switching state. More specifically, the region of the voltage vector is divided into twelve sectors, and  $\theta$  is used to identify which sector the vector is positioned in. The respective angular region for

each sector can be expressed as:

$$(n-2)\frac{\pi}{6} \le \theta_n < (n-1)\frac{\pi}{6}, \qquad n = [1, 12]$$

(2.48)

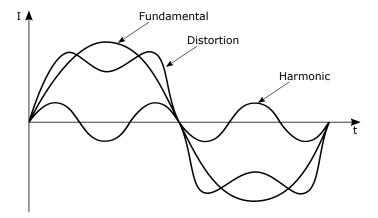

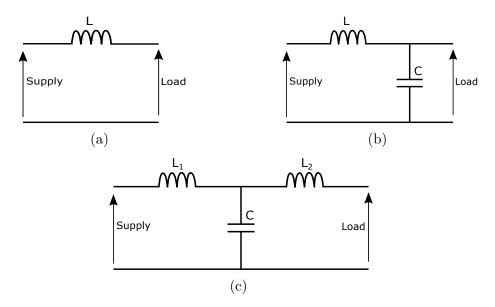

# 2.4 Harmonic Distortion

In power systems, disturbances are generally caused by loads without linear voltage/current characteristics (non-linear loads). Some examples of non-linear loads are transformers, rotating electric machines and all equipments with built in switching devices [51]. The reason such loads cause disturbances, is because they draw a deformed sinusoidal current (non-sinusoidal). This current is essentially a composite of harmonic waveforms, which are multiples of the fundamental frequency  $f_1$ . In other words, harmonics are higher frequency waveforms superimposed on  $f_1$ , and can therefore be expressed as:

$$f_h = f_1 \cdot h, \qquad h \in \mathbb{R}^+ \tag{2.49}$$

where h denotes the harmonic order. In a non-sinusoidal current, the summation of different harmonic components constitutes the distortion. Depending on the order, these harmonics can have a varying detrimental effect on electrical equipment and power systems [52–54]. Some categories of harmonics are: triplen harmonics, interharmonics, and sub-harmonics. The order of triplen harmonics are odd multiples of the third harmonic (h=3,9,15,...) and can cause overloading of the neutral wire in grounded-wye systems. If the harmonic order is not an integer multiple of the fundamental frequency, it is called an inter-harmonic. This type of harmonic can cause flicker, temperature rise, and malfunctioning of protective relays [55]. The rarest form of harmonics found in power systems are sub-harmonics. These can have a frequency which is below the fundamental frequency and can cause voltage modulation with visual flicker [56]. A current or voltage waveform can, to some degree, contain all these categories (and others) of harmonics.

A non-sinusoidal waveform can contain a whole spectre of different harmonics. It is therefore practical to use the common term Total Harmonic Distortion (THD), for describing the harmonic content of a distorted waveform. More specifically, THD is a percentage measure of the ratio between the RMS amplitude of a set of higher harmonic frequencies to the RMS amplitude of the fundamental frequency [57, 58]. An equation for this relationship can be derived by using Fourier analysis.

Figure 2.22: The effect of harmonic distortion.

Furthermore, any repeating waveform f(t) that satisfies the Dirichlet conditions can be expressed with the following Fourier expansion [59]:<sup>7</sup>

$$f(t) = a_0 + \sum_{h=1}^{\infty} [a_h \cos(h\omega t) + b_h \sin(h\omega t)]$$

(2.50)

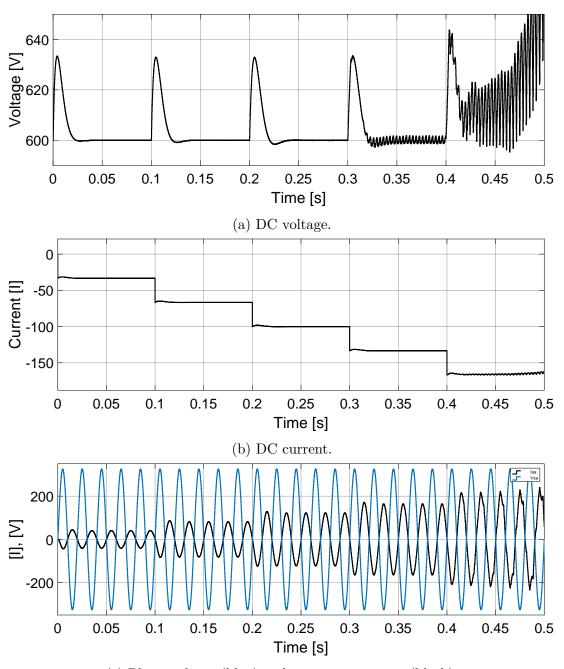

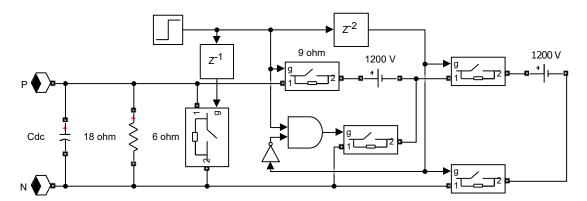

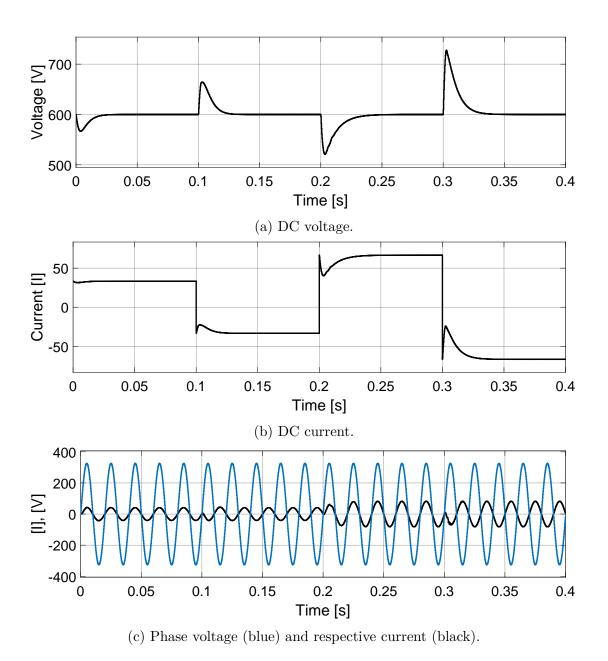

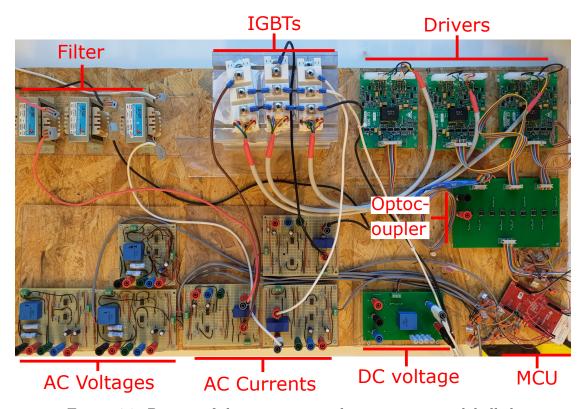

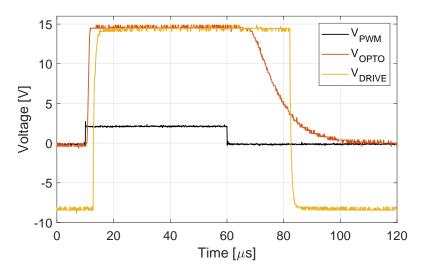

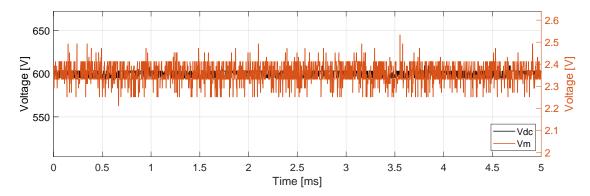

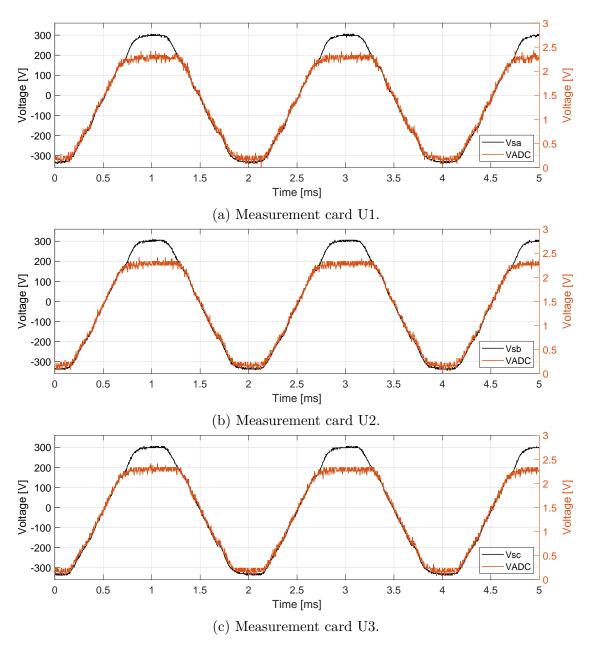

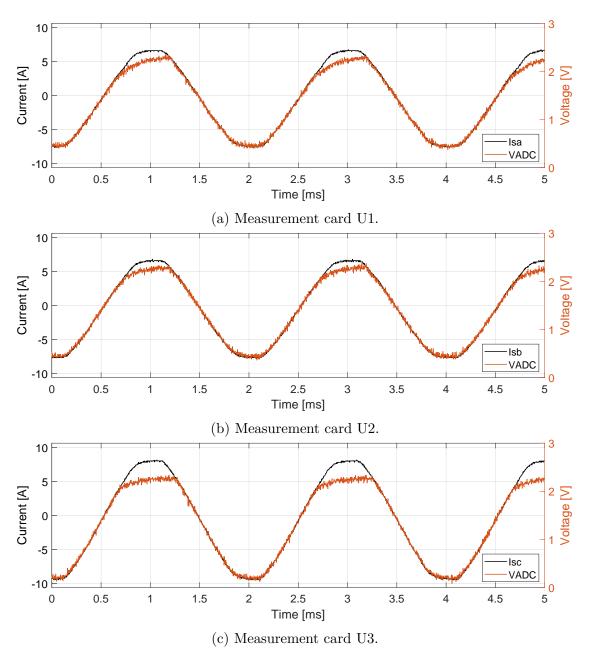

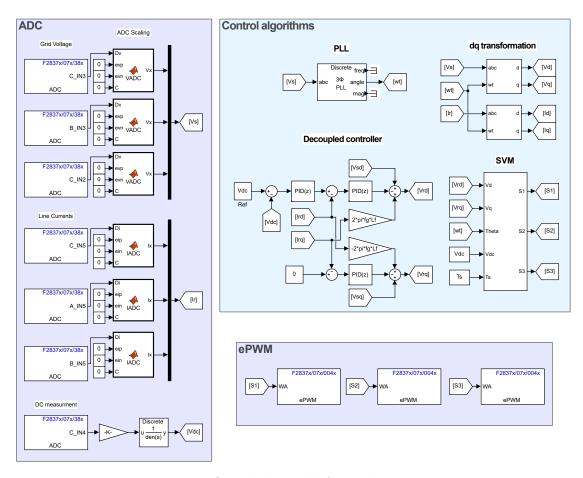

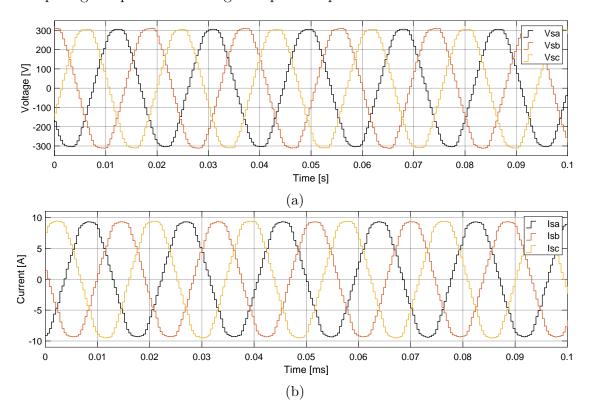

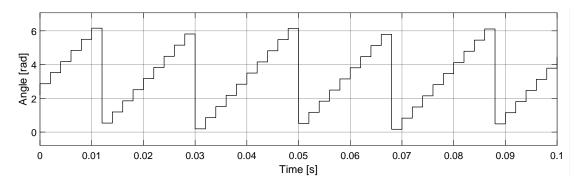

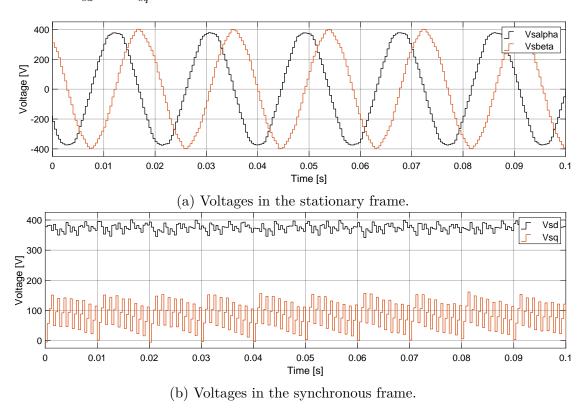

where  $\omega$  is the angular frequency. The average value  $a_0$ , and Fourier coefficients  $a_h$  and  $b_h$  can be given as: