# Design of Readout Electronics for the DEEP Particle Detector

Bendik Husa

Master's thesis in Physics

University of Bergen Department of Physics and Technology

November, 2021

#### Acknowledgements

I would like to extend my gratitude to my supervisor Kjetil Ullaland. I am grateful for being given the opportunity to work on this very interesting project, for all the helpful discussions we had, and for receiving good answers to every question I had along the way. I also want to thank Senior Engineer Shiming Yang. Your knowledge of PCB design has been an invaluable resource, and I always left your office with more knowledge than I had when going in. Thank you, Hilde Nesse Tyssøy for very helpful feedback on my thesis, and for providing insight into the world of particle precipitation.

I want to thank my friends on the third floor, Birger, Thomas, Amalie and Håvard for making this year memorable and for all the useful (and not so useful) discussions we had. A big thanks to Tobias Heggeli for proofreading and providing feedback on my thesis. Another thanks to Tarje Hillersøy and Vegard Milde for help and discussion about many aspects of the thesis.

Lastly, I want to thank Heidi for all your support and help throughout this year, and for being who you are.

Abstract

Along with electromagnetic radiation, the Sun also emits a constant stream of charged particles in the form of solar wind. When these particles enter Earth's atmosphere through a process known as particle precipitation, they can through a series of chemical reactions produce  $NO_x$  and  $HO_x$  gases. These gases are greenhouse gases and deplete the ozone in the mesosphere and upper stratosphere. It is important to quantify the rate of production of these gases to model the potential climate impact. Existing particle detectors in space are suboptimal because they cannot determine the energy flux and pitch angle distribution of precipitating particles. The primary scientific objective of the DEEP project is to design a particle detector instrument that is specifically designed for particle precipitation measurements.

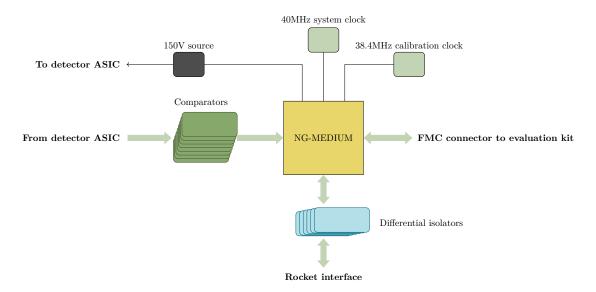

This thesis investigates different data acquisition schemes for handling the signal from a pixel detector. The chosen approach is measuring the width of a shaped pulse to quantify the energy of the particle. Known as Time-over-Threshold, a detector circuit board is designed featuring high-speed comparators as threshold discriminators and the NG-MEDIUM FPGA from NanoX-plore to implement the data acquisition.

Digitizing the comparator pulse width is done with a Time-to-Digital converter (TDC) implemented in the FPGA fabric. Since the difference in pulse width is small for different energies, a high conversion resolution is required. Two high-resolution TDCs are designed and compared, both of which feature a digital counter and a method of interpolating the counter clock period. The first interpolation method applies the use of a multitapped delay line implemented with hard carry chain resources, and the second method oversamples the input with several equally off-phase sampling clocks.

A resolution of 302 ps and a differential non-linearity of 3.26 was achieved with the delay line TDC clocked at 100 MHz. An automatic statistical calibration scheme is included to determine the actual delays of the delay line, utilizing a second asynchronous clock to generate uniformly distributed hits. The asynchronous oversampler resolution is clock frequency dependent and provides a 4-fold improvement to the clock period. The differential nonlinearity approaches zero with close matching of the off-phase clocks and operating frequency.

A complete firmware design for the data acquisition and rocket telemetry of the detector is proposed and demonstrated. A simulation of the firmware utilizing each TDC topology is conducted and the delay line TDC is demonstrated to be the most accurate at all operating frequencies and thus the recommended TDC for the DEEP data acquisition.

# Contents

| A        | crony          | /ms                                       | viii             |

|----------|----------------|-------------------------------------------|------------------|

| 1        | Intr           | oduction                                  | 1                |

|          | 1.1            | Scientific objective                      | 1                |

|          | 1.2            | Energetic particle precipitation (EPP)    | 1                |

|          |                | 1.2.1 Earth's atmosphere                  |                  |

|          |                | 1.2.2 Solar wind                          |                  |

|          |                | 1.2.3 The magnetosphere                   |                  |

|          |                | 1.2.4 Radiation belts                     |                  |

|          |                | 1.2.5 Particle precipitation              |                  |

|          |                | 1.2.6 Effects                             |                  |

|          | 1.3            | Detection                                 |                  |

|          |                | 1.3.1 NOAA POES MEPED                     |                  |

|          | 1.4            | Project background                        |                  |

| _        |                |                                           | _                |

| <b>2</b> |                | nciples of particle detection             | 7                |

|          | 2.1            | Amplification                             |                  |

|          | 2.2            | Pulse shaping                             |                  |

|          | 2.3            | Pile-up                                   |                  |

|          | 2.4            | Baseline shift                            |                  |

|          | 2.5            | Data acquisition                          |                  |

|          |                | 2.5.1 Analogue-to-Digital Conversion      |                  |

|          |                | 2.5.2 Time-over-Threshold $\ldots$        |                  |

|          |                | 2.5.3 Dynamic Time-over-Threshold         | 15               |

| 3        | $\mathbf{Sys}$ | tem overview and specifications           | <b>18</b>        |

|          | 3.1            | Detector house                            | 18               |

|          | 3.2            | Binning                                   | 20               |

|          | 3.3            | Sensor PCB                                | 21               |

|          | 3.4            | Rocket interface                          | 22               |

|          | 3.5            | Specifications                            | 23               |

| 4        | Ма             | nte Carlo simulation of EPP               | <b>25</b>        |

| 4        | 4.1            | Horizontal coincidence                    | <b>2</b> 5<br>27 |

|          | $4.1 \\ 4.2$   | Vertical coincidence                      |                  |

|          | 4.2            |                                           | 20               |

| <b>5</b> | Tin            | ne-to-digital conversion                  | <b>34</b>        |

|          | 5.1            | Performance measures                      | 34               |

|          |                | 5.1.1 Conversion in the presence of noise | 35               |

|          | 5.2            | Calibration methods                       | 36               |

|          |                | 5.2.1 Statistical calibration             | 36               |

|          |                | 5.2.2 Double registration                 | 37               |

|          |                | 5.2.3 Sliding scale                       | 37               |

|          | 5.3            | Other potential issues                    | 38               |

|          | 5.4            | Clock interpolation                       | 38               |

|    | 5.5  | Asynchronous oversampling                               | 39        |

|----|------|---------------------------------------------------------|-----------|

|    | 5.6  | Multitapped delay-lines                                 | 39        |

|    | 5.7  | Vernier delay-lines                                     | 40        |

|    | 5.8  | Looped delay lines                                      | 41        |

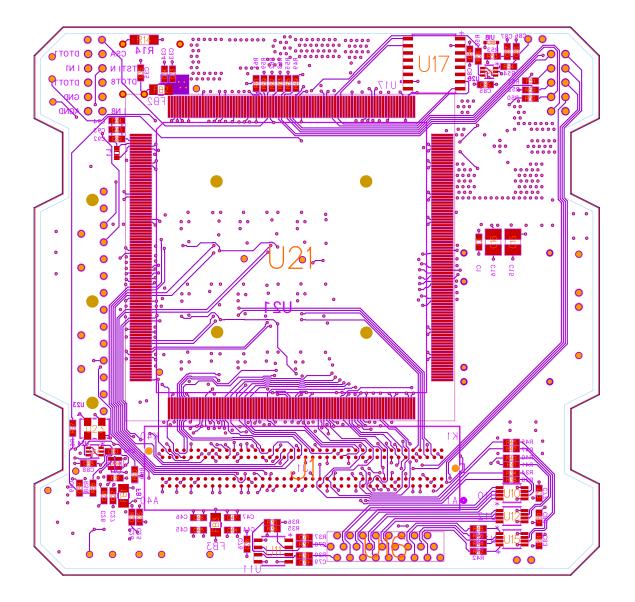

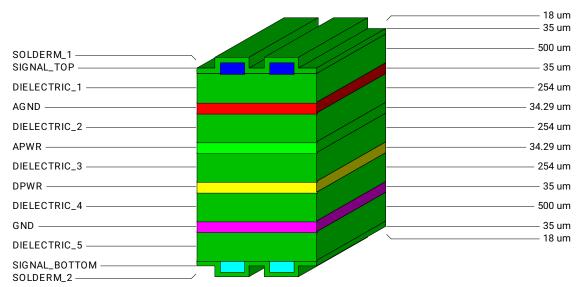

| 6  | PCI  | B design and layout                                     | 43        |

|    | 6.1  | PCB specifications                                      | 44        |

|    | 6.2  | PCB stackup                                             | 44        |

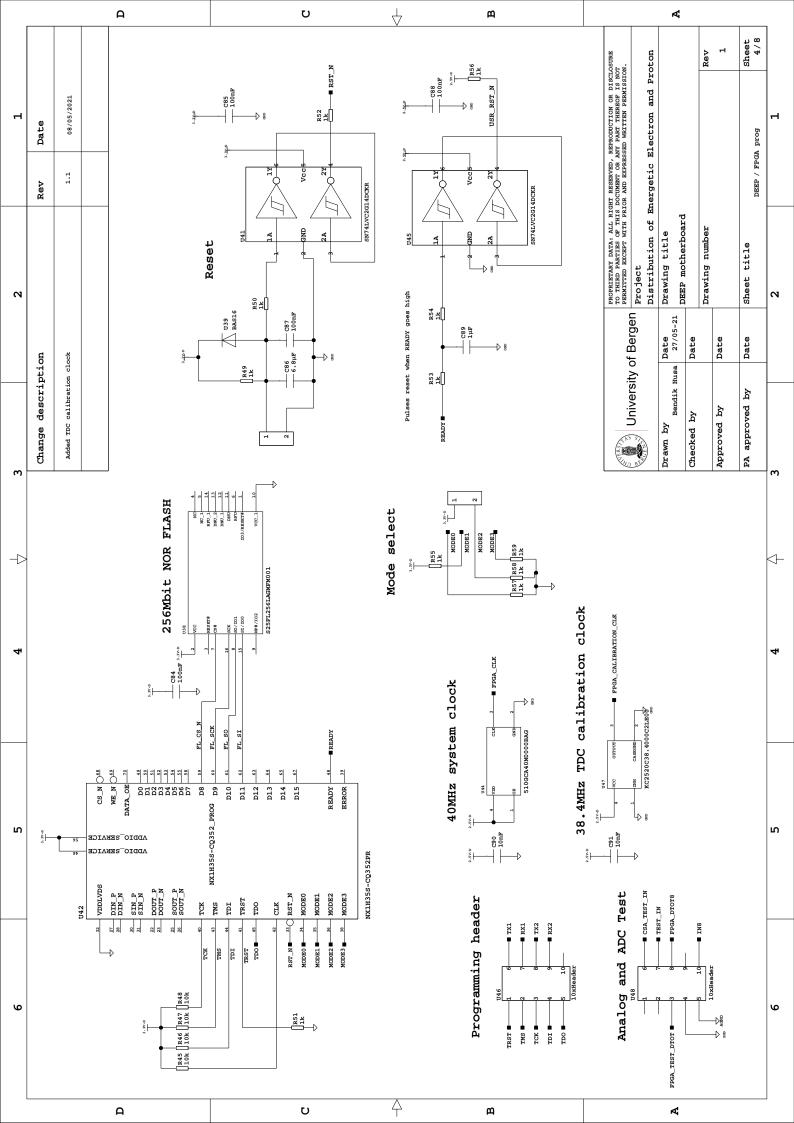

|    | 6.3  | FPGA                                                    | 45        |

|    |      | 6.3.1 Programming interface                             | 46        |

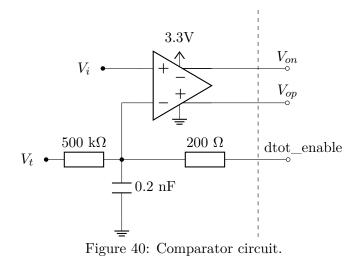

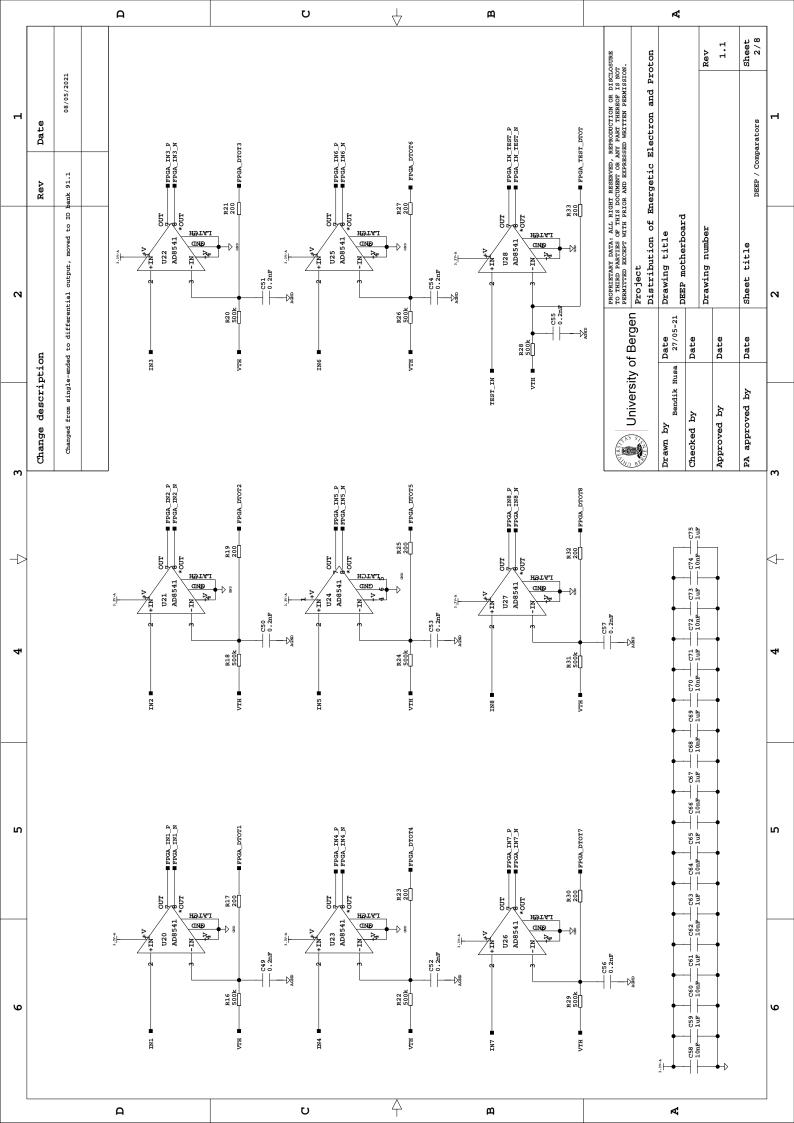

|    | 6.4  | Comparator circuits                                     | 47        |

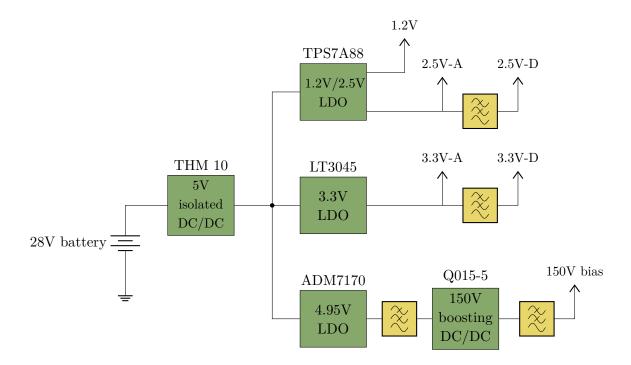

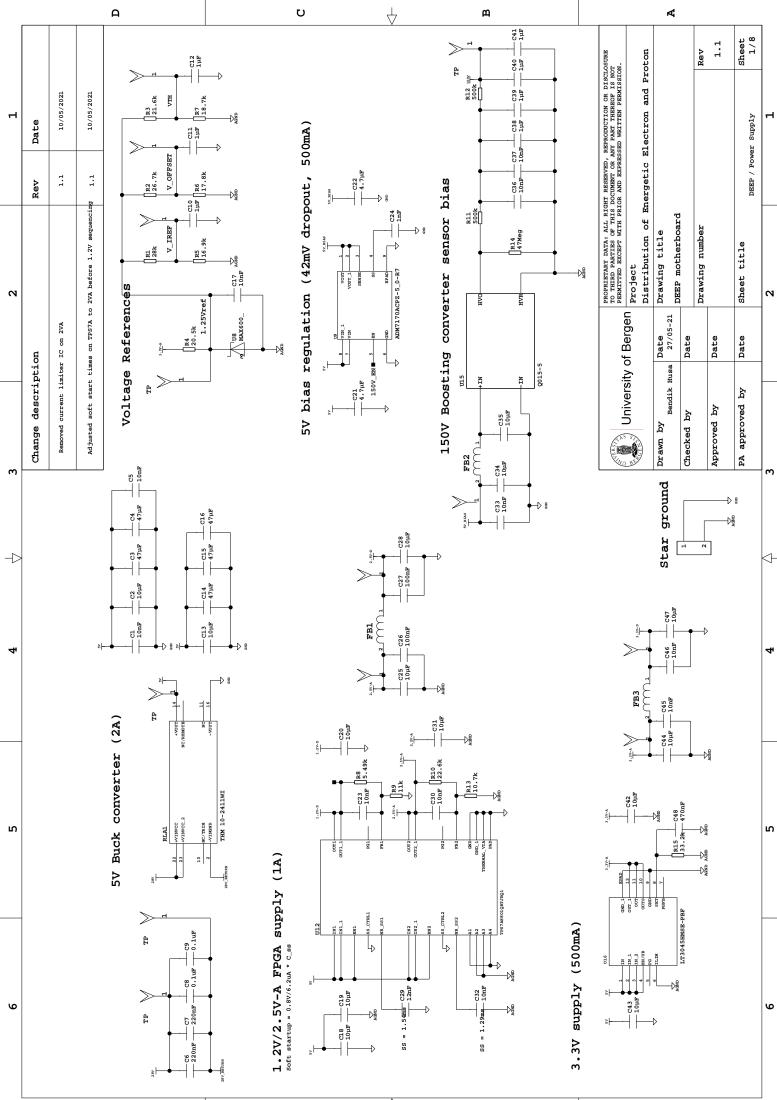

|    | 6.5  | Power delivery network                                  | 48        |

|    |      | 6.5.1 Bias supply                                       | 49        |

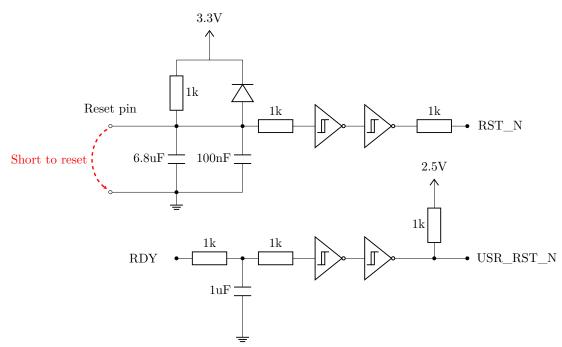

|    | 6.6  | Reset network                                           | 51        |

|    | 6.7  | Rocket interface                                        | 51        |

| 7  | Har  | dware testing                                           | <b>54</b> |

|    | 7.1  | Detector bias                                           | 54        |

|    | 7.2  | Comparator circuit                                      |           |

| 8  | Firm | nware implementation                                    | 60        |

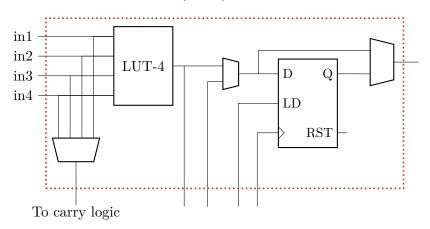

| 0  | 8.1  | NG-MEDIUM architecture                                  | 60        |

|    | 0.1  | 8.1.1 IO ring                                           | 60        |

|    |      | 8.1.2 Core logic                                        |           |

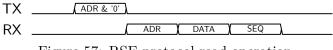

|    | 8.2  | RSE protocol                                            | 63        |

|    | 8.3  | Clock generation                                        | 64        |

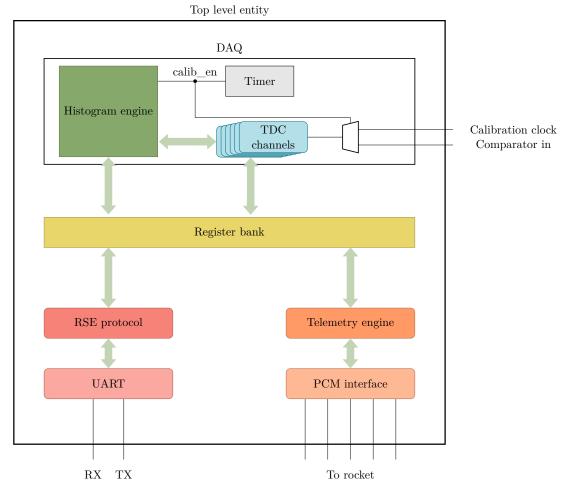

|    | 8.4  | Top level entity                                        | 64        |

|    | 8.5  | Time-to-digital converter                               | 65        |

|    | 0.0  | 8.5.1 Type I: Interpolationless counter                 | 66        |

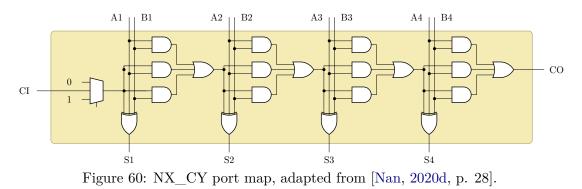

|    |      | 8.5.2 Type II: Counter with delay line interpolation    |           |

|    |      | 8.5.3 Type III: Counter with oversampling interpolation |           |

|    | 8.6  | Thermometer-to-binary encoder                           |           |

|    | 8.7  | Memory                                                  |           |

|    | 0.1  | 8.7.1 Transfer function ROM                             | 75        |

|    |      | 8.7.2 FIFO                                              | 76        |

|    |      | 8.7.3 Synchronization                                   | 77        |

|    | 8.8  | Histogram engine                                        | 77        |

|    |      | 8.8.1 Binning                                           | 78        |

|    | 8.9  | Coincidences                                            | 80        |

|    |      | 8.9.1 Horizontal coincidence check                      | 80        |

|    |      | 8.9.2 Multi-hit capability and pipelining               | 81        |

|    | 8.10 | Calibration                                             | 82        |

|    |      | Telemetry communication                                 | 87        |

| 9  | GA   | <b>FE/VHDL</b> testbench framework                      | 90        |

| 10 |      | '<br>ults and discussion                                | 92        |

|    |      |                                                         |           |

| 11 | Sum  | nmary and conclusion                                    | <b>97</b> |

|              | 11.1 Conclusion                                                        |     |

|--------------|------------------------------------------------------------------------|-----|

| A            | ppendices                                                              | 103 |

| $\mathbf{A}$ | Pinout                                                                 | 103 |

| в            | Register map                                                           | 104 |

| С            | Code         C.1 NX_CY delay line         C.2 Asynchronous oversampler |     |

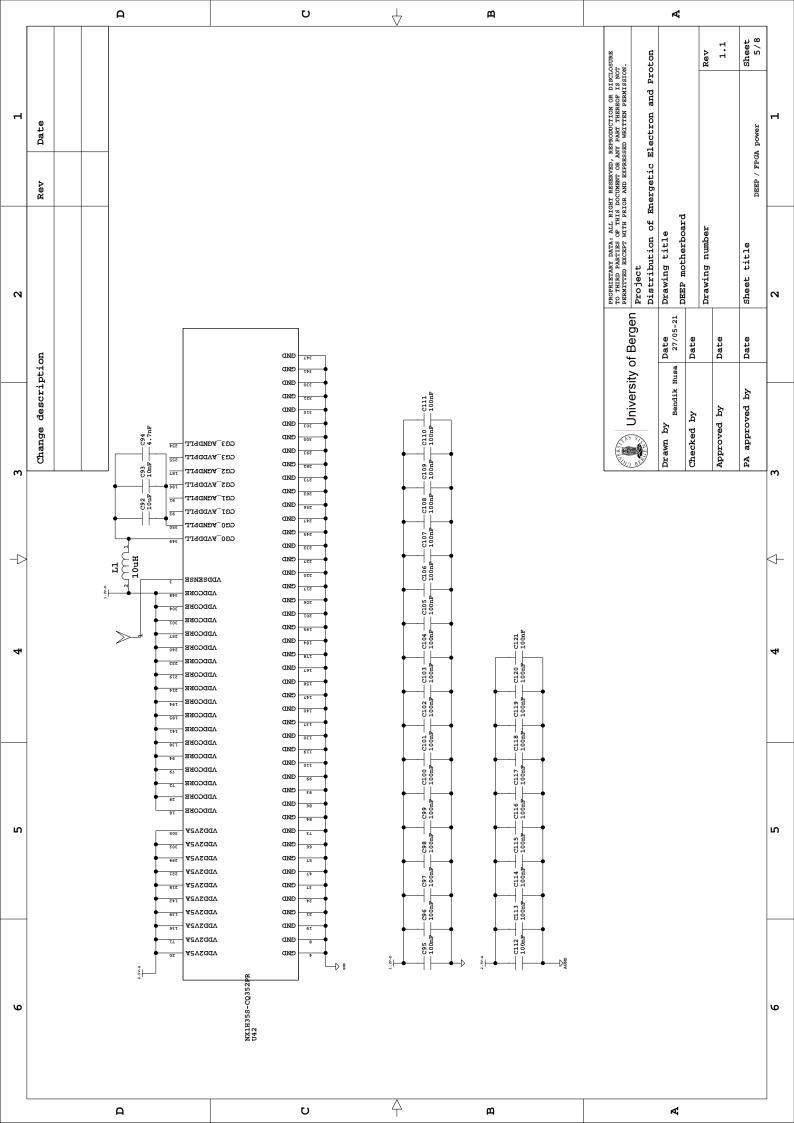

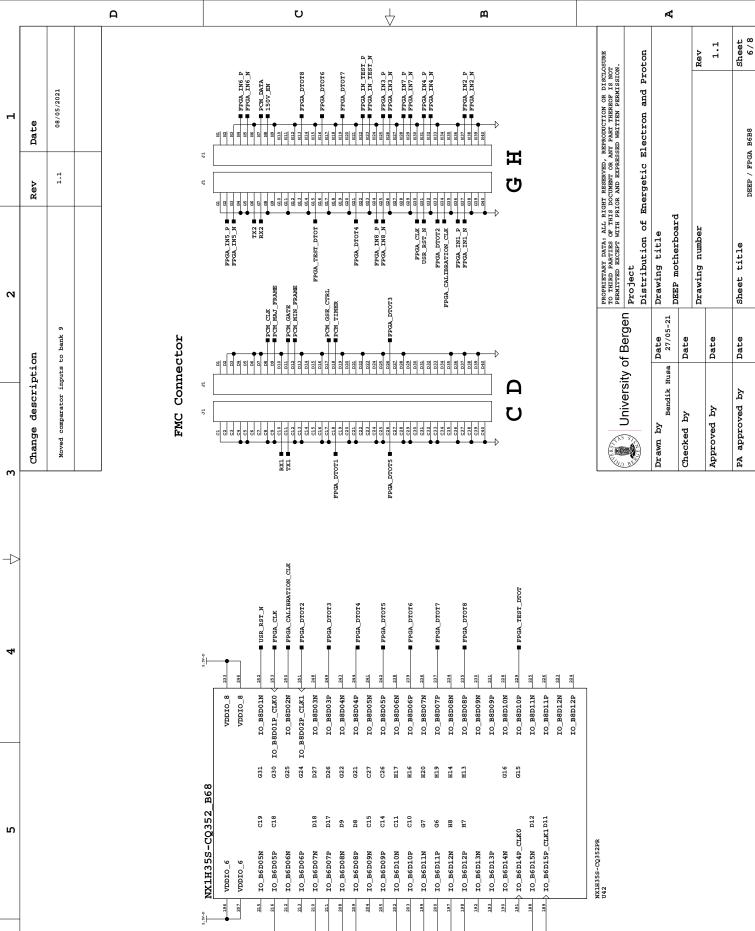

| D            | Schematic                                                              | 108 |

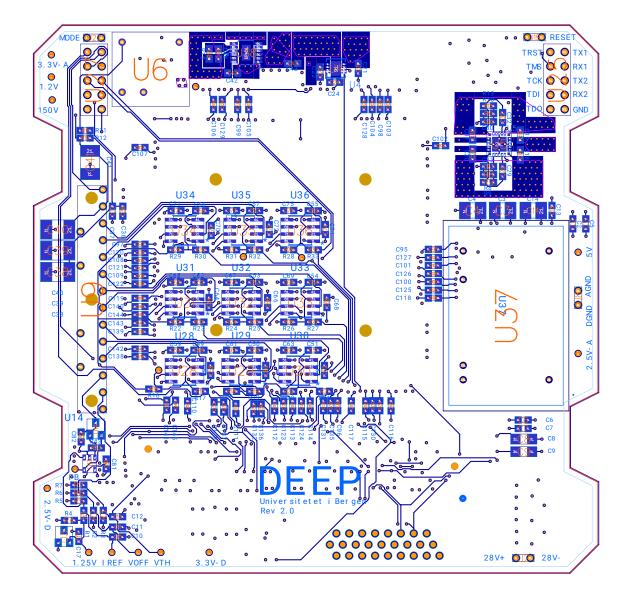

| $\mathbf{E}$ | Layout                                                                 | 117 |

### Acronyms

- ADC Analog-to-Digital Converter.

- ASC Andøya Space Centre.

- ASIC Application Specific Integrated Circuit.

BCSS Birkeland Centre for Space Science.

BRAM Block RAM.

**CERN** European Organization for Nuclear Research.

CGB Coarse Grain Block.

CI Carry In.

**CKS** Clock Generation Switch.

**CMOS** Complementary Metal–Oxide–Semiconductor.

CO Carry Out.

CSA Charge Sensitive Amplifier.

${\bf CSV}$  Comma-separated values.

DAQ Data Acquisition.

**DEEP** Distribution of Energetic Electrons and Protons.

**DLL** Delay-Locked Loop.

**DNL** Differential non-linearity.

**DSP** Digital Signal Processor.

**dToT** Dynamic Time-over-Threshold.

**EDAC** Error Detection and Correction.

**ENOB** Effective Number of Bits.

**EPP** Energetic particle precipitation.

**FE** Functional Element.

FIFO First In First Out.

FMC FPGA Mezzanine Connector.

FPGA Field Programmable Gate Array.

**FSM** Finite State Machine.

# ${\bf GATE}\,$ GEANT4 Application for Emission Tomography.

**ICI** Investigation of Cusp Irregularities.

JTAG Joint Test Action Group.

LDO Low Dropout Linear Regulator.

LSB Least Significant Bit.

${\bf LUT}$  Lookup Table.

**PCB** Printed Circuit Board.

$\mathbf{PCM}\xspace$  Pulse Code Modulation.

**PLL** Phase-Locked Loop.

$\mathbf{PVT}\,$  Process, Voltage and Temperature.

**RFB** Register File Block.

**ROM** Read Only Memory.

**RSE** Radiation Shutter Electronics.

**SDF** Standard Delay Format.

**SERDES** Serializer-Deserializer.

**SMILE** Solar wind Magnetosphere Ionosphere Link Explorer.

**SNR** Signal-to-Noise Ratio.

**SPI** Serial Peripheral Interface.

${\bf SRAM}$  Static RAM.

${\bf SSP}\,$  Single Shot Precision.

**TDC** Time-to-Digital Converter.

$\mathbf{ToT} \ \ \mathbf{Time-over-Threshold}.$

**VCO** Voltage Controlled Oscillator.

**VDL** Vernier Delay Line.

WFG Waveform Generator.

# **1 INTRODUCTION**

# 1.1 Scientific objective

The primary scientific objective of the Distribution of Energetic Electrons and Protons (DEEP) project at the Birkeland Centre for Space Science is developing a particle detector that can accurately quantify the energy flux deposited into the atmosphere by the process of Energetic particle precipitation (EPP). Existing particle detectors in orbit are inadequate for determining the amount of particles precipitating into the atmosphere, largely due to the highly anisotropic pitch angle distribution of precipitating electrons requiring a large field of view [Nesse Tyssøy et al., 2016]. The DEEP instrument will include three electron detectors mounted in different angles such that they collectively cover a field of view greater than 180°. This will provide new information about the distribution of particles backscattered by the atmosphere. In addition to this, three proton detectors are included to correct for proton contamination in the electron measurements [Nesse Tyssøy et al., 2017].

The contribution to the DEEP project and primary scientific objective of this thesis is developing a single scaled-down electron detector that is planned to be included in the payload of a sounding rocket launched by Andøya Space Centre (ASC) in 2023. This detector will serve as a proof of concept, and give valuable test information about the performance of the detector that can be used for further development. The thesis scope starts at the concept level, and extends as far as time will permit.

# 1.2 Energetic particle precipitation (EPP)

In order to understand the processes behind EPP, some background knowledge on the Earth-Sun environment and its dynamics is required. The information in this section is gathered from [Hargreaves, 1992].

# 1.2.1 Earth's atmosphere

The atmosphere of Earth is a layer of gases that is being confined by the gravitational pull. It is divided into layers based on the temperature gradient. These are, named in order of rising altitude, the troposphere, the stratosphere, the mesosphere and the thermosphere. The density of the atmosphere decreases rapidly with altitude, and since a major part of the energy from the Sun is absorbed in the thermosphere, it is particularly heated, reaching several hundred degrees Celcius. Though the temperature is high, the scarcity of particles means that there is almost no heat transfer. This point is important because it means that the situation is not quite as dire for temperature sensitive circuitry operating in the thermosphere as it might first appear. Because of the low particle density above 100 km from the surface, there is a permanent presence of ions and free electrons. This region of the thermosphere is known as the ionosphere, and it is electrically conductive.

# 1.2.2 Solar wind

The Sun is the centre of our solar system and its radiation is either directly or indirectly the primary source of all energy on Earth. In addition to the electromagnetic radiation the Sun emits, it also emits a continuous stream of charged particle plasma known as solar wind. One property of plasma is that it is electrically conductive, and magnetic fields become frozen in it. Because of this, the magnetic field of the Sun is carried along with the plasma stream and couples with the magnetic field of Earth. The solar wind is cyclic, following an 11-year solar cycle of continuously increasing and waning intensity.

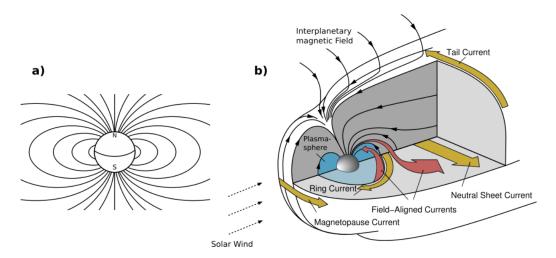

#### 1.2.3 The magnetosphere

The near-Earth space dominated by the Earth's magnetic field is called the magnetosphere. It is formed by the Earth's iron core, but continually reshaped by the varying solar wind. If not for the solar wind, Earth's magnetic field could accurately be modelled as a dipole with north and south poles slightly tilted off from the rotational axis. The solar wind, with its embedded magnetic field, has a large impact on the shape of the magnetic field surrounding earth. The magnetic field is compressed by the solar wind on the side facing the sun, and stretches out on the opposite side, creating a long tail on the night side as shown in Figure 1. If not for the magnetic field, the solar wind would blow away the atmosphere [Ødegaard, 2016, p. 7].

Figure 1: Earth's magnetic field [Ødegaard, 2016, figure 2.1].

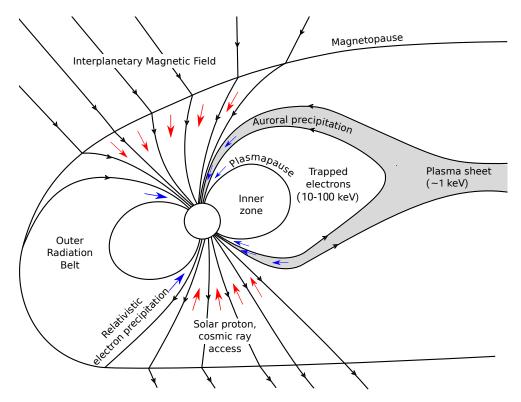

## 1.2.4 Radiation belts

Suspended in the magnetosphere are charged particles, trapped by the influence of the magnetic field. The discovery of the radiation belts starts with the Explorer 1 satellite, launched on 31 January in 1958. The satellite was equipped with a Geiger counter built by James Alfred Van Allen's research group at the University of Iowa. Measurements from this Geiger counter revealed that at certain times the counting rate was so large that it was interpreted as a malfunctioning counter. The same was observed by the satellites Explorer 3 and Sputnik 3, and it was speculated that these particles were electrons of energy around 100-150 keV. With results from Explorer 4, it was determined that the measured results stemmed from protons in a certain region with a kinetic energy above 30 MeV. Pioneer 3, also launched in 1958, discovered a second region of particles at a further distance from earth. This led Van Allen to formulate a theory of particles trapped in two distinct radiation belts in the magnetosphere [Van Allen and Frank, 1959]. Because of

this, these regions of trapped particles are also known as the Van Allen radiation belts. These regions of particles can be shown in Figure 2.

Figure 2: Illustration of the magnetosphere with trapped particles [Ødegaard, 2016, figure 2.2].

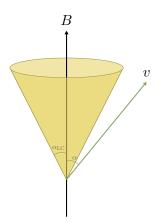

#### 1.2.5 Particle precipitation

Charged particles follow the field lines of the magnetosphere by spiralling around them. The angle of the velocity vector with respect to the geomagnetic field line is known as the pitch angle  $\alpha$ , as illustrated in figure 3. The pitch angle of a particle is defined as the angle of the velocity vector with respect to the field line, which can be constructed from the two velocity components  $v_{\parallel}$  and  $v_{\perp}$ , the components parallel and orthogonal to the field line respectively,

$$\alpha = \tan^{-1} \left( \frac{v_{\perp}}{v_{\parallel}} \right) \tag{1.1}$$

The pitch angle varies with the magnetic field, and since the magnetic field is weakest at the equatorial plane, the pitch angle of a particle is also at a minimum here [Ødegaard, 2016]. Because of the ever-changing nature of the pitch angle it is useful to characterize a particle by its pitch angle at this point, known as the equatorial pitch angle. As the particle moves along Earth's magnetic field, the pitch angle increases as it moves closer to the magnetic poles, and when the particle reaches a pitch angle of  $\alpha = 90^{\circ}$ , it will turn around and subsequently bounce back and forth between the hemispheres. The point at which the particle turns around is known as a mirror point, and it causes the particle to be indefinitely suspended in the magnetic field. If the mirror point is below an altitude of 100 km, it is unlikely that the particle will be able to mirror without colliding in the denser layers of the atmosphere. Such a particle is said to be lost to the atmosphere, or to precipitate into the atmosphere.

In order to quantify the rate of precipitating particles, a loss cone is defined at the equatorial plane that divides precipitating particles from trapped particles. If a particle has an equatorial pitch angle  $\alpha_{eq}$  within the loss cone, it has a mirroring point below the point at which it will be able to return before colliding with the gasses in the atmosphere, and thus it will be lost to the atmosphere. A typical pitch angle distribution has few particles within the loss cone, gradually decreasing with decreasing pitch angle. The loss cone pitch angle can be defined by the relationship,

$$\sin^2 \alpha_{LC} = \frac{B_{\rm eq}}{B_0} \tag{1.2}$$

where  $B_{eq}$  is the magnetic field strength in the equatorial plane and  $B_0$  is the magnetic field strength at some defined altitude, typically chosen to be 100 km. The geometry of the loss cone is shown in Figure 3.

Figure 3: Loss cone of the equatorial pitch angle. In this case the equatorial pitch angle of the particle points out outside the loss cone and the particle is trapped. Adapted from [Rodger et al., 2013].

#### 1.2.6 Effects

The most famous effect of particle precipitation is the appearance of aurora polaris, caused by the emission of photons at certain wavelengths as the precipitating particles excite the particles in the atmosphere. Different colours are associated with different atmospheric gasses, stemming from precipitation into different regions of the atmosphere.

There has been a lot of research into electron precipitation of energies less than 30 keV because of its ties to polar lights. Energetic particles with a kinetic energy greater than 30 keV are not typically associated with aurora, and their spectral energy flux is underrepresented in atmospheric models [Nesse Tyssøy et al., 2016] [Nesse Tyssøy et al., 2019]. These particles are of interest mainly due to the generation of  $NO_x$  and  $HO_x$  gases in the upper atmosphere [Lam et al., 2010]. During polar winter, the  $NO_x$  gases descend to a lower altitude, and through a series of chemical reactions they can deplete the ozone in the upper stratosphere. This causes a disturbance in the thermodynamic equilibrium of Earth's atmosphere.

## 1.3 Detection

In order to accurately quantify the loss cone flux, not only must the particle energy be detected, but also its pitch angle. To measure the pitch angle distribution, multiple pinhole detectors are placed at different angles, measuring the fluxes of different pitch angles. The typical pitch angle distribution has a near constant level of fluxes at all angles that fall outside the loss cone, but the flux gradually decreases for smaller and smaller pitch angles. A better angle resolution is attained by placing a pixel detector behind the pinhole to determine the angle at which it entered the pinhole. Multiple detectors at different angles will however not be a part of the system launching on the sounding rocket, where the proof of concept relates to the energy distribution.

## 1.3.1 NOAA POES MEPED

The Medium Energy Proton and Electron Detector (MEPED) from National Oceanic and Atmospheric Administration Polar Orbiting Satellites (NOAA POES) is currently the best instrument available for measuring the flux of precipitating high-energy particles [Nesse Tyssøy et al., 2016]. This instrument is part of the Space Environment Monitor (SEM) package, which comes in two generations known as SEM-1 and SEM-2. This instrument package is included on 14 satellites in total; 12 from NOAA POES and an additional two from the European Organisation of Meteorological Satellites (EUMETSAT). In addition to the MEPED, the SEM package also contains a Total Energy Detector (TED) which measures the energy flux of electrons and protons in the range of 0.5 to 20 keV [Ødegaard, 2016].

The MEPED instrument is able to detect protons and electrons in the energy channels specified in Table 1 and 2.

| Energy channel | Proton energy range                  |

|----------------|--------------------------------------|

| $P_1$          | 30  keV to $80  keV$                 |

| $P_2$          | 80  keV to $240  keV$                |

| $P_3$          | 240  keV to $800  keV$               |

| $P_4$          | $800~{\rm keV}$ to $2500~{\rm keV}$  |

| $P_5$          | $2500~{\rm keV}$ to $6900~{\rm keV}$ |

| $P_6$          | $6900~{\rm keV}$ and greater         |

Table 1: MEPED proton energy channels.

Table 2: MEPED electron energy channels.

| Energy channel | Electron energy range               |

|----------------|-------------------------------------|

| $E_1$          | $30~{\rm keV}$ to $2500~{\rm keV}$  |

| $E_2$          | $100~{\rm keV}$ to $2500~{\rm keV}$ |

| $E_3$          | $300~{\rm keV}$ to $2500~{\rm keV}$ |

The instrument consists of two detectors, one pointed to  $0^{\circ}$  and another pointing to  $90^{\circ}$  of the local vertical. At high latitudes the  $0^{\circ}$  detector points nearly parallel to the magnetic field and measures particles that will be lost to the atmosphere. The  $90^{\circ}$  detector will

detect precipitating or mirroring particles. In the common case of anisotropic pitch angle distribution, with fewer particles at the centre of the loss cone, the  $0^{\circ}$  will underestimate and the 90° detector will overestimate the precipitating fluxes. Several methods to mitigate this inaccuracy have been implemented such as applying the geometric mean, logarithmic mean, sinus fit and more advanced theoretical approaches [Nesse Tyssøy et al., 2016]. In addition to the insufficient pitch angle information, the MEPED instrument has a poor energy resolution, only providing three energy channels for electrons.

# 1.4 Project background

The DEEP instrument has been in development since the Birkeland Centre for Space Science (BCSS) first opened in 2013. Are Haslum started the work on the electronic design in 2017. He finished a prototype for the DEEP project that was onboard the ICI-5 sounding rocket launched from Ny-Ålesund on 26th November in 2019 [Lynnebakken, 2019] (rocket launch photograph in Figure 4). Contributions to the pixel design have also been made by Hogne Andersen in his 2018 Master's thesis.

Figure 4: ICI-5 launch from Ny-Ålesund 26th November 2019. Photo: Helge Markussen.

# 2 PRINCIPLES OF PARTICLE DETECTION

The theory in this section is retrieved from [Spieler, 2005], unless otherwise specified.

When a sufficiently energetic particle strikes a semiconductor, it will ionize the lattice atoms and generate electron-hole pairs along the particle track. Silicon is the predominant semiconductor used in detection of charged particles [Knoll, 2010, p. 354]. The energy required to ionize one atom is known as the ionization energy and is equal to roughly 3.6 eV for silicon, but this is subject to variation of the material. The ionization energy remains largely constant for incident energies, and the number of electron-hole pairs generated is thus approximately proportional to the kinetic energy of the particle.

The number of electron-hole pairs generated by incident radiation is equal to,

$$N = \frac{E}{E_i} \tag{2.1}$$

Where E is the energy imparted by the particle and  $E_i$  is the ionization energy. Each mobile carrier bears a charge equal to one elementary charge q. The total charge induced in a semiconductor by energetic radiation is thus,

$$Q = q \frac{E}{E_i} \tag{2.2}$$

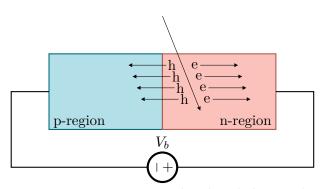

The semiconductor is in itself not sufficient as a detector, because although the incoming particle generates mobile carriers, they quickly recombine. A p-n junction, known for its primary purpose as a diode, is better suited for the task. A p-n junction is formed by two neighboring regions in a silicon crystal: one negative (n-doped) and one positive (p-doped) region.

With no external bias, a small current can be sensed as the mobile carriers are propelled by the small built-in potential present in a p-n junction, which depends on the doping level in the semiconductor. However, because of spontaneous recombination and trapping, not all charge carriers make it to the electrodes, and it is considered a poor sensor. By applying a suitably large reverse bias to the junction, almost all the mobile carriers make it to the electrodes. The p-n diode with a reverse bias acts as a capacitor, where the ohmic contacts are the electrodes and the depletion region is the dielectric material. The concept is illustrated in Figure 5. An incident particle hits the diode and frees electrons and holes. These are swept up into the electrodes on their respective ends, inducing a current. In practice, a pixel detector does not look like this, but is implemented in a larger two-dimensional area in a heavily p-doped silicon substrate. The pixel contains a negatively doped area known as an n-well at the top that attracts electrons, and an ohmic contact at the p-substrate at the bottom. The reverse bias is then applied top-to-bottom, and hole current travels downwards while electron current travels upwards.

Figure 5: p-n junction acting as an ionization chamber, holes are denoted h and electrons denoted e. Adapted from [Spieler, 2005, p.9].

As both holes and electrons are majority carriers in their respective electrode, they both contribute to the total current and are added in accordance with the superposition principle. Since the propagation speed of majority carriers is not equal, the current generated has two components as shown in Figure 6 (top). Hole propagation happens at roughly one third of the rate of electron propagation. By equation (2.3), the charge is the integral of the current with respect to time, so the total induced charge will look like Figure 6 (bottom).

Figure 6: Current generated by the propagation of majority carriers (top) and the equivalent induced charge (bottom). Adapted from [Knoll, 2010, p. 367].

#### 2.1 Amplification

The current that is generated by charge according to Figure 6 is amplified by a preamplifier that integrates the current to produce an output voltage. This is known as a Charge Sensitive Amplifier (CSA), and it outputs a voltage that is proportional to the total charge deposited in the sensor. The gain G of the CSA is commonly expressed in mV/fC.

## 2.2 Pulse shaping

The output voltage of the preamplifier can be measured directly by an Analog-to-Digital Converter (ADC), but this measurement is very susceptible to noise. To improve the Signal-to-Noise Ratio (SNR) of the detector system, a pulse shaper is included before the measurement. The pulse shaper consists of a low-pass and a high-pass filter that outputs a regular pulse shape with a known shaping time (or peaking time)  $\tau_P$ . The signal power is distributed in the frequency space, and the shaper filter is designed to favor the signal and attenuate the noise. The ideal shaper output for maximized SNR is a pulse that peaks for an infinitesimally small amount of time. This is impractical, however, because it becomes impossible for the digitizer to measure the peak value of the pulse. A practical implementation of the pulse-shaper is one in which the peak value persists for a measureable amount of time.

By the convolution theorem, one can relate the Fourier transform in the frequency domain to the pulse shape in the time domain. This is defined as,

$$f(t) * g(t) = \int_{-\infty}^{\infty} f(\tau)g(t-\tau)d\tau = F(f)G(f)$$

(2.4)

In practice, this relationship means that the shape of the signal in the time-domain is affected by the transfer function in the frequency domain.

The time response of a low-pass filter in response to a step input voltage  $V_i$  is,

$$f(t) = V_i \left[ 1 - \exp\left(\frac{-t}{\tau_i}\right) \right]$$

(2.5)

where  $\tau_i$  is the time constant of the low-pass filter (also known as an integrator). Similarly, the transfer function of a high-pass filter, also known as a differentiator, is,

$$g(t) = V_i \left[ \exp\left(\frac{-t}{\tau_d}\right) \right]$$

(2.6)

where  $\tau_d$  is the time constant of the high-pass filter (differentiator).

Calculating the output response in the time domain is done by convolving the input with the transfer functions,

$$V_o(t) = V_i(t) * f(t) * g(t)$$

(2.7)

For a unit step this is,

$$V_o(t) = \frac{\tau_d}{\tau_d - \tau_i} \left[ \exp\left(\frac{-t}{\tau_d}\right) - \exp\left(\frac{-t}{\tau_i}\right) \right]$$

(2.8)

And for  $\tau = \tau_i = \tau_d$ ,

$$V_o(t) = \left(\frac{t}{\tau}\right) \exp\left(\frac{-t}{\tau}\right) \tag{2.9}$$

As the output shape is the same for any step input, the amplitude must be proportional to the step amplitude, which in turn is proportional to the induced current. It can be useful to normalize this function if the amplitude is known. Since the maximum of this function occurs at the peaking time  $t = \tau$ , the normalized function  $V_o(t)$  is attained by multiplying  $V_o(t)$  with the inverse of the peaking value  $e^{-1}$ ,

$$\hat{V_o(t)} = \left(\frac{t}{\tau}\right) \exp\left(1 - \frac{t}{\tau}\right)$$

(2.10)

As the pulse is shaped, the energy that is proportional to the incident charge is now also proportional to the amplitude of the shaped pulse,

$$Q \propto E \propto A \tag{2.11}$$

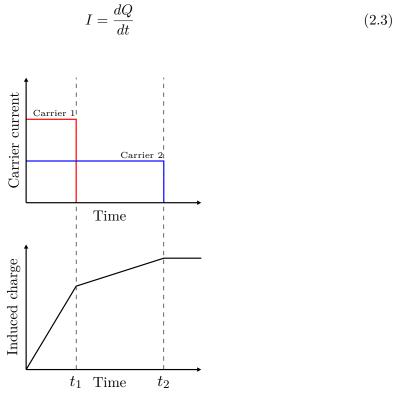

A complete readout chain is presented in Figure 7.

Figure 7: Particle detection signal chain [Spieler, 2005, p. 2].

#### 2.3 Pile-up

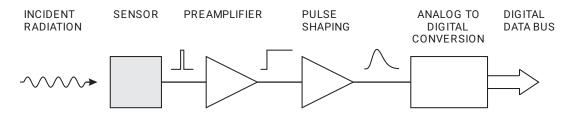

After a particle has generated charge in the sensor, there is a certain amount of time until the output returns to its baseline value, decided by the shaping time of the pulse. In the event that two particles should strike the sensor in a time interval shorter than this, a condition known as pile-up occurs. It is useful to divide pile-ups into two kinds: tail pileup and peak pile-up. In the first case, the pulses are sufficiently spaced so that they can be discerned, but the remnants of the tail of the first pulse, whether positive or negative (due to undershoot), is superimposed on the following pulse. Alternatively, in the case of peak pile-up, the particles strike the sensor with such a small time difference that the charge deposited appears as a single pulse. The superposition of the pulses causes their kinetic energy to be summed, and the fact that two particles struck the sensor is occluded. [Knoll, 2010]

Particles striking the sensor are randomly spaced in time and follow the Poisson distribution,

$$P(X = k) = \frac{\lambda^k \exp(-\lambda)}{k!}$$

(2.12)

where  $\lambda$  is the expectation value and P(X = k) is the probability that k events happen within a time interval. Letting  $\lambda = rt$ , where r is the rate of events and t is time, the probability of another particle striking the sensor within the time period  $\tau$  and causing a pile-up condition can be calculated. Let  $t_0$  be the time that a particle strikes the sensor and  $t_1$  be the time when the sensor circuitry is ready to detect another particle, and then define  $\tau = t_1 - t_0$ . The probability can then be calculated with (2.12) by finding the probability that no particle strikes within  $\tau$  and subtracting this from the total probability 1. Since this means that k = 0, the equation reduces to the cumulative exponential distribution and the pile-up probability P is given as,

$$P = 1 - \exp(-r\tau) \tag{2.13}$$

Figure 8 shows the pile-up probability by varying the time window  $\tau$  from 0 to 1000 ns and the event rate r from 10<sup>4</sup>/s to 10<sup>7</sup>/s. A low pile-up probability is desired, so ideally the shaping time needs to be low enough for a given flux so that the probability remains in the blue-shaded area on the graph. For low fluxes a long shaping time is fine, but the shaping time requirements become more stringent as the particle flux increases. A reduced shaping time can increase the complexity of the readout circuit if the pulses are so short that very high speed and high resolution methods need to be employed.

The expected count rate is on the order of  $r = 10^5$  events/second [Nesse Tyssøy et al., 2017].

Figure 8: Color map of pile-up probabilities for varying particle fluxes and shaping times.

## 2.4 Baseline shift

Since there is a series capacitor in the pulse shaper, any DC component of the input is blocked. A sequence of pulses will have a DC component that depends on the event rate. The DC baseline shifts make the total transmitted charge equal to zero. Since the event rate can change over time or fluctuate randomly, the baseline will shift over time, and this contributes to the noise of the system. In both the cases of low and constant event rates the effect of baseline shift will be minimal, but in high event rate systems it may affect the resolution of the system significantly. A baseline restorer can be included in the circuit that temporarily grounds the signal line in the absence of any signal, thereby removing unwanted charge.

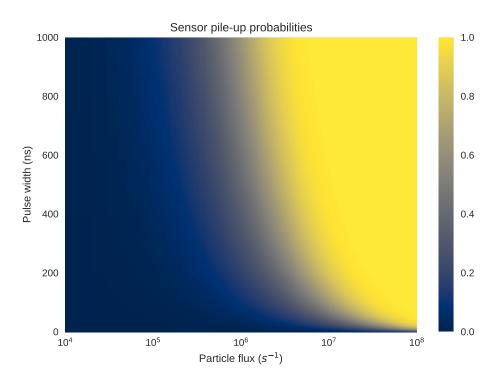

## 2.5 Data acquisition

The amplitude of the pulse generated by the CSA is proportional to the charge deposited in the pixel detector. Measuring the amplitude requires some form of analogue to digital conversion, and there are two primary ways to achieve this. The first method is a direct measurement of the pulse amplitude using an ADC. The other method exploits the fact that the shape of the pulse is the same for all incoming pulses, and the time a pulse spends over a given threshold is a function of the amplitude. A Time-to-Digital Converter (TDC) can be used to determine how long the pulse is above some threshold. This can be mapped to a corresponding amplitude of the signal pulse. Since the amplitude is proportional to the incident energy and deposited charge, these are readily determined also. The threshold must be selected such that it is below the lowest signal amplitude, but sufficiently greater than the noise floor.

#### 2.5.1 Analogue-to-Digital Conversion

The signal pulse can continually be sampled by an ADC, and the current pulse value compared to some locally stored maximum. If the pulse value is above the local maximum, the maximum is updated with the new value. After a pulse has passed, the maximum is recorded as the amplitude of the signal, and the energy is determined. This results in a linear relationship between measured pulse heights and incident particle energies. Error sources in an ADC-based data acquisition circuit include circuit noise and quantization error, but the main driver of inaccurate conversion is insufficient sampling rate. The shaping time must be minimal to avoid pile-up, and the amount of samples per pulse should be sufficient to accurately determine the peak; low rates can lead to sampling on both ends of a peak, missing the true peak of the pulse. Another challenge with implementing an ADC is that since particles can scatter through several sensors, multiplexing cannot be used, and a separate channel is required for each pixel. A high number of channels and a high sampling rate causes high power dissipation to be a limiting factor.

## 2.5.2 Time-over-Threshold

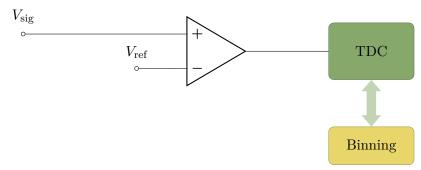

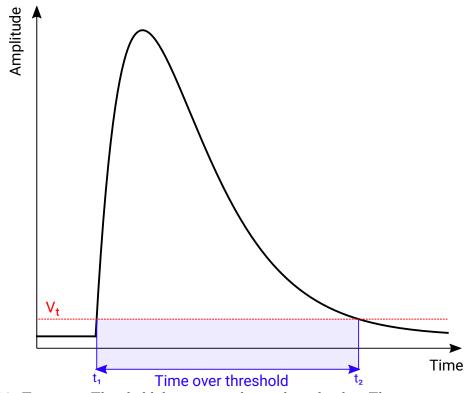

An alternative approach to converting the pulse to a digital value is by the Time-over-Threshold (ToT) method. It has been applied successfully in detector readout systems such as the BaBar Silicon Vertex Tracker at the Stanford Linear Accelerator Center [Kipnis et al., 1997]. By letting the signal be the input to a comparator with an appropriately chosen threshold voltage, the signal charge deposited into the sensor may accurately be quantified by measuring the pulse width of the comparator output, illustrated in Figure 9 and Figure 10. The conversion is done by a TDC that converts time intervals into quantized digital representations. The energy resolution is constrained by the resolution attainable in the TDC. The ToT method is very sensitive to noise on the input of the comparators, so circuit noise must be minimized to discern the signal from the noise in the lower range of energies.

The benefit of the ToT method is simplicity, resulting in a low component count and low power dissipation.

Figure 9: Implementation of Time-over-Threshold.

Figure 10: Time-over-Threshold demonstrated on a shaped pulse. The time interval shown in blue is digitized, and the pulse peak information is withdrawn from the pulse width.

One crux of the ToT method is that the width of the pulse generated by the comparator is highly nonlinear, and consequently the difference in width between short pulses is greater than the difference between two large pulses. This necessitates mapping the pulse width to energy nonlinearly with a conversion table. Another consequence of the nonlinear transfer function is that as the energy increases, the resolution decreases, because each step change in energy corresponds to a smaller and smaller difference in the time over threshold. A result of this is that the dynamic range suffers, as it becomes increasingly hard to detect differences in higher energies.

The ToT interval is dependent on the threshold voltage, the shaping time of the pulse shaper, as well as the incident energy.

The pulse peak value is known for a given incident energy and is the product of the deposited charge Q in coloumbs (given by equation (2.2)) and the gain G of the CSA in volts per coloumb,

$$V_{pk} = GQ = Gq\frac{E}{E_i} \tag{2.14}$$

Multiplying the peak with the function for the normalized shaped pulse in (2.10) gives the function for the pulse dependent on incident energy of the particle and gain of the CSA,

$$V_o(t) = Gq \frac{E}{E_i} \left(\frac{t}{\tau}\right) \exp\left(1 - \frac{t}{\tau}\right)$$

(2.15)

Of main interest is developing a function T(E) that maps from incident energies to time intervals. Note that the CSA gain G, the ionization energy of the semiconductor  $E_i$ , and the shaping time  $\tau$  are all known design variables, and can be considered constants for the remaining analysis.

Let the threshold voltage be a constant  $V_t$ .  $V_o(t)$  is zero both for t = 0 and  $t = \infty$ , and crosses the threshold exactly twice. The crossover points are the roots  $t_1, t_2$ ,

$$Gq\frac{E}{E_i}\left(\frac{t}{\tau}\right)\exp\left(1-\frac{t}{\tau}\right) - V_t = 0$$

(2.16)

Because of the exponential function, the roots of (2.16) are attained using the multivalued Lambert function W(E). Each root is given by the two branches of the Lambert function  $W_0$  and  $W_{-1}$ ,

$$t_1 = -\tau W_0 \left( \frac{-e^{-1}V_t}{G_{E_i}^{qE}} \right) \tag{2.17}$$

$$t_2 = -\tau W_{-1} \left( \frac{-e^{-1} V_t}{G_{E_i}^{qE}} \right)$$

(2.18)

The time interval above a given threshold is thus decided by the difference in the roots,

$$T(E) = t_2 - t_1 \tag{2.19}$$

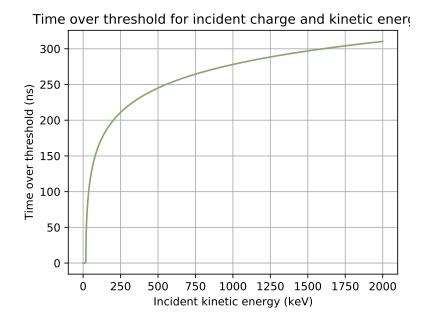

This is readily calculated by applying the Python package Scipy to calculate the Lambert function, and the function T(E) is solved for all energies in the interval up to 2 MeV. A plot of the resulting transfer function for ToT is given in Figure 11.

Figure 11: Time over threshold as a function of incident kinetic energy.

The resulting relationship between incident energy and time over threshold of the shaped pulse is highly nonlinear. For small energies, a small change in input energy results in large differences in the time interval produced by the comparators. This means that as the kinetic energy increases, the resolution of the readout electronics decreases in turn.

## 2.5.3 Dynamic Time-over-Threshold

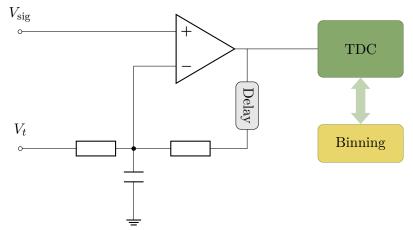

In an attempt to rectify the non-linear relationship described above, [Orita et al., 2015] presents a method of linearising the transfer function. Instead of having a static threshold value on the comparators, an alternative is a threshold value that dynamically changes with the same time constant as the shaping time of the pulse. This method is known as Dynamic Time-over-Threshold (dToT). An implementation is illustrated in Figure 12.

Figure 12: Implementation of Dynamic Time-over-Threshold. Adapted from [Orita et al., 2015].

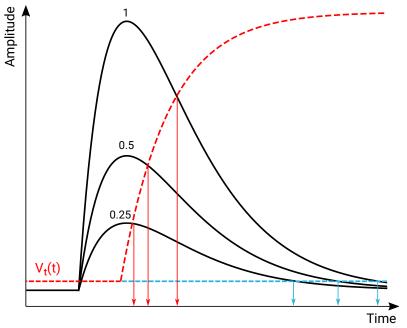

Orita et al. used a monostable vibrator to create the delay, but it can be generated in many ways. The important thing is to closely match the delay to the peaking time of the pulse. If there is random variation in the delay, this will manifest itself as noise on the time interval. The working principle is shown in Figure 13. The red dashed line is the dynamic threshold, and the blue line is the conventional static threshold. Shown here are three pulses of amplitude 0.25, 0.5 and 1. The non-linearity can be shown with the blue arrows. In a linear system it is expected that each doubling of the amplitude corresponds to a doubling of the time interval. However, in the static case, the difference between 0.5 and 1 is as large as the difference between 0.25 and 0.5. This is rectified by the dynamic threshold, where it can be seen that the distance in time between 0.5 and 1 is twice as large as the difference between 0.25 and 0.5.

Figure 13: Principle of Dynamic Time-over-Threshold. The threshold is triggered to rise exactly at the peaking time of the pulse. The red arrows signify at which point in time a pulse goes below the dynamic threshold, while the blue arrows show the times it transitions below the static threshold.

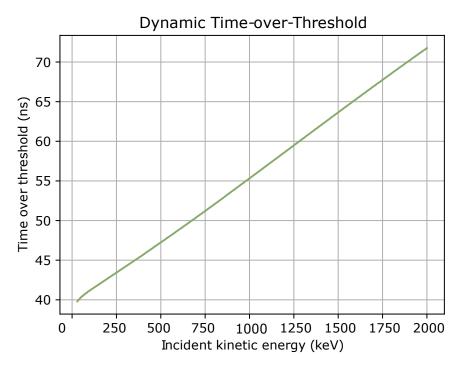

The transfer function between kinetic energy and time over threshold is shown in Figure 14.

Figure 14: The linear transfer function of a dToT implementation.

# **3 SYSTEM OVERVIEW AND SPECIFICATIONS**

The Investigation of Cusp Irregularities (ICI) rocket campaign is a scientific campaign that aims to investigate disturbances in the ionosphere through the use of sounding rockets. The last prototype of DEEP flew as part of the instrument package on the fifth ICI rocket known as ICI-5. This sounding rocket flew to an altidue of 253 km [lau, 2020]. The next iteration of the instrument is planned to be included in the payload the next ICI rocket in the campaign. Although this rocket is currently under development, preliminary specifications have been received, and it is assumed that many aspects of the integration will be comparable. The same detector house will be used, and the electrical interface between the instruments and rocket is confirmed to be backwards compatible with ICI-5 (Email correspondence, Geir Lindahl ASC via Ketil Røed (UiO) 30-04-2021). This section gives an overview of the system specifications, the sounding rocket integration, and work that has been done on the project prior to this thesis.

## 3.1 Detector house

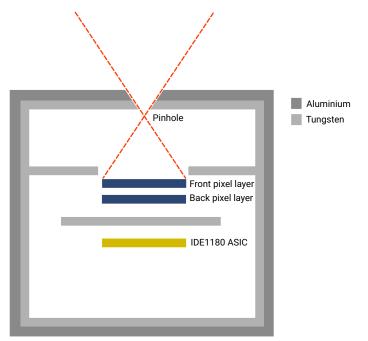

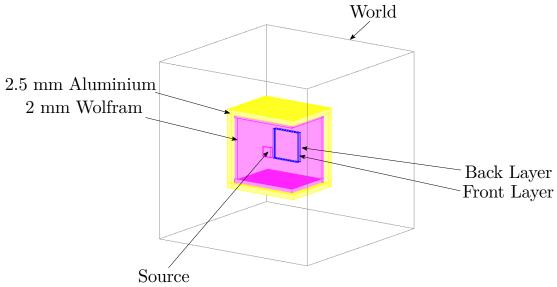

The instrument house consists of both the detector house and the readout electronics house. The detector house for the detector itself is made out of 2.5 mm thick aluminium sides, further shielded by 2 mm tungsten on the inside to protect from high-energy particles that may penetrate the sensor housing and deposit energy into the pixel sensors. The particles enter the detector house through a conical hole at the top known as a pinhole or aperture. A conceptual drawing is illustrated in Figure 15.

Figure 15: Conceptual detector house drawing. The outer walls are aluminium and the inner walls consist of Tungsten.

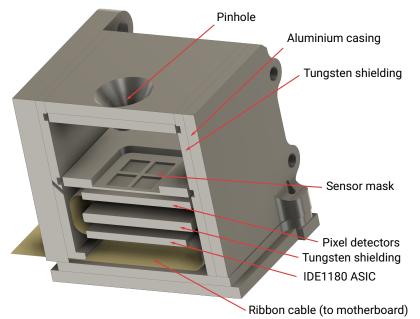

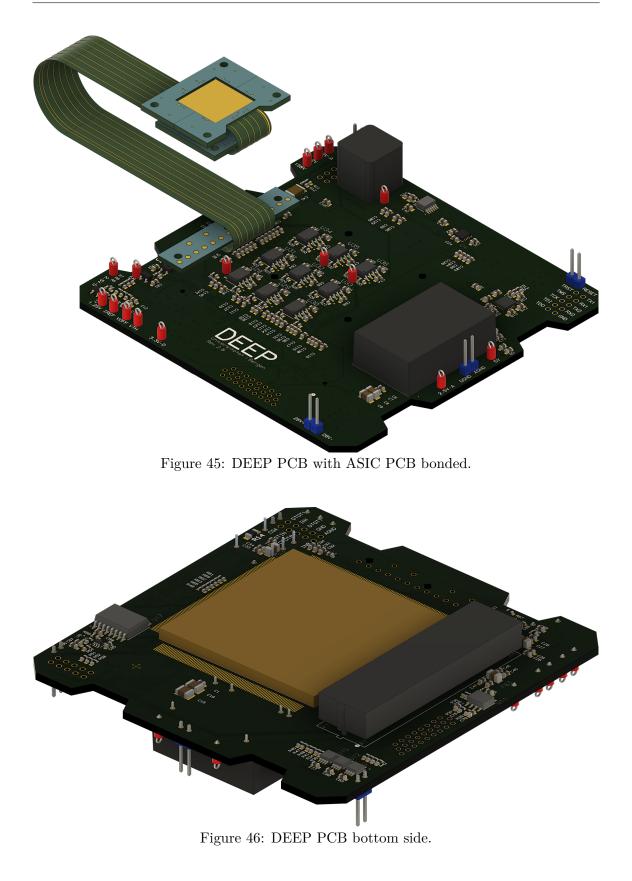

A CAD drawing is shown in Figure 16. The pinhole where electrons enter is shown at the top of the house. Inside, the pixel detectors are masked by a sensor mask made out of

Tungsten. It is thicker around the edge, and also provides a physical barrier between the pixel detectors. The purpose of the thick layer around the edge is to stop particles from scattering past the pixels. The thin dividing layer between the pixels is to stop electrons from scattering horizontally between pixels. Below the first pixel layer is the second pixel layer. This is another identical layer of pixels on the flip-side of the Printed Circuit Board (PCB), i.e. directly below the front layer. Below the pixel detectors is another layer of Tungsten shielding to protect the Application Specific Integrated Circuit (ASIC) from the radiation. Directly below the Tungsten shielding is the ASIC PCB. The output pulses from the ASIC travels on traces in the flex ribbon cable, leaving the detector house and entering the electronics house where it is bonded to the DEEP readout board.

Figure 16: Cross-section of detector house (CAD drawing by Torstein Frantzen).

Inside the detector house are two silicon diode layers, each consisting of four pixel detectors for high angular resolution. Each semiconductor layer is 1 mm thick. The proposed pixel arrangement for the complete system is two layers of 2x4 sensor pixels for the electron detector, and two layers of 2x2 sensor pixels for the proton detector. The scaled down test detector considered in this thesis makes use of a 2x2 array of electron detectors.

The combination of the electronics house, detector house and rocket interface constitutes the DEEP instrument. It is shown integrated with the ICI-5 rocket in Figure 17.

Figure 17: Left: Detector house consisting of detector house (top) and electronics house (bottom). Right: Detector house mounted on the ICI-5 rocket. Photo: Are Haslum.

# 3.2 Binning

The particle flux energies are expected to be exponential, and the incident radiation will be dominated by the lower range of energies. The number of bins must also be limited to not occupy a large amount of memory and telemetry bandwidth. The bins outlined in Table 3 are proposed for the histogram. Each bin width is doubled to account for the lower number of particles expected as energy levels increase.

| Bin | Energy range |

|-----|--------------|

| 1   | >30  keV     |

| 2   | >60  keV     |

| 3   | >120  keV    |

| 4   | >240  keV    |

| 5   | >480  keV    |

| 6   | >960  keV    |

| 7   | >1500  keV   |

Table 3: Desired bin widths in the DEEP histogram.

#### 3.3 Sensor PCB

The sensor module is a separate PCB that consists of eight pixel detectors arranged in a 2x2 pixel array, shown in Figure 19. The pixel detectors were produced by SINTEF. It features a flex cable that is to be connected to the DEEP readout board. When an energetic particle hits the detector, charge is deposited and this generates an electrical signal that can be sensed and amplified. The IDE1180 AMADEUS ASIC from IDEAS is used as a combined charge sensitive preamplifier and pulse shaper. It has 16 input channels, adjustable gain (mV/fC) as well as an adjustable shaping time ranging from 20 ns to 40 ns. The shaping time is the time interval between an input charge is collected to the output pulse peaks.

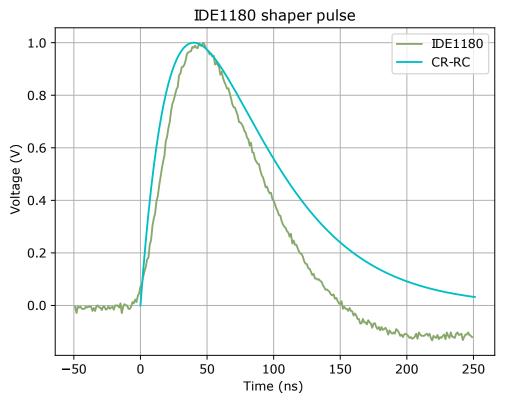

The theory discussed in section 2 is not practically applicable to the actual sensor PCB system. While the shaping time of the CSA is known, the exact pulse shape is not given in the accompanying datasheet. A measurement of the CSA pulse in response to a step input is shown superimposed on the pulse generated by (2.15) in Figure 18.

Figure 18: Idealized pulse versus measured IDE1180 pulse (normalized).

It can be seen that although the peaking time is the same, the IDE1180 pulse falls of at a steeper rate than the theoretical pulse. This is caused by an undershoot in the filter of the IDE1180 ASIC, and results in the ToT interval to be shorter than expected. The undershoot can also affect two pulses that are close in time, causing the second pulse to be smaller than expected.

Figure 19: Flex PCB with sensor (left), IDE1180 ASIC (middle) and bonding connection (right).

## 3.4 Rocket interface

The rocket interface consists of a power connection to the battery, as well as signals to and from the rocket. It is an ASC requirement that these are galvanically isolated to eliminate ground loop issues. These signals are the same as requested for the ICI-5 launch and is

| Signal      | Function                                                                                                          | Direction |

|-------------|-------------------------------------------------------------------------------------------------------------------|-----------|

| DATA        | Data to PCM encoder                                                                                               | Out       |

| GATE        | Enable signal for data channel                                                                                    | In        |

| SCLK        | Synchronizing clock                                                                                               | In        |

| MIN_FRAME   | Minority frame counter                                                                                            | In        |

| MAJ_FRAME   | Majority frame counter                                                                                            | In        |

| TIMER       | Timer signal that goes high when rocket reaches<br>a certain altitude, used for turning on 150V<br>source         | In        |

| GSE_CONTROL | Ground Support Equipment (GSE) signal that<br>can turn on and off 150V source when the rocket<br>is on the ground | In        |

listed in Table 4.

Table 4: Rocket interface signals.

The telemetry system on the sounding rocket from ASC is a type of Pulse Code Modulation (PCM) system using Time-Domain Multiplexing, and it offers digital channels as well as analogue channels. For this project histogram of counts for each energy bin is the main information that will be transmitted. This is readily represented as a digital value, and thus the digital channels will be used.

Data in a PCM system is structured into major and minor frames. To know when a frame starts and stops, synchronization words are included in the data stream. This process is handled by the PUSEK PCM encoder onboard the rocket, and signals are supplied to the DEEP instrument to identify the start of minor and major frames. A major frame consists of minor frames, which are small periods of time in which the output spectrum of a given sensor is transmitted.

## 3.5 Specifications

Since multiple parties have requirements that must be met in the development of the detector, it is useful to collect these in a specifications list. These requirements are based on information about and previous integration with the ICI-5 sounding rocket, desired integration with the completed mechanical house and sensor PCB, as well as a conceptual design report of the detector. The following system specifications are compiled for the design of this detector:

- The previous iteration of the circuit board was approved for flight by ASC. The new board should have the same physical dimensions and similar weight to avoid necessitating a new approval.

- The total power consumption of the system should be less than 10 watts.

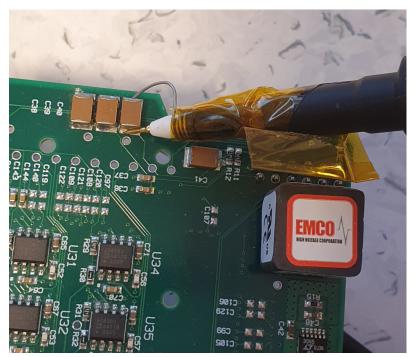

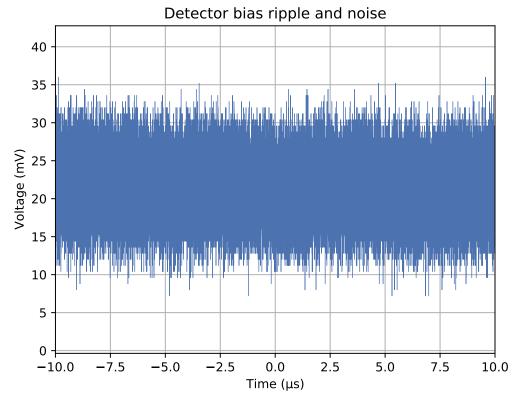

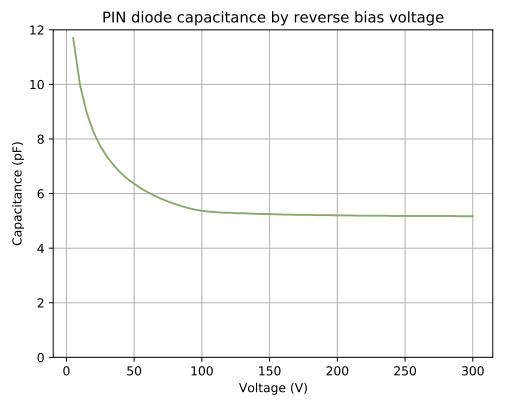

- The DEEP PCB is to be bonded to the sensor PCB and must supply the following to the IDE1180 ASIC: A bias current sink of 100 mA, a 150 V detector reverse bias, and a 0.5 V offset voltage. The 150 V bias supply needs to be disableable.

- Output pulses from the IDE1180 ASIC should be digitized and counts stored in a

histogram consisting of seven energy channels: 30 to 60 keV, 60 to 120 keV, 120 to 240 keV, 240 to 480 keV, 480 to 960 keV, 960 to 1500 keV as well as 1500 keV and greater.

- There is a total of eight pixel detectors, and each one should have its own dedicated digitizer to facilitate higher count rates.

- The pixel detectors must be shielded from high-energy particles not originating from the pinhole disturbing the pitch angle distribution measurement. Other methods of filtering these particles may also be employed.

- Count rates of up to  $10^6$  particles per second should be supported on each detector channel.

- Circuit components should be industry grade: automotive or military preferred.

- Preferrably, a space grade version of each component should be available even if it is not used on the proof-of-concept circuit.

- 28 V power will be supplied by the sounding rocket, but needs to be galvanically isolated to reduce ground loop issues. All locally required power lines must be generated on-board.

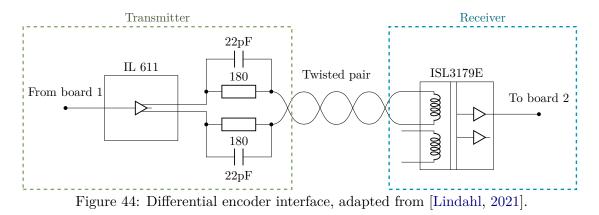

- The PCB needs to interface with the PCM encoder on the sounding rocket to transmit data through telemetry. Like the power line, these signals should be galvanically isolated and differential.

- The signal and power connections are interfaced to the rocket through a DSUB connector. The connector mounted to the detector house and is bonded to the PCB with flying leads.

# 4 MONTE CARLO SIMULATION OF ENERGETIC PARTICLE PRE-CIPITATION

In order to define an accurate algorithm for the processing of pixel data, it is useful to simulate the behaviour and movement of energetic particles once inside the detector house. Particles at relativistic velocities do not necessarily move in straight lines, and it is not guaranteed that they deposit charge in only one pixel. When a particle deposits energy in a medium, it is through a collision with atoms in the structure. When this happens, the path of the particle is altered. This process is known as scattering, and it should be accounted for when determining any algorithm involving the trajectory of particles. There are two key questions that should be answered before the data acquisition algorithm is determined:

- 1. At what rate do particles scatter from one pixel to another, and can it be determined which pixel the particle struck first?

- 2. What is the energy necessary to penetrate the Tungsten shielding and deposit energy in the back of the sensor, and can these particles be filtered to prevent them contaminating the pitch angle measurements?

This section extends upon the work carried out by Hogne Andersen in his 2018 Master's Thesis [Andersen, 2018]. In his thesis, he developed simulation models for the particle detector using GEANT4 Application for Emission Tomography (GATE), an open-source Monte Carlo simulation tool based on the Geant4 toolkit developed by European Organization for Nuclear Research (CERN). In particular, his simulation models of the pixel detectors has been reused, and his proposition for vertical coincidence checking is further examined. The simulation model is a detector house as described in 3.1, where the walls are shielded by aluminium and tungsten, and inside there are two Silicon plates that act as the sensors. In the simulation, these front and back sensor plates are singular units, and definitions of pixels are added during the processing stage based on the coordinates of the deposited energy.

The simulation environment used is shown in Figure 20.

Figure 20: GATE simulation environment [Andersen, 2018].

The simulation input is specified in a MAC file, wherein the simulation environment, materials and geometry and particle radiation sources are defined. In the simulation, particles are emitted from the source towards the Silicon detector layers. The angle of the radiation source is specified by two angles,  $\theta$  and  $\phi$ .

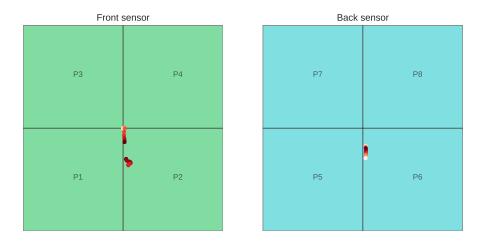

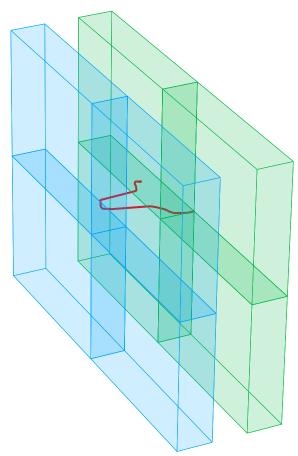

The output of the simulation is a ROOT file, which is structured as a list of events. The file is read by a Python wrapper for ROOT known as PyROOT. Each event is a collision of the particle with a medium, and contains the particle ID, deposited energy, the spatial coordinates and a timestamp. The information is used to structure the hits into energy deposited in each pixel for each particle. The data can also be used to track the trajectory of the particles. Figure 21 shows the track of a particle that travels through the first sensor layer, hitting the second layer and bouncing back into the first layer again. It can be hard to see such patterns in a 2D plot, but since the particle data contains three-dimensional coordinates it can also be plotted in 3D as illustrated in figure 22.

Figure 21: Electron hitting front and back sensors, simulated using GATE.

Figure 22: 3D visualization of the same electron scattering through sensor.

## 4.1 Horizontal coincidence

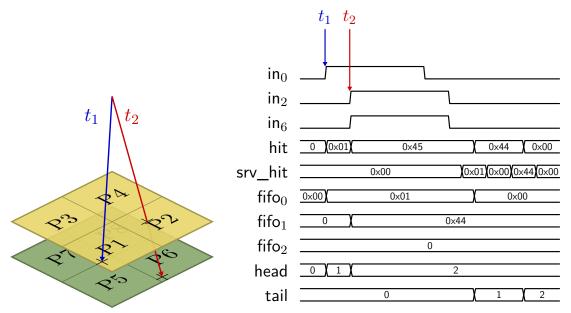

To be able to determine the pitch angle distribution, it is necessary to be able to determine from which direction a particle came from. This is a problem when detecting electrons because of scattering. An electron may scatter throughout many of the pixel detectors and deposit energy, known as a horizontal coincidence event. Determining if a particle struck several sensors can be done in the circuit by noting if the detectors both detect a hit in the same clock period, they belong to the same particle, and the energy must be summed. When a coincidence event has been established, the question arises of which histogram the particle belongs to. To uncover if the energy distribution can be used to determine which of the pixel was hit first, a simulation is needed.

The idea is that an electron is likely to deposit more energy in the pixel it first struck than in any of the other it hit. Therefore, the initial pixel and thus angular information about the particle can be retrieved by finding the pixel in the front layer that has the maximum energy in a hit. 100 000 electrons of energy 960 keV were fired towards the pixel array in GATE, and the coordinates of the first deposited energy event in the simulation were saved for each particle. The coordinates were used to determine which pixel a particle struck first and assign it to the particle. Next, the total deposited energy was sorted into a sum for each pixel. Since this only concerns the particles that hit multiple pixels, the data was filtered to only include coincidence events in the front layer.

The pixel with the most deposited energy for each particle was compared to the pixel each

particle struck first. If they match, it is counted as a success. Of the 100,000 electrons, 20,713 of them deposited energy in multiple pixels. Of these, the initially struck pixel detector was the one with the most deposited energy in 10,319 cases, yielding a success rate of 49.8%. Since there are four pixels, it could be concluded that this is at least better than chance. In the vast majority of cases, however, the particle deposited energy in exactly two pixels. Only 1,214 cases had hits in more than two pixels. It is not really feasible to use this to determine the pitch angle of an electron based on this method. A proposed solution that retains information about both pitch angle distribution and flux energies is the inclusion of a ninth histogram. This histogram is used to collect all the particle hits for which the pitch angle is ambiguous.

### 4.2 Vertical coincidence

Andersen suggests in his thesis that as a particle scatters through both of the pixel layers, the energy deposited in the first layer relative to the second layer (so-called front/back ratio) is greater than some ratio  $R_c$  for lower energies. After a certain energy threshold  $E_c$ , the relationship flips and most of the energy deposited is in the back layer. [Andersen, 2018, p. 62]. In principle this ratio can be arbitrarily selected because each ratio has its own respective critical energy that can be determined by simulation. Since we want to say something about how the energy is distributed between the two pixel layers depending on the direction of the particle, the ratio is set to 1. It is important to recognize the fallacy of increasing detector efficiency by altering the ratio. By shifting the ratio, more hits that are known to originate from the pinhole (front pixel layer first) are accepted, but proportionally fewer of the hits from the back are rejected.

This is easily demonstrated by the inequality of accepted hits,

$$\frac{F}{B} > R_c \quad \Leftrightarrow \quad \frac{B}{F} < 1/R_c \tag{4.1}$$

where F is the energy deposited in the front layer and B is the energy deposited in the back layer. Essentially, this means that if ratios above  $R_c$  are accepted, only ratios above  $1/R_c$  are rejected. Taken to an extreme, all hits can be accepted by setting the ratio to an infinitesimal  $\epsilon$ , but this leads to rejecting all hits that are above  $1/\epsilon$ , which is such a large number that in reality it does not reject any hit that penetrated the shielding and hit the sensor from the back.

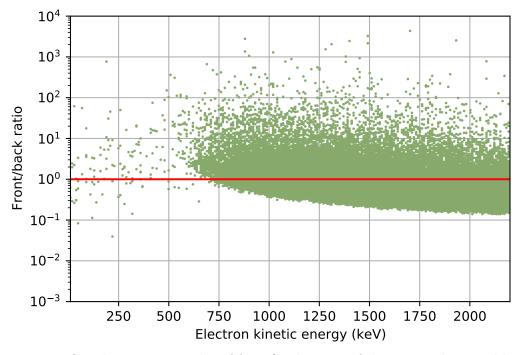

To investigate this proposed method of determining the direction of a hit, a simulation was defined that radiates electrons from a source towards the pixel array with energies ranging from 0 to 2 MeV. In order to sort them by energy, the electrons have been defined by a static energy and increased in steps of 10 keV with repeating GATE runs. The scatter plot generated from this simulation is shown in Figure 23. Along the x-axis of this scatter plot are the true energies of the electrons, that is the actual kinetic energy of the particle being spawned by the radiation source.

Figure 23: Simulation scatter plot of front/back ratios of the energy deposited by precipitating electrons across an energy range of 0 to 2MeV. Logarithmic Y-scale.

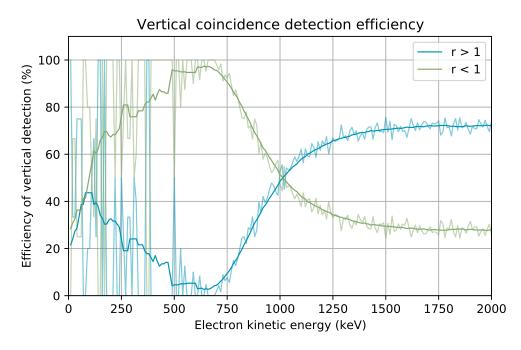

When looking at the particles that struck both the front and the back sensors, a pattern can be discerned in figure 24. The turning point is located almost exactly at  $E_c = 1$  MeV. In the right figure, the efficiency of coincidence detection when the ratio is reversed after 1 MeV is seen.

Figure 24: Efficiency of vertical coincidence discrimination for F/B ratios below and above 1. In this plot only the particles that hit both the front and back pixel array are included.

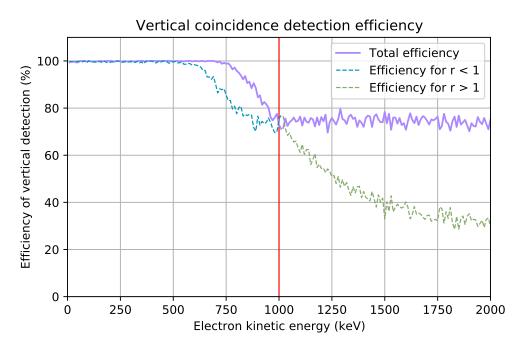

Combining these with the hits that did not scatter to the front sensor, the total efficiency of the vertical coincidence detection is shown in Figure 25.

Figure 25: The total efficiency of the vertical detection efficiency including all particles, accepting different F/B ratios based on incident energy.

This simulation experiment confirms that there is a pattern that can be exploited in how

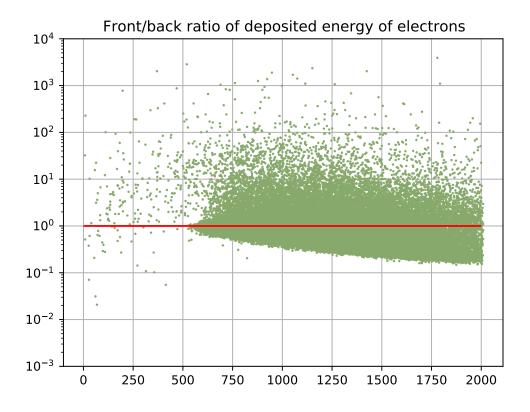

the energy is distributed between the pixel layers, but this relies on a faulty premise as in the simulation the initial energy of the particle is known. In practice, this energy cannot be accurately determined, only the energy actually deposited in the sensor can be sensed and converted into an energy. Accounting for this, a second simulation was defined where the source is a uniform distribution of energies from the source. Here, the energy spawned is not known, and it is defined as the sum of energies deposited in any of the pixel sensors. The scatter plot of this simulation is shown in figure 26,

Figure 26: Simulation scatter plot of front/back ratios of the energy deposited by precipitating electrons across an energy range of 0 to 2MeV. Logarithmic Y-scale. Electron energy in keV on x-axis and front/back ratio on y-axis.

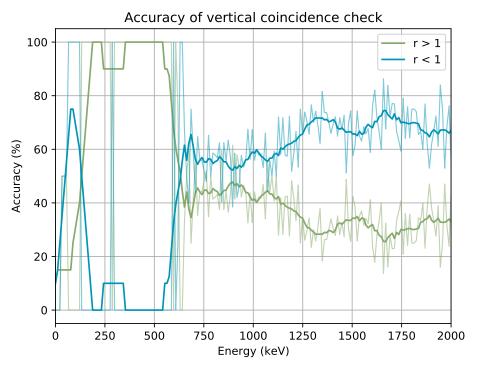

The accuracy when selecting r > 1 and r < 1 is shown in Figure 27. This plot has more noise stemming from the fact that particles can scatter away from the sensors and not deposit all of their kinetic energy in the simulation, disturbing the pattern. The thicker line is a moving average with an averaging window of 20.

Figure 27: Efficiency of vertical coincidence discrimination for F/B ratios below and above 1. Only particles that hit both the front and back pixel array are included.

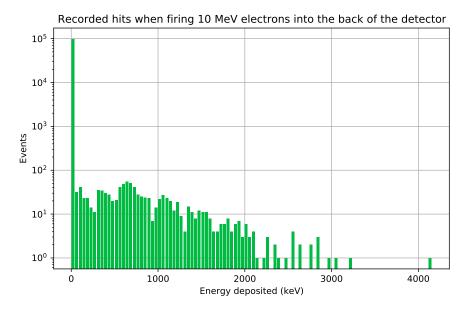

What this plot reveals is that there is little to no information to be gained by reversing the relationship at any energy point. As soon as there is a significant amount of particles that strike both pixel layers, the case for r > 1 quickly comes out on top. Since there is not a clear distinctive trend, this method is deemed infeasible. Even if the origin of the particle can be ascertained with 70% certainty, this means reducing the detector efficiency to 70% to stop 70% of the particles originating from the back. To investigate how common this is, 10 MeV electrons were fired into the detector house from the back. The simulation was run with 100,000 particles. A logarithmic histogram of the recorded energy bins in the pixel detectors are shown in Figure 28.

Figure 28: Deposited energy in the pixel detectors when firing 100,000 10 MeV electrons to the back of the detector house. Logarithmic Y-scale.

The number of particles penetrating the shield here are not likely to have an adverse effect on the measurement for two reasons. First of all, electrons of such high energy are relatively rare. Secondly, the simulation shows that almost all of these particles were stopped by the tungsten shield. The energy distribution discrimination scheme proposed by Andersen is thus not recommended.

## 5 TIME-TO-DIGITAL CONVERSION

Information in this section is gathered from [Henzler, 2010] if not otherwise specified. Time-to-Digital converters are used in a wide range of applications such as particle detectors, Time-of-Flight measurements, LIDARs and even Phase-Locked Loops (PLLs) where they serve as phase detectors. It can be implemented in many ways, but most commonly it is implemented in Field Programmable Gate Arrays (FPGAs), ASICs or Complementary Metal–Oxide–Semiconductor (CMOS) processes where control of the time domain is great. The simplest way to do a Time-to-Digital conversion is to employ a digital counter that is enabled by some input and counts clock edges. The main benefit of using a counter is the superb range; incrementing the number of bits in the counter doubles the range. The drawback is that the resolution of the conversion is limited by the clock period, requiring very high clock speeds for accurate conversion. This is impractical due to difficulty of clock generation and excessive power consumption. Methods exist to achieve sub-clock period resolution, and this is an actively researched field. There is a plethora of available choices for high-resolution TDCs, but many methods are designed for implementation in CMOS processes. Fortunately, a subset of the available methods are both physically and practically realizable in FPGA fabric, and these are described here.

#### 5.1 Performance measures

There are several measures used to accurately quantify the performance of a TDC, and these will be described here. The first and most obvious performance measure is the resolution  $T_{\text{LSB}}$ . The resolution is a measure of conversion granularity and is defined as the time input period that corresponds to a change of 1 Least Significant Bit (LSB) in the binary output of the TDC. Similar to ADCs, TDCs inescapably must sample in a discrete fashion, and the time difference between the true analog input transition and the first subsequent sample is called the quantization error  $\varepsilon$ . Since the input signal is asynchronous, this error means that this is not an invertible relationship, i.e. the true interval cannot be repoduced exactly from the digitized value. The relationship between the input time and the binary output vector N may then be described as,

$$T_{in} = NT_{\rm LSB} + \varepsilon \tag{5.1}$$

If the input signal is not correlated with the TDC sampling clock, the quantization error is an equally distributed random error constrained between 0 and  $T_{\text{LSB}}$  with a mean value  $\langle \varepsilon \rangle = \frac{1}{2}T_{\text{LSB}}$ . The quantization error contributes to the noise floor of the conversion, and cannot be improved without improving the resolution.

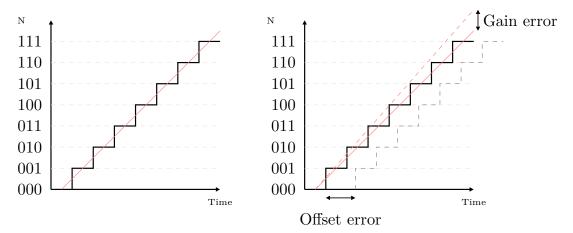

#### Offset error and gain error

Offset error and gain error can be described by the linear ideal transfer function  $N = dt + N_{\text{offset}}$ . The offset is the output for t = 0, and can be adjusted by shifting the staircase to match the offset error. The gain error is the error in the transfer function with respect to the ideal transfer function. This happens in a delay line if, for instance, the operating temperature is increased, which in turn increases the propagation delay of

each element. If a delay line is matched to the clock period, it would now be impossible for the last bits in the delay line to transition before the next clock edge.

Figure 29: Left: Ideal input-output characteristic of a TDC. Right: Linear imperfections that may appear in a practical implementation.

#### Non-linearity

Differential non-linearity (DNL) is a measure of how much each step deviates from the nominal width  $T_{\text{LSB}}$ . It is a measure for each step, but usually a single figure is stated, which corresponds to the DNL of the worst step. It is normalized to 1  $T_{\text{LSB}}$ , and can be both negative and positive. For instance, a step of width  $\frac{1}{5}LSB$  has a DNL of -0.8.

Integral non-linearity is the stepwise distance from the ideal transfer function and the actual transfer function. In the same fashion as DNL, the number for the worst step is typically stated. It is tempting to think of this as the sum of the DNL, but the DNL contains both the gain and non-linearity error, whereas the INL only contains the non-linearity error. If every step in the transfer function is off by the same amount, the integral non-linearity would be zero, although each DNL step is non-zero.

#### 5.1.1 Conversion in the presence of noise

The detrimental effects discussed above are obtained using static measurements, and are attained by averaging several measurements to reduce the presence of noise in the measurements. In a real situation, noise from peripheral circuitry does affect the measurement, and dynamic performance measures are required. For ADCs, these are typically SNR and Effective Number of Bits (ENOB). Measuring the SNR of an ADC is trivial, as an analogue signal, being continuous, inherently has a much higher resolution than the ADC, and a simple sinusoidal wave can be fed into the ADC. For TDCs there is no simple way to generate a sinusoidal sequence that encompasses all possible time intervals, so a different approach is needed to define equivalent performance measures.

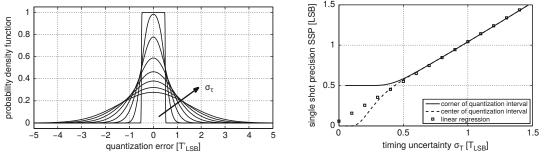

The single shot experiment is introduced to create an equivalent of these measurements for TDCs. Instead of using a sinusoidal signal to convert each possible voltage level, a fixed time interval is repeatedly applied to the TDC. Without noise, the resulting value would be the same each conversion. The standard deviation of the difference in the actual measurements is defined as the Single Shot Precision (SSP). The quantization error is shown for increasing timing uncertainty  $\sigma_{\tau}$  in Figure 30. In the ideal case, with no error introduced by noise, the lower bound on the precision is placed by the quantization error of  $\pm \frac{1}{2}T_{\text{LSB}}$ . This is illustrated by the experiment being carried out both when the time interval is placed exactly in the middle of a quantization interval, and when the interval is placed in the corner of a quantization interval. In the former case, there is no quantization error and the SSP approaches the ideal 0. For timing uncertainties of above  $\frac{1}{2}T_{\text{LSB}}$ , there is little difference, and single-shot precision increases linearly with timing uncertainty. Because of this, SSP is often used as a real measure of resolution.

Figure 30: Left: Time interval dependent probability quantization error function. Right: Single-shot precision. [Henzler, 2010, p. 29, 31].

# 5.2 Calibration methods

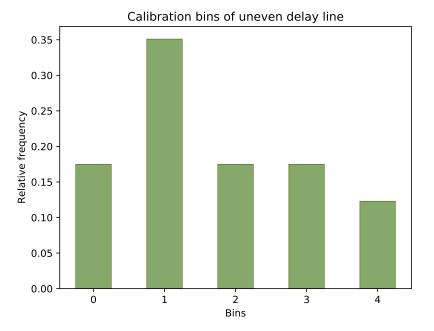

Ideally each conversion step should be of equal width as shown in Figure 29 (left). One shortcoming of implementing a TDC in an FPGA is that the steps will have varying width, resulting in a high DNL compared to a CMOS implementation where control over delay and routing is much greater. The primary cause of DNL in an FPGA is uneven routing delays between cells. This is very pronounced in those interconnects that bridge logic cells together, resulting in what is known as *ultrawide bins*. Because of the uneven nature of FPGA circuits, it is very important to calibrate the bins to the circuit. Another worry is the variance of Process, Voltage and Temperature (PVT) affecting the speed of the circuit. While process variation can be treated as static in an FPGA (unless programming multiple FPGAs with the same configuration), temperature and voltage cannot. In a review paper of TDC methods, four methods to calibrate the bin widths are described [Tancock et al., 2019]. One of these is manual calibration which is not of interest because it cannot be performed by the FPGA post-programming and thus does not solve the PVT dependency. The remaining three are described in the following sections.

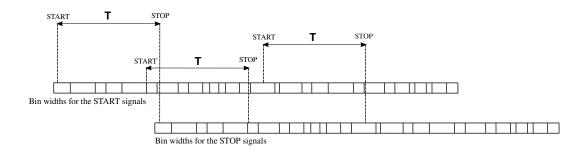

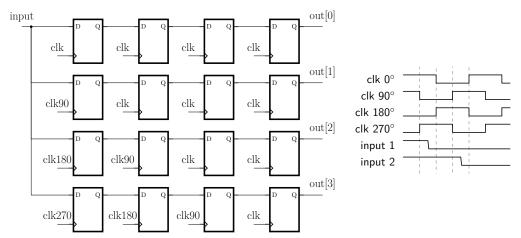

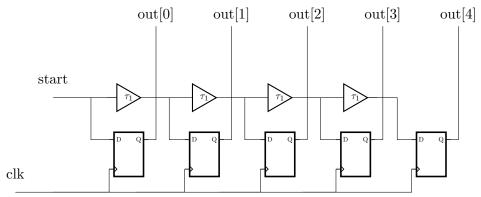

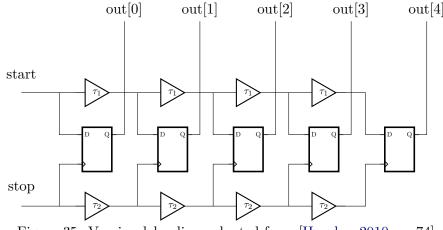

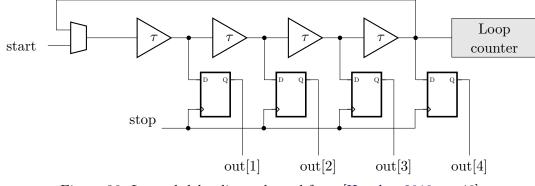

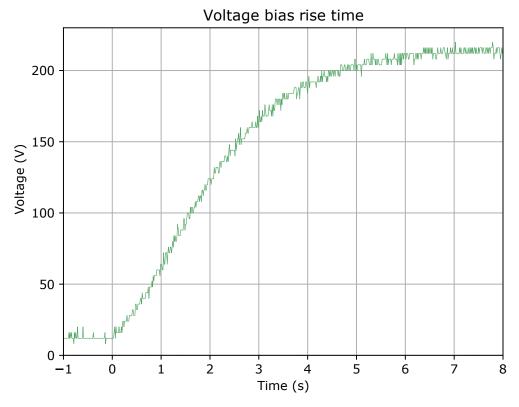

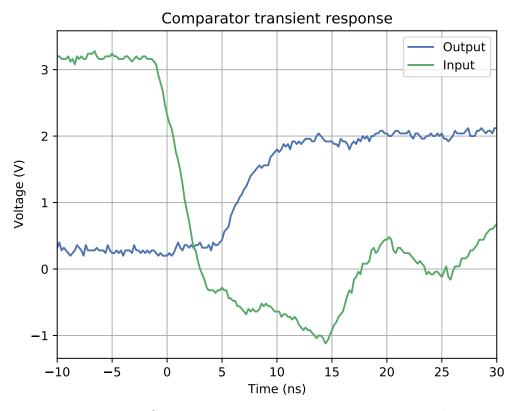

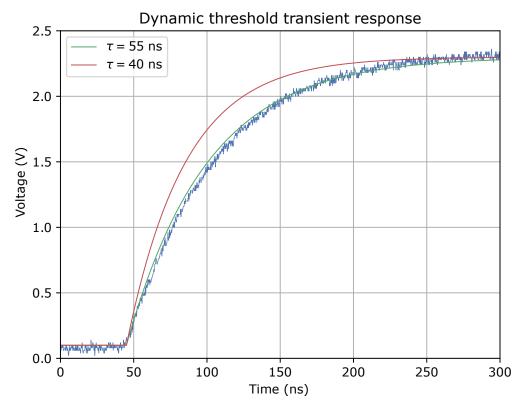

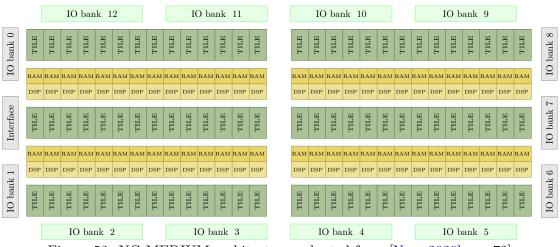

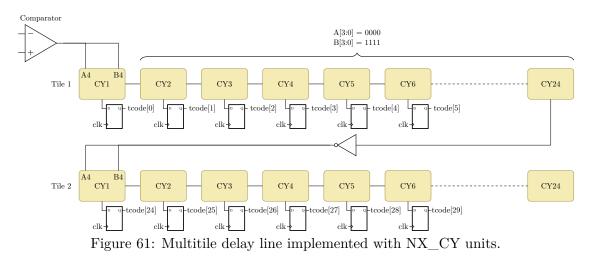

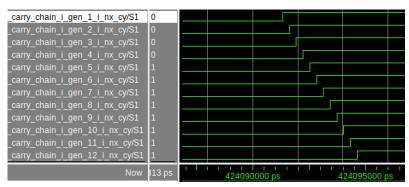

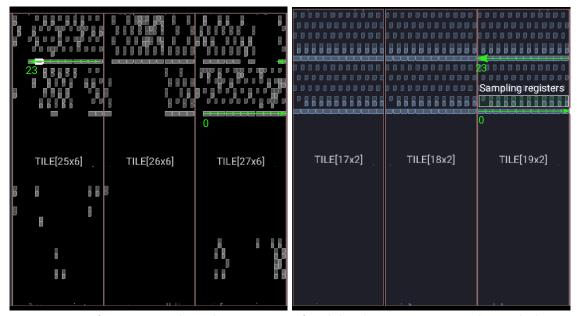

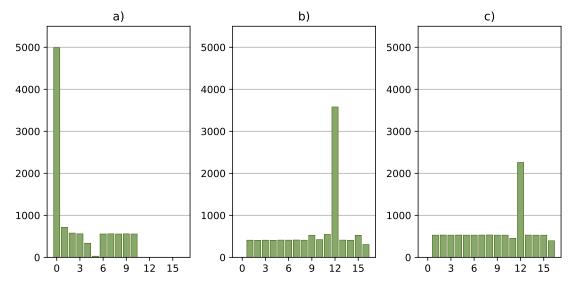

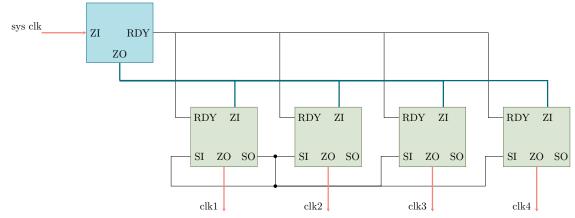

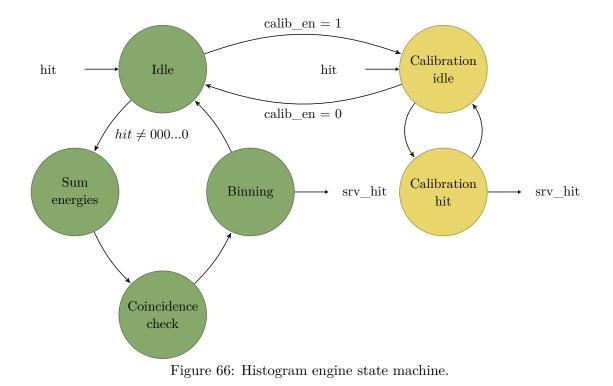

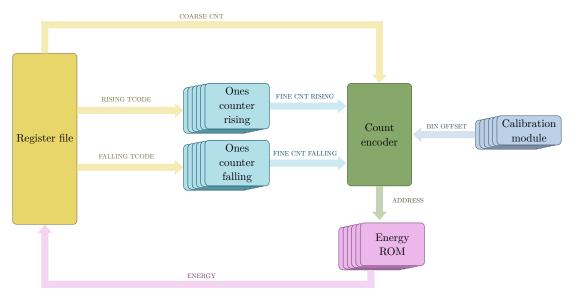

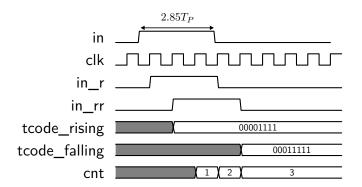

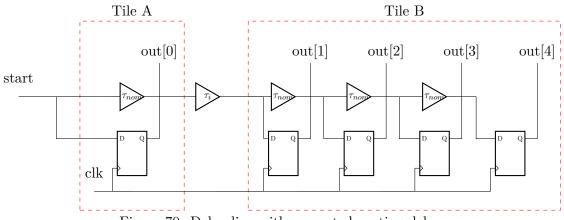

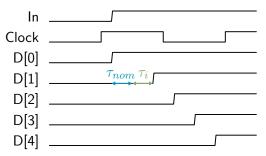

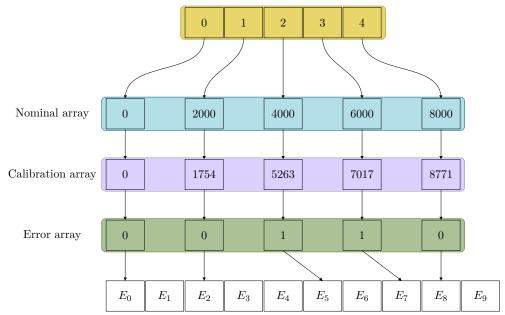

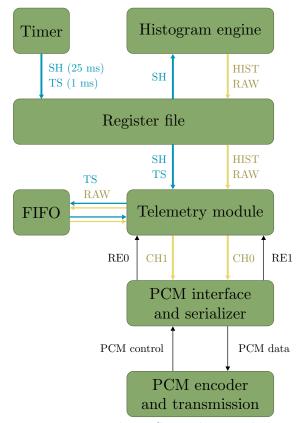

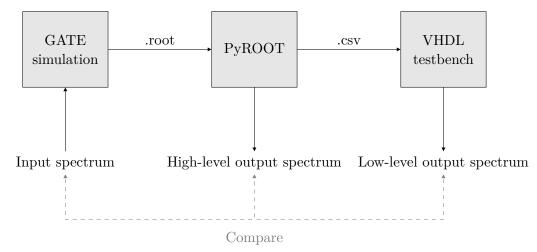

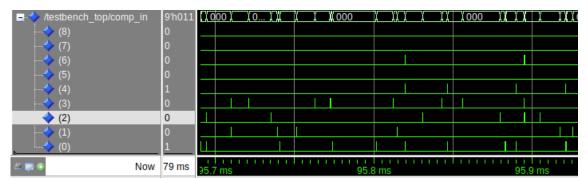

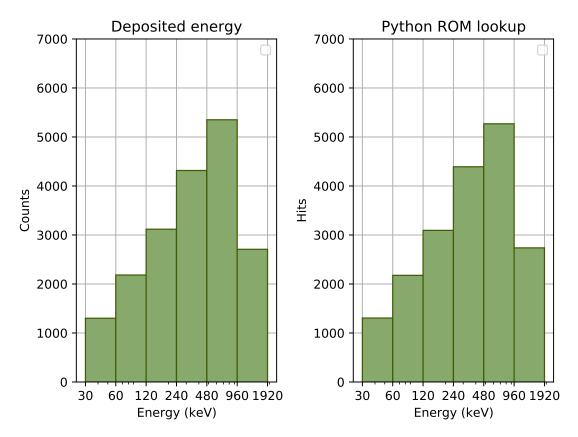

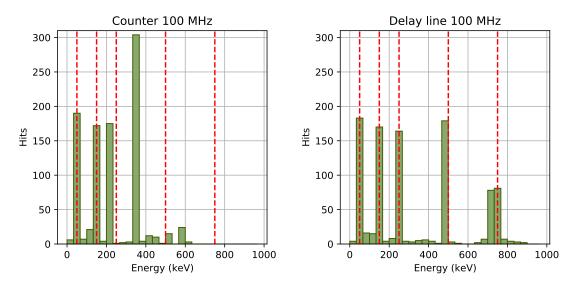

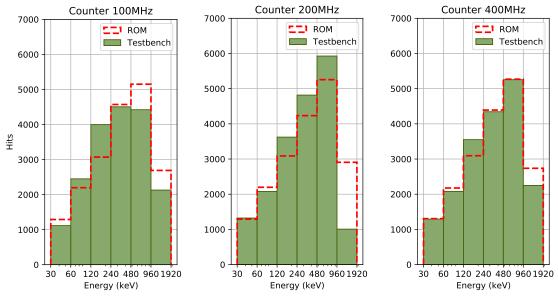

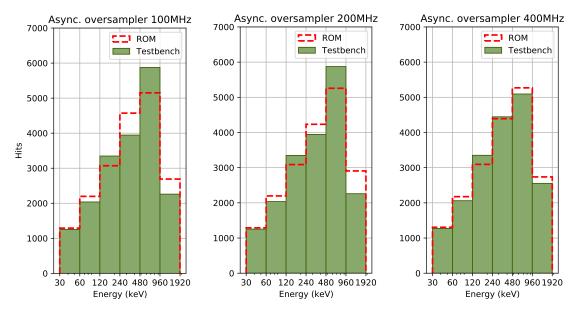

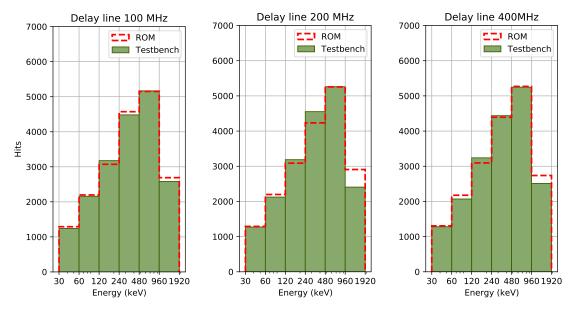

#### 5.2.1 Statistical calibration