# **University of Bergen**

Geophysical Institute

Master Thesis in Energy Electrical Power Engineering

# Control of Grid Connected Inverter

Sami El Habbach

08.08.2022

# **Preface**

This master thesis concludes the effort of a five year long education for the degree of Master of Science in the field of electrical power engineering at the University of Bergen. The thesis has been submitted in partial fulfilment after having been worked on over the course of two semesters. I am grateful over the Western Norway University of Applied Sciences for providing an office space and a steady work environment from fall 2021 to spring 2022.

I would like to express my sincerest gratitude to my master thesis supervisor: Assistant Professor Eirik Haustveit, for his knowledge, patience and for providing necessary feedback throughout the final two semesters of my thesis. I would also like to express a special thanks to Assistant Professor Omes Jawaid Bajwa, for providing me with practical ideas and for his support.

Finally I wish to express my deepest gratitude to my fellow master students whom I have been working along side for the past two years, some of whom I have had the pleasure of knowing since the start of my five year education. Their presence has been a guiding light towards the completion of my studies, and I would like to thank them for sharing their knowledge and experiences.

# Abstract

Power electronic converters and their control systems have played a significantly important role in the integration of renewable energy systems. The application of these converter systems have been rapidly growing as of late, and the subject of improving the systems by means of control is a key topic in research today. The Active Front End (AFE) converter, which allows for the bidirectional power-flow is one of such systems with the possibility of grid tied connection. This master thesis embarks on some of the methods which can be used to provide control over a Grid tied inverter (GTI), for the sake of charging and discharging a battery supply/load. The thesis has been separated into several chapters starting with the needed theoretical framework as an overview over the preliminary knowledge required for the rest of the thesis. The following chapters provide in detail all the required parts of the control and the design of the converter system. Once these chapters have been presented the simulation model is introduced with its results. The last chapters conclude the work by presenting the physical hardware components for a prototype, ending with the final chapter presenting the conclusions and suggestions for future work.

# Acronyms

**ADC** Analog to digital conversion. 103

**AFE** Active Front End. ii, 6–8, 101, 104

**BESS** Battery Energy Storage System. 12, 25–27, 81, 84, 104

CCL Current Control Loop. 32, 41, 42, 44, 54, 59, 67–70, 105, 106

**CCM** Continuous conduction mode. 13, 14, 104

**DAB** Dual Active Bridge. 101, 102

**DCM** discontinuous conduction mode. 13, 14, 52, 104

**DERs** Distributed Energy Resources. 1, 2

**DG** Distributed Generation. 1, 2

**DPC** Direct Power Control. 28, 30, 43, 44, 69, 70, 72, 74, 102, 105, 106, 116

ESS Energy Storage System. 52, 59

**EV** Electric vehicle. 2

**FFT** Fast Fourier Transform. 70, 72, 74, 76, 123

**GTI** Grid tied inverter. ii, 2, 3, 5, 6, 28, 38, 41, 45, 69, 70, 72, 83, 90, 98, 99, 101, 102, 105

**IEC** International Electrotechnical Commission. 6, 7

IEEE Institute of Electrical and Electronics Engineers. 6, 7, 46, 50, 74, 75, 79, 80, 102

**IGBT** Insulated Gate Bipolar Transistor. 6, 8, 9, 12, 51–54, 64, 65, 86, 98, 99, 103, 136

KCL Kirchhoff's Current Law. 10

iv Acronyms

KVL Kirchhoff's Voltage Law. 10

MCU Microcontroller. 83, 84, 86, 87, 93, 99, 100, 103

**MO** Modulus Optimum. 18, 20–22, 41, 55, 67, 68, 109

MOSFET Metal oxide semiconductor field effect transistor. 6, 8

P Proportional. 19

PCB Printed Circuit Board. 83, 84, 86–88, 90, 103, 107, 132

**PF** Power Factor. 8, 81

PI Proportional Integral. 17–21, 38, 41, 42, 44, 54, 55, 63, 67–69, 104, 106, 109

PLL Phase Locked Loop. 3, 38, 41, 59, 62, 63, 67, 71, 77, 105

**PQ** Power Quality. 8, 22

**PWM** Pulse Width Modulation. 8, 9, 14, 32–34, 36, 38, 45, 51, 63, 67, 104, 106

RMS Root Mean Squared. 22, 23, 46

SO Symmetrical Optimum. 20, 22

SPWM Sinusoidal Pulse Width Modulation. 33, 34, 37, 65, 66

**SRF-PLL** Synchronous reference frame PLL. 38

SVM Space Vector Modulation. 34, 36, 37, 51

SVPWM Space Vector Pulse Width Modulation. 25, 34, 63–67, 102, 105

**TF** Transfer function. 19–21, 38, 54–57, 105

**THD** Total Harmonic Distortion. 22, 23, 46, 50, 70, 71, 73–76, 78–80, 102, 109

**THIPWM** Third harmonic injection Pulse Width Modulation. 37, 105

**UPF** Unity Power Factor. 42, 43, 68, 69, 72, 75, 79, 80

**UPS** Uninterruptible Power Supply. 6

VCL Voltage Control Loop. 41, 42, 59, 67, 68, 70, 78, 105, 106

VOC Voltage Oriented Control. 28, 41, 42, 54, 68, 70, 74, 102, 105, 106

# Contents

| P            | refac | e       |                                     | i   |

|--------------|-------|---------|-------------------------------------|-----|

| $\mathbf{A}$ | bstra | ıct     |                                     | ii  |

| $\mathbf{A}$ | crony | yms     |                                     | iii |

| $\mathbf{C}$ | ontei | nts     |                                     | v   |

| 1            | Inti  | oduct   | ion                                 | 1   |

|              | 1.1   | Backg   | round                               | 1   |

|              | 1.2   | Objec   | tives                               | 2   |

|              | 1.3   | Outlin  | ne                                  | 3   |

| 2            | The   | eoretic | al Framework                        | 5   |

|              | 2.1   | Conve   | erter systems                       | 5   |

|              |       | 2.1.1   | grid-tied standards                 | 5   |

|              |       | 2.1.2   | Active Front End Converter overview | 6   |

|              |       | 2.1.3   | Three phase inverter                | 8   |

|              |       | 2.1.4   | DC-DC converter topologies          | 12  |

|              | 2.2   | Contr   | ollers                              | 17  |

|              |       | 2.2.1   | Hysteresis controller               | 18  |

vi CONTENTS

|   |     | 2.2.2    | Proportional Integral Controller (PI)         | 19 |

|---|-----|----------|-----------------------------------------------|----|

|   |     | 2.2.3    | Controller tuning and optimizations           | 20 |

|   | 2.3 | Power    | Waveform Distortions                          | 22 |

|   | 2.4 | Filter   | Methods                                       | 23 |

|   | 2.5 | Batter   | ry Energy Storage Systems - BESS              | 25 |

| 3 | Con | ntrol st | ructure and strategies of grid tied converter | 28 |

|   | 3.1 | Clark    | and Park transform                            | 28 |

|   |     | 3.1.1    | Clark transformation                          | 29 |

|   |     | 3.1.2    | Park transformation                           | 31 |

|   | 3.2 | Pulse    | Width Modulation - PWM                        | 32 |

|   |     | 3.2.1    | Sinusodial Pulse Width Modulation - SPWM      | 33 |

|   |     | 3.2.2    | Space vector pulse width modulation - SVPWM   | 34 |

|   | 3.3 | Phase    | Locked Loop - PLL                             | 38 |

|   | 3.4 | Contro   | ol strategy                                   | 39 |

|   |     | 3.4.1    | Voltage oriented control - VOC                | 41 |

|   |     | 3.4.2    | Direct Power Control - DPC                    | 43 |

| 4 | Con | verter   | Modelling and Design                          | 45 |

|   | 4.1 | LCL F    | Filter Design methodology                     | 46 |

|   | 4.2 | DC-lin   | nk                                            | 51 |

|   | 4.3 | Propo    | sed DC-DC Model                               | 52 |

|   | 4.4 | PI Co    | ntroller Optimization and Analysis            | 54 |

| 5 | Sim | ulation  | n Model                                       | 58 |

|   | 5.1 | Coord    | inate transformations - Clark and Park        | 61 |

|          | •                      |

|----------|------------------------|

| CONTENTS | $\mathbf{V}\mathbf{I}$ |

|          |                        |

|   | 5.2 | Phase Locked Loop - PLL |                                       |    |  |

|---|-----|-------------------------|---------------------------------------|----|--|

|   | 5.3 | PWM                     |                                       |    |  |

|   | 5.4 | PI Controller           |                                       |    |  |

|   | 5.5 | Converter Control loops |                                       |    |  |

|   | 5.6 | Simula                  | ation Tests and results               | 70 |  |

|   |     | 5.6.1                   | Initial Simulation tests              | 70 |  |

|   |     | 5.6.2                   | Inverter Operation                    | 74 |  |

|   |     | 5.6.3                   | Rectifier Operation                   | 78 |  |

|   |     | 5.6.4                   | Bidirectional Operation               | 80 |  |

| 6 | Har | dware                   | and Prototype PCB circuits            | 83 |  |

| U |     |                         | V -                                   |    |  |

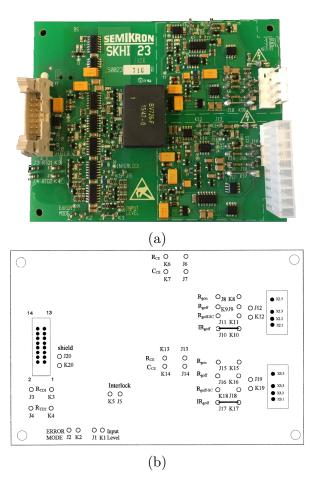

|   | 6.1 | Micro                   | controller unit - MCU                 | 84 |  |

|   | 6.2 | Scalin                  | g and offset                          | 85 |  |

|   | 6.3 | Initial                 | ly intended Modules                   | 86 |  |

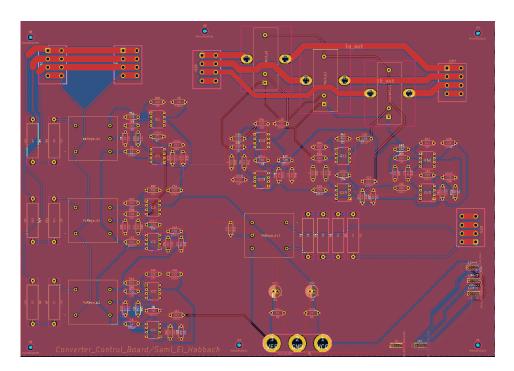

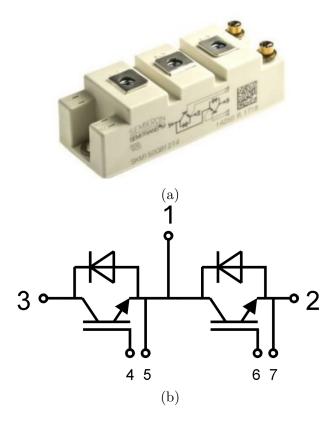

|   |     | 6.3.1                   | Power module (transistors and driver) | 86 |  |

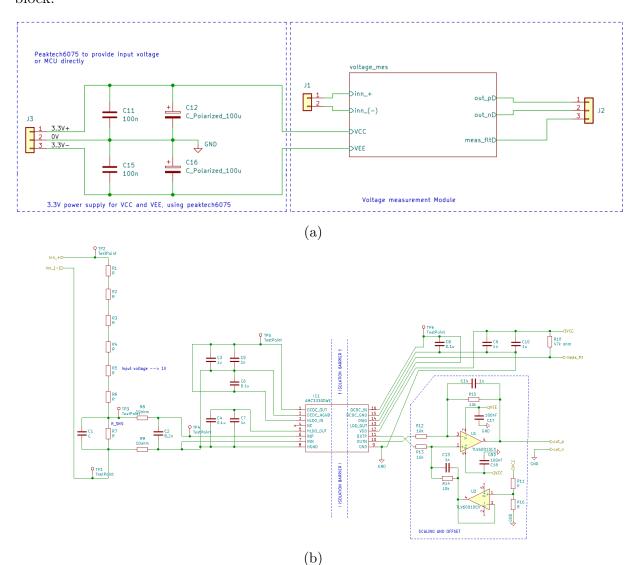

|   |     | 6.3.2                   | Voltage Measurement Module            | 87 |  |

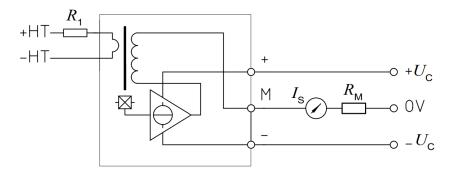

|   |     | 6.3.3                   | Current Measurement Module            | 89 |  |

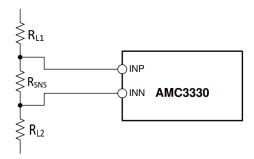

|   | 6.4 | Altern                  | native Measurement Modules            | 90 |  |

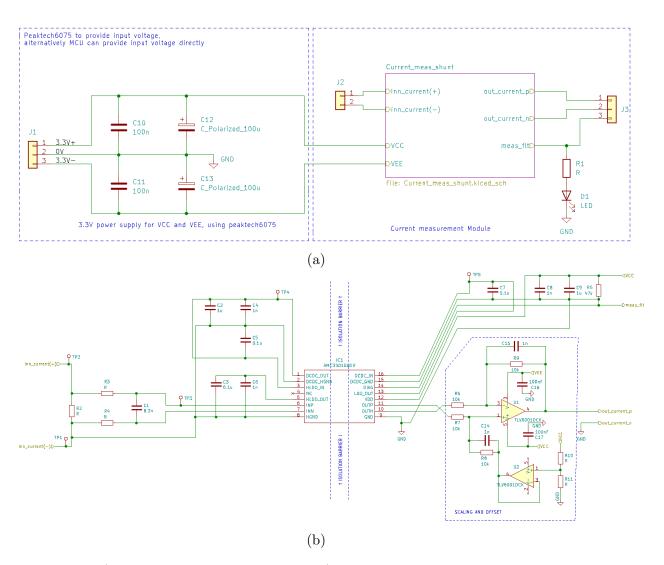

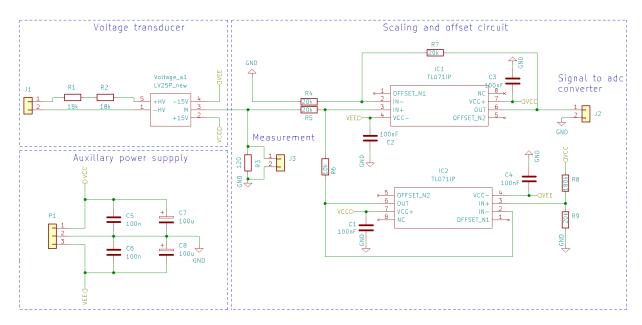

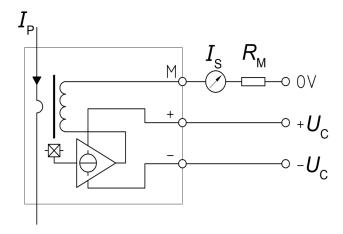

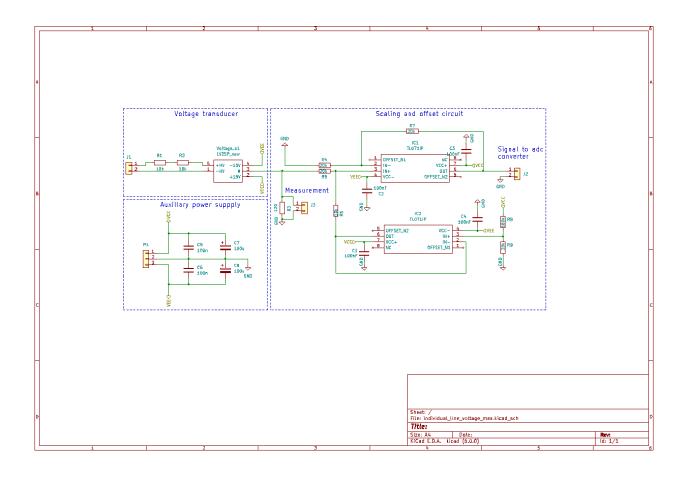

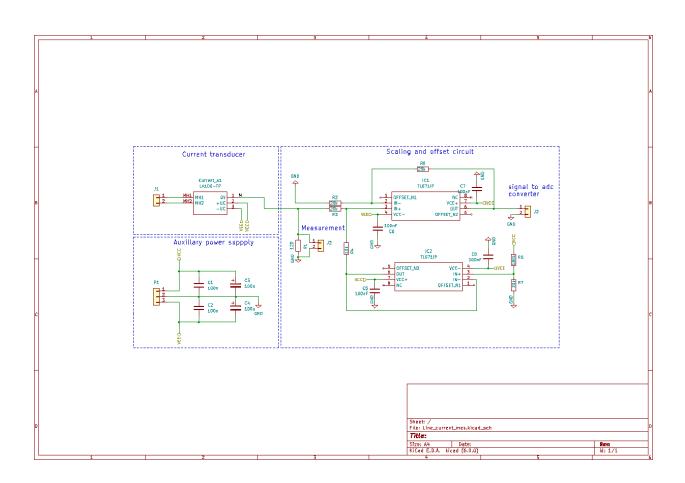

|   |     | 6.4.1                   | Voltage Measurement circuit           | 91 |  |

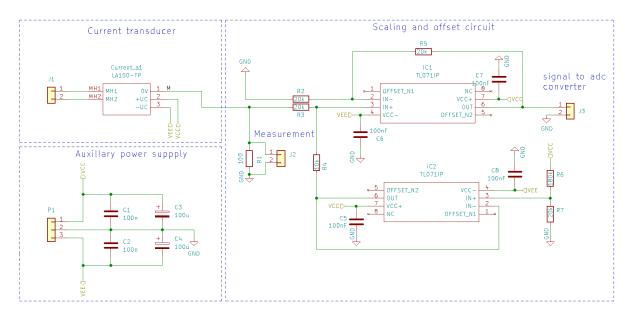

|   |     | 6.4.2                   | Current Measurement circuit           | 94 |  |

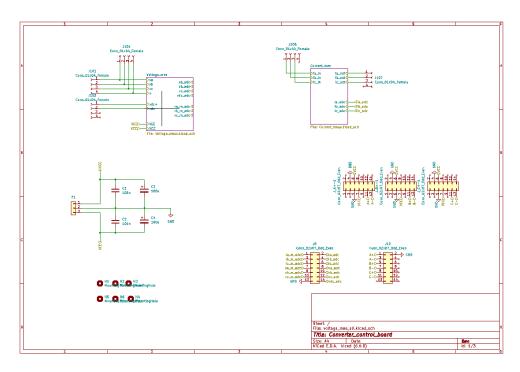

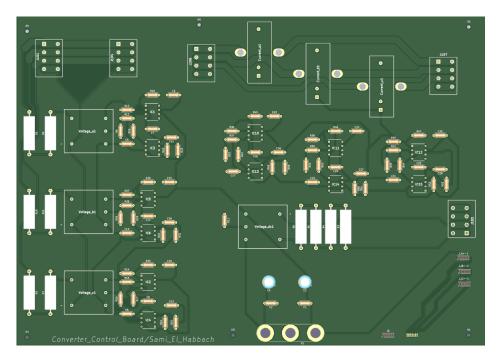

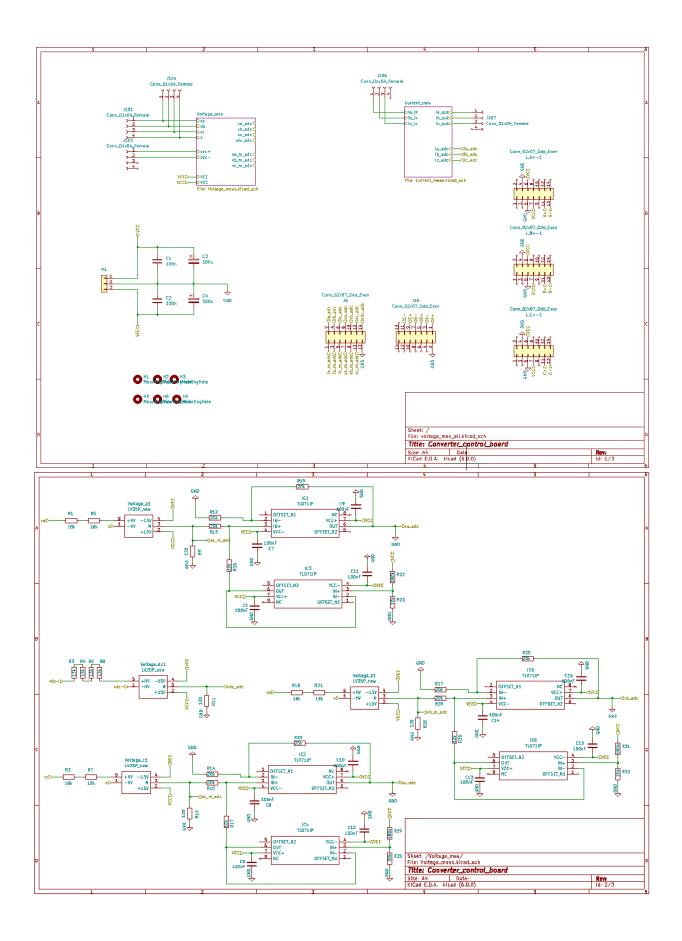

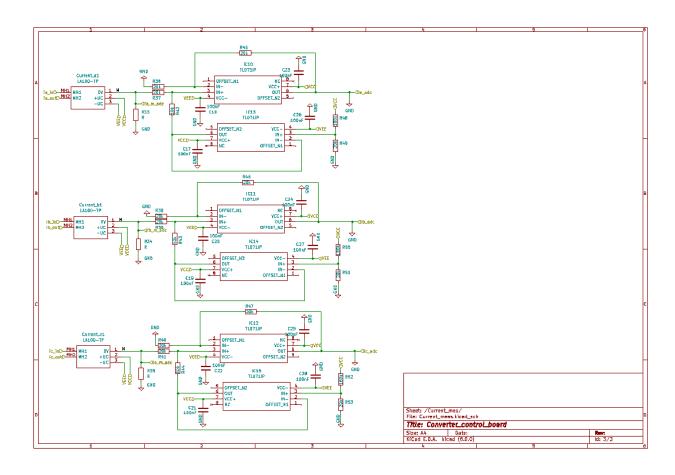

|   |     | 6.4.3                   | Converter Control Board               | 96 |  |

|   | 6.5 | IGBT                    | component                             | 98 |  |

|   | 6.6 | Transi                  | istor Driver card                     | 99 |  |

|   |     |                         |                                       |    |  |

| viii | CONTENTS |

|------|----------|

| List of Figures | 104 |

|-----------------|-----|

| List of Tables  | 109 |

| Bibliography    | 110 |

| Appendices      | 115 |

| A Matlab code   | 115 |

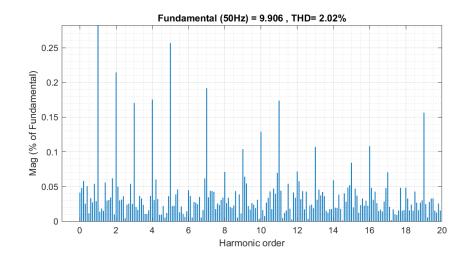

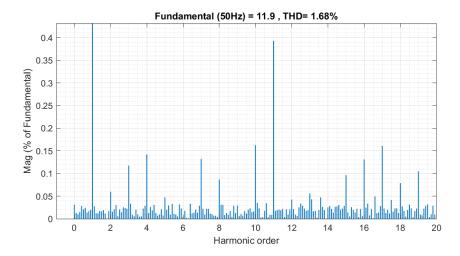

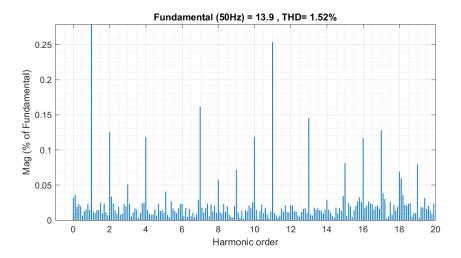

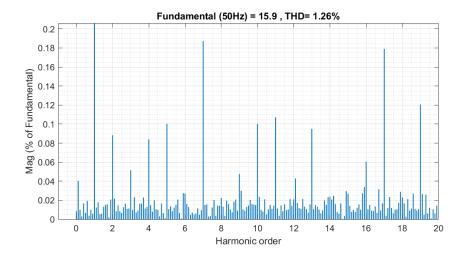

| B FFT analysis  | 123 |

| C Schematics    | 132 |

| D Datasheets    | 136 |

# Chapter 1

# Introduction

## 1.1 Background

The global electrical infrastructure in the latest years has been going through rapid changes, while motivated by the growing concerns over climate change and the environmental degradation. The systemic shift of the global energy structure has also been driven by the increased demand for electrical energy and the rapid technological advancements, particularly in the field of power electronics and the growing battery innovations. Such advancements are playing a key role to the transition towards clean energy and global sustainability.

Climate change and the environmental concerns have lead to policy changes and international treaties such as the "European Green Deal" with its goal to make Europe climate neutral in 2050. The currently proposed strategy to achieve this is by developing a systemic shift from the fossil fuel-based energy infrastructure towards the renewable energy sources and to develop greater improvements in energy efficiency [1]. Conventionally the traditional power generation stations have utilized large synchronous generators, built to operate with a fixed speed and frequency. The generated power is generally transmitted over the electric grid through large centralized facilities, such as fossil fuel based power plants. While the traditional methods have been advantageous they do not come without their own problems. Such as the loss of efficiency due to the large distance the generated energy is transported and should the grid go down, numerous people will be left without power. The development of smaller power systems which are located nearby their respective loads offers a solution, thereby the issues in the Distributed Generation (DG) can be avoided.

Distributed Energy Resources (DERs), are small-scale electrical resources or controllable

2 Introduction

loads that are often interconnected with a nearby distribution system or the electrical grid. The DERs include a variety of energy generation systems such as PV solar panels, wind turbines, electrical energy storages and Electric vehicle (EV). Through the development and integration of such systems the future of the power system is going towards a smart grid, offering more control and communication between the producer and the consumer of the energy system. While also offering a viable solution towards the reduction of environmental pollution though the degradation of carbon based energy resources, while gradually developing systems which are better suited to be interconnected with renewable energy sources. This can be observed by the exponential growth of the PV power plants and the massive wind farms which are being constructed worldwide. However it must be stated that the increased development towards a smart grid has come with its own challenges, such as causing the grid structure to become far more complex. The reliability of the renewable energy sources come to question as the overall energy which can be collected can vary greatly due to numerous reasons, such as the meteorological conditions. Furthermore there can often be geographical limitations to these systems, in addition the grid-stability and power quality can be greatly effected by the volatile power generation of such system. While generally these issues have been previously solved through the use of conventional power plants containing large scaled synchronous generators and by the use of reliable and consistent fossil fuel based energy sources such as coal or natural gas. However with the external utility grid seeing an increase of connectivity with DG units, the issues pertaining to the use of renewable energy sources must be solved through the distribution [2].

These growing challenges which we are now faced with, can be prevailed through proper integration and control of the power electronic converters which are contained in their respective generation units. Fortunately the rise of technological advancements and the massive benefits related to the control of power electronic converters. Have lead to great interests being shown in the further research and development of such systems in the last few years. These developments include a copious amount of topologies such as the GTI, and the various control algorithms and methods of grid synchronization. Some of which will be presented in detail in the coming chapters of this thesis.

## 1.2 Objectives

The objective of this thesis is to design and implement a grid tied three phase bidirectional inverter connected to a battery. In addition to designing and utilizing a variation of control methods to be compared with each-other. The objectives of this thesis is intended to be completed in a set of steps which are as stated:

1.3 Outline 3

• Studying past research articles and methods which have been utilized, for the construction of a successful inverter and active front end converter systems.

- Selection of a three phase inverter and DC-DC topology with bidirectional power flow capabilities, while also displaying the characteristics.

- Selecting the different control and modulation structures which are to be used, and develop proper tuning methods for the controllers.

- Designing and calculating the proposed converter filter, while taking standards and requirements of grid connected converter systems into consideration.

- Designing the chosen converter topology and confirming its function using simulation software. choosing the necessary components and testing the bidirectional power flow capability, as well as the different control methods.

- Collecting all the necessary components and constructing a functioning prototype.

Take measurements and compare with simulation test results to verify the control methods.

### 1.3 Outline

The master thesis rapport is divided between the theory and the engineering of the converter model. The theoretical framework as well as the control structure is introduced in chapter 2 and 3. This part of the thesis has more emphasis on the theory behind the required parts which are needed to build and control a grid tied inverter with bidirectional capabilities. Chapter 2 introduces the theoretical framework pertaining to the GTI which will be used further in this thesis. Furthermore DC-DC converter topologies which can be used with the battery supply/load are presented along with several key topics such as filtering, controllers and waveform distortions. While chapter 3 focuses on the control system structure and strategies which are used in the later simulated model. Such as the Park and Clarke coordinate transformations, Phase Locked Loop (PLL) structure, modulation strategies and so on.

Following these two chapters, comes the design and simulation of the converters system and its components which is split into chapters 4 and 5. Where chapter 4 presents the systems proposed topology including all parts such as the filter, inverter and the DC-DC converter with the battery supply/load. This chapter also explains how the different components are dimensioned and how the gain constants for the control are acquired.

4 Introduction

Chapter 5 presents the simulation model using the simulation software known as Matlab Simulink and all its components, in addition to introducing and explaining alternative methods for both control and modulation. This chapter ends with the results from the simulation model showing different modes of operation.

Chapter 6 presents the physical hardware and components which are used or was intended to be used, as well as the design schematics of the intended PCB circuits. Due to a global chip shortage some alternative methods where necessary and have been presented as well.

Chapter 7 contains the final conclusions and discussion of the thesis. The approach which was taken in the completion of this thesis as well as the challenges are discussed in more detail during this chapter.

# Chapter 2

# Theoretical Framework

This chapter serves to give an overview of the fundamental knowledge as a prerequisite to the design of a grid connected inverter that is capable of bidirectional power flow. This chapter takes emphasis on converter topologies used for three phase DC-AC conversion, while also introducing DC-DC converter topologies that can be used in a two stage topology. Which can be necessary for the sake of bidirectional operation and a stable DC-link while using a battery supply/load. However the main topic of this thesis is the GTI which will be presented with far more detail throughout this thesis, while the DC-DC converters will only be introduced to present a necessary background for the selection and operation. Furthermore various topics concerning the control, power waveform distortions and grid filtering methods are presented.

# 2.1 Converter systems

The converter in a power electronic system is one of the main components and the focus of this thesis. In this section some of the required standards when designing a grid tied converter will be presented. Three phase inverter topology and DC-DC converter topologies which will be later used to connect the battery storage system will be presented with their operational principle during this section.

### 2.1.1 grid-tied standards

Three phase GTI are power converters which convert DC to AC and feed it into an existing electrical grid system. These types of converters are often used to convert the

DC which is produced by renewable energy sources such as PV plants, wind turbines and batteries which can be converted to AC and become connected to the power grid. GTIs cannot typically be used in stand-alone applications where the utility power is unavailable [3]. Standards are required when integrating such converters into the electrical grid and must follow a list of requirements which are relevant to the performance, operation, testing and safety of the applications. Therefore when one seeks to design a grid connected converter system, it becomes necessary to undergo research on the rules and regulations for the requirements to be met. These standards however can be subject to variations based on where the system is intended to be applied. However for the most part these standards tend to be quite similar and mostly based around two international standards being the Institute of Electrical and Electronics Engineers (IEEE) and International Electrotechnical Commission (IEC). Additionally as many of the grid tied converter system applications utilize renewable power sources and/or Uninterruptible Power Supply (UPS) systems it can also be important to research the standards built specifically for them. Some of the most relevant standards which provides the requirements for the interconnection of distributed generation resources into the grid, are as follows:

- 1547-2018 IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces [4].

- 61850 IEC Communication networks and system for power utility automation [5].

These standards which have been presented are not specifically targeted towards any particular application, and serve more as a general requirements. Should the need of more specific applications be considered such as renewable energy sources there are different standards that must be researched and complied for overall approval. This master thesis has an emphasis on the control of the GTI system. which is why further standards which specify the limitations of the distortions to the system must also considered. Such as: 519-2014 - IEEE standard for Harmonics [6].

#### 2.1.2 Active Front End Converter overview

The AFE converter is a power electronic converter which generally uses controllable switches such as the Insulated Gate Bipolar Transistor (IGBT) or Metal oxide semi-conductor field effect transistor (MOSFET) for power conversion. An AFE is generally connected to the grid through a passive filter, which consists of an inductor or the combination of inductors and capacitors, as will be explained in further detail in a later

section. The application of an AFE converter can be anywhere from power conversion for grid-tied electrical applications, motor drives and power conditioning. AFE converters are becoming more and more popular as the power ratings are increasing while the costs of the power electronic converters and device components are decreasing. With the use of renewable sources on the rise such as photovoltaic systems and wind power, the added benefits of utilizing the AFE converters as part of the drive system becomes important considering the necessary control and requirements that must be upheld following the standards, generally IEEE or IEC standards. Furthermore this becomes driven by the continuous advancement in technological development of power electronics, semiconductor devices and advanced control methods. Some of the advantages of an AFE converter are as follows[7][8]:

#### • Reduced harmonic distortion in the grid

The AFE converter utilizes controllable switches which allow for better control over the power conversion. Such as the capability of using complex modulation strategies which reduce the harmonic distortion. This advantage is quite apparent when compared to the simple thyristor and diode based converters which are more limited in their control and harmonic levels.

#### • Bidirectional power flow

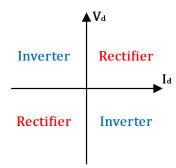

Perhaps the most advantageous feature which we acquire from the AFE topology is the bidirectional power flow capability, which is attained from the converter being capable of operating in all four quadrants of the V-I plane, as shown in figure 2.1 As depicted in the illustration one can see that there are two quadrants of operation wherein the converter acts as a rectifier and vice versa as an inverter.

Figure 2.1: V-I plane with four quadrant operation of an AFE converter, adapted from [8].

#### • Forced commutation

Due to the nature of controllable switches having the ability to switch on and off when it is required, we gain the advantage of utilizing forced Commutation independent of the line voltage. Forced Commutation is something which can occur numerous times during a single period based on the operation, and allows for modulation of the drawn current by controlling the gate pulses relative to the reference signal. Furthermore by applying proper control strategies the dc voltage level of the converter can be controlled to be within a desirable boundary.

• Reactive power control, Active power filter and enhanced grid stability

The reactive power flow of the converter is controllable and can be regulated to

achieve and maintain desired Power Factor (PF) such as unity. As mentioned

earlier in this section the AFE converter has the capability to regulate the grid

current, which allows for the converter to be used for power conditioning purposes.

This is achieved by harmonic cancellation with the use of active current injection

into the non-fundamental frequency into the grid. By applying these capabilities

we can contribute to an overall increased grid stability.

Generally the performance of a converter is determined by its means of efficiency, output Power Quality (PQ), harmonic distortion, the complexity of both the topology and control circuit in addition to the overall cost of implementation. AFE converters use controllable switches which allows for them to be switched on and off at any given time. With this advantage forced commutation becomes possible regardless of the line voltage, and the drawn current can be modulated based on the control of the gate pulses and reference signal. The quality of this output current will improve with the increase of commutations per cycle of the output voltage, but in turn will lead to energy loss due to the switching. Which is why selecting the proper type of controllable semiconductor switches is essential to reduce this loss, a simple rule of thumb is to use IGBTs when the switching frequency is less than 21 kHz and MOSFETs when its above if the application allows for it. This method of controlling the commutations (switching) to gain the desired current/voltage relative to a reference signal is known as Pulse Width Modulation (PWM), and is used in state of the art converters to enable the power transfer [9][10].

### 2.1.3 Three phase inverter

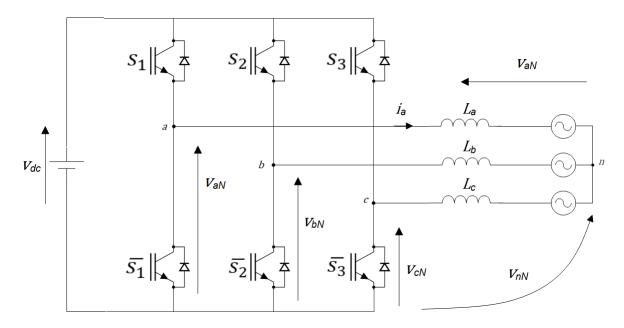

A three-phase two-level inverter topology is illustrated in figure 2.2, containing as the name implies three legs with two controllable switches on each leg. Power electronic converters schemes such as three phase inverters can produce a highly distorted current to the grid, this is considered undesirable and can cause numerous problems and reduce the efficiency of the overall system. To alleviate this issue filtering becomes necessary to reduce the distortions. Installing passive filters between the grid and the converter is a solution to filtering out harmonic distortions, this will be explained in further detail in a later section of this chapter. For the sake of simplicity line inductors have been added

to act as the filter in the illustration of the inverter. This simplicity comes with the disadvantage of being bulky and considerably costly, and may therefore not be considered suitable for some applications. Commonly inverters combine the passive filter with an active filtering technique such as PWM to acquire higher efficiency and less distortion.

It is important that any of the switches in the leg of the inverter is not switched on simultaneously, as this would lead to a short-circuit across the converter system. Which can cause irreparable damage to the converter itself. To avoid undefined states in the inverter and thereby the AC output line voltages, the switches of any leg must also not be switched off simultaneously. This could lead to voltages that depend upon the respective line current polarity. Commonly a preventative measure is taken by applying a blanking time which normally will occur during the switching operation of the converter [11]. Each of the legs in the inverter consists of two IGBTs that are connected in anti-parallel

Figure 2.2: three phase voltage source inverter circuit [12].

with a flyback diode. For phase a the upper switch is named  $S_1$  and the lower switch is named  $\overline{S_1}$ , and as illustrated the inverter consists of three legs where the rest of the switches has been named accordingly. The line inductors are represented as  $L_a$ ,  $L_b$  and  $L_c$ , and for the sake of simplicity we can assume that they are all equal in size and may be used interchangeably with the term L in this section. A consideration can be made in the replacement of the IGBT switches to reduce losses if a considerably high switching frequency is used. For this thesis the switching frequencies will not exceed 20 kHz therefore the IGBTs can be considered to have good efficiency. The flyback diodes placed in the switches are installed to protect the IGBTs by providing the dc-link current a return path. Essentially solving the problem of high switching frequencies over an inductive load, which will produce voltage spikes due to the potential difference

between the switches and the inductor. This is further explained by the equation of the inductive load voltage  $V_L = L \frac{di}{dt}$ .

By applying Kirchhoff's Voltage Law (KVL) and Kirchhoff's Current Law (KCL) the voltage and current equations from the inverter illustration can be derived. As mentioned previously all the line inductors will be termed as L for the derived expressions shown.

$$\begin{bmatrix} v_{aN} \\ v_{bN} \\ v_{cN} \end{bmatrix} = L \frac{d}{dt} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix}$$

(2.1)

The switching state of the converters upper leg switches termed  $S_x$  (x=1,...,3) and their lower leg switches  $\overline{S_x}$  (x=1,...,3) can be represented by the switching signals  $S_a$ ,  $S_b$  and  $S_c$  are defined as followed:

$$S_a = \begin{cases} 1 & \text{if } S_1 \text{ on and } \overline{S_1} \text{ off} \\ 0 & \text{if } S_1 \text{ off and } \overline{S_1} \text{ on} \end{cases}$$

(2.2)

$$S_b = \begin{cases} 1 & \text{if } S_2 \text{ on and } \overline{S_2} \text{ off} \\ 0 & \text{if } S_2 \text{ off and } \overline{S_2} \text{ on} \end{cases}$$

(2.3)

$$S_c = \begin{cases} 1 & \text{if } S_3 \text{ on and } \overline{S_3} \text{ off} \\ 0 & \text{if } S_3 \text{ off and } \overline{S_3} \text{ on} \end{cases}$$

(2.4)

where the switching signals will define the output voltage value as shown in the following equation:

$$\begin{bmatrix} v_{aN} \\ v_{bN} \\ v_{cN} \end{bmatrix} = V_{dc} \begin{bmatrix} S_a \\ S_b \\ S_c \end{bmatrix}$$

(2.5)

where  $V_{dc}$  represent a DC voltage source. The phase-to-neutral voltages as shown in figure 2.2 are represented as  $v_{aN}$ ,  $v_{bN}$ ,  $v_{cN}$ . The three phase voltages can be defined using vectorial representation with a unitary vector expressed as  $\mathbf{a} = e^{\frac{j2\pi}{3}} = \frac{1}{2} + j\frac{\sqrt{3}}{2}$ . Where  $\mathbf{a}$  represents the 120° phase displacement between the phases. The instantaneous voltage space vector written in terms of inverter output voltages can be expressed as:

$$\mathbf{v} = \frac{2}{3}(v_{aN} + \mathbf{a}v_{bN} + \mathbf{a}^2v_{cN}) \tag{2.6}$$

This way the switching state  $(S_a, S_b, S_c) = (0, 0, 0)$  will generate the voltage vector  $V_0$

which can be expressed as:

$$\mathbf{V}_0 = \frac{2}{3}(0 + \mathbf{a}0 + \mathbf{a}^20) = 0 \tag{2.7}$$

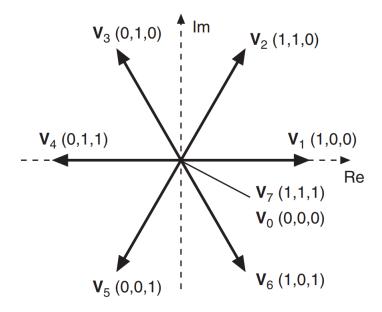

Figure 2.3: Voltage vectors in the complex plane [12]

Based on the combinations of the gating signals  $(S_a, S_b, S_c)$  we can obtain a total of 8 switching states and their respective voltage vectors, as shown in Table 2.1. However considering that  $\mathbf{V_0} = \mathbf{V_7}$  as shown in 2.3, only 7 different voltage vectors in the complex plane are obtained.

| $S_a$ | $S_b$ | $S_c$ | Voltage vector $\mathbf{V}$                                       |

|-------|-------|-------|-------------------------------------------------------------------|

| 0     | 0     | 0     | $\mathbf{V}_0 = 0$                                                |

| 1     | 0     | 0     | $\mathbf{V}_1 = \frac{2}{3} V_{dc}$                               |

| 1     | 1     | 0     | $\mathbf{V}_2 = \frac{1}{3}V_{dc} + j\frac{\sqrt{(3)}}{3}V_{dc}$  |

| 0     | 1     | 0     | $\mathbf{V}_3 = -\frac{1}{3}V_{dc} + j\frac{\sqrt{(3)}}{3}V_{dc}$ |

| 0     | 1     | 1     | $\mathbf{V}_4 = -\frac{2}{3}V_{dc}$                               |

| 0     | 0     | 1     | $\mathbf{V}_5 = -\frac{1}{3}V_{dc} - j\frac{\sqrt{(3)}}{3}V_{dc}$ |

| 1     | 0     | 1     | $\mathbf{V}_6 = \frac{1}{3}V_{dc} - j\frac{\sqrt{(3)}}{3}V_{dc}$  |

| 1     | 1     | 1     | $\mathbf{V}_7 = 0$                                                |

Table 2.1: Switching states  $(S_a, S_b, S_c)$  and voltage vectors

It should be noted that for the sake of simplicity a simple model has been used. A more complex model of the converter might for instance include dead time, IGBT saturation voltage, diode forward voltage drop. However the emphasis of this section is to explain the overall operation and overview of the inverter model with simplicity.

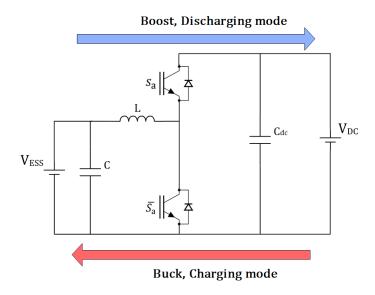

#### 2.1.4 DC-DC converter topologies

A DC-DC converter can be a necessary converter to have between the battery system and the inverter to ensure a stable voltage and current is provided, which is a key requirement to be able to control the bidirectional inverter. Traditionally, it is not common practise to depend on battery cells in series to increase the voltage as this comes with several disadvantages such as: large economic cost and a large space is often needed. There are however many different DC-DC topologies which can be selected based on the application. The power conversion system is responsible for the power flow through the grid and Battery Energy Storage System (BESS). The manner in which the BESS and the grid is interconnected depends on the selected design, which is between a single stage topology or a two stage topology. Where are single stage topology will often contain a grid tied bidirectional DC-AC converter directly connected to the BESS. While a two stage topology contains a DC-DC converter between the BESS and the grid tied converter. The proposed method of this thesis will utilize a two stage topology. Thus a DC-DC converter becomes a necessity. The single and two stage topology will be explained with further detail in a later section of this chapter. in this section the Buck and Boost DC-DC converter topologies will be presented. The converters topologies will be introduced individually to explain their function and structure, and a combination of these two converters will be presented in a later chapter. The converter models that are introduced in this section will not be explained in great detail, as these converters are well established in literature such as in the following sources which have been used: [9; 13; 14; 15].

#### **Buck** converter

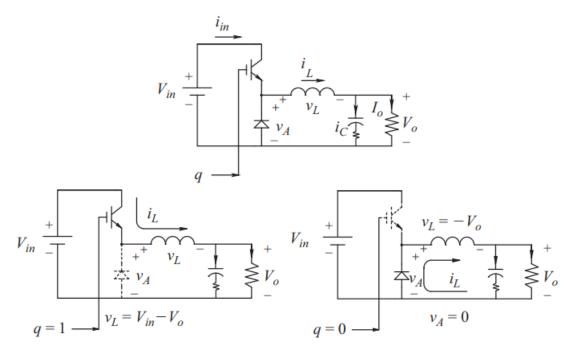

Buck converters often termed as step-down are simple and efficient converters, and as the name states it's primary use is to convert an input DC voltage to a lesser output voltage. One of the advantages of the buck converter is that it can provide a continuous output current. However a large capacitor is required in order to smoothen the discontinuous input current. A buck converter and its operation has been illustrated in figure 2.4. The converter contains a diode and a controllable switch where the gate signal has been

termed q, additionally the converter consists of passive components such as an inductor and a capacitor with its internal resistance. During the controllable switches off time the diode will allow the inductor current to freewheel across as depicted in figure 2.4 when the gate signal q is equal to zero. The converter has the ability to operate in both Continuous conduction mode (CCM) or in discontinuous conduction mode (DCM), which depends on the inductor waveform. A method of controlling the operation of the Buck converter and some simple calculations will be presented as follows:

Figure 2.4: Buck converter topology, and switching state.[14]

#### • Operation

When the controllable switch is on, the circuit will be able to provide the output load current and allow for the DC input to charge the inductor. Generally the converter can be controlled as shown in the waveform illustration where the inductor will be able to charge until the output voltage reaches the desired reference voltage. Once this is obtained the controller will turn off the switch allowing for the output voltage to remain close to the reference voltage. Furthermore due to the switch being turned off the circuit will no longer be charging the inductor, this will lead to the inductor changing its voltage polarity allowing for the current to flow in the same direction through the diode. The discharging of the inductor will continue until the output voltage reaches below the reference voltage, in which case the controller will turn on the switch to compensate for the output voltage drop and continue the operating cycle [16].

#### • Duty cycle calculation

The controllable switch is commonly controlled by using a PWM where its on and off state are determined by the switching frequency  $f_{sw} = 1/T$  and the duty cycle D can be derived as:

$$D = \frac{t_{on}}{T} = \frac{t_{on}}{t_{on} + t_{off}} = \frac{V_o}{V_{in}}$$

(2.8)

where  $t_{on}$  is the time interval that the controllable switch is in its on-state, likewise the  $t_{off}$  represents the time interval that the switch is not conducting (off-state). The period is termed T and the switching frequency  $f_{sw}$ .

#### • Buck converter Calculations

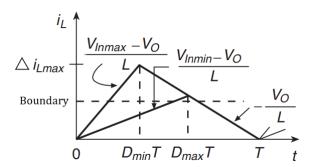

The inductor current waveform at the boundary between the CCM and the CDM are illustrated in Figure 2.5. Where the inductor current waveform can be described by the following equation:

$$i_L = \frac{V_{in} - V_o}{L}t, \quad \text{for} \quad 0 < t \le DT$$

(2.9)

Figure 2.5: Inductor current at CCM/DCM boundary [15].

Furthermore we can derive the peak-peak inductor current often termed as ripple current  $\Delta i_{L,p-p}$  as follows:

$$\Delta i_{L,p-p} = \frac{(V_{in} - V_0)DT}{L} = \frac{V_0(1-D)T}{L}$$

(2.10)

The size of the inductor component can be determined by calculating the minimum inductance required to maintain the CCM operation for the duty cycle range ( $D_{min}$  and  $D_{max}$ ) as shown in the following equation:

$$L_{min} = \frac{V_0(1 - D_{min})}{\Delta i_{L,max} f_{sw}}$$

(2.11)

from equation 2.11 it can be observed that by increasing switching frequency  $f_{sw}$  we can reduce the minimum inductance required. For the sake of simplicity all

resistances are neglected and the minimum required capacitor size can be calculated by the following equation:

$$C_{min} = \frac{\Delta i_L}{8f_{sw}\Delta v} = \frac{V_0(1 - D_{min})}{8Lf_{sw}^2 \Delta v}$$

(2.12)

where the voltage ripple is termed  $\Delta v$ , The calculation can be more complex if the resistances are included, which can be further detailed in the following source [17].

#### Boost converter

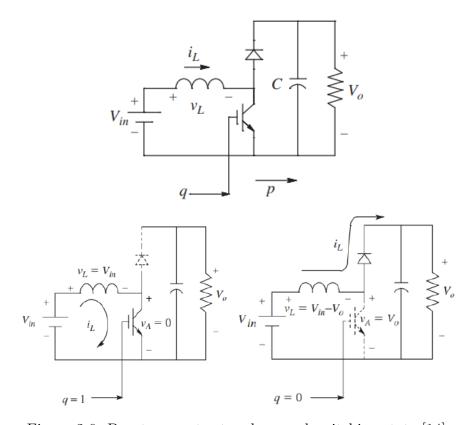

The boost converters often termed as step-up converters primary function is essentially the opposite of a buck converter, by providing an output voltage which is greater than the input voltage. Figure 2.6 provides an illustration of a Boost converter as well as its operation.

Figure 2.6: Boost converter topology and switching state [14].

The converter is supplied by a continuous input current and provides a discontinuous output current, with a better dynamic response. A disadvantage of the converter is the requirement of a high input side current, which means that it is not a suitable topology for all types of applications. Such as in the case of a PV system where the high input side current may not be possible to maintain at all times. Furthermore the converter requires

a larger inductance compared to that of a buck converter. The boost converter does however have the advantage of a cheaper implementation cost than a buck converter due to lower value input capacitor being required. Similar to the Buck converter topology the reverse current in the Boost converter is prevented by using a freewheeling diode, shown clearly in Figure 2.6.

#### Operation

By turning on the controllable switch (q = 1), the diode will be reverse biased and the inductor voltage  $V_L$  will be equal to the input voltage  $V_{in}$ , as is shown in figure 2.6. While also allowing the inductor current  $i_L$  to increase linearly at a rate of  $V_{in}/L$ , increasing the energy in the inductor. When the controllable switch is turned off (q = 0), the inductor current will be forced to flow through the forward biased diode. Hence leading to the stored energy of the inductor to be transferred to the filter capacitor C and the output load. At this time the inductor voltage will be equal to  $V_L = V_{in} - V_0$  with the inductor current  $i_L$  decreasing at a rate of  $(V_{in} - V_0)/L$ . The operation of the Boost converter, while the switch is on and off has been illustrated in the previously mentioned figure 2.6.

#### • Input/output voltage ratio

It is common for the controllable switch to be controlled using a PWM where its on and off state are determined by the switching frequency, similar to what has been presented previously with the buck converter. The relationship between the input and output voltage can be derived by using either the waveform of  $V_L$  or  $V_A$  as is sown in figure 2.7. By using the inductor voltage waveform in steady state we can obtain the following equation:

$$V_{in}(DT_s) = (V_0 - V_{in})(1 - D)T_s$$

(2.13)

Which allows for the input/output voltage ratio to be expressed as:

$$\frac{V_0}{V_{in}} = \frac{1}{1 - D} \qquad (V_0 > V_{in}) \tag{2.14}$$

2.2 Controllers

Figure 2.7: Boost converter waveforms [14].

#### • Inductor size calculation

Traditionally the inductor size is determined through the inductor current ripple. By calculating the average inductor current  $I_L$  using equation 2.15, where  $I_o$  represents the output current. It is then suggested that the peak-peak ripple current termed  $\Delta i_{L,p-p}$  should be around 20-40% of  $I_L$  [18].

$$I_L = \frac{V_0 I_0}{V_{in}} \tag{2.15}$$

The inductor current waveform is built up by the average value, which is dependent on the output load and the ripple component:

$$i_L(t) = I_L + i_{L,ripple}(t) (2.16)$$

where the inductor ripple current termed  $i_{L,ripple}$  is also dependent on the inductor voltage  $v_L$ . This is shown clearly in figure 2.7 where  $i_{L,ripple}$  increases when  $v_L$  is positive and decreases when  $v_L$  is negative, finally resulting in an average of zero. we can then determine the inductor size by calculating the peak-peak ripple as shown in the following equation:

$$\Delta i_{L,p-p} = \frac{1}{L} \underbrace{V_{in}(DT)}_{AreaA} = \frac{1}{L} \underbrace{(V_0 - V_{in})(1 - D)T_s}_{AreaB}$$

(2.17)

## 2.2 Controllers

There are various types of controllers which can be used for the purpose of controlling a converter or for the sake of grid angle extraction. However some of the most common types for the sake of converter control include the hysteresis controller and the Proportional Integral (PI) controller, which will be presented in this section along with a method of tuning and optimizing a PI controller through Modulus Optimum (MO) criteria.

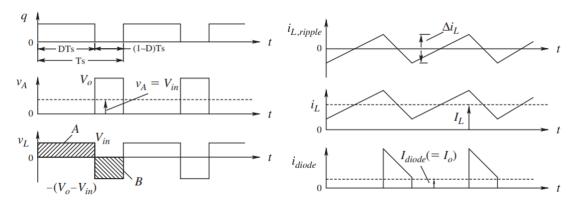

### 2.2.1 Hysteresis controller

The hysteresis controller theory has been sourced from [9]. Hysteresis control is often termed as tolerance band control and through out this thesis will be used interchangeably. This form of controller is commonly used as a current regulator. The tolerance band current control method is illustrated in figure 2.8 using one of the legs of an arbitrary inverter for a sinusoidal reference current  $i_A^*$ , where the real phase current  $i_A$  is compared to the tolerance band around the reference current to the phase. As shown in the figure  $V_d$  represents the DC voltage and the switches on the inverter leg are termed  $T_{A+}$  for the upper leg and  $T_{A-}$  for the lower leg.

Essentially the operational principle of the controller consists of an upper and lower tolerance band which dictate when the switches on the converter can be turned on and off. For instance when the real current value  $i_A$  increases above the upper level of the tolerance band,  $T_{A-}$  is turned on, conversely  $T_{A+}$  is turned off. Furthermore the same logic is implied for when the real current goes below the lower level of the tolerance band, with the opposite switching. The switching frequency is thereby determined by the speed of which the current changes from the the upper limit to the lower limit of the tolerance band and vice versa. However despite the simplicity of the hysteresis control method, a notable drawback of this controller is that the switching frequency changes as a function of the current waveform. For this specific reason, constant switching frequency controllers are often used as an alternative.

Figure 2.8: Hysteresis current control [9].

2.2 Controllers

### 2.2.2 Proportional Integral Controller (PI)

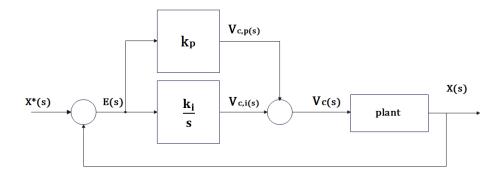

Figure 2.9: PI control loop in the frequency domain.

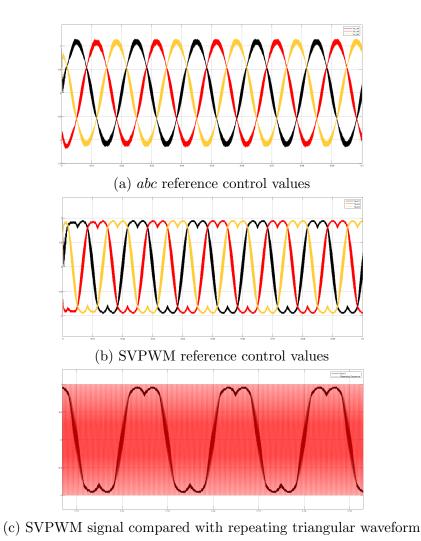

The Proportional Integral (PI) controller is a well established controller which is applied in a wide range of applications [19]. This type of controller is built up by two separate controller parts the proportional and the integral, as is illustrated in Figure 2.9. The Proportional (P) controller is the most basic type, which consists of a simple proportional gain,  $k_p$ . The proportional controller produces an output which can be expressed as:

$$V_{c,p}(s) = k_p E(s) \tag{2.18}$$

Where the difference between the reference input and the measured output is considered the input error of the controller  $E(s)=X^*(s)$  - X(s). The integral part of the controller takes the error input signal and removes the steady state control offsets by ramping the output up or down depending on the amplitude and duration of the input error signal. However the integral constant which controls the ramp rate must be tuned properly or there becomes a risk of oscillations [20][21]. As illustrated in 2.9 the integral controllers output is proportional to the integral of the error E(s), and can be expressed in the Laplace domain as:

$$V_{c,i}(s) = \frac{k_i}{s} E(s) \tag{2.19}$$

where the integral controller gain is termed  $k_i$ . Such controllers have a slow response time due the actions being proportional to the time integral of the error. However the steady-state error will go towards zero for a step change in input because the integrator will continue until there is no error (ie, error equal to zero). The Transfer function (TF) of a PI controller can be expressed as:

$$PI(s) = \frac{V_c(s)}{E(s)} = k_p + \frac{k_i}{s} = \frac{k_p s + k_i}{s} = \frac{k_p \left(s + \frac{k_i}{k_p}\right)}{s}$$

(2.20)

Or alternatively the TF with the integral time constant  $T_i = \frac{k_p}{k_i}$ , can be expressed as:

$$PI(s) = k_p \left[ \frac{1 + T_i s}{T_i s} \right] \tag{2.21}$$

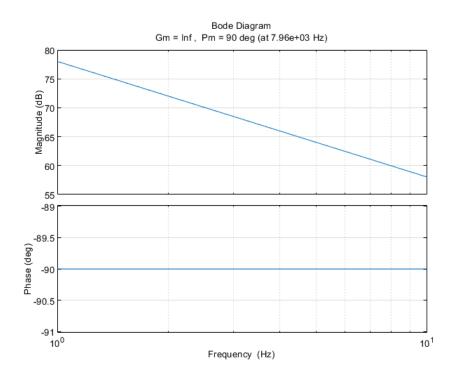

### 2.2.3 Controller tuning and optimizations

There are various methods which can be used for optimizing PI controllers, in this section two popular tuning methods known as the MO and Symmetrical Optimum (SO) are introduced. These methods are based on a similar idea of finding a controller which makes the frequency response from set-point to the plant output as close to unity as possible [22]. Both optimization techniques have been proven to be successful in the tuning of PI controllers and have been widely implemented in grid tied converters. The parameter of PI controllers as has been previously explained consist of a proportional gain constant  $k_p$  and the integral time constant Ti.

#### Modulus optimum

MO, also known as absolute value optimum criterion as has been explained is a methodology of tuning a PI controller based on keeping the magnitude value of the systems closed loop TF  $G_{CL}(s)$  equal to unity, while maintaining as wide of a frequency range as possible [22]. For instance if one has an arbitrary controller TF known as G(s), we would then like to tune the controller in way which allows G(0) = 1 and for  $\frac{d^n |G(j\omega)|}{d\omega^n} = 0$ at  $\omega = 0$  for as long as possible [23].

For low order controlled plants without time delay, the MO is generally used in the conventional analog controller tuning. If the controlled system has one dominant time constant in addition to other minor time constants, the PI controller can be considered suitable for optimization by using the MO criteria. When the conditions are met, the standard form of the control systems TF for the MO is obtained by cancelling the largest time constant. This is done while keeping the closed loop gain larger than unity for as high frequencies as possible [24]. If we assume the TF of a plant system expressed as:

$$L(s) = \frac{1}{(1 + T_a s)(1 + \tau s)Rp}$$

(2.22)

where  $T_a$  represents a large time constant, while  $\tau$  represents a small time constant or the sum of multiple smaller time constants, in addition to fulfilling the following condition  $T_a >> \tau$ . With reference to the PI-controllers TF shown in 2.21, we can derive the

2.2 Controllers 21

system open loop and closed loop TF  $(G_{OL}(s), G_{CL}(s))$ , as:

$$G_{OL}(s) = k_p \left[ \frac{1 + T_i s}{T_i s} \right] \frac{1}{(1 + T_a s)(1 + \tau s)R_p}$$

(2.23)

$$G_{CL}(s) = \frac{k_p(1 + T_i s)}{k_p(1 + T_i s) + \frac{T_i}{R_p} s(1 + T_a s)(1 + \tau s)}$$

(2.24)

Zero pole cancellation can be applied for the dominating pole of the system, giving the PI gain parameters  $k_p$  and  $T_i$  by MO tuning criteria as follows:

$$T_i = \tau \tag{2.25}$$

$$k_p = \frac{R_p \tau}{2T_a} \tag{2.26}$$

with the tuning criteria given from the above equations (2.25, 2.26), the open loop and closed loop TFs of the systems control loop can be expressed as:

$$G_{c,OL}(s) = \frac{1}{2T_a} \cdot \frac{1}{s(1+T_a s)}$$

(2.27)

$$G_{c,CL}(s) = \frac{1}{2T_a^2 s^2 + 2T_a s + 1} = \frac{\frac{1}{2T_a^2}}{s^2 + \frac{1}{T_a} s + \frac{1}{2T_a^2}}$$

(2.28)

The resulting closed loop TF from equation 2.28, resembles the form of a generic second order TF as expressed in 2.29. Given the similarity of these TFs we can determine the natural frequency and the damping factor of the closed loop system. Which has been expressed in equation 2.30 and 2.31.

$$G(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2} \tag{2.29}$$

$$\omega_n = \frac{1}{\sqrt{2}T_a} \tag{2.30}$$

$$\zeta = \frac{1}{\sqrt{2}} \tag{2.31}$$

Due to the simplification of the system by using pole cancellation, and optimizing the absolute value to unity. The systems resulting response will always correspond to the given values of  $\zeta$  and  $\omega_n$  as shown in the above equations. However the crossover frequency can be tuned to obtain the desired value by regulating the proportional gain constant  $k_p$ . It is common to select the crossover frequency to be one or two orders smaller than the switching frequency of the system, thereby one can avoid the interference from the switching noise.

The MO criteria proves to be a suitable tuning technique, when the controlled system has one dominant time constant along with other minor time constants. However this is not the case when one of the poles is located near the origin or at the origin itself, due to the pole shift not causing any significant change. In which case an alternative controller tuning technique could be used such as the SO criterion which will not be used in this thesis [24].

#### 2.3 Power Waveform Distortions

Power systems quality monitoring is considered to be common practice for utilities, as there has been an increased amount of requirements on the control and performance of such systems. The PQ refers to the amount of variation in voltage, current, harmonics, and frequency on the power system. The distortion in power distribution systems 50 Hz sinusoidal waveform, is referred to as the term "Waveform distortions". These waveform distortions can occur through various means, which can be separated into select groups such as: Harmonics, Noise and Impulsive transients [25].

Ideally we would like the converter systems current to be free from distortion and be completely sinusoidal, however this is not possible in a practical system due to the distortion in the converters output voltages occurring from the dead time and non-ideal characteristics of the power switches or due to the distorted grid voltage [26].

Harmonic current distortions in Power electronic systems in addition to the voltage waveform distortions it can lead to malfunctioning of components due to over-voltages due to resonance conditions. And has the capability of undesirable effects such as increased heating to the cables, loads and components of the circuits as well as additional problems to the power electronic system [9].

A distorted waveform will often contain a large amount of different harmonic distortions, and therefore when describing the harmonic content within the waveform it is common to use the term Total Harmonic Distortion (THD). A distorted waveform can be split into its fundamental component and its harmonic component, where the THD describes the percentage ratio of the Root Mean Squared (RMS) amplitude of the fundamental frequency compared to a set of harmonic frequencies. We are able to calculate these components by means of Fourier analysis [8].

A repeating waveform f(t) which satisfies the Dirichlet conditions is able to be expressed

2.4 Filter Methods 23

with the use of Fourier expansion as shown.

$$f(t) = a_o + \sum_{h=1}^{\infty} (a_h \cdot \cos(h\omega t) + b_h \cdot \sin(h\omega t))$$

(2.32)

In which case the coefficients  $a_o$ ,  $a_h$  and  $b_h$  can be defined by the following expressions:

$$a_o = \frac{1}{T} \int_{-T/2}^{T/2} f(t)dt \tag{2.33}$$

$$a_h = \frac{2}{T} \int_{-T/2}^{T/2} f(t) \cdot \cos(h\omega t) dt$$

(2.34)

$$b_h = \frac{2}{T} \int_{-T/2}^{T/2} f(t) \cdot \sin(h\omega t) dt$$

(2.35)

each frequency component is represented in term of its RMS value, can be calculated as:

$$F_{RMS} = \sqrt{a_o^2 + \sum_{h=1}^{\infty} \frac{a_h^2 + b_h^2}{2}}$$

(2.36)

However it is important to note that the DC component  $a_o$  of f(t) is often zero, simplifying the equation to:

$$F_{RMS} = \sqrt{\sum_{h=1}^{\infty} \frac{a_h^2 + b_h^2}{2}}$$

(2.37)

using the above equation we can derive an expression for the THD, where  $F_{1,RMS}$  represents the fundamental signal as:

$$THD = \sqrt{\frac{F_{RMS}^2 - F_{1,RMS}^2}{F_{1,RMS}^2}}$$

(2.38)

Furthermore the THD can be derived in terms of the current, where  $I_1$  is the line frequency component of the drawn current from a load and  $I_h$  is the h harmonic current injected. this can be expressed as [9]:

$$THD = \frac{\sqrt{\sum_{h=2}^{\infty} I_h^2}}{I_1} \tag{2.39}$$

### 2.4 Filter Methods

As previously mentioned the effects of harmonic distortion can be quite substantial, which is why it is common to develop a filter connected between the grid and the con-

verter too attenuate the harmonics. This method of acquiring a stable region of operation variates depending on the application, bandwidth and cost with several different methods of filtering to select from. One can generally divide the type of attenuation into two methods passive- and active damping. Both methods are capable of compensating the harmonic current precision and damp the switching ripples sufficiently. the passive and active damping methods which will be presented have been based on [27].

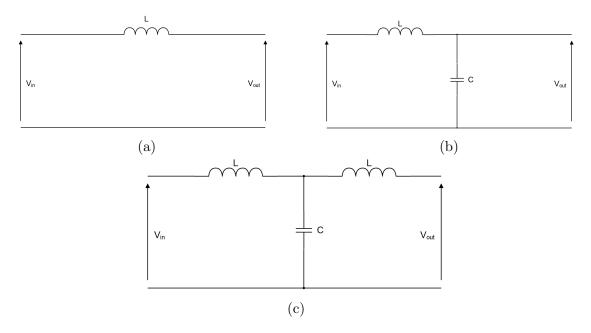

The state of the art methods of filtering today mainly contain three filter topology variations: L, LC, and LCL filter variations as is illustrated in 2.10. The size of the components are determined by the topology selection. Considering the LCL filter topology the filter size is determined by the inverter output current, switching frequency and the system bandwidth. The LCL filter design is considered to be the most preferred method for power conditioners when taking the advantages into consideration. Such as the lowered requirement of inductance and capacitance which reduces the bulkiness and cost. However with this topology the resonant peaks that are developed during the operation can be a challenge to attenuate, and may need passive or active damping depending on the operational requirements and chosen component values.

Figure 2.10: Three different types of passive filters, a) L filter, b) LC filter, c) LCL filter

The passive damping method consists of only passive elements such as resistors inductors and capacitors, which simplifies the complexity of design and can be more cost efficient when compared to the active damping counterpart. The advantages of having a simple control algorithm, cause the passive method of filtering to have a better bandwidth and dynamic performance. This advantage is one of the reasons that it can be the preferred choice given the right use of application. However the losses of the damping

resistance can be considerable to the point that is unacceptable when applied in a high-power system. This disadvantage can be mitigated given the right improvements of the filter topology, which can possibly reduce the power losses of the damping resistors to the point that it can be comparable with active methods. While simultaneously keep the advantages that is acquired by the passive methods.

The active damping method can be more expensive due to the requirement of more sensors and will cause an increase of the algorithm complexity in turn. While the passive methods have a large bandwidth, this is not the case for the active methods which have a smaller bandwidth and poor performance of dynamic response and noise immunity. Unlike the passive methods where it is common to use a physical resistor to damp the system, the active damping generally uses a control algorithm. These control methods come in many variations for instance with a LCL filter topology some of the commonly used control methods include complex modulation strategies such as Space Vector Pulse Width Modulation (SVPWM).

# 2.5 Battery Energy Storage Systems - BESS

In modern day BESS can have monitoring and control systems as well as power conversion systems. Batteries have the capability of storing energy chemically, with the advantages of having a dynamic response time, high energy efficiency and can generally be easily transported with out relying on any specific geographical restrictions. At least compared to other storage devices such as water storage, which can be limited by geographical restrictions, for instance water reservoirs.

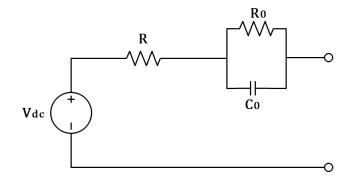

BESS usually contain non-linear characteristics, thus leading to some challenges in its proper representation when one intends to perform tests by simulating. One model design method used to represent a battery storage system, consists of a circuit with an internal resistance in series with an ideal voltage source. Which is considered to be the simplest and the most commonly used model of a battery, this has been illustrated in figure 2.11.

Figure 2.11: Simple Thevenin battery model [30].

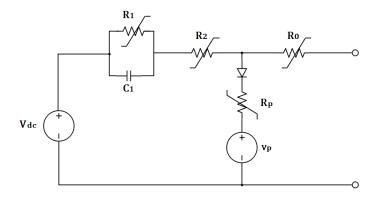

However often there is a need for a more realistic model which takes the non-linear parameters into consideration. With such models the characteristics of the battery's internal resistance, self-discharge resistance, overcharge resistance and adding a separation between the charging and discharging processes. One of such models known as a third order battery model has been illustrated in figure 2.12. In the illustrated third order model the main branch which contains  $V_{dc}$ ,  $R_1$ ,  $C_1$  and  $R_2$  components is used to approximate the battery charge/discharge dynamics. While the parasitic branch which contains  $R_p$  and  $V_p$  represents the self-discharge, furthermore a resistor  $R_0$  is placed in order to approximate the overcharge resistance. As is clearly displayed in the illustrated figure of the third order battery model the resistive elements are non-linear and current dependent. Both the simplistic model and the more realistic model are explained in further detail from their source [30].

Figure 2.12: Third order battery model [30].

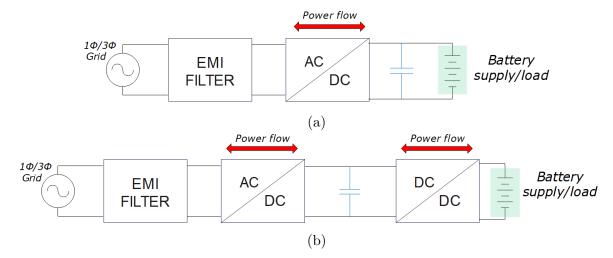

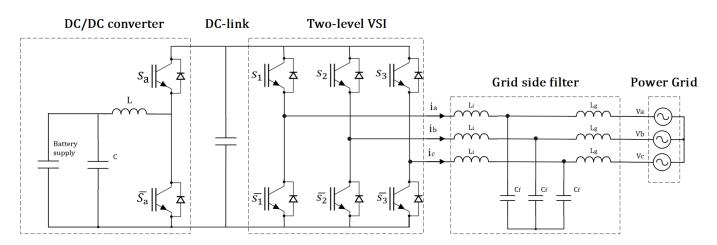

In order for the power to flow across the BESS and the grid, a power conversion system must be utilized. There are generally two variations of the topologies used for such systems, which are commonly known as single stage and two stage topologies as illustrated in figure 2.13a and 2.13b respectively. The single stage design topology connected to a BESS consists of a bidirectional DC-AC converter which interconnects the battery and the grid directly. While the two stage topology has an additional DC-DC converter

between the DC-AC converter and the battery supply/load. Using such power conversion systems a dc-link capacitor is often placed in order to stabilize the dc-link voltage. There are challenges which come depending on the selected topology. The single stage is considered a more simple design, however the two stage topology is considered to be superior in efficiency following the results of numerous studies such as [28]. The usual design topology of these systems have been illustrated and can be compared as mentioned in figure 2.13. As stated both of these topology variations have full bidirectional power flow capabilities, although each of the topologies come with their own advantages and disadvantages [29]. For this thesis the two stage topology will be used in the later chapters due to the overall advantages such as the capability of both boosting and bucking the voltage provided by the BESS.

Figure 2.13: a) Single stage BESS topology. b) two stage BESS topology. [29].

# Chapter 3

# Control structure and strategies of grid tied converter

When converting DC to AC power and vice versa, it is essential that the three phase AC voltage and current is controlled. Where the main objective is to control the voltage and current components magnitude, frequency, phase angle and the direction of the power flow. Each of the respective voltage and current components, are the determining factors of the total amount of power delivered.

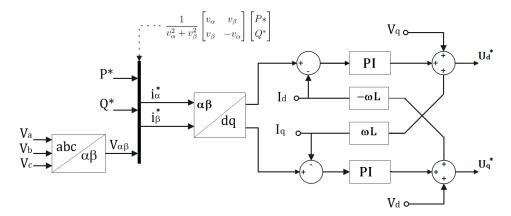

This chapter aims to present the control structures, components and strategies which are used in the GTI system. The chapter introduces coordinate transformations, modulation strategies, Phase Locked Loop control and the Voltage Oriented Control (VOC) strategy with an overview of the entire control structure. Furthermore an alternative control method by using the Direct Power Control (DPC) method will also be described. The following sections of this chapter will be using an inverter model with a LCL-filter when describing the method of control unless stated otherwise. This is the intended topology for simulation and prototyping of the system.

## 3.1 Clark and Park transform

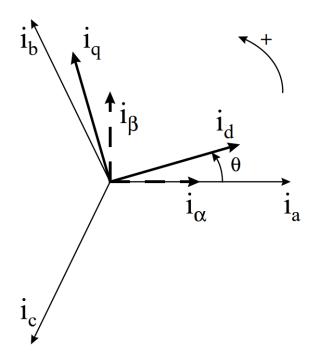

In VOC and DPC, we use coordinate transformations to turn the measured AC values into quantities that can be more manageable and simpler to regulate by the converter control loops. Once these values have been transformed and regulated by the control loops we can then inverse transform these quantities into their corresponding AC-values. For this implementation we utilize two types of transformations to acquire our desired quantities the Clark and Park transform. An illustration has been provided to showcase

a graphical representation of the three phase reference frames, in figure 3.1. These transformations have their variations based on what invariance one would like, more specifically there is the magnitude invariant and the power invariant [8][31].

Figure 3.1: the stationary reference frame  $(\alpha\beta)$  and synchronous reference frame (dq) with its relation to the three phase (abc) reference frame [32].

#### 3.1.1 Clark transformation

The Clarke transformation is used to transform the components in a three phase system (in abc frame) into two components in an orthogonal stationary frame  $(\alpha\beta)$  which is also referred to as the  $\alpha\beta$  coordinate system [8][31]. By assuming symmetrical balanced three phase AC, the ideal voltage and current values termed as  $\mathbf{V}_{abc}$  and  $\mathbf{I}_{abc}$  (120°phase shift) are derived as:

$$\mathbf{V}_{abc} = \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix} = \begin{bmatrix} V \cdot \sin(wt) \\ V \cdot \sin(wt - \frac{2 \cdot \pi}{3}) \\ V \cdot \sin(wt + \frac{2 \cdot \pi}{3}) \end{bmatrix}$$

(3.1)

$$\mathbf{I}_{abc} = \begin{bmatrix} I_a \\ I_b \\ I_c \end{bmatrix} = \begin{bmatrix} I \cdot sin(wt) \\ I \cdot sin(wt - \frac{2 \cdot \pi}{3}) \\ I \cdot sin(wt + \frac{2 \cdot \pi}{3}) \end{bmatrix}$$

(3.2)

For the transformation equations the current values will be selected to showcase the transformation. We use the Clark transformation to represent the corresponding orthog-

onal components  $I_{\alpha}$  and  $I_{\beta}$  as shown:

$$\mathbf{I}_{\alpha\beta0} = \begin{bmatrix} I_{\alpha} \\ I_{\beta} \\ I_{0} \end{bmatrix} = \mathbf{T}_{c} \mathbf{I}_{abc} = \frac{2}{3} \underbrace{\begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix}}_{T_{c}} \begin{bmatrix} I_{a} \\ I_{b} \\ I_{c} \end{bmatrix}$$

(3.3)

As shown we acquire three components by using this transformation matrix, however the zero components value will always remain 0 with the assumption of a symmetrical balanced sinusoidal three phase signal. Therefore we choose to neglect the zero component and focus more on the  $\alpha$  and  $\beta$  components. This variant of the Clark transformation is known as the magnitude invariant, in which the magnitude of the three phase system vector is the same as the two phase system vector:

$$|I_a(t)| = |I_\alpha(t)| \tag{3.4}$$

This method can be a good choice for motor drive designers due to its intuitive nature of having the measured voltage magnitude be the same in both reference frames, which can be advantageous for control. Likewise the power invariant may be more suitable for DPC applications, as the power can be estimated using the  $\alpha\beta$  coordinate. The magnitude invariant inverse Clark transformation can be expressed as:

$$\mathbf{I}_{abc} = \begin{bmatrix} I_a \\ I_b \\ I_c \end{bmatrix} = \mathbf{T}_{c,inv} \mathbf{I}_{\alpha\beta0} = \underbrace{\begin{bmatrix} 1 & 0 & 1 \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} & 1 \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} & 1 \end{bmatrix}}_{T_{c,inv}} \begin{bmatrix} I_{\alpha} \\ I_{\beta} \\ I_{0} \end{bmatrix}$$

(3.5)

However in order to perform calculations on the active and reactive power whilst working in the  $\alpha\beta$  domain one would need to utilize another form of the Clark transformation to accommodate for this. The currently shown Clarke transformation matrix does not contain the necessary criteria to allow for these calculations due to the matrix being non-unitary. Which implies that this variation of the Clark transformation does not fulfil the following criteria:  $\mathbf{T}^*\mathbf{T} = \mathbf{T}\mathbf{T}^*$ . The power invariant Clark transformation can be expressed as:

$$\mathbf{I}_{\alpha\beta0} = \begin{bmatrix} I_{\alpha} \\ I_{\beta} \\ I_{0} \end{bmatrix} = \mathbf{T}_{c} \mathbf{I}_{abc} = \sqrt{\frac{2}{3}} \underbrace{\begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix}}_{T} \begin{bmatrix} I_{a} \\ I_{b} \\ I_{c} \end{bmatrix}$$

(3.6)

As mentioned by using the power invariant equation we can calculate and determine an estimate of the instantaneous active power (P) and reactive power (Q) by using the voltage and current quantities in the  $\alpha\beta$  coordinate as shown:

$$\begin{bmatrix} P \\ Q \end{bmatrix} = \begin{bmatrix} V_{\alpha} & V_{\beta} \\ -V_{\beta} & V_{\alpha} \end{bmatrix} \begin{bmatrix} I_{\alpha} \\ I_{\beta} \end{bmatrix}$$

(3.7)

The power invariant transformation shown in equation 3.6, can then be inverted by applying the inverse Clark transformation as shown:[33]

$$\mathbf{I}_{abc} = \begin{bmatrix} I_a \\ I_b \\ I_c \end{bmatrix} = \mathbf{T}_{c,inv} \mathbf{I}_{\alpha\beta0} = \sqrt{\frac{2}{3}} \underbrace{\begin{bmatrix} 1 & 0 & \frac{1}{\sqrt{2}} \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} & \frac{1}{\sqrt{2}} \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} & \frac{1}{2} \end{bmatrix}}_{T_{c,inv}} \begin{bmatrix} I_{\alpha} \\ I_{\beta} \\ I_{0} \end{bmatrix}$$

(3.8)

#### 3.1.2 Park transformation

The Park transformation is used to transform the two components which are represented in an orthogonal stationary frame  $(\alpha\beta)$  into a orthogonal rotating reference frame (dq) with also two components. Which in essence simplifies the two ac components which rotate with a fixed frequency that are represented by the orthogonal  $\alpha\beta$  components, to appear as two DC quantities instead [8][31]. By using the  $\alpha\beta$  quantities of the power invariant Clark transformation we can then transform them over to the dq coordinate by using the park transformation. Where the frame rotation speed is represented by  $\omega$  and the position of the rotating reference frame is given by  $\omega$ t. Assuming that the dq components are rotating at an arbitrarily given frequency in order to derive the dq components in the Park transformation which is expressed as:

$$\mathbf{I}_{dq0} = \begin{bmatrix} I_d \\ I_q \\ I_0 \end{bmatrix} = \mathbf{T}_P \mathbf{I}_{\alpha\beta0} = \underbrace{\begin{bmatrix} \cos(\omega t) & \sin(\omega t) & 0 \\ -\sin(\omega t) & \cos(\omega t) & 0 \\ 0 & 0 & 1 \end{bmatrix}}_{T_P} \begin{bmatrix} I_\alpha \\ I_\beta \\ I_0 \end{bmatrix}$$

(3.9)

We can see that the Parks transformation does also contain the homopolar or zerosequence component which should remain unchanged given the assumption that one is working with a balanced three phase signal. The inverse park transformation is given by:

$$\mathbf{I}_{\alpha\beta0} = \begin{bmatrix} I_{\alpha} \\ I_{\beta} \\ I_{0} \end{bmatrix} = \mathbf{T}_{P,inv} \mathbf{I}_{dq0} = \underbrace{\begin{bmatrix} cos(\omega t) & -sin(\omega t) & 0 \\ sin(\omega t) & cos(\omega t) & 0 \\ 0 & 0 & 1 \end{bmatrix}}_{T_{P,inv}} \begin{bmatrix} I_{d} \\ I_{q} \\ I_{0} \end{bmatrix}$$

(3.10)

By combining the Clark and Park transformation we obtain a method to transform the three phase abc components from the time domain over to the dq coordinate directly. We do this by simply combining the transformation matrices  $\mathbf{T}_c$  and  $\mathbf{T}_p$  with one another. the resulting matrix  $\mathbf{T}_{cp}$  can then be shown as:

$$\mathbf{T}_{cp} = \mathbf{T}_{c} \mathbf{T}_{p} = \sqrt{\frac{2}{3}} \begin{bmatrix} cos(\omega t) & cos(\omega t - \frac{2\pi}{3}) & cos(\omega t + \frac{2\pi}{3}) \\ -sin(\omega t) & -sin(\omega t - \frac{2\pi}{3}) & -sin(\omega t + \frac{2\pi}{3}) \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix}$$

(3.11)

With the inverse transformation begin derived as:

$$\mathbf{T}_{cp,inv} = \sqrt{\frac{2}{3}} \begin{bmatrix} cos(\omega t) & -sin(\omega t) & \sqrt{\frac{1}{2}} \\ cos(\omega t - \frac{2\pi}{3}) & -sin(\omega t - \frac{2\pi}{3}) & \sqrt{\frac{1}{2}} \\ cos(\omega t + \frac{2\pi}{3}) & -sin(\omega t + \frac{2\pi}{3}) & \sqrt{\frac{1}{2}} \end{bmatrix}$$

$$(3.12)$$

Variations of the inverse transformation in equation 3.12 are possible depending on the desired alignment (ie. d- or q-axis alignment), and of the desired invariance. By multiplying the transformation matrix with  $\sqrt{\frac{2}{3}}$  and altering the zero components of the matrix from 1 to  $\sqrt{\frac{1}{2}}$  as is shown in 3.12, we acquire the power invariant transformation.

## 3.2 Pulse Width Modulation - PWM

In previous sections, PWM has been described as a modulation technique used to generate the gate signals for the purpose of controlling the switching of converters. While also ensuring both rectifying and inverting operation through the modulation of the drawn currents from the voltage source. Which is obtained by having the drawn current in phase with the drawn voltage. When applying the intended control methods for this thesis, the modulation process occurs within the Current Control Loop (CCL). This is achieved by using the coordinate transforms (Clarke and Park) to generate the needed control voltage reference signals for the PWM module.

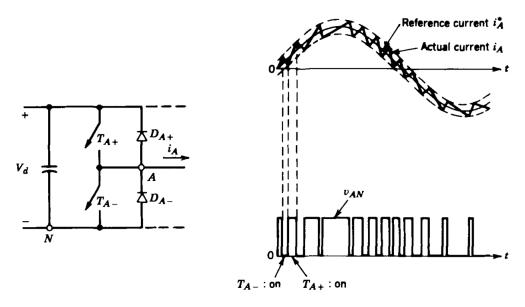

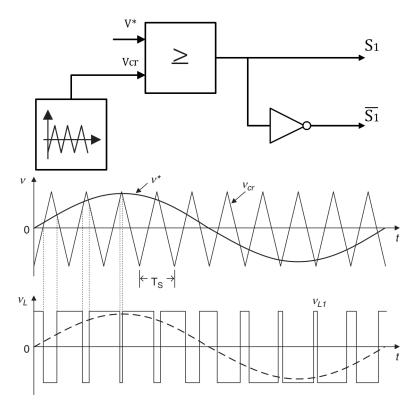

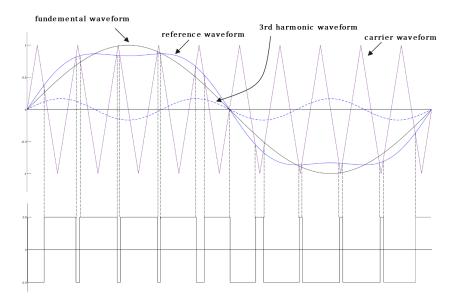

#### 3.2.1 Sinusodial Pulse Width Modulation - SPWM

To put it simply the Sinusoidal Pulse Width Modulation (SPWM) is achieved by comparing a carrier waveform (triangular waveform)  $V_{cr}$  with a sinusoidal reference voltage  $V^*$ . Thereby generating a pulsed waveform at the output of the converter. The fundamental component of this output voltage is proportional to the reference voltage. For the sake of simplicity the PWM technique applied in a single phase inverter has been illustrated in Figure 3.2.

Figure 3.2: Sinusoidal PWM for a single phase [12].

By observing the waveforms in the figure one can see that the switches on and off time are determined by the following conditions:

$$\begin{cases} V* > V_{cr} & S_1 \text{ is on, } \overline{S_1} \text{ is off} \\ V* < V_{cr} & S_1 \text{ is off, } \overline{S_1} \text{ is on} \end{cases}$$

(3.13)

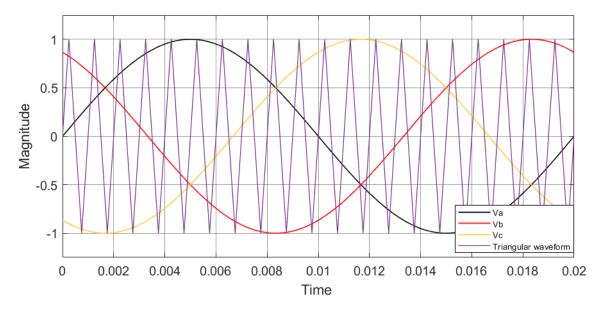

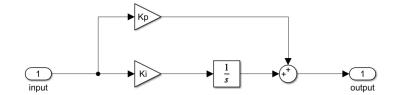

Similarly three phase output voltages are obtained by comparing the carrier waveform  $V_{cr}$  with three sinusoidal reference control voltages  $(V_a^*, V_b^*, V_c^*)$  with a 120° displacement as shown in figure 3.3. Where the triangular waveform represents the carrier waveform  $V_{cr}$ .

Figure 3.3: Sinusoidal PWM for three phase signal.

## 3.2.2 Space vector pulse width modulation - SVPWM

A variation of the PWM is termed Space Vector Modulation (SVM), which fully utilizes the available dc-bus voltage. Additionally resulting in an increased AC output of approximately 15% higher than that of SPWM control method which is limited to  $V_{LL,max} = \frac{\sqrt{3}}{2}V_{dc}$ . This is due to the SPWM method not taking advantage of the three phase properties and rather synthesizes the output voltages on a per-pole basis, where the power poles are  $\bar{v}_{aN}$ ,  $\bar{v}_{bN}$  and  $\bar{v}_{cN}$ . However by taking line-to-line voltages into consideration it is possible to get  $V_{LL,max} \approx V_{dc}$  while using SVPWM [14].

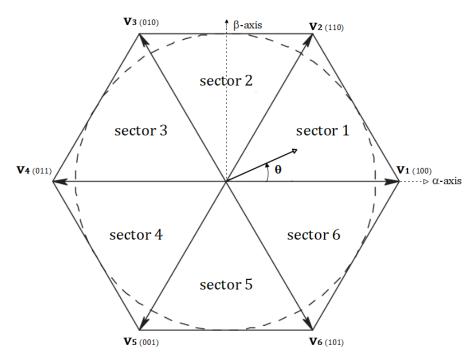

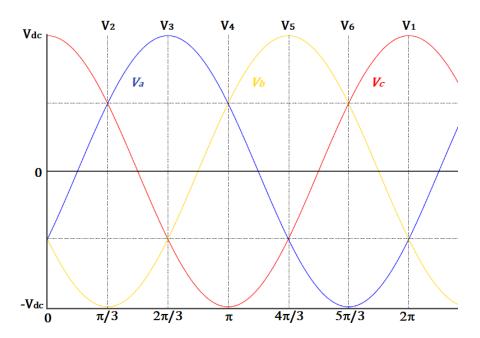

The previously described three phase inverter from chapter 2, has been shown to only operate within eight distinct switching state topologies. Where six out of these eight switching states produce a non-zero output voltage which can be referred to as *active* vectors ( $\mathbf{v}_1 \to \mathbf{v}_6$ ) while the remaining two switching states produce zero output voltage and are termed zero vectors ( $\mathbf{v}_0, \mathbf{v}_7$ ). The six active vectors in the stationary reference frame form a hexagon and six separate sectors as shown in figure 3.4 [34]. The zero vectors ( $\mathbf{v}_0, \mathbf{v}_7$ ) have not been included on the figure however they would be located in the origin. Additionally the angular position of the three phase voltages have been illustrated in figure 3.5.

Figure 3.4: Representation of a three phase inverters active vector switching states, in the stationary reference frame [34].

Figure 3.5: Angular position of the three phase voltages [8].

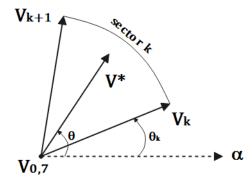

By considering the division of the six sectors, where the voltage vectors are generated by the inverter in the  $\alpha\beta$  plane as shown in figure 3.4. A given reference voltage vector termed  $\mathbf{v}^*$ , positioned within a generic sector k, is able to be synthesized by using the adjacent vectors known as  $\mathbf{V}_k$ ,  $\mathbf{V}_{k+1}$  and  $\mathbf{V}_0$  as shown in figure 3.6.

Figure 3.6: Reference vector in a generic voltage sector k [12].

Each vector is applied during their respective time  $t_k$ ,  $t_{k+1}$  and  $t_0$ . This can be expressed with the following equations which have been adapted from [12].

$$\mathbf{v}^* = \frac{\mathbf{V}_k t_k + \mathbf{V}_{k+1} t_{k+1} + \mathbf{V}_0 t_0}{T} \tag{3.14}$$

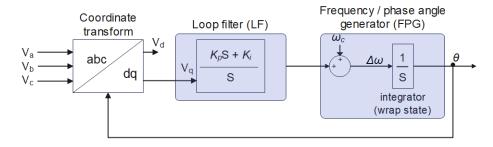

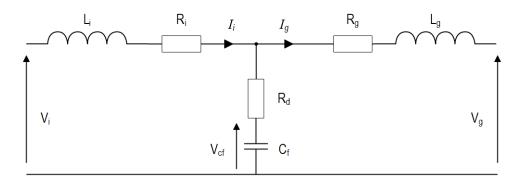

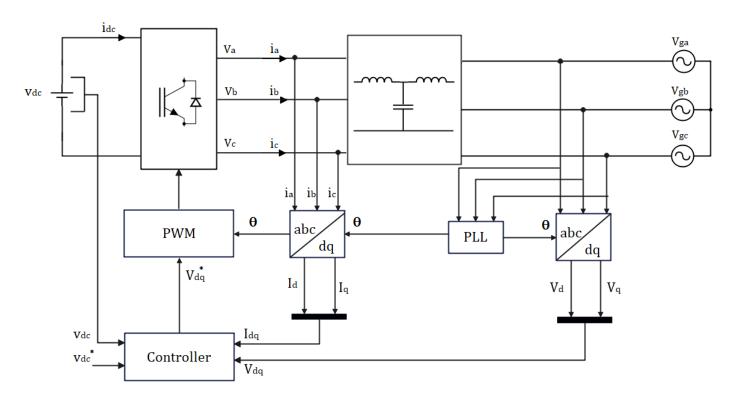

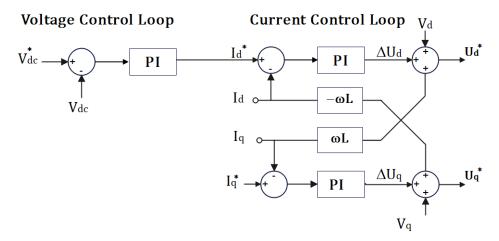

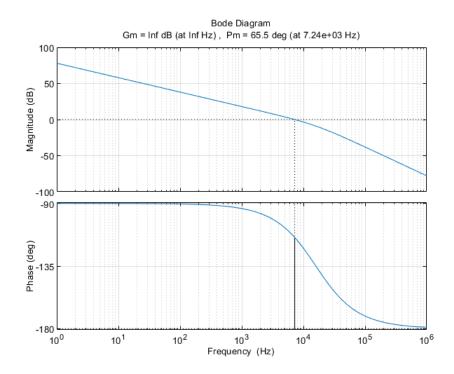

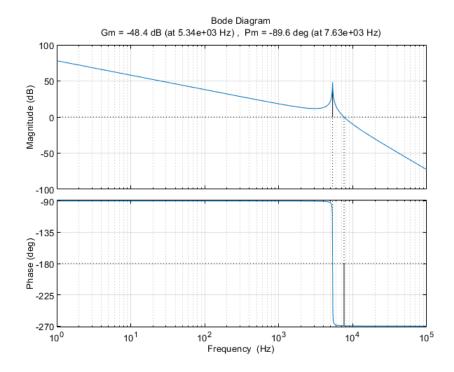

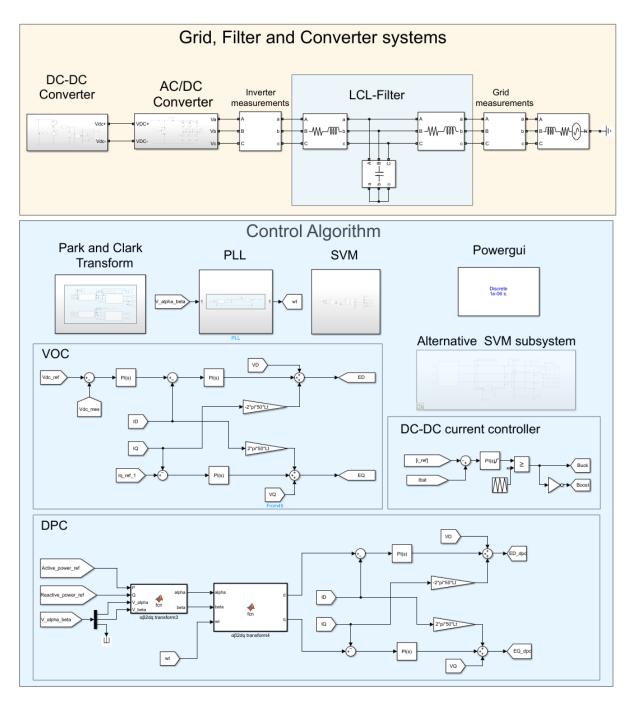

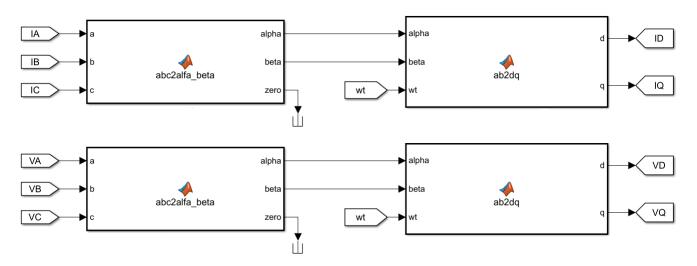

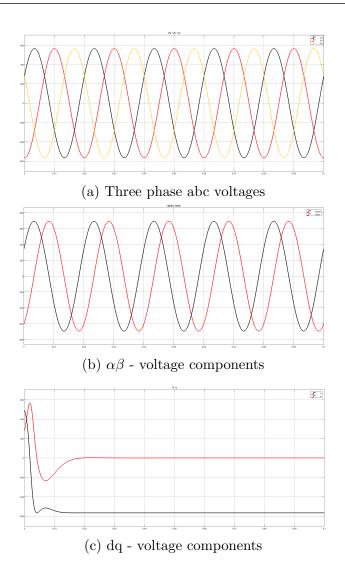

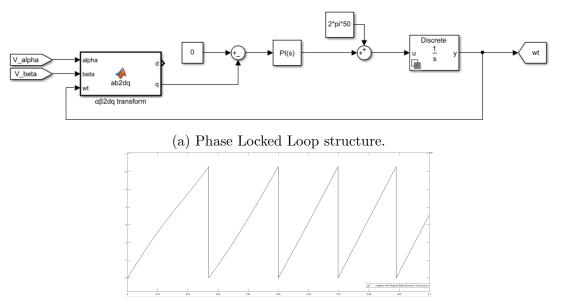

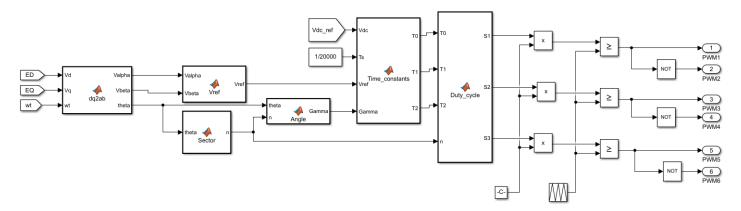

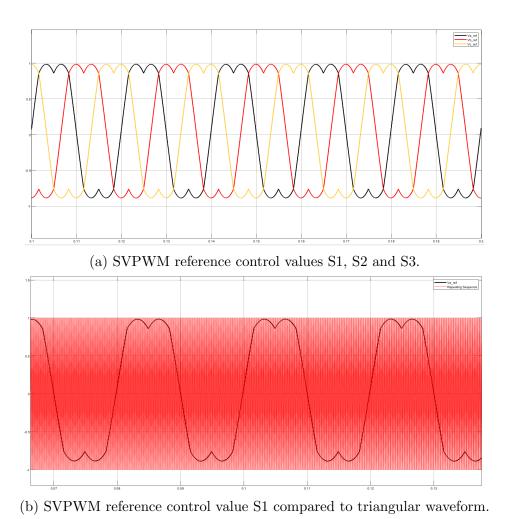

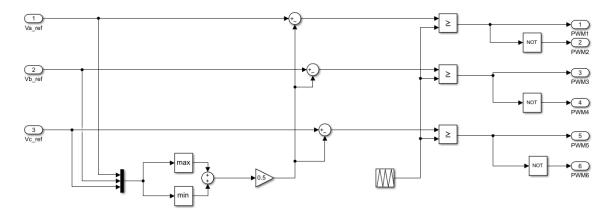

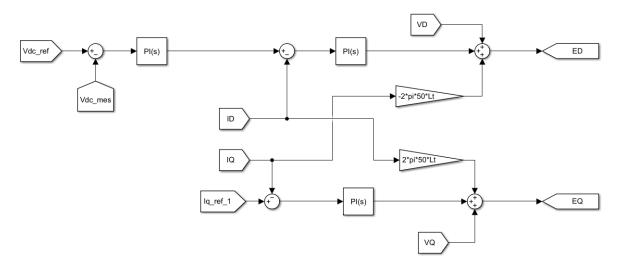

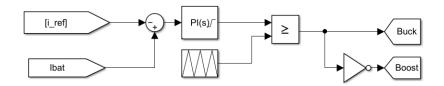

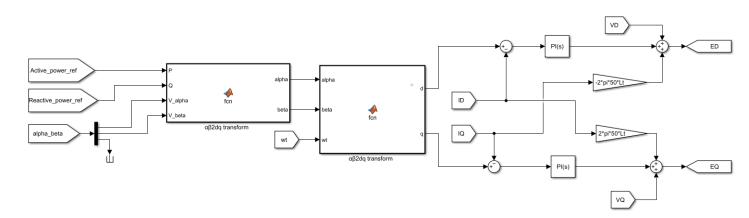

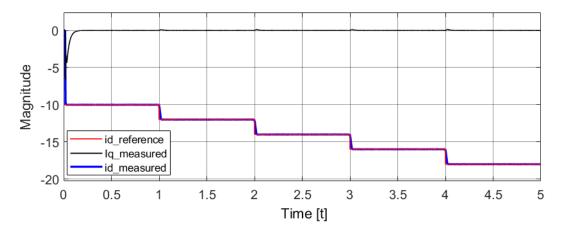

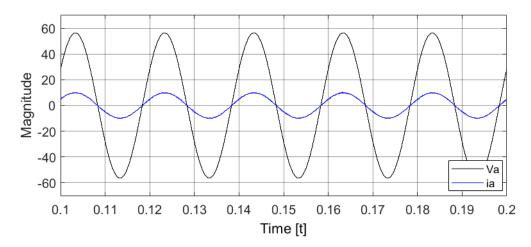

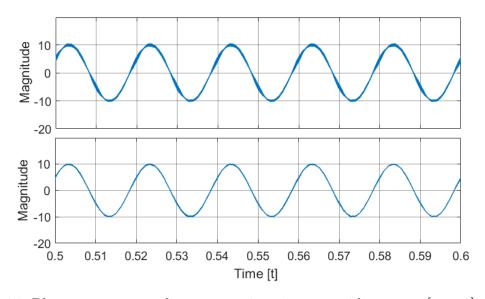

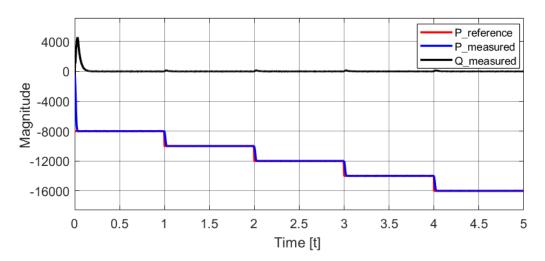

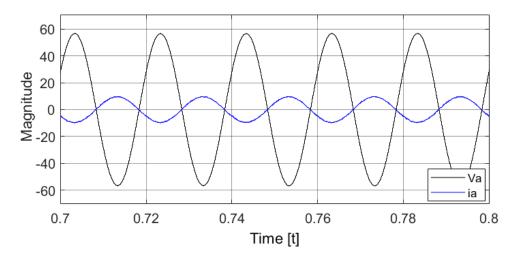

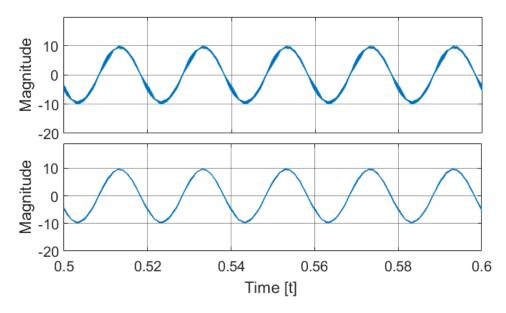

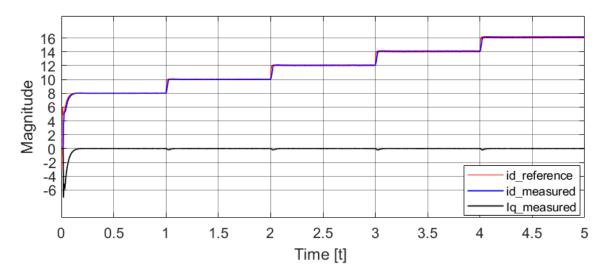

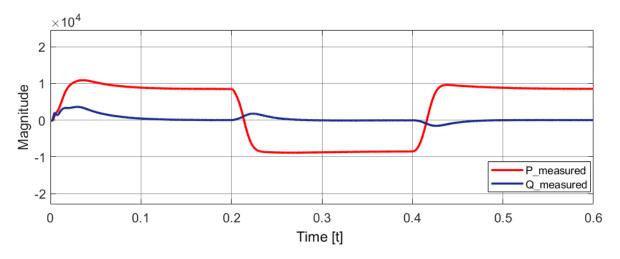

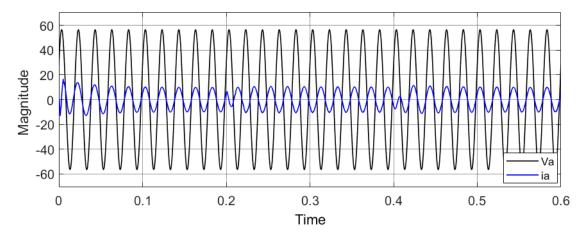

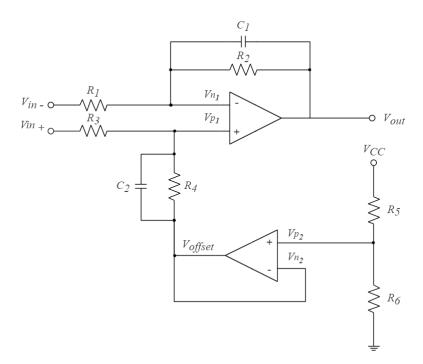

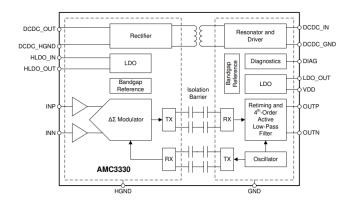

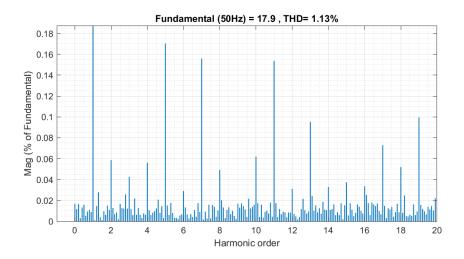

$$T = t_k + t_{k+1} + t_0 (3.15)$$