# Design of a 60 GHz Low Noise Amplifier in a 0.13 µm SiGe BiCMOS Process

A THESIS BY MAGNUS PALLESEN FOR THE DEGREE OF MASTER OF SCIENCE IN PHYSICS

Department of Physics and Technology University of Bergen June 2016

#### Abstract

The Large Hadron Collider (LHC) in CERN outside Geneva in Switzerland is scheduled for an upgrade to improve the luminosity. This upgrade will require higher granularity for the triggering system, increasing the need for very high bandwidth data transfer. This thesis is a part of a feasibility study at the University of Heidelberg regarding the possibilities of using wireless data transfer in the 60 GHz band for data readout on the trigger system. In order to realize 60 GHz data transfer, a fully functional transceiver operating at 60 GHz must be developed. This work covers the design and realization of a low noise amplifier for use in this system.

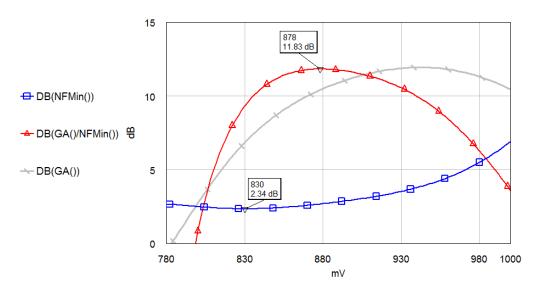

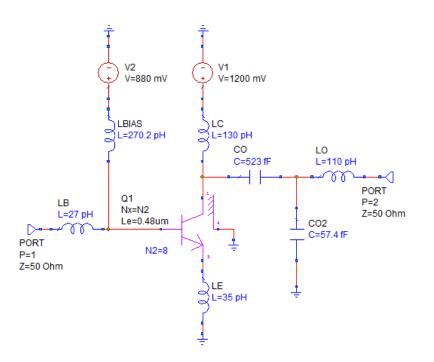

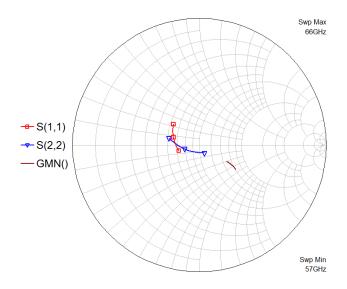

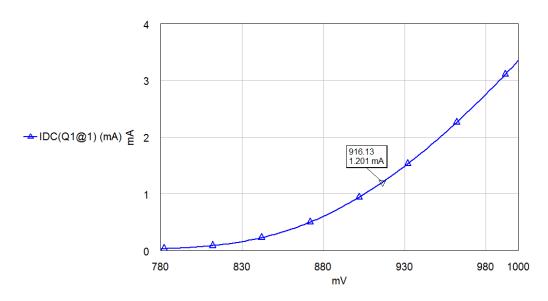

In order to obtain the required design knowledge, a comprehensive study of microwave theory is performed. This theory forms the basis for designing a low noise amplifier operating at very high frequencies. A summary of the most important theory is also included in this thesis.

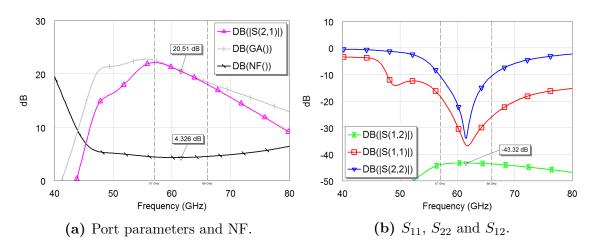

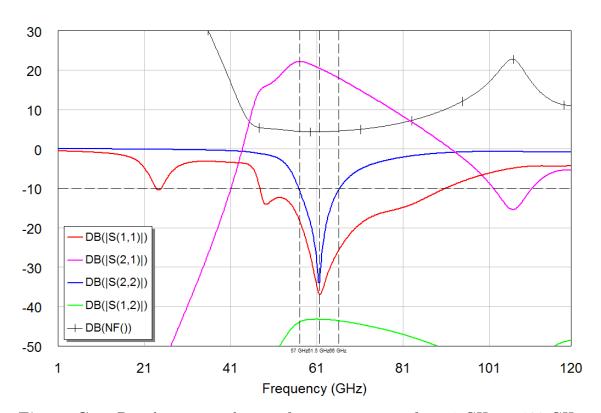

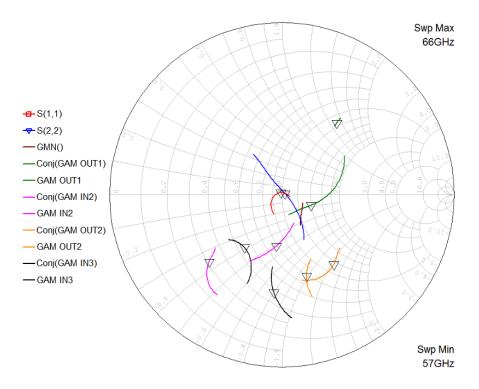

A low noise amplifier for use in a 60 GHz transceiver is designed and simulated using National Instruments Microwave Office. Simultaneous impedance- and noise matching is used in order to realize both low noise and low return loss at the same time. The amplifier is designed in a 0.13  $\mu$ m SiGe BiCMOS process and a layout measuring 0.13 mm<sup>2</sup> is proposed. The resulting low noise amplifier has 9.5 GHz bandwidth, 4.3 dB noise figure, 20.4 dB gain and 9.8 mW power consumption and is within all given specifications. Although the results only show simulated response, we have good reason to believe that these results can be realized by performing a thorough EM simulation and process variation simulation. If this is the case, the resulting amplifier will be very competitive to previously published low noise amplifiers.

## Preface

This work was carried out between August 2015 and June 2016 at the University of Bergen, in collaboration with Hans Kristian Soltveit at the Physikalisches Institut, Heidelberg University.

My experience within electronics at the start of the thesis mainly covered low frequency analog electronics and thus microwave engineering was a completely new topic for me. Microwave engineering is a comprehensive subject and a large part of this work was therefore attributed to the learning of RF design.

A fellow student, Hans Schou, which is designing the power amplifier in the same system, is also in the same situation. This has led to a very productive collaboration in learning microwave engineering theory and RF design methods. We have also continuously discussed various RF topics throughout the thesis and assessed specific problems together in order to ensure the quality of the work. Even though we have collaborated with theory, we have carried out an independent work.

# Acknowledgments

First and foremost, I would like to thank my supervisor **Kjetil Ullaland** at the University of Bergen for his support and guidance throughout this work.

A special thanks goes to **Hans Kristian Soltveit** for providing the opportunity to work with 60GHz IC design, for sharing his vast knowledge within IC design and for arranging an enjoyable trip to Heidelberg University with both great academic progression and local sightseeing.

I would also like to thank **Yngve Thodesen** at the Royal Norwegian Naval Academy for providing essential guidance within RF-design.

Last but not least, I would like to thank my fellow students for great moments at our office. A special thanks goes to **Hans Schou** for the collaboration throughout the whole year and for the good collegial solidarity.

# Contents

| $\mathbf{P}_{\mathbf{I}}$ | Preface |                                         |     |  |  |

|---------------------------|---------|-----------------------------------------|-----|--|--|

| $\mathbf{A}$              | ckno    | wledgments                              | vii |  |  |

| 1                         | Intr    | roduction                               | 1   |  |  |

|                           | 1.1     | System Architecture                     | 2   |  |  |

|                           | 1.2     | 60 GHz Band Characteristics             | 3   |  |  |

|                           |         | 1.2.1 60 GHz transmission               | 4   |  |  |

|                           | 1.3     | Goal of This Thesis                     | 5   |  |  |

|                           | 1.4     | Thesis Outline                          | 6   |  |  |

| <b>2</b>                  | Pro     | cess Technology                         | 7   |  |  |

|                           | 2.1     | III-V Devices                           | 7   |  |  |

|                           | 2.2     | SiGe Heterojunction Bipolar Transistors | 8   |  |  |

|                           | 2.3     | SG13S Process Specification             | 8   |  |  |

|                           |         | 2.3.1 SG13S NPN Transistors             | 9   |  |  |

|                           |         | 2.3.2 SG13S Passive Components          | 10  |  |  |

| 3 Microwave Theory |     | rowav              | e Theory                                                          | 13 |

|--------------------|-----|--------------------|-------------------------------------------------------------------|----|

|                    | 3.1 | Transmission Lines |                                                                   | 13 |

|                    |     | 3.1.1              | Characteristic Impedance                                          | 14 |

|                    |     | 3.1.2              | Transmission Line Reflections                                     | 15 |

|                    |     | 3.1.3              | Wavelength in a dielectric                                        | 17 |

|                    | 3.2 | Scatte             | ering Parameters                                                  | 17 |

|                    | 3.3 | Two-p              | oort Power Gain                                                   | 18 |

|                    | 3.4 | Two-p              | oort Noise Parameters                                             | 19 |

|                    |     | 3.4.1              | Optimum source admittance                                         | 21 |

|                    | 3.5 | Smith              | Chart                                                             | 22 |

|                    |     | 3.5.1              | Constant-Gain Circles                                             | 24 |

|                    |     | 3.5.2              | Unilateral Figure of Merit                                        | 25 |

|                    |     | 3.5.3              | Constant-Noise Circles                                            | 26 |

|                    | 3.6 | Imped              | lance Matching                                                    | 28 |

|                    |     | 3.6.1              | Matching with lumped elements using the Smith Chart $\ . \ . \ .$ | 28 |

|                    |     | 3.6.2              | Transmission Line Impedance Transformation                        | 30 |

|                    |     | 3.6.3              | Single Element Matching                                           | 31 |

|                    |     | 3.6.4              | Single-stub Matching                                              | 32 |

|                    |     | 3.6.5              | Two-element Matching                                              | 32 |

|                    |     | 3.6.6              | Considerations With Lossy Transmission Lines                      | 33 |

|                    |     | 3.6.7              | Smith Chart Q-Contours                                            | 33 |

| 4                  | т   | NT - •             | A                                                                 | 95 |

| 4                  |     |                    | e Amplifier Design Methodology                                    | 35 |

|                    | 4.1 | -                  | ogies                                                             |    |

|                    | 4.2 |                    |                                                                   |    |

|                    |     | 4.2.1              | Noise Sources in Bipolar Transistor                               | 36 |

|   |     | 4.2.2   | Minimum Noise Figure                                                                                                                           | 7 |

|---|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |     | 4.2.3   | Noise Matching                                                                                                                                 | 8 |

|   |     | 4.2.4   | Noise in Casaded Stages                                                                                                                        | 8 |

|   | 4.3 | Stabili | ty                                                                                                                                             | 9 |

|   |     | 4.3.1   | Single Stage Stability                                                                                                                         | 9 |

|   |     | 4.3.2   | Multistage Stability                                                                                                                           | 0 |

|   | 4.4 | Non-li  | nearity                                                                                                                                        | 1 |

|   |     | 4.4.1   | 1dB Compression Point                                                                                                                          | 1 |

|   |     | 4.4.2   | Intermodulation Distortion                                                                                                                     | 2 |

|   |     | 4.4.3   | Emitter Degeneration                                                                                                                           | 2 |

|   | _   |         |                                                                                                                                                |   |

| 5 | Des | 0       | d Simulation 45                                                                                                                                | 5 |

|   | 5.1 | Design  | Specifications and Topology Decision                                                                                                           | 5 |

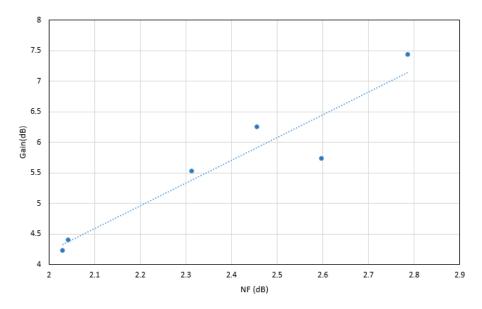

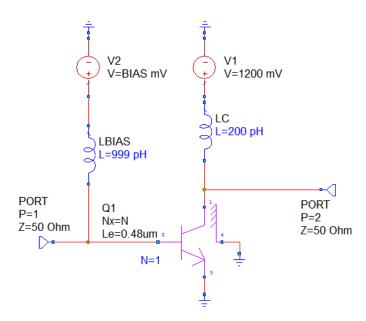

|   | 5.2 | Choose  | ing Transistor $\ldots \ldots 40$                          | 6 |

|   | 5.3 | Gain v  | rs. Noise Trade-off                                                                                                                            | 6 |

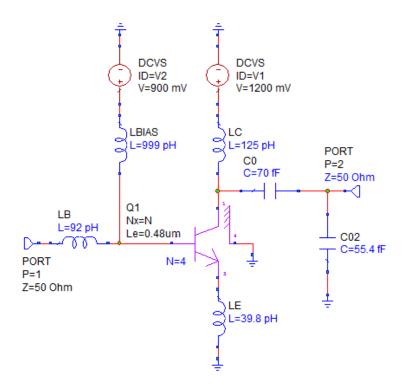

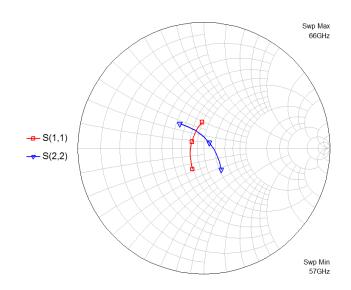

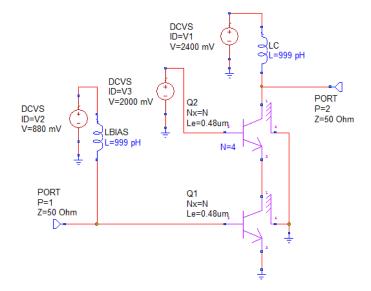

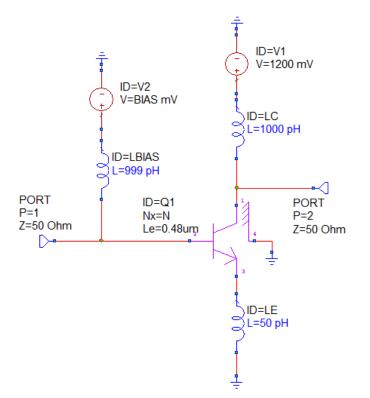

|   | 5.4 | Input   | Stage Design                                                                                                                                   | 8 |

|   | 5.5 | Second  | l Stage Design                                                                                                                                 | 3 |

|   | 5.6 | Outpu   | t Stage Design                                                                                                                                 | 6 |

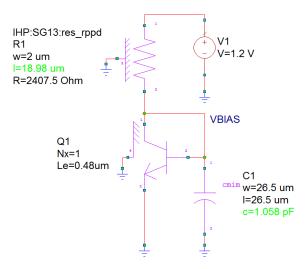

|   | 5.7 | Bias C  | fircuit                                                                                                                                        | 9 |

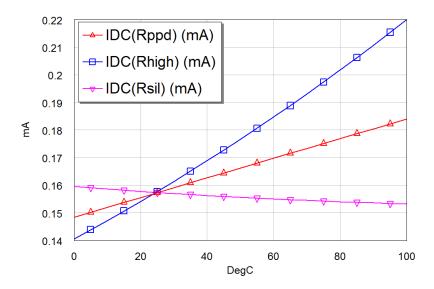

|   |     | 5.7.1   | Bias Circuit Temperature Dependency 6                                                                                                          | 1 |

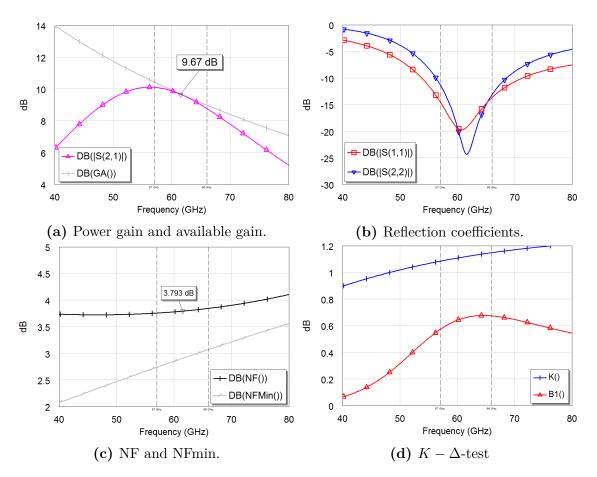

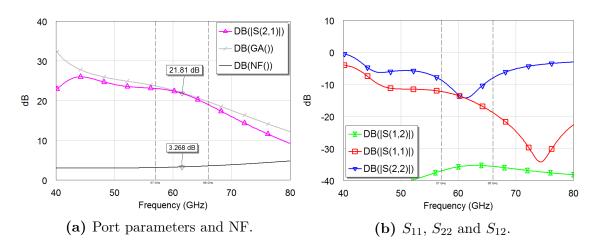

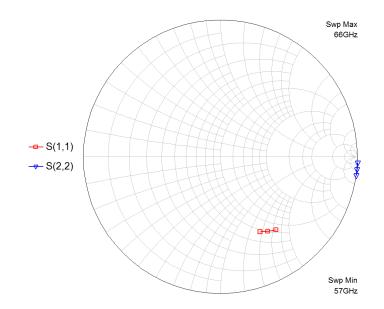

|   | 5.8 | Multis  | tage Design $\ldots \ldots 62$ | 2 |

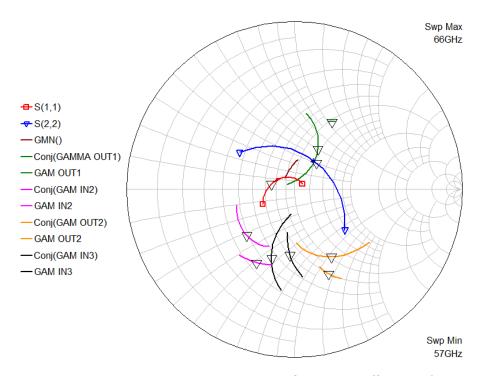

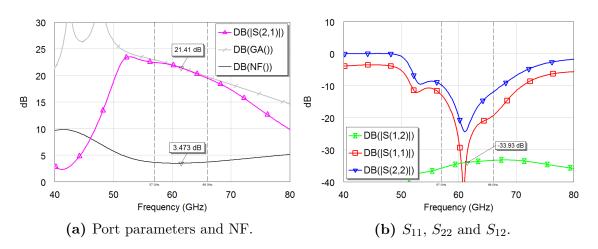

|   |     | 5.8.1   | Improving the Initial Design                                                                                                                   | 3 |

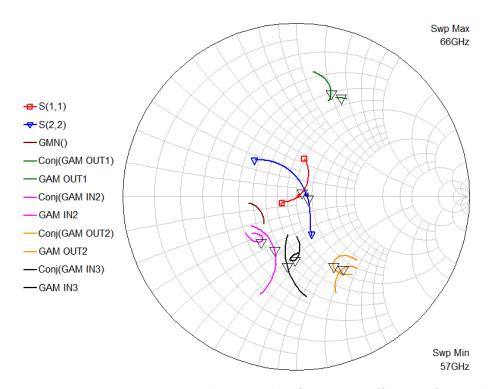

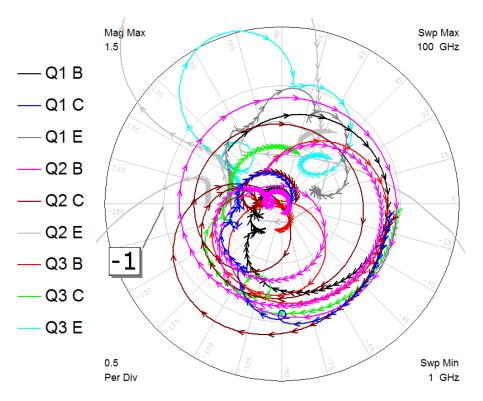

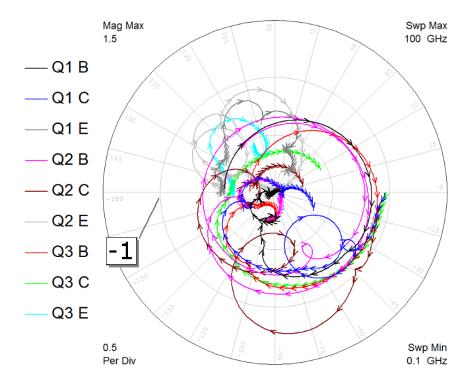

|   |     | 5.8.2   | Stability of Multistage Amplifier                                                                                                              | 5 |

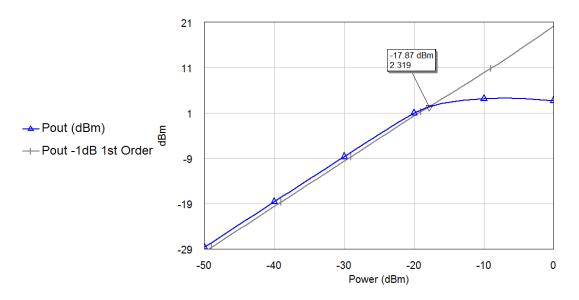

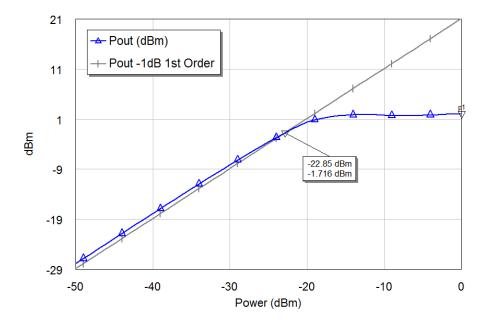

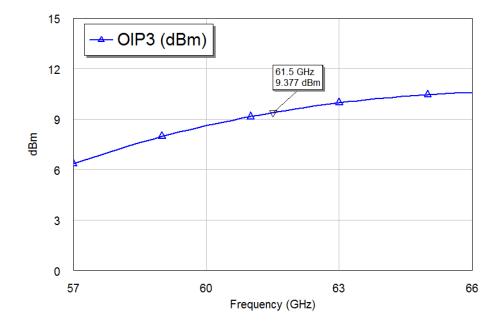

|   |     | 5.8.3   | Compression Point                                                                                                                              | 7 |

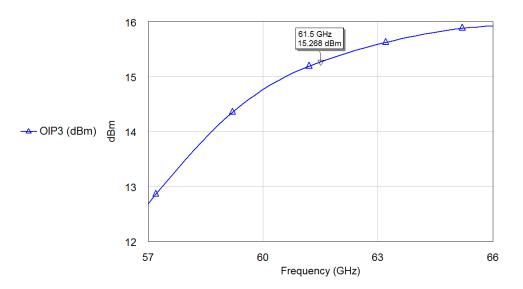

|   |     | 5.8.4   | Intermodulation                                                                                                                                | 7 |

|   |     | 5.8.5   | Results                                                                                                                                        | 8 |

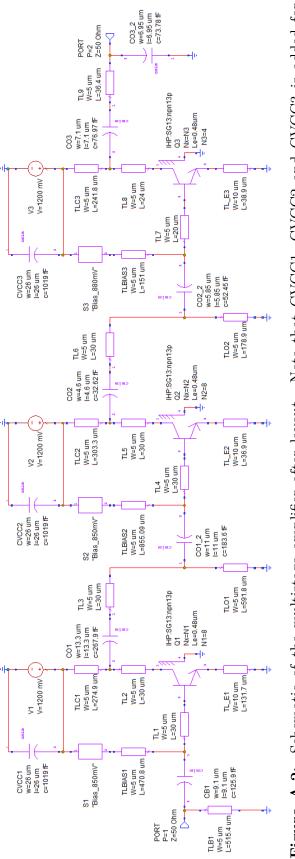

| 6            | Des  | ign Realization and Layout                  | 69 |

|--------------|------|---------------------------------------------|----|

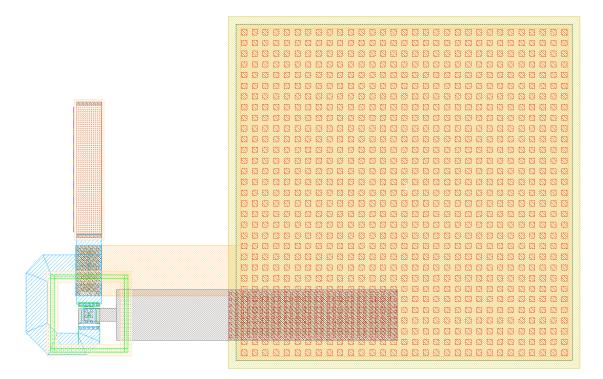

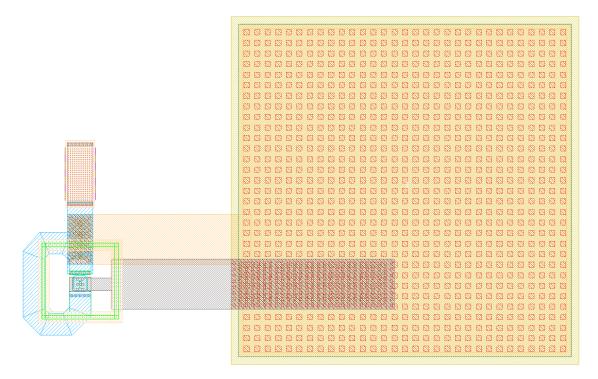

|              | 6.1  | Replacing Inductors With Transmission Lines | 69 |

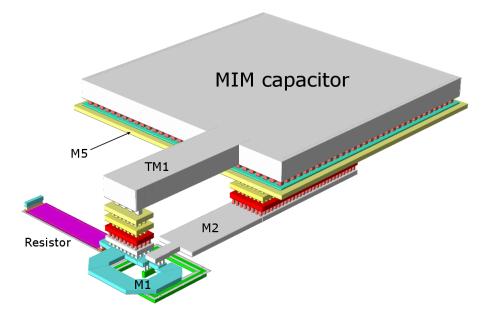

|              | 6.2  | MIM Capacitors                              | 69 |

|              | 6.3  | Thermal Noise From Transmission Lines       | 70 |

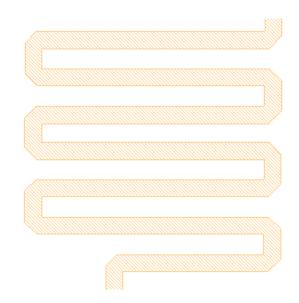

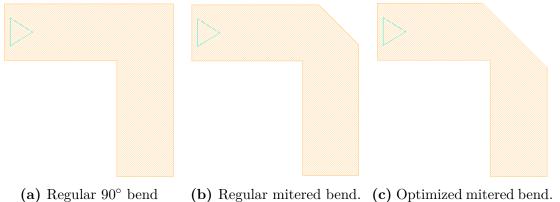

|              | 6.4  | Meandered Transmission Lines                | 70 |

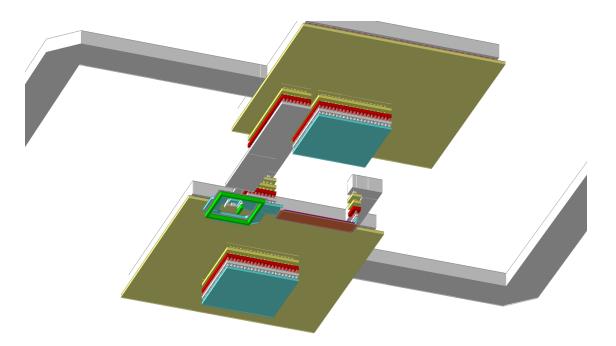

|              | 6.5  | Layout of Bias Circuit                      | 71 |

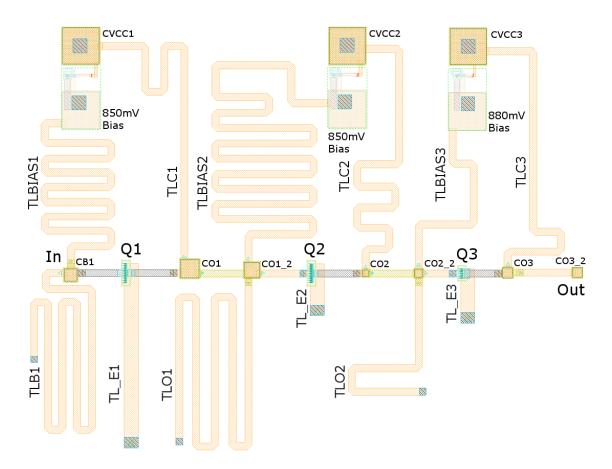

|              | 6.6  | Layout of Multistage Amplifier              | 72 |

|              | 6.7  | Post Layout Simulation Results              | 74 |

| 7            | Dis  | cussion                                     | 77 |

|              | 7.1  | Performance Comparison With Published LNAs  | 77 |

|              | 7.2  | Design Trade-offs                           | 78 |

|              | 7.3  | Simulation Model Accuracy                   | 79 |

|              | 7.4  | CAD Tools                                   | 80 |

|              | 7.5  | Future Work                                 | 80 |

| 8            | Cor  | nclusion                                    | 81 |

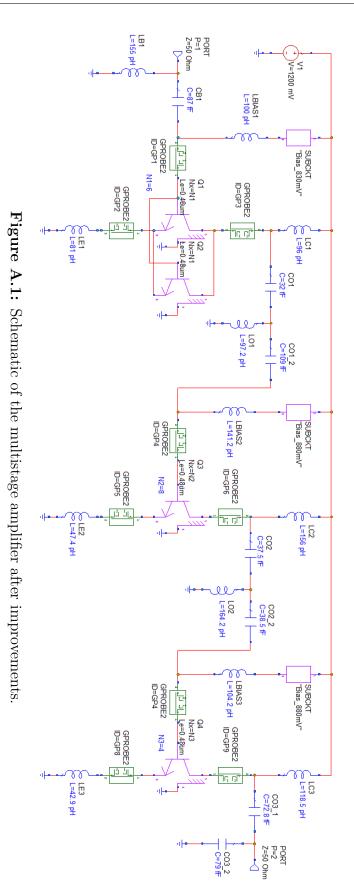

| $\mathbf{A}$ | Cire | cuit Schematics                             | 83 |

| в            | Lay  | out                                         | 87 |

| $\mathbf{C}$ | Pos  | t Layout Simulations                        | 91 |

| D            | Cas  | code Topology Bandwidth Issue               | 95 |

| E            | Tes  | t benches                                   | 97 |

| A            | bbre | viations                                    | 99 |

## CHAPTER 1

## Introduction

The Large Hadron Collider (LHC) in CERN outside Geneva in Switzerland is scheduled for an upgrade to improve the luminosity/collision rate. After the upgrade, there will be in average 50 times more proton-proton collisions. The two multipurpose experiments ATLAS and CMS are therefore facing a big challenge to identify rare physics processes in an immense background of events. A trigger system is used to separate interesting physics processes from the background and in the present detectors the trigger decision is based on information from all sub-detector systems except the tracker. These detectors have limited granularity and after the upgrade it will no longer be able to differentiate physics processes and background. It is therefore interesting to use the tracker data for triggering decision since this detector has the required granularity. There is, however, a challenge in reading the amount of data produced by the tracker in time for the fast trigger decision. The bandwidth required to perform a complete readout of the silicon micro-strip tracker is between 50 and 100 Tb/s. In order to use the tracker in the fast triggering system it is therefore necessary to increase the transfer bandwidth from the tracker or reduce the amount of data or use a combination of both. [2]

This high bandwidth readout has usually been performed using wire based systems or optical links, perpendicularly to the particle path. The weakness of this approach is the size of the connectors and that the cabling is mechanically fragile. In addition to this, the readout is bound to the modularity of the tracker which is not ideal for a fast trigger decision. Wireless data transfer does however not suffer from these problems.

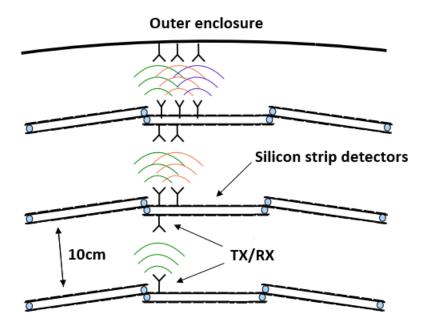

The technical paper Towards Multi-Gigabit readout at 60 GHz for the ATLAS silicon microstrip detector[26] describes a system for reading out the data radially using wireless transceivers operating in the 60 GHz band. Figure 1.1 illustrates the idea of wireless radial readout. The bandwidth in the proposed system is much higher

Figure 1.1: Radial readout for the tracker detector of the ATLAS experiment [26].

than the present optical links, the connectors are not needed and the readout can be performed radially instead of perpendicular. [2]

The 60 GHz band provides a spectral bandwidth of 4 - 9 GHz, which combined with a good modulation scheme would allow for a data rate in the 10's of Gbs [26]. In order to realize this data transfer, a fully functional 60 GHz transceiver must be developed for this purpose. This thesis focuses on the design of a 60 GHz Low Noise Amplifier (LNA) for use in this transceiver.

## **1.1** System Architecture

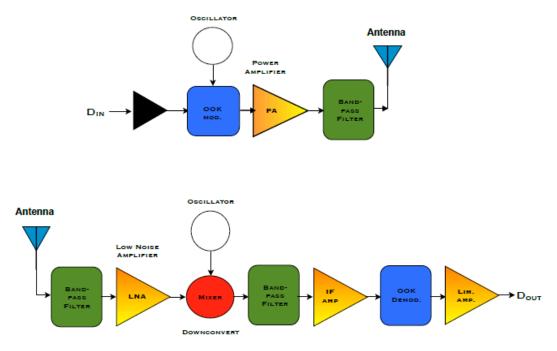

Figure 1.2 shows a block diagram of the proposed 60 GHz system. The system consists of two parts, the transmitter and the receiver. The transmitter part comprises of an oscillator which provides the carrier frequency, an on-off-keying (OOK) modulator, a power amplifier and a band pass filter. The band pass filter is necessary in order to suppress broad band noise generated from the PA. The receiver chain consists of a band pass filter, a low noise amplifier, a mixer, an intermediate frequency (IF) amplifier and an OOK demodulator. The low noise amplifier is located behind a band pass filter, which is present to filter out of band interference. The input sensitivity of the LNA must be very high, and it must produce very little noise in order to maintain the integrity of the signal.

Both the transmitter and receiver is to be implemented on a single transceiver chip.

Figure 1.2: Block diagram of proposed 60 GHz system[26]

### **1.2 60 GHz Band Characteristics**

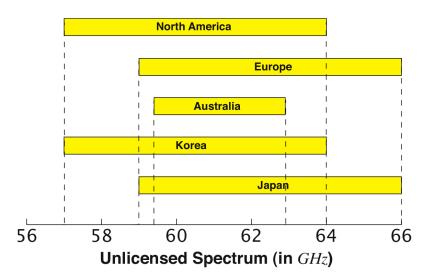

Frequencies from 30 - 300 GHz has very short wavelengths ranging from 1 - 10 mm and is therefore called millimetre waves. Use of these frequencies has increased in popularity due to technology advances and is today used in several applications. Millimetre wave radars using 77 GHz provides good resolution and small integration size in the automotive industry and is also a key component in future autonomous cars. The millimetre wave based imaging is a different type of radar application where millimetre waves is used in security and surveillance applications to disclose concealed items [30]. In addition, the 60 GHz band provides up to 7 GHz of unlicensed bandwidth. This allows for multigigabit short range wireless transfer in many applications. Figure 1.3 shows the unlicensed band for different regions.

The 60 GHz frequencies have several properties beneficial for short range communication. One of the properties is the atmospheric attenuation caused by the absorption of microwave energy in molecular oxygen. Maximum absorption occurs when the frequency is equal to one of the resonance frequencies of the water vapor or molecular oxygen[22]. This absorption is peaking at 60 GHz, making long range communication with 60 GHz unsuitable. Since the range of transmission in our system is well below 1 m, this attenuation will not influence the signal noteworthy. It does however ensure that radio waves from other interfering 60 GHz sources is well attenuated.

Another benefit of the 60 GHz band for this specific purpose is the high attenuation

Figure 1.3: Unlicensed spectrum for 60 GHz band. [6]

through silicon detectors. The wide bandwidth also allows for a simple and low spectrum efficiency modulation scheme.

#### 1.2.1 60 GHz transmission

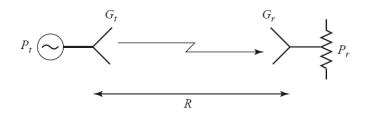

Figure 1.4 shows a basic radio system where  $P_t$  is the transmit power,  $G_t$  is the transmitter antenna gain,  $G_r$  is the receiver antenna gain,  $P_r$  is the power delivered to the matched load and R is the distance between the antennas.

The delivered power is described by the *Friis formula* given in equation 1.1 [22].

$$P_r = \frac{G_t G_r \lambda^2}{(4\pi R)^2} P_t \tag{1.1}$$

The received power is highly dependent on the distance between the antennas as well as the frequency. The transmitted power is distributed isotropically, causing the power to drop over distance since the transmitted power musts cover a larger area corresponding to a growing sphere. The  $\frac{1}{4\pi R^2}$  term is due to this power loss. The frequency dependency is not because of the signal getting attenuated in free space, but rather due to a definition that the antenna is unity gain. Antenna size is dependent on the frequency. The lower the frequency is, the larger the antenna is. A larger antenna would be able to cover a larger area and hence the energy collection is better. This leads to the frequency dependency,  $\lambda^2$ .

A useful measure of the attenuation in free space is the free space path loss (FSPL). This is basically the ratio of the transmitted power and received power with unity gain antennas. For a signal in the 60 GHz band this would lead to the following loss

Figure 1.4: Basic radio system[22]

for one meter:

$$FSPL = \left(\frac{4\pi d}{\lambda}\right)^2 = \left(\frac{4\pi \times 1\mathrm{m}}{5\mathrm{mm}}\right)^2 = 68\mathrm{dB}$$

(1.2)

## 1.3 Goal of This Thesis

The goal of this thesis is to design and simulate a low noise amplifier for use in the 60 GHz transceiver ASIC. In addition, a layout should be made and eloectromagnetic (EM) simulations performed to ensure that parasitics are accounted for. The performance of the LNA must satisfy the specifications given by Table 1.1.

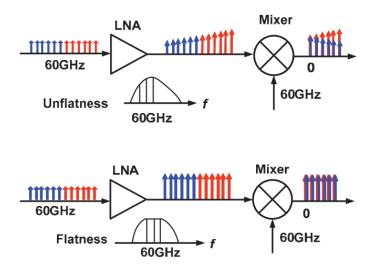

The bandwidth is defined by the region where  $S_{11}$  and  $S_{22}$  is below -10 dB, although this measure is somewhat conservative. The gain should be as flat as possible within the bandwidth without sacrificing power consumption and fall below 0 dB as quickly as possible. Both gain and noise is specified for the center frequency, 61.5 GHz. The input and output is to be matched towards 50  $\Omega$ , since the bonding method and antenna configuration is not yet decided.

| Specification     | Value         | Unit           |

|-------------------|---------------|----------------|

| Bandwidth         | 57-66         | GHz            |

| Input sensitivity | -100  to - 30 | $\mathrm{dBm}$ |

| $S_{21}$          | $\geq 20$     | $\mathrm{dB}$  |

| Noise Figure      | $\leq 5$      | $\mathrm{dB}$  |

| Power Consumption | $\leq 12$     | $\mathrm{mW}$  |

| $S_{11}$          | $\leq -10$    | $\mathrm{dB}$  |

| S <sub>22</sub>   | $\leq -10$    | dB             |

Table 1.1:LNA specifications.

## 1.4 Thesis Outline

This section provides an overview over the different chapters in the thesis.

- Chapter 2 Microwave theory Provides basic theory related to transmission lines and RF circuit design for better understanding of this thesis.

- Chapter 3 Process technology Brief introduction to different RF processes and the SG13S process.

- Chapter 4 Low noise amplifier design methodology Theory related to low noise amplifier design.

- **Chapter 5 Design and simulation** A detailed description of the whole design procedure as well as pre-layout simulations.

- Chapter 6 Design Realization and Layout Realization of design with real components and design of layout. Post-layout simulations.

- Chapter 7 Discussion The results of the design is discussed.

- Chapter 8 Conclusion A conclusion is made based on the results of this work.

## CHAPTER 2

# Process Technology

This chapter includes a description of the chosen process technology as well as some theory related to the transistors and process. In addition to this, a brief explanation of some common RF processes are made.

## 2.1 III-V Devices

Silicon (Si) devices are well suited to high-transistor-count, high-volume production of microprocessors, memory applications and general purpose ICs. Although Si is the most used semiconductor it has small electron and hole mobility as well as relatively low saturation velocity, compared to other processes. RF and microwave circuit applications places high performance demands and thus Si may provide insufficient performance for these applications. Many of the compound semiconductors<sup>1</sup> from group III and V provides far better mobility and saturation velocities. GaAs and InP are two semiconductor compounds that are widely used whereas GaAs is often used in RF circuits. In addition to the improved speed, the bandgaps of III-V devices are easily altered for specific needs. This atomic-level customization of the semiconductor is called *bandgap-engineering*. [5]

One of the drawbacks of III-V devices is that the yield is lower than for standard Si technologies[5]. In addition to this, the thermal conduction is poorer. The result is that the production is more difficult causing more expenses. In order to overcome these drawbacks, SiGe was utilized to allow for bandgap-engineering in the Si material system.[5]

$<sup>^1\</sup>mathrm{A}$  compound semiconductor is made of elements from two or more different groups of the periodic table.

## 2.2 SiGe Heterojunction Bipolar Transistors

A heterojunction is a pn junction made of two different materials [11]. In contrast, a regular bipolar homojunction transistor uses the same material in both the p-type and n-type regions. In the 0.13 µm SiGe process the transistors are heterojunction with silicon n-type region and germanium p-type region (the base of the transistor). Usually 10-20% of the atoms in the silicon crystalline in the base are replaced with Ge atoms.

By adding Ge to the base one can change the bandgaps of the two junctions. Ge has lower bandgap than Si and by forming a SiGe compound in the base, the bandgap for this region can be decreased [11]. The relatively large bandgap in the emitter is used to prevent holes from being injected from the base to the emitter and therefore the current gain,  $\beta$ , gets higher since the base current is lower in theory. In addition to this it is now possible to dope the base region more heavily and reduce the base width compared to a normal BJT. This decreases the transit time and base capacitance, without making the base resistance larger. The net result is that  $f_T$ increases, making the HBT more beneficial for high frequency applications compared to a normal BJT. [10]

SiGe HBTs can also be easily adapted with Si CMOS to form a monolithic SiGe HBT BiCMOS technology [5]. Compared to a normal CMOS process, the typical SiGe process has a mask addition of approx. 20%. This means that there will be an increase of approx. 20% in process manufacturing steps. This is often considered as an acceptable compromise between performance benefit and cost[5].

## 2.3 SG13S Process Specification

The process technology chosen for realization of the transceiver is the SG13S process from IHP (Innovations for High Performance Microelectronics). SG13S is a high performance 0.13  $\mu$ m BiCMOS process. The process includes SiGe npn-HBTs with  $f_T$  and  $f_{max}$  up to 250GHz and 340GHz respectively. This makes the process ideal for applications in the higher GHz bands.

This section includes basic information about the SG13S process. The process specification is IHP confidential proprietary and thus the details provided in this work is published online at the IHP website[13].

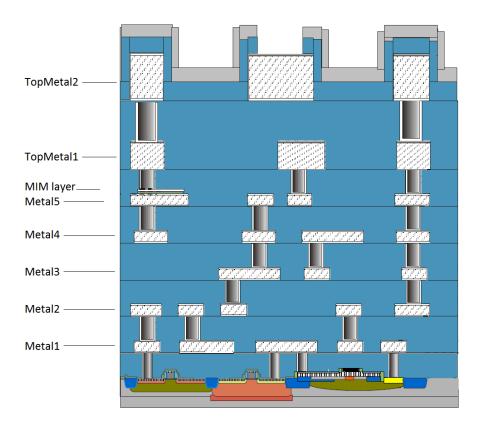

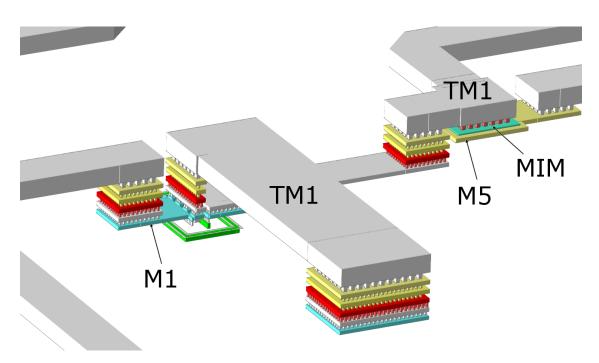

The SG13S process provides 7 layers of aluminum metal whereas two of the layers are thick top-metal layers. These top-metal layers are intended for design of passives e.g. inductors and transmission lines in order to reduce the resistance and parasitic capacitance. In addition to this, a special MIM layer is available for MIM capacitors. Each metal layer is separated by a layer of Silicon-dioxide.

Figure 2.1 shows a cross-section of the SG13S process.

Figure 2.1: Cross-section of SG13S process (not to scale) [12]

#### 2.3.1 SG13S NPN Transistors

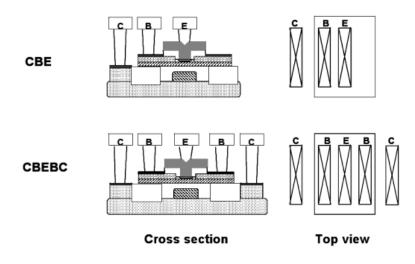

SG13S provides three different HBT transistors, npn13p, npn13pl2 and npnv2. npnv2 is a high voltage transistor with a relatively low  $f_T$ . npn13p and npn13pl2 have comparable  $f_T$  but differs in the way the layout is made. npn13p utilizes a BEC layout while npn13pl2 utilizes a CBEBC layout. These two configurations are shown in Figure 2.2. Table 2.1 shows the performance of the npnpl2 transistor.

BEC layout was historically preferred by IHP, but the CBEBC layout was included in the  $0.13\mu$ m process due to the fact that users of other technologies are used to CBEBC layout. In addition to this, CBEBC layout is mandatory for the high voltage npn and thus implementing the CBEBC layout for the high performance transistor is easy. (G. Fischer, IHP, private communication, 01.12.2015)

The BEC layout has the disadvantage that the base resistance gets high when the emitter length increases. This will lower the  $f_{max}$ . For high power design one should therefore use many emitters in parallel. npn13p is available in two lengths, 0.48µm

| Parameter        | npn13p                           |

|------------------|----------------------------------|

| $\overline{A_E}$ | $0.12\times0.48~\mu\mathrm{m}^2$ |

| Peak $f_{max}$   | 340                              |

| Peak $f_T$       | 250                              |

| $BV_{CE0}$       | 1.7                              |

| $BV_{CB0}$       | 5                                |

| $\beta$          | 900                              |

Table 2.1:

SG13S npn13pl2 bipolar performance

Figure 2.2: BEC vs CBEBC layout [15]

and  $0.84 \mu m$ .

#### 2.3.2 SG13S Passive Components

SG13S provides models for MIM capacitors, planar spiral inductors and poly silicon resistors.

Metal-insulator-metal (MIM) capacitors are formed between Metal 5 and a special MIM layer located above Metal 5. The distance between the two metal layers is very short and thus it is possible to gain high values of capacitance.

Inductors are not well documented in the process specification, but IHP provides a model for an octagonal planar spiral inductor. The inductor is formed on topmetal 2 with contacts on top-metal 1. The minimum inductance provided by these inductors is approx. 120 pH, making it unsuitable for use in very high frequency designs e.g. 60 GHz.

| SG13S provides three different types of resistors with sheet resistances ranging from |

|---------------------------------------------------------------------------------------|

| low to high. These are listed in Table 2.2.                                           |

| Resistor | Sheet Resistance | Resistor material  |

|----------|------------------|--------------------|

| Rsil     | -                | N+ poly resistor   |

| Rppd     | $250 \ \Omega$   | P+ poly resistor   |

| Rhigh    | 1300 $\Omega$    | High Poly Resistor |

Table 2.2: SG13S resistors

## chapter 3

# Microwave Theory

This chapter will provide basic theory related to transmission lines and RF circuit design for better understanding of this thesis. The theory is mainly based on subjects found in [21], [22] and [18].

## **3.1** Transmission Lines

Standard circuit analysis requires the assumption that the physical dimension of the network is much smaller than the wavelength of the electrical signal. This means that the amplitude and phase is unchanged through the whole network. For a transmission line where the electrical wavelength is comparable<sup>1</sup> to or shorter than the length of the line, this assumption is no longer true. The amplitude and phase can now vary along the transmission line, as a consequence of finite speed of wave propagation.

Transmission line elements with a finite physical length are thus called *distributed elements* while elements with negligible physical dimensions are called *lumped elements*.

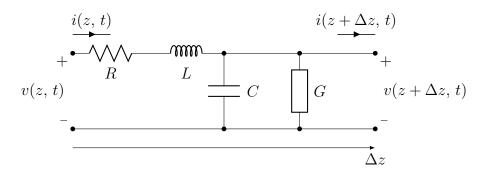

The transmission line can be represented by a lumped element model shown in figure 3.1. The model represents a small fraction of the whole transmission line, and a complete transmission line consists of several cascaded lumped element models.

L is the series inductance represented by self inductance of the conductors. C is the shunt capacitance, caused by the close proximity of the conductors. R and Grepresent losses due to the series resistance of the conductor, R, and the dielectric

<sup>&</sup>lt;sup>1</sup>Generally considered to be  $\frac{\lambda}{10}$  [28]

Figure 3.1: Lumped element model of a small fraction of a transmission line.

losses in the material between the conductors, G.

By using kirchoff's voltage law and solving the differential equations, it can be shown that the traveling wave solutions for a transmission line is [21]:

$$V(z) = V_0^+ e^{-\gamma z} + V_0^- e^{\gamma z}, \qquad (3.1)$$

$$I(z) = I_0^+ e^{-\gamma z} + I_0^- e^{\gamma z}.$$

(3.2)

where the <sup>+</sup> and <sup>-</sup> label denotes respectively the incident wave and the reflected wave.  $\gamma$  is the propagation constant given by equation 3.3:

$$\gamma = \alpha + j\beta = \sqrt{(R + j\omega L)(G + j\omega C)}$$

(3.3)

The real part,  $\alpha$ , is called the *attenuation constant*, while the imaginary part,  $\beta$ , is called the *phase constant*.

In the traveling wave solution, the  $e^{-\gamma z}$  term represents the wave propagation in the +z direction while the  $e^{\gamma z}$  term represents the wave traveling in the -z direction. In other words, both the incident wave and the *reflected* wave is represented in the traveling wave solution. Reflection of a traveling wave is a transmission line phenomenon that will be further discussed in section 3.1.2.

#### 3.1.1 Characteristic Impedance

The characteristic impedance  $Z_0$  of a lossy transmission line is given by equation 3.4 [21]. The definition of this impedance is based on the ratio of the positive and negative traveling voltage and current wave. Therefore,  $Z_0$  is not an impedance in the conventional circuit sense.

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}} = \frac{V_0^+}{I_0^+} = \frac{V_0^-}{I_0^-}$$

(3.4)

For a lossless transmission line, this simplifies to equation 3.5.

$$Z_0 = \sqrt{\frac{L}{C}} \tag{3.5}$$

Note that the characteristic impedance is no longer frequency dependent when the transmission line is lossless.

#### **3.1.2** Transmission Line Reflections

When a incident wave initially travels down a transmission line, the voltage to current ratio must satisfy the characteristic impedance. However, when the transmission line is terminated with an impedance not equal to the characteristic impedance, the voltage to current ratio will no longer satisfy the load impedance. Therefore a reflected wave must be generated at the load to satisfy this condition.

The voltage ratio of the reflected wave to the incident wave is called the reflection coefficient, and is denoted by  $\Gamma$ , given by equation 3.6 [21].

$$\Gamma = \frac{V_0^-}{V_0^+} = \frac{Z_L - Z_0}{Z_L + Z_0} \tag{3.6}$$

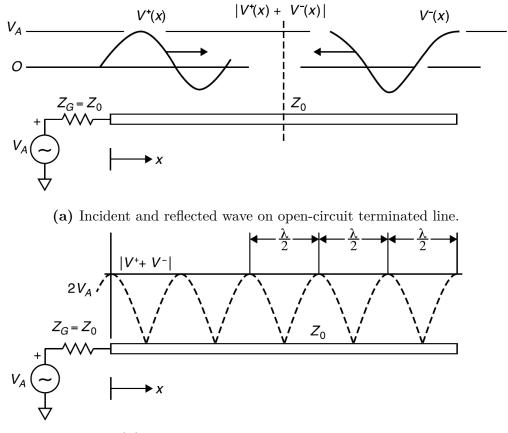

Figure 3.2a shows how a sinusoidal wave travels on a open-circuit terminated transmission line. The incident wave,  $V^+$ , is reflected at the end of the line, due to the impedance mismatch, causing a reflected wave,  $V^-$ . This reflected wave will sum with the incident wave and distort the transmitted signal. Since the source resistance is equal to the characteristic impedance, all the energy from the reflected wave will then dissipate in the source.

When the length of the transmission line is a multiple of  $\frac{\lambda}{2}$ , standing wave patterns will form as shown in 3.2b. Since the incident wave is in phase with the reflected wave, the amplitude is doubled at their maxima. The maxima and minima are separated by a half wavelength due to the doubling of their relative velocities resulting from their opposite directions of travel [28].

By sizing the load resistance equal to the characteristic impedance, one can eliminate the reflections by making  $\Gamma = 0$ . We then obtain what is called a *matched* load.

Although the reflections is unwanted in most situations, one can purposely introduce reflections in order to provide impedance matching. This is called *impedance matching with distributed elements* and is discussed further in Section 3.6.2

(b) Standing waves on a transmission line.

Figure 3.2: Behaviour of traveling waves on an open-circuit terminated transmission line. [28]

Figure 3.3: Convention for defining S-parameters.

#### 3.1.3 Wavelength in a dielectric

The velocity of a wave propagating with air as dielectric is very close to the speed of light in vacuum. This is due to the relative permittivity of air which is  $\approx 1$ . The velocity and thus the wavelength of the wave propagating is reduced when traveling in a dielectric material with higher than 1 relative permittivity. This relationship is given by Equation 3.7 [28]:

$$\lambda = \frac{v}{f\sqrt{\epsilon_R}},\tag{3.7}$$

where  $\epsilon_R$  is the relative permittivity of the material.

### **3.2** Scattering Parameters

Scattering parameters or S-parameters are commonly used to characterize a twoport network in RF circuit design. The reason for not using the traditional two-port parameters is the fact that in order to determine the parameters one would need to short or/and open the input and output of the two-port network. This is not preferable due to several reasons. For instance, a wire from a short may introduce a significant amount of inductance, and an open circuit can load the output with a significant amount of capacitance. Both instances may cause failure of the correct conditions for determining the traditional two-port parameters. Another aspect is that a short or/and open circuit will cause reflections of the traveling waves. By using S-parameters it is possible to characterize the two-port network without requiring unachievable terminal conditions. [18]

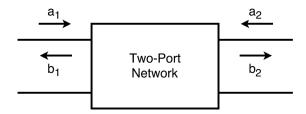

Figure 3.3 shows the convention for s-parameters. Each port has two parameters,  $a_n$  and  $b_n$ .  $a_n$  represents the wave traveling towards the network.  $b_n$  represents the wave traveling away from the network. All parameters are normalized by the characteristic impedance,  $Z_0$ .

The S-parameter matrix for a two port network are as follows [18]:

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(3.8)

Figure 3.4: General two-port amplifier

where the terms are

$$S_{11} = \frac{b_1}{a_1} \bigg|_{a_2=0} \equiv \frac{\text{reflected power wave at port 1}}{\text{incident power wave at port 1}}$$

(3.9)

$$S_{21} = \frac{b_2}{a_1}\Big|_{a_2=0} \equiv \frac{\text{Transmitted power wave at port } 2}{\text{incident power wave at port } 1}$$

(3.10)

$$S_{22} = \frac{b_2}{a_2} \bigg|_{a_1=0} \equiv \frac{\text{reflected power wave at port } 2}{\text{incident power wave at port } 2}$$

(3.11)

$$S_{12} = \frac{b_1}{a_2} \bigg|_{a_1=0} \equiv \frac{\text{Transmitted power wave at port 1}}{\text{incident power wave at port 2}}$$

(3.12)

$a_2 = 0$  and  $a_1 = 0$  conditions assumes that no power waves are returned to the network. These conditions requires that the transmission lines are terminated with the characteristic impedance.

By looking at equation 3.9 we immediately see that this must be the reflection coefficient for the input side,  $\Gamma_{in}$ . Equation 3.11 is the reflection coefficient for the output side,  $\Gamma_{out}$ . Equation 3.10 and 3.12 represents respectively the forward power gain and the reverse power gain.

### 3.3 Two-port Power Gain

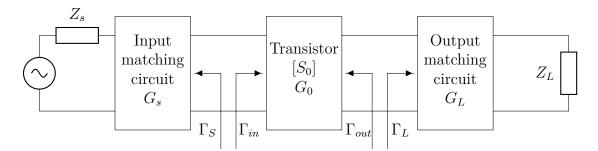

Figure 3.4 shows a general two-port amplifier with input and output matching network.

$G_S$  and  $G_L$  represents the gain due to impedance mismatches between the transistor and the source and load impedance whereas  $G_0$  is the transistor gain.

There are several definitions of power gain in a two-port system. The distinction between the different definitions are primarily in the way the input and output are matched.

The different types of gain are defined as follows:

Power Gain =

$$G = \frac{P_L}{P_{in}}$$

(3.13)

*Power gain* is the ratio of the power dissipated in the load  $Z_L$  to power delivered to the input of the two-port network. This gain is independent of  $Z_S$ . [21]

Available Gain =

$$G_A = \frac{P_{avn}}{P_{avs}}$$

(3.14)

Available gain is the ratio between the available power from the two-port network to the power available from the source. This assumes conjugate matching of both the source and the load, and depends on  $Z_S$  but not  $Z_L$ . [21]

Transducer power gain =

$$G_T = \frac{P_L}{P_{avs}}$$

(3.15)

Transducer Power Gain is the ratio of the power delivered to the load to the power available from the source. This depends on both  $Z_S$  and  $Z_L$ . [21] This dependency makes  $G_T$  a very useful gain, since it accounts for mismatches in both the source and load.

If both the input and output are conjugately matched to the two-port, the gain is maximized and  $G = G_A = G_T$ .

### **3.4** Two-port Noise Parameters

The noise performance of a two-port is usually specified by the *noise factor*, F, or the noise figure, NF, where the noise figure is simply  $10 \log(F)$  [17]. The noise factor is defined as

$$F = \frac{\text{total output noise power}}{\text{output noise due to input source}}.$$

(3.16)

The noise factor is a measure of the degradation in signal-to-noise ratio for the system and thus for a noiseless system the noise factor will be unity.

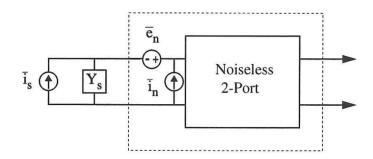

Figure 3.5 shows a noiseless two-port with a source admittance,  $Y_S$  and the corresponding noise source,  $I_S$ . The net effect of all internal noise sources can be modeled as two external noise sources,  $e_n$  and  $i_n$ . This is a huge advantage and simplifies the noise calculations significantly as long as we are only interested in the overall noise performance. This will also allow for rapid evaluation of how the source admittance affects the overall noise performance.

Figure 3.5: Two-port system with external noise sources [17].

Lee [17] describes how the noise parameters for a two-port system is derived. The noise factor for the two-port system in figure 3.5 is given by equation 3.17:

$$F = \frac{\overline{i_s^2 + |i_n + Y_S e_n|^2}}{\overline{i_s^2}}$$

(3.17)

Notice that the noise from the source admittance is not correlated with the noise from the two-port. Both sources from the two-port are however assumed correlated. This may not be the case, and to accommodate the possibility for uncorrelated noise,  $i_n$  is expressed as the sum of both correlated and uncorrelated noise:

$$i_n = i_c + i_u \tag{3.18}$$

$i_c$  is correlated with  $e_n$ , and hence  $i_c$  can be treated as proportional to  $e_n$ :

$$i_c = Y_c e_n \tag{3.19}$$

$Y_c$  is defined as the *correlation admittance* since  $\frac{i_n}{e_n}$  is an admittance.

By combining Equation 3.17, Equation 3.18 and Equation 3.19 the noise factor is expressed by the following equation:

$$F = 1 + \frac{\overline{i_u^2} + |Y_c + Y_s|^2 \overline{e_n^2}}{i_s^2}.$$

(3.20)

Equation 3.20 contains three independent noise sources. These noise sources can be treated as thermal noise produced by an equivalent resistance or conductance:

$$R_n \equiv \frac{\overline{e_n^2}}{4kT\Delta f},\tag{3.21}$$

$$G_u \equiv \frac{\overline{i_u^2}}{4kT\Delta f},\tag{3.22}$$

$$G_s \equiv \frac{i_s^2}{4kT\Delta f}.$$

(3.23)

By decomposing each admittance into both conductance, G, and susceptance, B, and by using Equation 3.21, 3.22 and 3.23, we can rewrite the noise figure equation:

$$F = 1 + \frac{G_u + \left( (G_c + G_s)^2 + (B_c + B_s)^2 \right) R_n}{G_s}.$$

(3.24)

#### **3.4.1** Optimum source admittance

Once the expression for the noise factor has been established, a determination of the general conditions for minimum noise factor is necessary. By taking the first derivative of Equation 3.24 with respect to the source admittance and setting this to zero we obtain the following expressions:

$$B_s = -B_c = B_{opt},\tag{3.25}$$

$$G_s = \sqrt{\frac{G_u}{R_n} + G_c^2} = G_{opt}.$$

(3.26)

For minimum noise factor, the source susceptance should be made equal to the negated correlation susceptance. The source conductance should also fulfill the conditions of Equation 3.26. Thus, for a low noise design great care should be taken in designing the circuit to provide  $G_{opt} = G_s$ .

Notice that minimizing noise does not necessarily give maximum power transfer and hence there will usually be a gain vs. noise trade-off. There are for example no reason to expect that the correlation susceptance is equal to the negated input source susceptance.

Choosing  $Y_s = Y_{opt}$  would result in a minimum noise factor, defined as  $F_{min}$ . The noise factor can thus be expressed in terms of  $F_{min}[21]$ :

$$F = F_{min} + \frac{R_n}{G_s} |Y_s - Y_{opt}|^2.$$

(3.27)

$R_n$  applies as a multiplier in front of the second term in Equation 3.27. For a fixed source admittance,  $R_n$  tells something about the relative sensitivity of the noise figure when deviating from the optimum noise conditions. When  $R_n$  is of large magnitude, the sensitivity gets higher and thus the noise conditions is more difficult to optimize [17].

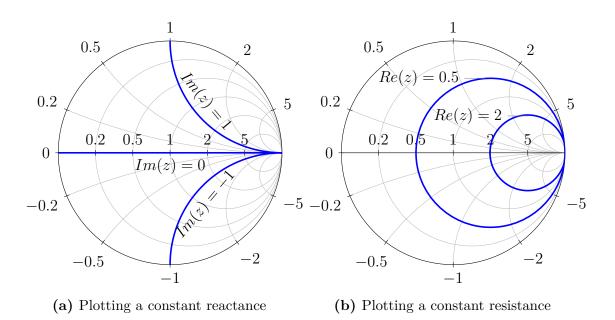

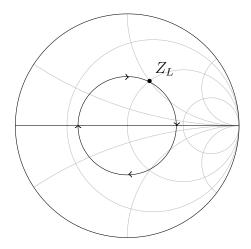

Figure 3.6: Plotting constant values

## 3.5 Smith Chart

Phillip H. Smith developed the Smith chart in the 1930s as an easy and intuitive display of the reflection coefficients as well as the line impedance in one single graph[18]. The Smith chart is essentially just a polar plot of the voltage reflection coefficient,  $\Gamma$ . The polar plot is overlayed with an impedance and/or admittance grid. The impedance/admittance is normally referenced to a normalized 1 $\Omega$  characteristic impedance.

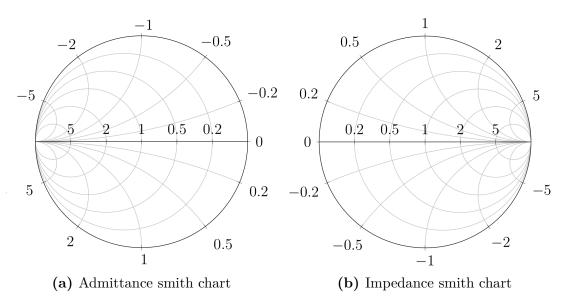

Figure 3.6 shows both the admittance and the impedance smith chart.

The Smith chart has a circumferential scale expressed in both degrees and wavelengths. The wavelength scale represents a distance along the transmission line and is used with distributed components. The degree scale represents the angle of the reflection coefficient at a specific point. The resistance and reactance is represented by values along circles (reactance) and arcs (resistance). As an example a constant resistance will transform to a circle. Similarly, a constant reactance will transform into an arc. Figure 3.7 shows an example of some constant reactances and resistances plotted.

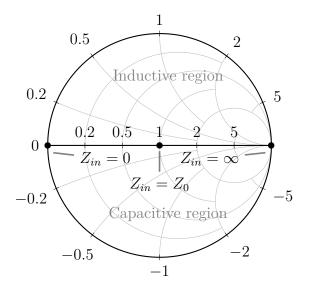

There are some properties that are worth discussing. The left and right corners of the horizontal line corresponds to respectively  $\Gamma = -1$  and  $\Gamma = 1$ . In therms of impedance, this corresponds to a short  $(Z_{in} = 0)$  or open circuit  $(Z_{in} = \infty)$ . The center point corresponds to a perfect match leading to  $|\Gamma| = 0$ . Figure 3.8 shows these locations. Further on, the top half of the diagram corresponds to the inductive region. Thus the lower half is the capacitive region.

Figure 3.7: Plotting constant values

Figure 3.8: Regions of the Smith diagram

The relationship between the reflection coefficient,  $\Gamma$ , and the input impedance (plotted impedance) is given by Equation 3.28 [16]:

$$Z_{in} = Z_0 \frac{1 + \Gamma_{in}}{1 - \Gamma_{in}} \tag{3.28}$$

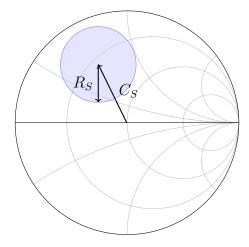

#### 3.5.1 Constant-Gain Circles

Gain circles utilizes the Smith chart to provide a graphical aid in designing an amplifier for a specific gain. This is practical in cases where one would need a specific gain or when gain is traded for improved noise figure, bandwidth etc. The design procedure is facilitated by plotting circles of constant gain in the smith chart. When a specific gain is needed for either the input section or output section ( $G_S$  or  $G_L$ ), impedance mismatches are purposely introduced by placing  $\Gamma_S$  or  $\Gamma_L$  along the circle of interest.

It can be shown that the center and radius for the input section gain circle is expressed by the following equations [21]:

$$C_S = \frac{g_S S_{11}^*}{1 - (1 - g_S)|S_{11}|^2},$$

(3.29)

$$R_S = \frac{\sqrt{1 - g_S} (1 - |S_{11}|^2)}{1 - (1 - g_S)|S_11|^2}.$$

(3.30)

Likewise, the center and radius for the output section is expressed by the following equations:

$$C_L = \frac{g_S S_{22}^*}{1 - (1 - g_L)|S_{22}|^2},$$

(3.31)

$$R_L = \frac{\sqrt{1 - g_L} (1 - |S_{22}|^2)}{1 - (1 - g_L)|S_22|^2}.$$

(3.32)

where  $g_S$  and  $g_L$  are the normalized gain factors expressed by:

$$g_S = \frac{G_S}{G_{S_{max}}} = \frac{1 - |\Gamma_S|^2}{|1 - S_{11}\Gamma_S|^2} (1 - |S_{11}|^2), \qquad (3.33)$$

$$g_L = \frac{G_L}{G_{L_{max}}} = \frac{1 - |\Gamma_L|^2}{|1 - S_{22}\Gamma_L|^2} (1 - |S_{22}|^2), \qquad (3.34)$$

Figure 3.9 shows a noise circle plotted in the smith chart. Usually one would plot several circles to get a graphical overview of the gain trade-off. Placing  $\Gamma_S$  along the circle of interest would produce a specific amount of gain whereas placing it within the circle would produce more than the specified gain.

Figure 3.9: A Smith chart with a gain circle for the input section plotted

Notice that these expressions is in the case of a unilateral device. This is normally not the case and thus the error caused by approximating  $|S_{12}| = 0$  must be assessed before evaluating the gain circles. Unilateral figure of merit is explained in Section 3.5.2.

These gain expressions are given explicitly for the input and output section and are thus not usable for assessing the available gain. Available gain circles are however often available in CAD tools.

#### 3.5.2 Unilateral Figure of Merit

The design approach for constant gain discussed in section 3.5.1 assumes that the reverse gain,  $S_{12}$ , is zero. This is usually not the case and thus the error introduced by the actual value of  $S_{12}$  must be assessed. The unilateral figure of merit provides a method for quantifying this error, and is given by Equation 3.35.

$$U = \frac{|S_{12}||S_{21}||S_{22}||S_{11}|}{(1 - |S_{11}|^2)(1 - |S_{22}|^2)}.$$

(3.35)

This figure of merit should be as small as possible in order to use the unilateral design procedure. Usually an error of a few tenths of a dB or less will justify the unilateral assumption[21].

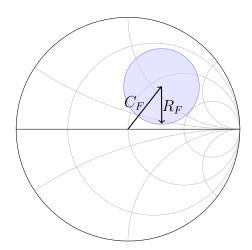

## 3.5.3 Constant-Noise Circles

As previously discussed in section 3.4.1 there is an optimum source admittance that produces a minimum amount of noise,  $F_{min}$ . This optimum source admittance can also be expressed as an optimum reflection coefficient,  $\Gamma_{opt}$  [21].

$$Y_{opt} = \frac{1}{Z_0} \frac{1 - \Gamma_{opt}}{1 + \Gamma_{opt}}.$$

(3.36)

By using this relationship together with Equation 3.27 it can be shown that it is possible to define circles of constant noise in the smith chart[21]. The center of this circle is defined as:

$$C_F = \frac{\Gamma_{opt}}{N+1},\tag{3.37}$$

where the radii is given by

$$R_F = \frac{\sqrt{N(N+1-|\Gamma_{opt}|^2)}}{N+1}.$$

(3.38)

The noise figure parameter, N, is defined by Equation 3.39:

$$N = \frac{F - F_{min}}{4\frac{R_N}{Z_0}} |1 + \Gamma_{opt}|^2.$$

(3.39)

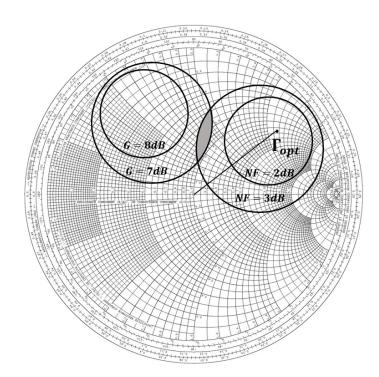

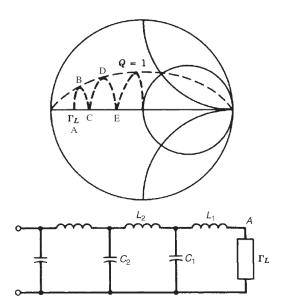

These circles can be used as a graphical aid when designing amplifiers. By using the design specifications one can plot constant noise circles for specified noise levels. To design for a specific noise level one would then place  $\Gamma_S$  along the noise circle of interest. Placing  $\Gamma_S$  within the circle of interest would produce less than the specified noise. Figure 3.10 shows a noise circle placed in the smith diagram.

The biggest advantage of using noise circles are when they are used in conjunction with gain circles. The gain vs. noise trade-off is then easily assessed by placing  $\Gamma_S$  within the circles of interest. By moving the reflection coefficient towards the center of the noise circles one can achieve lower noise. The same applies for gain, where one can move the reflection coefficient towards the center of the gain circle to achieve higher gain.

Figure 3.11 shows a smith chart with both noise and gain circles plotted. In order to achieve a gain of 7dB as well as a noise figure of 2dB,  $\Gamma_s$  must be placed within both these circles. This area is shaded with grey. By moving  $\Gamma_s$  to the left or right, one can achieve respectively more gain or less noise. Figure 3.11 also shows that  $\Gamma_{opt}$  would obtain minimum noise figure. The center of all noise circles are located on a straight line from the center of the smith chart towards  $\Gamma_{opt}$ . This also applies for the gain circles where the centers of all circles are placed a long a straight line towards  $S_{11}^*$

Figure 3.10: A Smith chart with a noise circle plotted

Figure 3.11: Smith chart with both noise and gain circles plotted

# 3.6 Impedance Matching

The maximum power transfer theorem states that, to obtain maximum external power from a source with a finite internal resistance, the resistance of the load must equal the resistance of the source as viewed from its output terminals. This means that the load resistance should *match* the source resistance. The theorem can also be extended to include circuits with reactive source impedance. It then states that the maximum power transfer occurs when the load impedance is equal to the complex conjugate of the source impedance[1].

$$Z_{in} = Z_S^*.$$

(3.40)

In terms of reflection coefficient this transforms to [21]:

$$\Gamma_{in} = \Gamma_S^*. \tag{3.41}$$

In practice when matching for  $50\Omega$ , this will make the source reactance resonate with the input reactance and thus make the terminations purely resistive and equal.

The impedance matching network is usually designed so that the impedance seen looking in to the matching network is  $Z_0$ , the characteristic impedance of the transmission line. This will eliminate the reflections between the matching network and the source, as previously discussed in section 3.1.2. In multistage designs where interfacing with 50 $\Omega$  elements is not necessary, the matching impedance may differ from 50 $\Omega$  as this makes the matching more easily achieved.

The matching networks can be implemented as both lumped or distributed elements. A common design strategy is to design the circuit using lumped elements and then if needed switch to a distributed element later in the design process. Whether or not this is needed depends on the frequencies of interest and the process specifications. Both methods are commonly used in Monolithic Microwave Integrated Circuit (MMIC) design.

Vendelin [27] does however point out that this equivalence between lumped and distributed elements are not recommended since the movements on the Smith Chart is somewhat different. Redesigning for distributed elements could then prove to be a time consuming process.

## 3.6.1 Matching with lumped elements using the Smith Chart

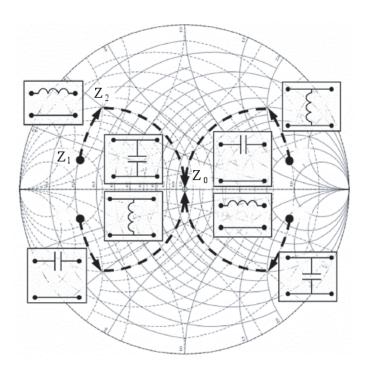

The matching network can easily ble implemented using both the impedance and admittance Smith Chart. By plotting the normalized impedance, one can simply navigate from this impedance to origo (perfect match) using a combination of the circles of constant resistance and conductance.

Figure 3.12: Using the Smith Chart for impedance matching. [16]

In general, placing a series element in the matching circuit will transform the impedance along the circles of constant resistance in the impedance chart. Placing a shunt element will transform the impedance along the circles of constant conductance in the admittance chart. A capacitor will shift the impedance towards the capacitive region whereas a inductor will shift the impedance towards the inductive region.

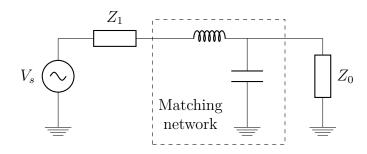

Figure 3.12 shows the different movements possible together with the corresponding lumped element required, and demonstrates four different matching situations. Starting with a load impedance,  $Z_1$ , it is possible to transform the impedance to a new impedance,  $Z_2$ , by using a series inductor. The impedance has now followed the circle of constant resistance in clockwise direction (towards inductive region). Stopping at  $Z_2$  ensures that one can use a shunt capacitor in order to move along the circle of constant conductance towards  $Z_0$ . The load is now matched to  $Z_0$ . Figure 3.13 shows the matching network implemented between the source- and load impedance for this example.

The distance of the impedance shift equals the reactance of the required component and thus two simple design equations is used to calculate the value of the component:

$$C = \frac{1}{\omega Z_0 X_C},\tag{3.42}$$

$$L = \frac{Z_0 X_L}{\omega},\tag{3.43}$$

Figure 3.13: Matching network implemented between source and load.

where  $Z_0$  is the characteristic impedance.

Note that these equations are for use with the impedance grid. For use with the admittance grid  $X_{L/C}$  must be replaced with the susceptance  $B_{L/C} = \frac{1}{X_{L/C}}$ .

Another important consideration in impedance matching using the Smith chart is that high frequencies travels *faster* in the Smith chart, making the impedance match more narrow if the distance is large. It is therefore always good practice to choose the shortest distance when selecting devices for matching.

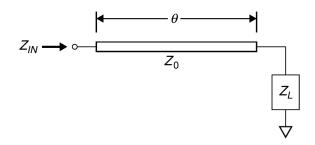

### 3.6.2 Transmission Line Impedance Transformation

One important property of a transmission line is that it has the ability to transform an impedance,  $Z_L$ , into a new input impedance,  $Z_{in}$ , by using a length of transmission line in series with the load. Figure 3.14 shows the equivalent circuit for this setup.

The length of the transmission line is given by the *electrical length*  $\theta$ :

$$\theta = \frac{l}{\lambda} 360^{\circ}, \tag{3.44}$$

where l is the length of the transmission line.

Equation 3.45 describes the input impedance of the equivalent circuit in Figure 3.14 [28]:

$$Z_{in} = Z_0 \frac{Z_L + jZ_0 \tan(\theta)}{Z_0 + jZ_L \tan(\theta)}$$

(3.45)

Note that this equation assumes lossless transmission line. Equation 3.46 shows the relationship when losses are present [28]:

$$Z_{in} = Z_0 \frac{Z_L + Z_0 \tanh(\gamma l)}{Z_0 + Z_L \tanh(\gamma l)}$$

(3.46)

There are some special cases that are worth discussing:

Figure 3.14: Equivalent circuit model for a transmission line,  $Z_0$ , in series with a load,  $Z_L$  [28].

- When a transmission line of zero length or a multiple of  $\frac{\lambda}{2}$  is connected to the load, the load is not transformed and thus  $Z_{in} = Z_L$ .

- An open-circuit terminated transmission line is purely capacitive when  $\theta < 90^{\circ}$ , becomes a short-circuit when  $\theta = 90^{\circ}$ , and is inductive when  $90^{\circ} < \theta < 180^{\circ}$ . This behavior repeats every half wavelength. In this special case, Equation 3.45 is simplified to the following expression:

$$Z_{in} = -jZ_0 \cot(\theta) \tag{3.47}$$

The behavior will be similar for a short-circuit terminated transmission line, but the phase is then shifted  $90^{\circ}$ , making it inductive up to  $90^{\circ}$ , and capacitive from  $90^{\circ}$  to  $180^{\circ}$ . Equation 3.48 shows the impedance relationship for the short-circuit terminated transmission line:

$$Z_{in} = jZ_0 \tan(\theta) \tag{3.48}$$

#### 3.6.3 Single Element Matching

Transmission line matching/impedance transformation is easily adapted with use of the Smith Chart. Given that the transmission line impedance is  $50\Omega$ , the movements are always along the constant voltage standing wave ratio (VSWR) circle as showed in Figure 3.15. The length of the transmission line is determined by using the wavelength scale on the Smith chart. A full rotation in the Smith Diagram corresponds to a electrical length of  $180^{\circ}$ .

If the characteristic impedance is different than 50  $\Omega$ , the center of the circular motion will be shifted.  $Z_0 < 50 \ \Omega$  will shift the circle towards 0  $\Omega$  while  $Z_0 >$ 50  $\Omega$  will shift the circle towards  $\infty \ \Omega$ . This property is exploited when the load impedance is located within the 1 + jX/B circles and makes it possible to match the load impedance using only a single transmission line. Vendelin [27] explains a manual procedure using the Smith Chart. Utilizing this matching by hand is a tedious operation and it is therefore more convenient to use CAD tools for this

Figure 3.15: A transmission line with  $50\Omega$  impedance will exhibit a circular motion movement around the origo of the Smith Chart.

operation. The transmission line can then easily be tuned in order to achieve perfect match.

## 3.6.4 Single-stub Matching

As previously discussed in 3.6.2, a shorted or open transmission line will exhibit a purely inductive or capacitive response. If a transmission line is connected in parallel and left open or shorted it is called a *stub*. This stub can be utilized to cancel out any reactive impedance.

Since the stub is connected in parallel and acts purely reactive, the movement in the Smith chart follows the constant circles of conductance. A short-terminated stub will always start at 0+j0 while a open-terminated stub will always start where the load is located. This is also analog to the previously mentioned 90° phase shift between the shorted and open stub. Increasing the length of the stub will move the impedance in a circular motion in clockwise direction. The initial matching conditions will therefore determine whether to use a shorted or open stub. As previously discussed in section 3.6.1 choosing a short matching path will provide higher bandwidth.

## 3.6.5 Two-element Matching

Even though matching is possible using only one element, most of the cases requires the use of two elements. This is achieved by combining a transmission line with a parallel stub. The matching procedure is as follows:

1. Plot the load in the Smith chart. Place a transmission line of 50  $\Omega$  between

the load and the input.  $50\Omega$  is used in order to rotate the impedance in a circular motion with origo of the Smith chart as center.

- 2. In the Smith chart, rotate the load in clockwise direction as previously showed in Figure 3.15. The rotation should stop as the impedance intersects the 1+jBcircle of constant conductance.

- 3. The length of the transmission line is then determined by reading the wavelengths toward generator scale on the Smith chart. The length of the transmission line is then given by:  $l = (\lambda_{end} - \lambda_{start}) \times \lambda$

- 4. Use a stub with 50  $\Omega$  impedance to cancel out the reactive part of the load impedance. The impedance will then move along the constant circle of admittance in clockwise direction. The length of the stub is determined by reading the susceptance where the load is located and then read the *wavelength toward* generator scale. Use the equation given in step 3 to calculate the length of the stub. Choose the appropriate termination of the stub based on the initial location in the Smith chart.

Using this procedure with a  $Z_0 \neq 50 \ \Omega$  transmission line is also possible, but keep in mind that the center of the circular motion is then shifted away from the center of the Smith Chart.

#### 3.6.6 Considerations With Lossy Transmission Lines

The previous matching methods with transmission lines and stubs assumes lossless elements. When designing a real transmission line there are losses present and thus ideal behavior is not the case. In addition to this there will be parasitic capacitance and inductance as well as coupling to surrounding structures. This will cause the movements in the Smith chart to be somewhat different. These movements are difficult to anticipate and thus CAD tools are used in order to match using transmission lines.

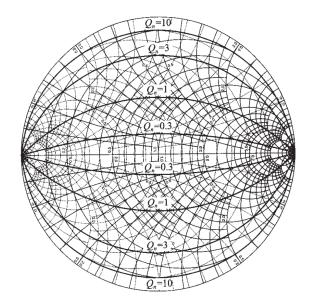

## 3.6.7 Smith Chart Q-Contours

An important consideration in filter design and impedance matching is the quality factor. The quality factor is a quantitative measure of the bandwidth relative to the center frequency. A high Q-value corresponds to a narrow bandwidth and vice versa. The smith chart with constant Q-contours is a useful aid in designing a matching network with a specific Q-value. Figure 3.16 shows a smith chart with these Qcontours. By keeping the impedance transformations within the desired Q-contour one can achieve a specific Q-value. In general it is apparent that one could achieve

Figure 3.16: Contours of constant Q in smith chart [18]

lower Q-values and thus higher bandwidth by constraining the movements in the smith chart within a small area close to the  $I_m = 0$  line. The disadvantage of this is that one must often use additional components to achieve this, increasing the area and complexity. Figure 3.17 shows how one could achieve a q-factor of 1 when the impedance is originally located far from the center of the smith chart.

Figure 3.17: Matching for a q-factor of 1 [27]

# CHAPTER 4

# Low Noise Amplifier Design Methodology

The LNA is the first stage after the antenna and it must handle very small signal amplitudes. In addition to this, the amplifier must have little contribution to the overall noise figure. This chapter will go through some of the theory needed for the design of a LNA.

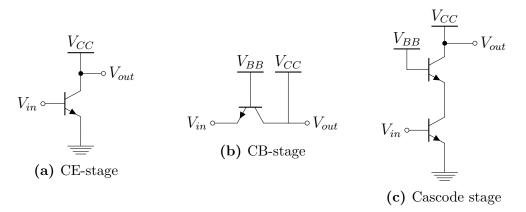

## 4.1 Topologies

There are three prevailing topologies that are used in LNA designs. These are the common-emitter (CE), common-base (CB) and cascode topology shown in Figure 4.1. A comparison of some of the most important parameters in these topologies are shown in Table 4.1 [7].

Figure 4.1: The three prevailing LNA topologies

| Characteristic           | Common Emitter              | Common Base                  | Cascode                 |

|--------------------------|-----------------------------|------------------------------|-------------------------|

| Noise Figure             | Lowest                      | Rises rapidly with frequency | Slightly higher than CE |

| Gain                     | Moderate                    | Lowest                       | Highest                 |

| Linearity                | Moderate                    | High                         | Potentially Highest     |

| $f_{-3\mathrm{dB}}$      | Low                         | Fairly high                  | High                    |

| Stability                | Often requires compensation | Higher                       | Higher                  |

| <b>Reverse Isolation</b> | Low                         | High                         | High                    |

| <b>PVT Sensitivity</b>   | Greater                     | Lesser                       | Lesser                  |

Table 4.1: Comparison of commonly used topologies

[7]

The cascode amplifier is doing quite well on all parameters except for the noise figure which is slightly higher than for the CE-stage. The cascode stage does, however, add some complexity to the circuit since it needs higher supply voltage in addition to an extra bias voltage for the cascode transistor. The high supply voltage also results in a higher power consumption for the same bias conditions.

The common-gate amplifier has good reverse isolation and good linearity but has lower gain and more noise compared to the CE-stage. One additional advantage is that one could easily achieve 50  $\Omega$  match by manipulating the transconductance of the transistor, based on the fact that the input impedance of a common-base amplifier is  $\approx \frac{1}{gm}$ . The low gain and high noise does, however, make the commonbase amplifier less suitable for a LNA design.

The common-emitter stage has the lowest noise of all three topologies and moderate gain and linearity.

As several stages are most likely needed, it will probably be beneficial to combine several topologies. The CE-stage does a very good job as an input stage based on the low noise and moderate gain. The cascode stage would make a good output stage based on the high reverse isolation and high gain.

## 4.2 Noise

Noise is one of the most important parameters in a system, and thus great care should be taken in analyzing the noise performance of the amplifier. As previously discussed in Section 3.4, NF is a important measure of the overall noise contribution of the amplifier. Keeping this figure low is of great importance.

#### 4.2.1 Noise Sources in Bipolar Transistor

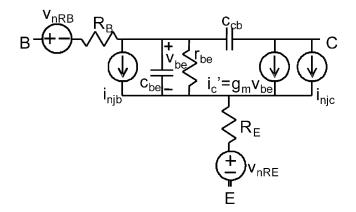

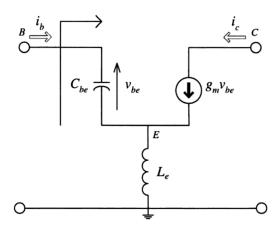

An HBT contains several intrinsic noise sources. Figure 4.2 shows a simplified bipolar transistor small signal model with the dominating noise sources.

Figure 4.2: Small signal schematic of bipolar transistor with dominating noise sources [24]

The noise sources are as follows:

- **Collector current shot noise**  $i_{njc}$  is the collector current shot noise given by the following expression:  $i_{njc} = 2qI_c\Delta f$ . This noise is caused by electron movements from the emitter to the base and the statistical distribution of different energy and direction of the crossing of the PN-junction.

- **Base current shot noise**  $i_{njb}$  is the base current shot noise given by the following expression:  $i_{njb} = 2qI_B\Delta f$ . This noise source origins from holes moving towards the emitter. The base current shot noise and collector current shot noise is typically uncorrelated for a modern HBT.

- **Thermal noise** Uncorrelated thermal noise is also present due to the parasitic resistance in the base and emitter. The expressions for the base and emitter thermal noise is  $v_{nRB} = 4KTR_B\Delta f$  and  $v_{nRE} = 4KTR_E\Delta f$ .

#### 4.2.2 Minimum Noise Figure

In order to evaluate the noise figure of the amplifier the term  $F_{min}$  is used. This is the minimum achievable noise figure for a given topology and configuration.

The minimum noise figure for a SiGe HBT is given by equation 4.1 [24]:

$$F_{min} \cong 1 + \frac{n}{\beta} + \sqrt{\frac{2I_C}{V_T}(R_B + R_E)\left(\frac{f^2}{f_T^2} + \frac{1}{\beta}\right) + \frac{n^2}{\beta}}$$

(4.1)

where  $V_T = kT/q$ ,  $R_B$  is the base resistance,  $R_E$  is the emitter resistance and n is the  $I_C$  ideality factor.

This expression can be simplified since  $\beta$  typically is larger than 100, n is very close to 1 and  $R_B$  is much larger than  $R_E$ . This gives the following expression:

$$F_{min} \cong 1 + \sqrt{\frac{2I_C}{V_T}(R_B) \left(\frac{f^2}{f_T^2} + \frac{1}{\beta}\right)}$$

$$(4.2)$$

## 4.2.3 Noise Matching

Scaling of the transistor is primarily done to achieve noise matching through choosing the optimum source admittance. This was previously discussed in Section 3.4.1.

For a given bias, Equation 4.2 suggests that reducing  $R_B$  would yield better noise performance. This can be achieved by increasing the base area.

The optimum source resistance for low noise operation is given by equation 4.3 [25]:

$$R_{s,opt} = \frac{f_T}{f} \frac{1}{\sqrt{L_E}} \sqrt{\frac{2R_B}{J_C W_E}} \frac{kT}{qI_C}$$

(4.3)

If the current density is given by choosing a specific bias point, equation 4.3 suggests that the  $R_{s,opt}$  could be matched by changing the emitter width or emitter length. For optimal noise performance, the  $R_{s,opt}$  should be sized to 50  $\Omega$  which is the source impedance of the antenna.

Note that as previously discussed in section 3.4.1, the correlation susceptance will also have an impact on the noise matching of the device. Thus using the Smith chart with noise circles or the optimum reflection coefficient will give more insight in the noise matching of the device.

#### 4.2.4 Noise in Casaded Stages

The total noise figure for n cascaded stages is given by equation 4.4 [1]:

$$F_{tot} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{G_1 G_2 \dots G_{n-1}} + \dots$$

(4.4)

As seen by the expression, the noise from the subsequent stages have less impact on the total noise figure due to the gain from the previous stages. The gain of the first stage will therefore "suppress" the noise from the subsequent stages relative to the signal. Given that the gain in the first stage is adequate, the first stage will dominate the noise figure of the system.

## 4.3 Stability

An important consideration in amplifier design is whether the amplifier is stable at all frequencies of interest. Figure 3.4 shows the general two-port amplifier. Oscillation in this amplifier is possible if the input or output port impedance has a negative real part, causing the reflection coefficients to be larger than unity. Reflections can then sum with the input signal and cause uncontrollable oscillations. Since  $|\Gamma_{in}|$ and  $|\Gamma_{out}|$  are directly related to  $|\Gamma_S|$  and  $|\Gamma_L|$  this means that the stability of the amplifier is dependent on the input and output matching. Two types of stability can be defined [21]:

- Unconditional stability: The network is unconditionally stable if  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  for all passive source and load impedances.

- Conditional stability: The network is conditionally stable if  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  only for a certain range of passive source and load impedances. This case is also referred to as *potentially unstable*.

## 4.3.1 Single Stage Stability

In order to determine if the amplifier is unconditionally stable there are two criteria that one must satisfy. This is known as *Rollet's condition* and is defined by the following two conditions[21]:

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{11}S_{22}|} > 1,$$

(4.5)

$$|\Delta| = |S_{11}S_{22} - S_{12}S_{21}| < 1.$$

(4.6)

If both these expressions are satisfied, the device will be unconditionally stable. This test is also known as the K- $\Delta$ -test.

Not all CAD tools provide  $\Delta$  as a simulation parameter. Thus, a second auxiliary parameter B1 is defined:

$$B1 = 1 + |S_{11}|^2 - |S_{22}|^2 - |\Delta|^2$$

(4.7)

The necessary condition for unconditionally stability is then: K > 1 and B > 0.

If the s-parameters do not satisfy these conditions, *stability circles* in the Smith chart or other methods must be used to determine if the amplifier is stable.

**Figure 4.3:** Two networks connected and described using signal flow chart modeling. [14]

### 4.3.2 Multistage Stability

The k-factor stability criteria is only valid for a single stage amplifier. Designing a multistage amplifier requires more advanced methods for determining stability since there could be internal oscillations that are not accounted for when looking at  $S_{11}$  and  $S_{22}$ .

One approach in making the multistage amplifier stable is to design each stage for unconditionally stability. This may prove to work, but feedback between the amplifier stages may cause oscillations. Although there will normally not be any feedback between the stages, unintentional feedback may occur through the bias networks. Another drawback with this method is that performance must be traded when making the amplifier unconditional stable.

Stability evaluation using *Gamma probes* provides a very good solution for evaluating the internal stability. Using this method may provide better performance as well as satisfactory margin for stability. [14] This method is based on the fact that one can represent the connection between two networks as a signal flow chart model shown in Figure 4.3.

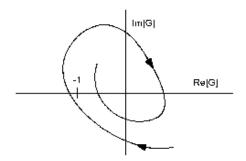

Figure 4.3 shows two networks connected and represented by signal flow chart modeling. This modeling allows use of the Nyquist stability criterion which is often used to determine stability in control systems. The stability is now evaluated by looking at the loop in the signal flow chart as feedback loop. The open loop frequency domain response is then given by Equation 4.8:

$$G = -\Gamma_1 \Gamma_2 \tag{4.8}$$

$\Gamma_1$  and  $\Gamma_2$  represent the reflection coefficients of the gamma probe.

Figure 4.4: G plotted in polar plot showing instability. [14]

In order to evaluate stability, G is plotted in a polar plot. The Nyquist stability criteria states that if the open loop function G, when plotted in a polar plot as a function of frequency, encircles the -1 point in the clockwise direction, then the closed loop system will be unstable [14]. Figure 4.4 shows G plotted for an unstable system where the -1 point on the real axis is encircled in clockwise direction.

By inserting gamma probes within the circuit and plotting G, it is now possible to evaluate the internal nodes for stability. The gamma probes are placed in series with the input or output of active devices where the stability is to be evaluated. The element is completely transparent to the circuit and thus normal simulations can be applied with these probes inserted.

## 4.4 Non-linearity

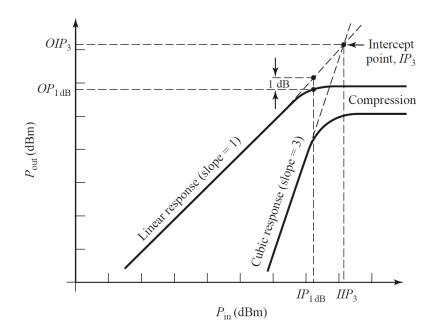

One of the important properties of an amplifier is the linearity. Even though a transistor can be made fairly linear for small input signals, it will exhibit non-linear response for large input signals.

It can be shown that for a general non-linear system, the output can be modeled as a taylor series given by Equation 4.9

$$v_o = a_0 + a_1 v_i + a_2 v_i^2 + a_3 v_i^3 + \dots$$

(4.9)

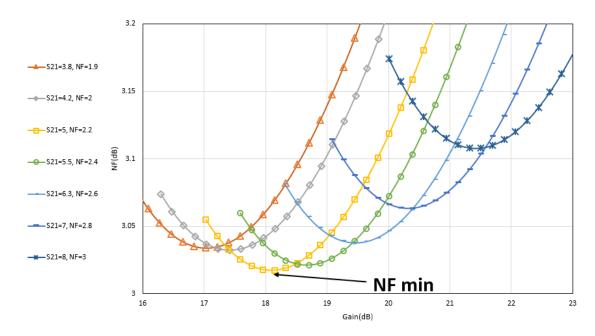

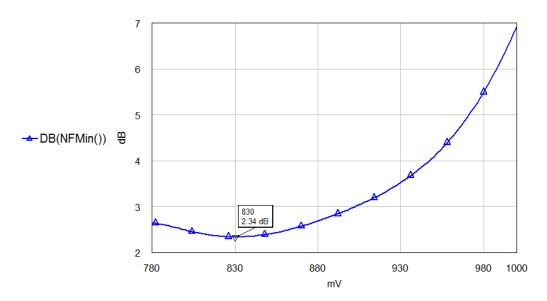

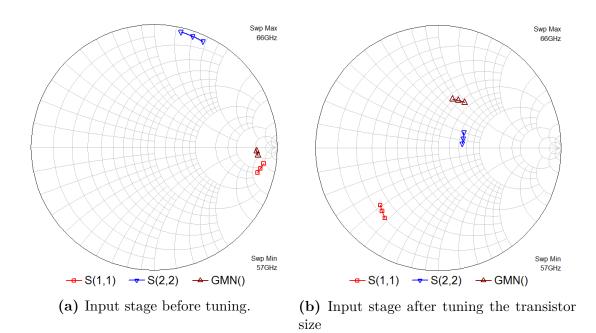

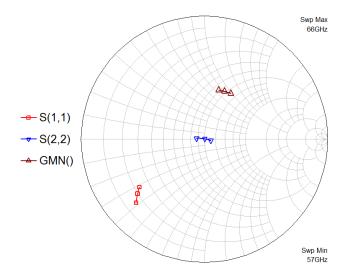

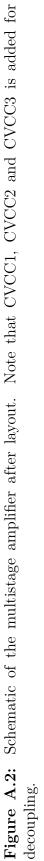

If the second- or higher order coefficients are of large magnitude, the resulting output will be nonlinear. Thus, for a linear system, these coefficients should be zero.