# UNIVERSITY OF BERGEN

# **GEOPHYSICAL INSTITUTE**

Master Thesis in Energy Specialization in Energy Technology Electrical Power engineering

# Design of rectifier system for electric ferries

By: Andreas Sagedal

June 1, 2018

#### Abstract

This study investigates the requirements and technologies to provide power from shore to ship when the electric ferry is at quay. Different rectifier systems will be evaluated in terms of requirements given by the utility grid owner BKK and the ferry company Fjord1. Two suitable rectifier systems based on voltage orientated control method will be simulated in Simulink under various load conditions. The simulation results will be evaluated with the grid parameters and requirements given by BKK. Important parameters to be considered are power factor, efficiency, harmonic distortion of current and voltage at the point of common coupling and stability of the rectifier. The voltage orientated rectifier system with L-filter is built in the laboratory where the goal is to validate the simulation results. The hardware design is based on insulated gate bipolar transistors from SEMIKRON and digital signal controller eZdsp delivered by spectrum digital.

# Acknowledgement

This master thesis in Electrical Power Engineering marks the end of a six year long education and marks the starting point of my career at Siemens. I am grateful for the collaboration between The Western Norway University of Applied Science and Siemens for giving me both a deep insight in power electronics theory and practical applications used in the industry.

I wish to express my sincere gratitude towards my supervisor, Associate Professor Shujun Zhang for his knowledge, understanding and patience. In addition he has been a great contributor in my first academic paper publication, which gave me the opportunity to attend the 21st International Conference on Electrical Machines and systems in Jeju, Korea.

Senior Engineer Lars Manger Ekroll deserves a big thanks for supporting me with practical ideas and purchase of equipment for my laboratory model.

A special thanks to my supervisors at Siemens: Senior Engineer Øystein Eik, Tor Martin Iversen and Group Manager Bendic Aronsen, for guidance, feedback and support.

Finally, I would like to thank my fellow master students for making these last two years a great experience.

# **Table of Contents**

| Li | st of ] | Figures       |                                          | v    |

|----|---------|---------------|------------------------------------------|------|

| Li | st of [ | <b>Fables</b> |                                          | viii |

| 1  | Intr    | oducti        | on                                       | 1    |

|    | 1.1     | Backg         | round                                    | 1    |

|    | 1.2     | Objec         | t of thesis                              | 3    |

|    | 1.3     | Struct        | rure of thesis                           | 3    |

| 2  | Sho     | re Con        | nection Systems                          | 5    |

|    | 2.1     | Differ        | ent topologies                           | 6    |

|    |         | 2.1.1         | High voltage shore connection            | 6    |

|    |         | 2.1.2         | Low voltage shore connection             | 9    |

| 3  | Rec     | tifier sy     | <b>/stems</b>                            | 11   |

|    | 3.1     | Nonsi         | nusoidal waveform in steady state        | 11   |

|    | 3.2     | Rectif        | ìers                                     | 15   |

|    |         | 3.2.1         | Diode rectifier                          | 15   |

|    |         | 3.2.2         | Thyristor rectifier                      | 19   |

|    |         | 3.2.3         | Active Front End rectifier               | 22   |

|    |         | 3.2.4         | Choosing the rectifier topology          | 25   |

|    | 3.3     | Contr         | ol of rectifiers                         | 25   |

|    |         | 3.3.1         | Clarke and Park transformation           | 27   |

|    |         | 3.3.2         | Space vector modulation                  | 31   |

| 4  | Des     | ign of t      | he onboard rectifier system              | 36   |

|    | 4.1     | Voltag        | ge orientated control                    | 36   |

|    |         |               | L-filter design                          | 41   |

|    | 4.2     |               | ge orientated control with LCL-filter    | 42   |

|    |         | 4.2.1         | LCL-filter design                        | 45   |

|    | 4.3     | Addit         | ional parameters                         | 48   |

| 5  | Sim     | ulatior       | n and grid calculation                   | 49   |

|    | 5.1     | VOC A         | AFE rectifier                            | 49   |

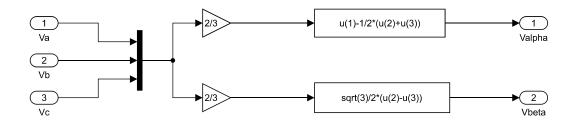

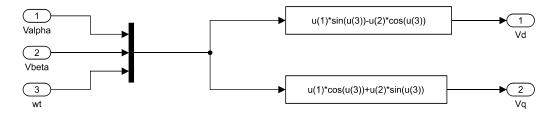

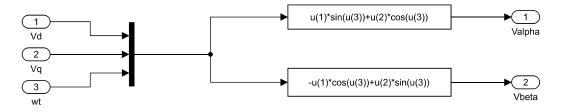

|    |         | 5.1.1         | Clarke and Park transformation subsystem | 51   |

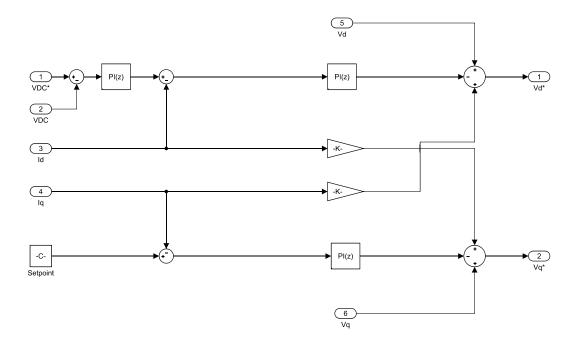

|    |         | 5.1.2         | Controller circuit subsystem             | 52   |

|    |         | 5.1.3         | SVPWM subsystem                          | 54   |

|    |         | 5.1.4         | Power factor subsystem                   | 58   |

|    |         | 5.1.5         | Results                                  | 60   |

|    |                                      | 5.1.6 Grid calculations                  | 66  |  |  |

|----|--------------------------------------|------------------------------------------|-----|--|--|

|    | 5.2                                  | VOC AFE rectifier with LCL-filter        | 72  |  |  |

|    |                                      | 5.2.1 Results                            | 73  |  |  |

|    |                                      | 5.2.2 Grid calculations                  | 79  |  |  |

| 6  | Lah                                  | oratory model                            | 83  |  |  |

| Ū  | 6.1                                  | IGBT loss calculation and cooling demand | 84  |  |  |

|    | 6.2                                  | IGBT driver card                         | 91  |  |  |

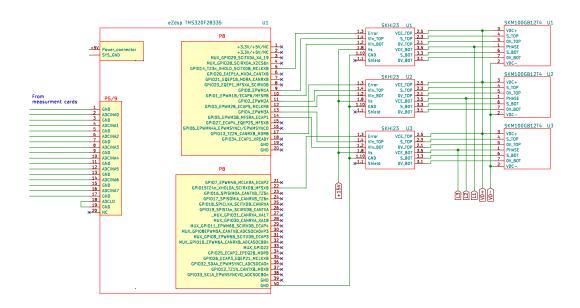

|    | 6.3                                  | DSC card                                 | 93  |  |  |

|    | 6.4                                  | Measurement cards                        | 96  |  |  |

|    |                                      | 6.4.1 Line voltages                      | 98  |  |  |

|    |                                      | 6.4.2 Line currents                      | 100 |  |  |

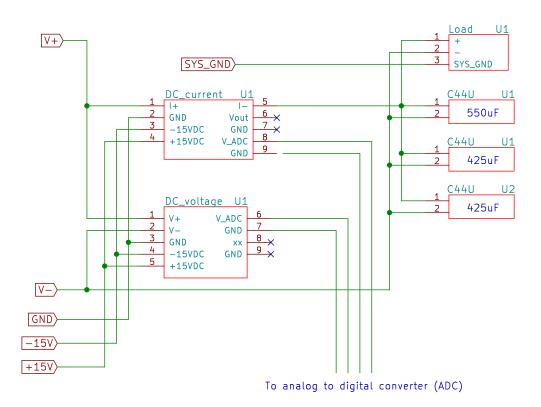

|    |                                      | 6.4.3 DC voltage and current 1           | 102 |  |  |

|    | 6.5                                  | Wiring diagram                           | 103 |  |  |

|    | 6.6                                  | Programming 1                            | 105 |  |  |

|    | 6.7                                  | Results                                  | 107 |  |  |

| 7  | Disc                                 | cussion 1                                | 11  |  |  |

|    |                                      |                                          |     |  |  |

| 8  | Con                                  | clusion 1                                | 14  |  |  |

| Bi | bliog                                | raphy 1                                  | 16  |  |  |

| Ap | penc                                 | lices 1                                  | 19  |  |  |

| A  | Clar                                 | ke and Park transformation 1             | 19  |  |  |

| B  | Power calculations 123               |                                          |     |  |  |

| С  | Filter loss calculation125           |                                          |     |  |  |

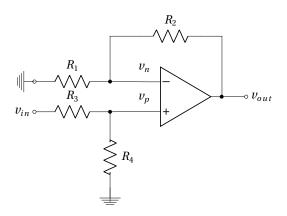

| D  | Operational amplifier derivation 126 |                                          |     |  |  |

# List of Figures

| 1  | Main switchboard with DC busbar on board electric ferries $\ldots \ldots$ | 6  |

|----|---------------------------------------------------------------------------|----|

| 2  | Generic block diagram for HVSC system                                     | 7  |

| 3  | Generic block diagram for LVSC system                                     | 9  |

| 4  | Example of a harmonic waveform                                            | 11 |

| 5  | Example of a distorted current with its decomposed values                 | 13 |

| 6  | Interface between the utility grid and the ferry charger                  | 14 |

| 7  | Three-phase full bridge diode rectifier                                   | 16 |

| 8  | Waveform for the three-phase full bridge diode rectifier                  | 17 |

| 9  | Three-phase full bridge thyristor rectifier                               | 19 |

| 10 | Waveform for the three-phase full bridge thyristor rectifier              | 20 |

| 11 | Three-phase Active Front End rectifier                                    | 23 |

| 12 | Phasor diagrams for the AFE rectifer                                      | 24 |

| 13 | Waveform of CB-PWM                                                        | 26 |

| 14 | Phasor diagram for the Park and Clarke voltages                           | 28 |

| 15 | Waveform for the three-phase voltages and the Clarke and Park volt-       |    |

|    | ages                                                                      | 30 |

| 16 | Space vector representation                                               | 31 |

| 17 | Decomposed space vector in sector I                                       | 33 |

| 18 | Pulse pattern for the space vector in sector I                            | 34 |

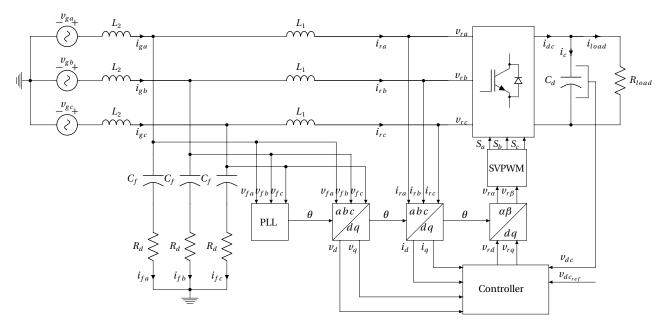

| 19 | Configuration of the VOC AFE rectifier with L-filter                      | 37 |

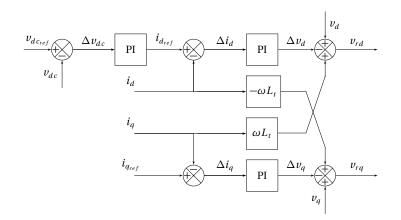

| 20 | Synchronous controller for the VOC AFE rectifier                          | 39 |

| 21 | Phasor diagram for the VOC AFE rectifier                                  | 40 |

| 22 | Phase diagram for the VOC AFE rectifier                                   | 42 |

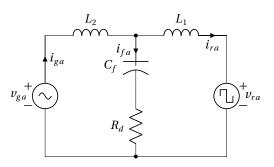

| 23 | Configuration of the VOC AFE rectifier with LCL-filter                    | 43 |

| 24 | Synchronous controller for the VOC AFE rectifier with LCL-filter          | 44 |

| 25 | Phase diagram for the VOC AFE rectifier with LCL-filter                   | 47 |

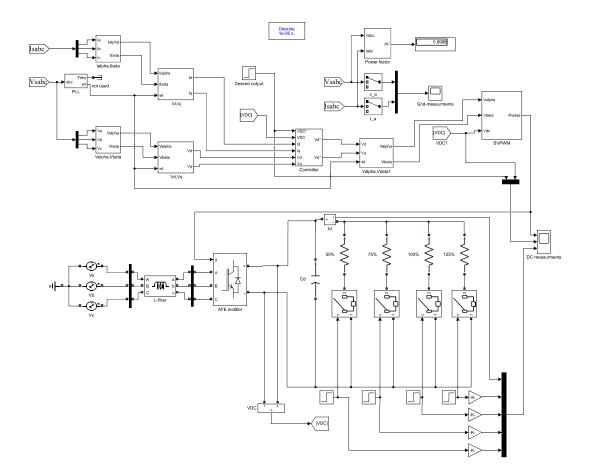

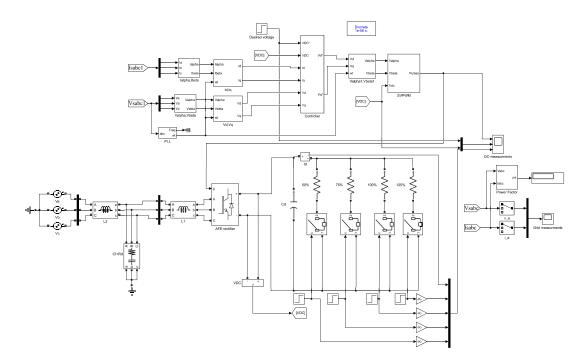

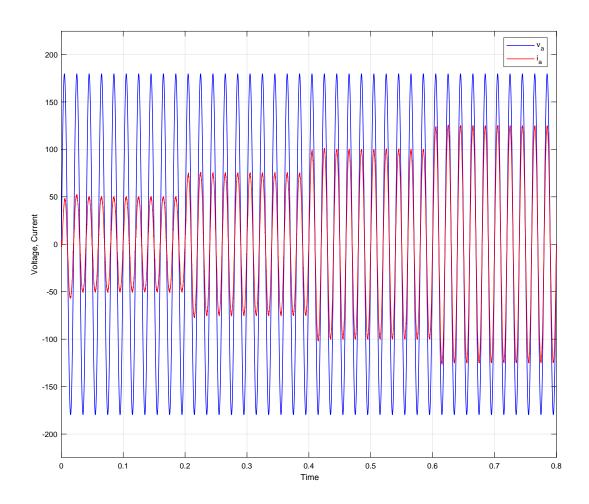

| 26 | Simulation scheme for the VOC AFE rectifier in Simulink                   | 50 |

| 27 | Subsystem for the Park and Clarke transform                               | 51 |

| 28 | Subsystem for the synchronous controller                                  | 53 |

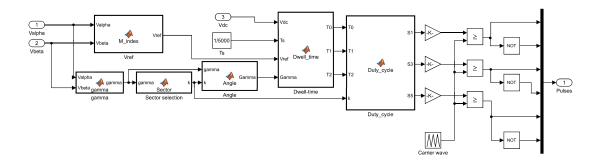

| 29 | Subsystem for the SVPWM block                                             | 54 |

| 30 | Subsystem for the calculation of the space vector                         | 54 |

| 31 | Subsystem for the sector selection                                        | 55 |

| 32 | Subsystem for the calculation of the angle for the space vector           | 56 |

| 33 | Dwell time calculation for the active and zero vectors                    | 56 |

| 34 | Subsystem for the calculation of the switching time to the IGBTs          | 57 |

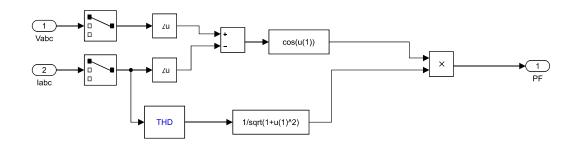

| 36 | Subsystem for the PF calculation                                          | 58 |

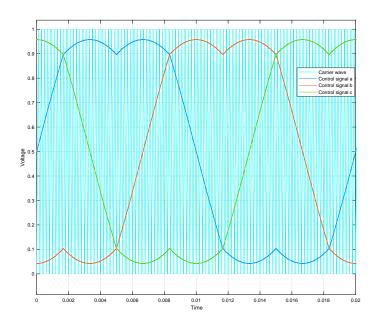

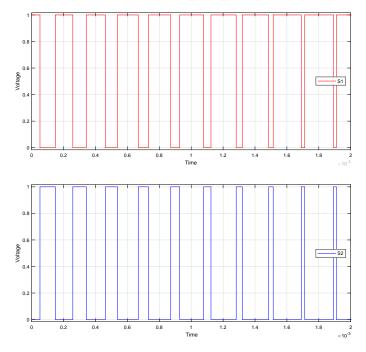

| 35 | Example waveform of generated switching signals to the IGBTs            | 59  |

|----|-------------------------------------------------------------------------|-----|

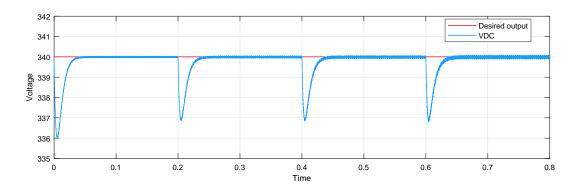

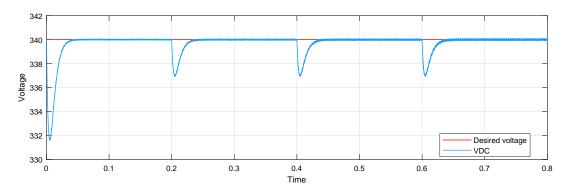

| 37 | Simulated dc voltage and current for the VOC AFE rectifer               | 61  |

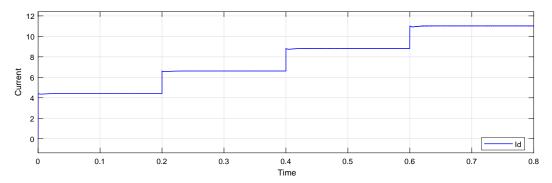

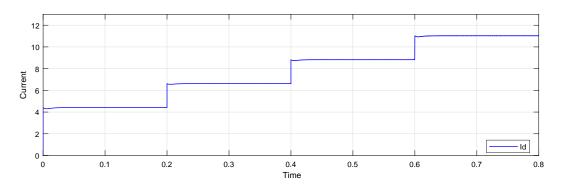

| 38 | Simulated grid voltage and current for the VOC AFE rectifier            | 62  |

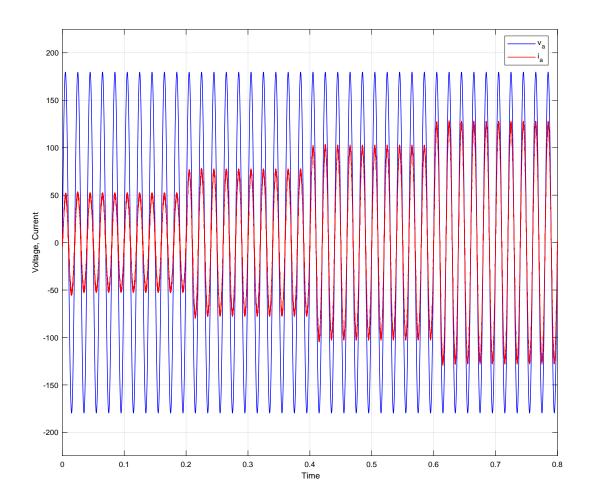

| 39 | Bode plot for the VOC AFE rectifier                                     | 63  |

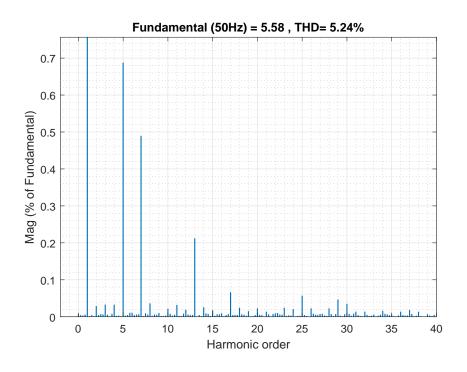

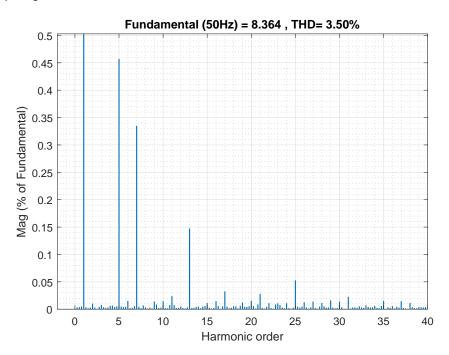

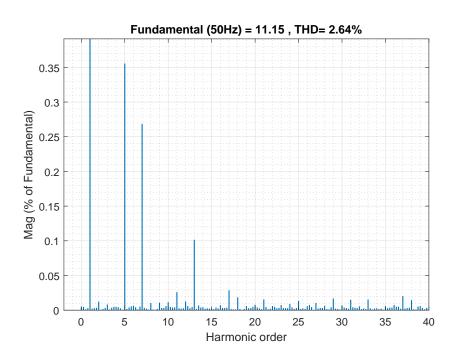

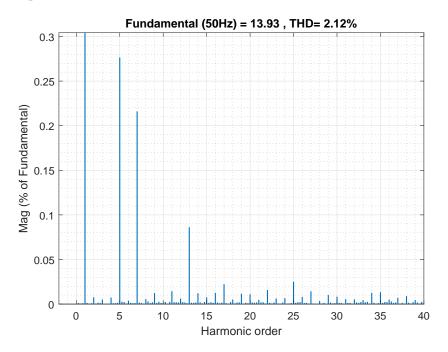

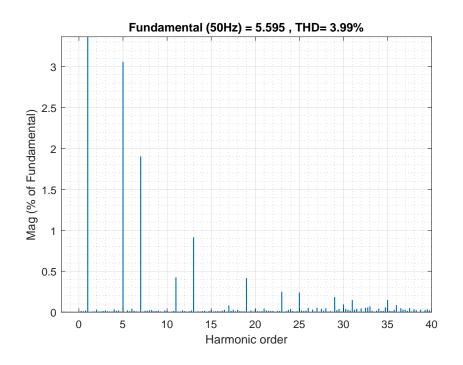

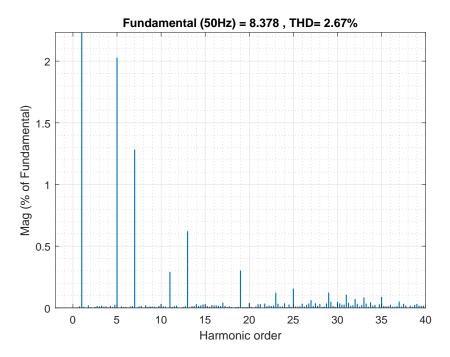

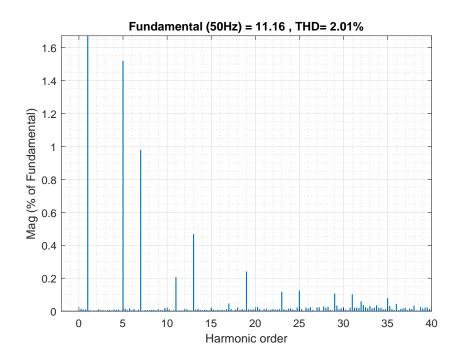

| 40 | Simulated $THD_i$ for the VOC AFE rectifier                             | 65  |

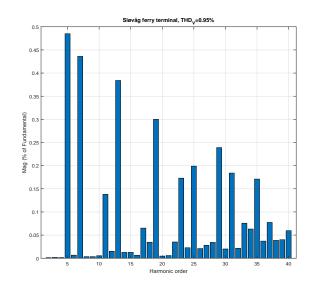

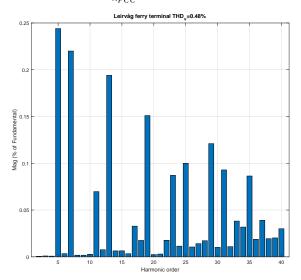

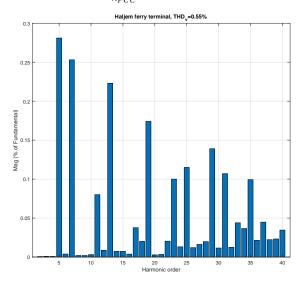

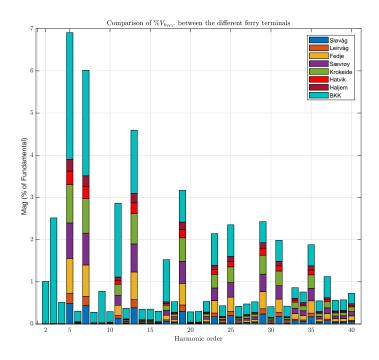

| 41 | Calculated $THD_v$ at the PCC for the VOC AFE rectifier                 | 71  |

| 42 | Comparison of the voltage harmonics referred to requirements from       |     |

|    | ВКК                                                                     | 71  |

| 43 | SimulationschemefortheVOCAFErectifierwithLCL-filterinSimulink           | 72  |

| 44 | Simulated dc voltage and current for the VOC AFE rectifier with LCL-    |     |

|    | filter                                                                  | 74  |

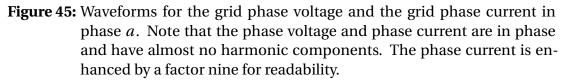

| 45 | Simulated grid voltage and current for the VOC AFE rectifier with       |     |

|    | LCL-filter                                                              | 75  |

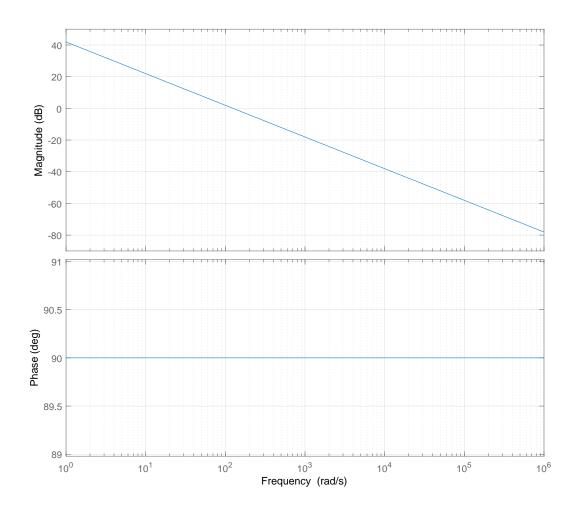

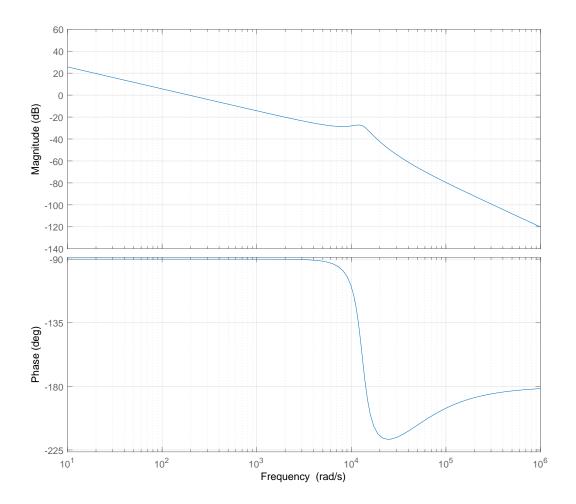

| 46 | Bode plot for the VOC AFE rectifier with LCL-filter                     | 76  |

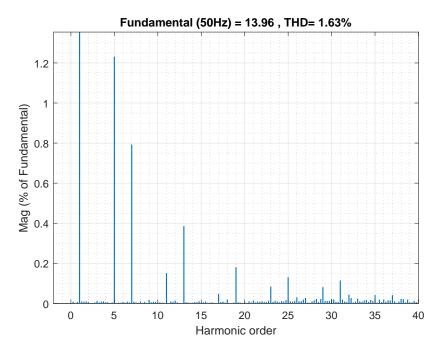

| 47 | Simulated $THD_i$ for the VOC AFE rectifier with LCL-filter             | 78  |

| 48 | Calculated $THD_v$ at the PCC for the VOC AFE rectifier with LCL-filter | 81  |

| 49 | Comparison of the voltage harmonics referred to requirements from       |     |

|    | ВКК                                                                     | 82  |

| 50 | Block scheme of the laboratory model for the VOC AFE rectifier $\ldots$ | 83  |

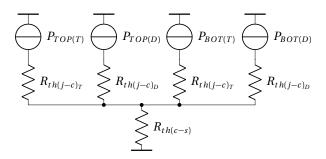

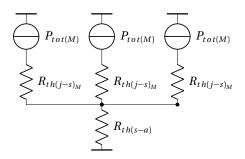

| 51 | Thermal resistance per IGBT module                                      | 89  |

| 52 | Thermal reistance for three IGBT modules including the heatsink         | 89  |

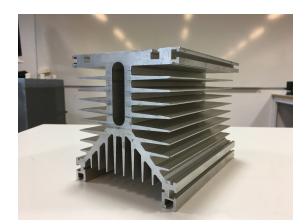

| 53 | Heat sink used for the IGBT modules                                     | 90  |

| 54 | IGBT driver card SKHI 23/12 (R)                                         | 92  |

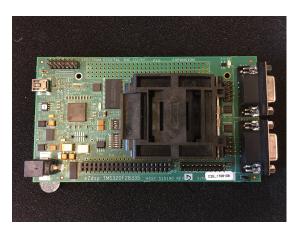

| 55 | DSC card eZdsp F28335                                                   | 93  |

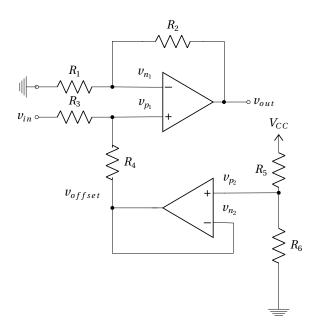

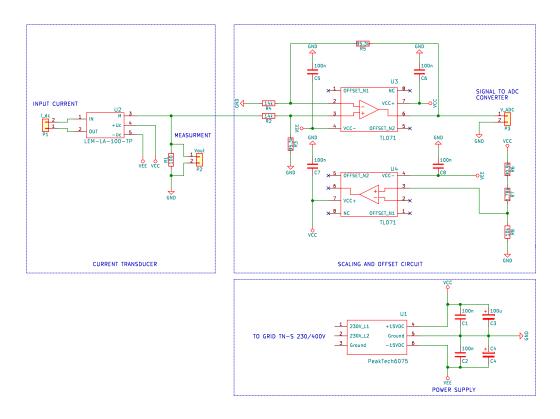

| 56 | Scaling and offset circuit for voltage and current transducers          | 97  |

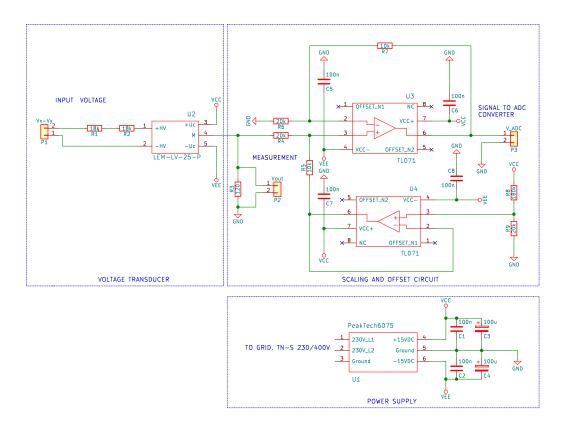

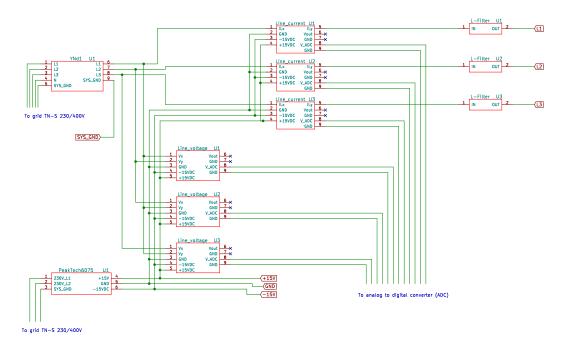

| 57 | Measurement card for the line voltages                                  | 98  |

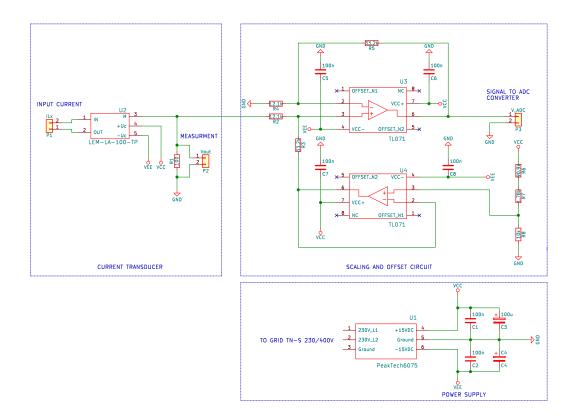

| 58 | Measurement card for the line currents                                  | 101 |

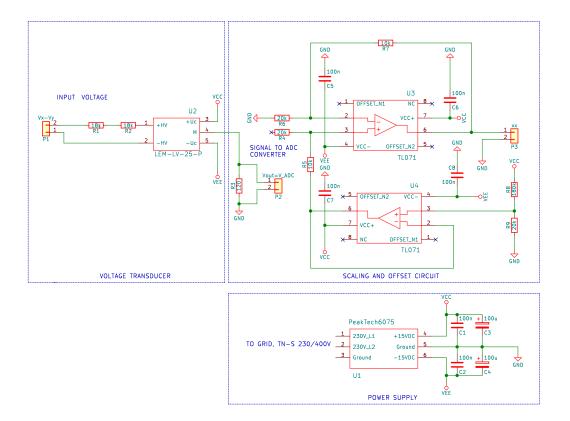

| 59 | Measurement card for the dc voltage                                     | 102 |

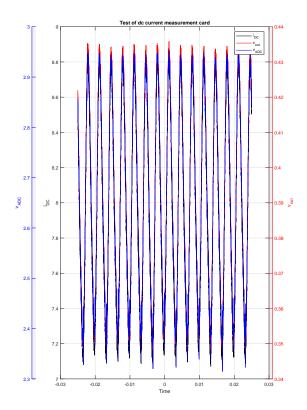

| 60 | Measurement card for the dc current                                     | 103 |

| 61 | Wiring diagram for the laboratory model part 1                          | 104 |

| 62 | Wiring diagram for the laboratory model part 2                          | 104 |

| 63 | Wiring diagram for the laboratory model part 3                          | 105 |

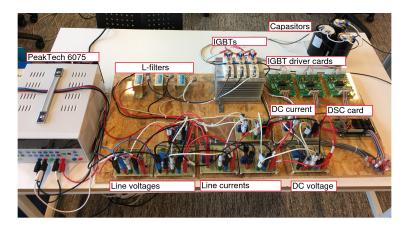

| 64 | Physical laboratory model                                               | 107 |

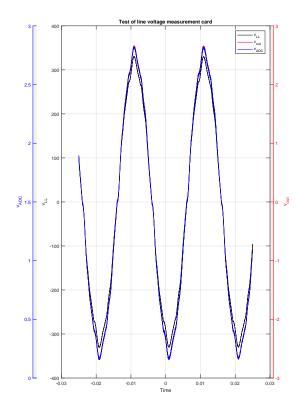

| 65 | Measured line voltage in the laboratory                                 | 108 |

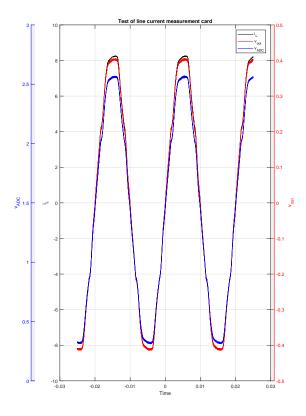

| 66 | Measured line current in the laboratory                                 | 109 |

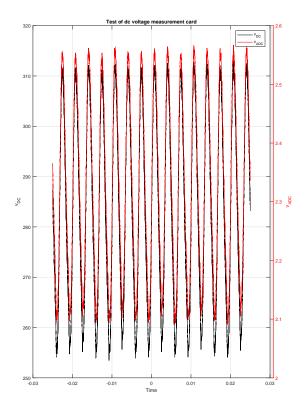

| 67 | Measured dc voltage in the laboratory                                   | 109 |

| 68 | Measured dc current in the laboratory                                   | 110 |

| 69 | Correlation between three-phase componets and the Clarke compo-     |

|----|---------------------------------------------------------------------|

|    | nents 119                                                           |

| 70 | Correlation between the Clarke componets and the Park components122 |

| 71 | Vector summation of the phase currents in equation B.8124           |

| 72 | Phase diagram for the L-filter power loss calaculation              |

| 73 | Phase diagram for the LCL-filter power loss calaculation 126        |

| 74 | Scaling circuit for voltage and current transducers                 |

# List of Tables

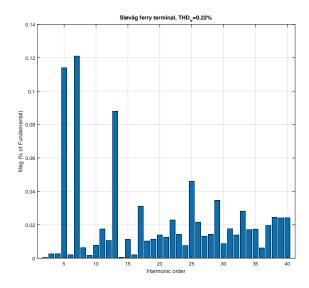

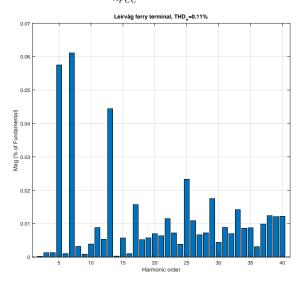

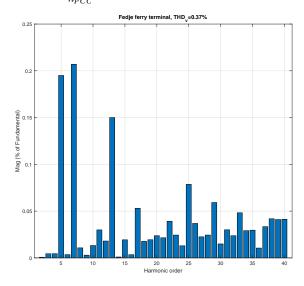

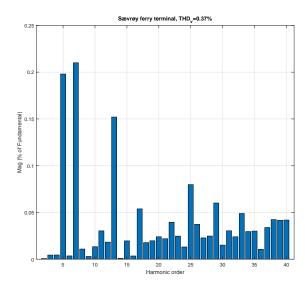

| 1  | Parameters from the utility grid near ferry terminals                             | 2  |

|----|-----------------------------------------------------------------------------------|----|

| 2  | Maximum values for the harmonic components drawn from the util-                   |    |

|    | ity grid owner BKK                                                                | 3  |

| 3  | Features for the different rectifier topologies                                   | 25 |

| 4  | Switching table for SVPWM                                                         | 32 |

| 5  | Switching times for sector I to VI                                                | 35 |

| 6  | Parameters for the VOC AFE rectifier simulation                                   | 50 |

| 7  | Parameters for the PI-controllers in the VOC AFE rectifier simulation             | 53 |

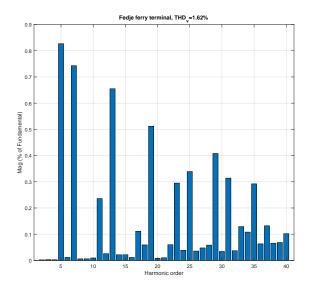

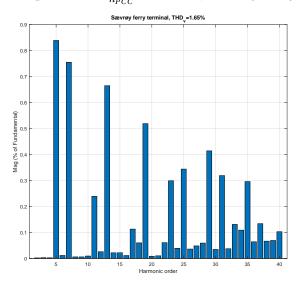

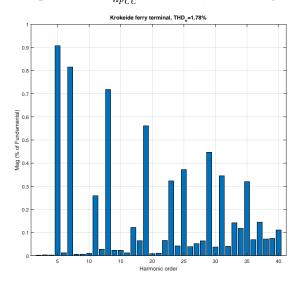

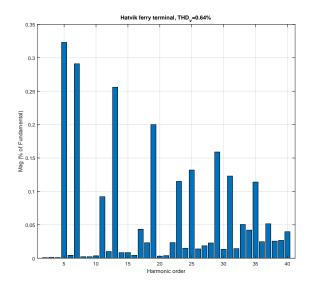

| 8  | Short circuit capacity and grid impedance                                         | 66 |

| 9  | Parameters for calculating $\% V_{h_{PCC}}$ at the different ferry terminals $$ . | 68 |

| 10 | Parameters for the VOC AFE rectifier with LCL-filter                              | 73 |

| 11 | Parameters for the PI-controllers in the VOC AFE rectifier with LCL-              |    |

|    | filter simulation                                                                 | 73 |

| 12 | Parameters for the VOC AFE laboratory model                                       | 84 |

# List of Abbreviations

| SC     | Shore connection                                    |

|--------|-----------------------------------------------------|

| UPF    | Unity power factor                                  |

| AC     | Alternating current                                 |

| DC     | Direct current                                      |

| IEEE   | Institution of Electrical and Electronics Engineers |

| IEC    | International Electrotechnical Commission           |

| ISO    | International Organization for Standardization      |

| SWBD   | Switchboard                                         |

| HVSC   | High voltage shore connection                       |

| LVSC   | Low voltage shore connection                        |

| HV     | High voltage                                        |

| THD    | Total harmonic distortion                           |

| rms    | Root mean square                                    |

| PWM    | Pulse with modulation                               |

| IGBT   | Insulated gate bipolar transistor                   |

| KVL    | Kirchhoff's voltage law                             |

| KCL    | Kirchhoff's current law                             |

| PF     | Power factor                                        |

| AFE    | Active front end                                    |

| CB-PWM | Carrier based pulse with modulation                 |

| SVPWM  | Space vector pulse with modulation                  |

| VOC    | Voltage orientated control        |

|--------|-----------------------------------|

| VFOC   | Virtual flux orientated control   |

| DPC    | Direct power control              |

| VF-DPC | Virtual flux direct power control |

| PLL    | Phase lock loop                   |

| PI     | Proportional Integral             |

| ADC    | Analog to digital converter       |

| DSP    | Digital signal processor          |

| DAC    | Digital to analog converter       |

| CCS    | Code composer studio              |

| DSC    | Digital signal controller         |

| ePMW   | Enhanced PWM                      |

| MUX    | Multiplexer                       |

| S/H    | Sample and hold                   |

| TB     | Time-base                         |

| CC     | Counter compare                   |

| AQ     | Action-Qualifier                  |

| GPIO   | General-purpose input/output      |

| DB     | Dead band                         |

| PC     | PWM-chopper                       |

| TZ     | Trip zone                         |

| OSHT   | One-shot-trip                     |

# ET Event trigger

SOC Start of conversion

- op amp Operational amplifier

- GND Ground

## 1 Introduction

In Norway there are approximately 180 ferry crossings where 80% are located between Stavanger and Trondheim [1]. The ferry fleet is mainly driven by combustion engines, running on diesel, liquefied nature gas or marine gas oil. Instead of conventional combustion engines it is possible to install electric motors fed by batteries on board. Some of the existing ferries use diesel electric propulsion systems, which means that it is even more convenient to go from fossil fuel to battery powered propulsion. Thus the diesel/gas generators can be removed, and the installation of battery packs which deliver electrical energy to the already installed electric motors can be conducted. For ferry crossings that have transit time less than 35 minutes and at least 20 trips per day, is it preferable with battery-powered ferries [2]. The batteries supply electrical energy for propulsion systems, shipboard technical systems and hotel services. In order to have a successful electrification of the ferry fleet, is it crucial to design a reliable shore connection (SC) system for battery charging.

## 1.1 Background

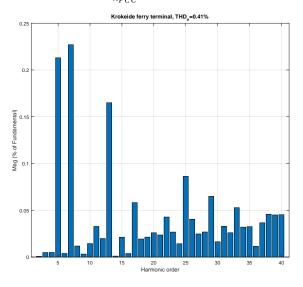

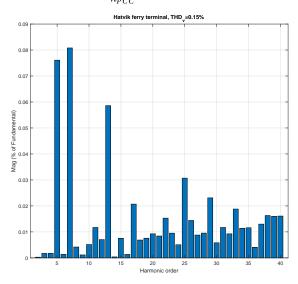

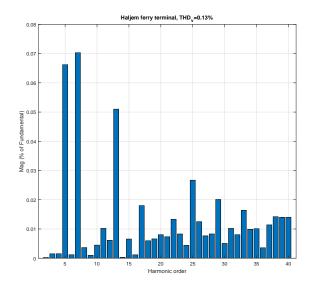

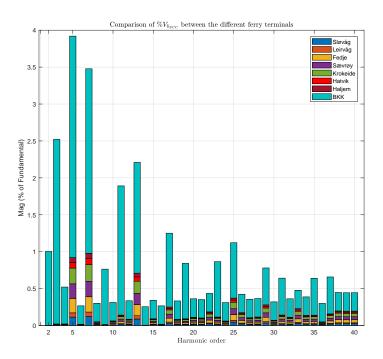

Due to the increased awareness of climate change and the fact that Norway signed the Paris agreement in 2015, this has led to the commitment to decrease emissions. The transportation sector is a major polluter and must decease their emissions if the Paris agreement is to be met. Ferry companies have to take their responsibility to reduce their emissions and use new technology to achieve lower energy consumption and environmental impacts. In Norway there are several new ferry contracts that either are fully electrical with batteries as energy source or hybrid vessels combined with diesel generators and batteries. In regards to electrification of the new ferry fleet, grid owners must consider to upgrade the utility grid near ferry terminals. The ferry crossings taken into account are limited to the locations in table 1. The most important parameters from the utility grid owner BKK are listed up [3]. The power capacity is limited in several locations and BKK might need to reinforce the utility grid in several areas before a electric ferry terminal can be established. The connection of the ferry terminal is regulated by supply safety

| Ferry terminal | Estimated power capacity | Voltage level | Short circuit capacity | $\cos\phi_{sc}$ |

|----------------|--------------------------|---------------|------------------------|-----------------|

| Leirvåg        | 3 MVA                    | 22 kV         | 115 MVA                | 0.42            |

| Sløvåg         | 3.5 MVA                  | 22 kV         | 58 MVA                 | 0.4             |

| Fedje          | 0.5 MVA                  | 22 kV         | 34 MVA                 | 0.8             |

| Sævrøy         | 0.5 MVA                  | 22 kV         | 33.5 MVA               | 0.76            |

| Krokeide       | 50kVA                    | 11kV          | 31 MVA                 | 0.62            |

| Hatvik         | 4 MVA                    | 22 kV         | 87 MVA                 | 0.48            |

| Haljem         | 2 MVA                    | 22 kV         | 100 MVA                | 0.43            |

**Table 1:** Parameters from the utility grid near ferry terminals. Limited to the concession of the grid owner BKK. Note that  $\cos \phi_{sc}$  is the relationship between the inductive and resistive short circuit capacity of the grid.

regulations and there are requirements to voltage quality in regards to the total harmonic distortion (THD), rapid voltage changes and flicker [4]. However the grid owners can demand stricter limits than described in the supply safety regulation [3]. BKK requires half of the parameters values described in the supply safety regulation in regards to harmonic distortion. After meeting BKK at their office in Kokstad, it was clear that the most important parameters regarding to voltage quality are the harmonic distortion and the voltage dips. The ferry charger involves power electronic components that are a source of harmonic distortion. Furthermore, electric ferries will have frequent connections to the utility grid that can lead to voltages dips. The maximum values for the harmonic components are listed up in table 2. THD are limited to 8% measured as an average value over 10 minutes or maximum 5% measured as an average value over 1 week [5]. The explanation on how to compute the distortion will be derived in section 3.1. The supply safety regulations describe voltage dips greater or equal 5% below agreed voltage rms value with a short duration (10ms-60s) to occur maximum 12 times per 24 hours.

The aforementioned requirements are important for BKK, but the ferry companies also have demands for the ferry charger application. In that regard there was conducted a meeting with Fjord1 that is the largest ferry company in Norway. They have several new ferry projects with predominantly electric ferries. Some of the important parameters that were mentioned under the meeting were power efficiency of the ferry charger, controllable power factor (PF) configured as either unity power factor (UPF) or leading PF using the ferry charger as a static compensator (STAT-COM).

**Table 2:** Maximum values for the harmonic components drawn from the utility grid owner BKK. Parameters described in the table are restricted to nominal voltages  $V \in [0.23, 35]$  kV

|          | Odd harr    | Even harmonics |       |                |       |

|----------|-------------|----------------|-------|----------------|-------|

| Not a mu | ltiple of 3 | Multiple of 3  |       |                |       |

| Order h  | $V_h$       | Order <i>h</i> | $V_h$ | Order <i>h</i> | $V_h$ |

| 5        | 3.0%        | 3              | 2.5%  | 2              | 1.0%  |

| 7        | 2.5%        | 9              | 0.75% | 4              | 0.5%  |

| 11       | 1.75%       | 15             | 0.25% | >4             | 0.25% |

| 13       | 1.5%        | 21             | 0.25% |                |       |

| 17       | 1.0%        | >21            | 0.25% |                |       |

| 19,23,25 | 0.75%       |                |       |                |       |

| >25      | 0.5%        |                |       |                |       |

## 1.2 Object of thesis

To restrict the scope of the ferry charger it was decided to investigate solutions for the rectifier system. This thesis attempts to answer the following question: Which rectifier is the most suited for charging electrical ferries? Parameters that are crucial are efficiency, controllable PF, harmonic current drawn from the utility and stability of the rectifier under several load conditions. To answer the following question, several rectifier technologies will be analyzed and simulated in Simulink. One of the rectifier topology will be built in the electric power laboratory. If the physical model is completed in time will the measured values be compared to the simulation results.

## 1.3 Structure of thesis

This thesis is divided in several section as follows: Section 2 gives an overview of two generic SC systems according to international standards. Section 3 analyzes different rectifier systems in regards to crucial parameters mentioned in section 1.2. Section 4 describes two rectifier systems with different filter design. Both systems are simulated in Simulink in section 5, where their parameters in regard to

voltage quality and stability are presented. Section 6 describes the physical rectifier model build in the electric power laboratory. The discussion of the results for both simulation and the laboratory model are discussed in section 7. The conclusion and future work of this thesis are presented in section 8.

# 2 Shore Connection Systems

Shore-to-power-systems come in a variety of names. The most common ones are cold ironing, alternative maritime power, shore-side electricity and onshore power supply. The term cold ironing originates from when ships were equipped with steam generators docked for repair. Both the pipes and steel for the boiler were cold during repair and therefore the term cold ironing is used [6]. In this text, the abbreviation shore connection systems will be used.

The world's first commercial shore connection system was installed at the port of Gotenburg in year 2000. The connection voltage varies between 400V to 10kV 50Hz [7]. Since the year 2000 several ports in the Pacific coast of North America and in Europe have installed shore connection systems. The nominal system voltage is usually 440V, 6.6kV or 11kV depending on the power requirement. The frequency is also varying between the different regions. Europe, Africa and Oceania operate with 50Hz and North America has a grid frequency of 60Hz. Asia uses mostly 50Hz and South America uses both. Over 50% of ships use 60Hz voltage systems[8]. This has lead to the need for a static or rotating frequency inverter in ac systems.

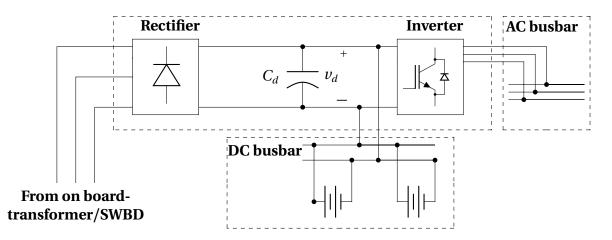

In applications, such as an electric ferry, the ac voltage has to be rectified before charging the batteries on board. Nevertheless, heavy consumers, such as the electric motors for the propulsion systems, pumps, lights and other technical services, need ac voltages to operate. One solution is to have both the rectifier and inverter in the main switchboard (SWBD) on board the electric ferry. In figure 1 the aforementioned solution is illustrated with a diode rectifier and a two-level switch-mode converter. Electrical and hybrid ferries often have a dc distribution system on board to charge the batteries. Therefore the electrical energy, either delivered from the diesel generator and/or from the utility grid on shore, has to be rectified.

To get an overview of the SC systems will the following section present different topologies according to international standards.

**Figure 1:** Three-phase diode rectifier charging the on board batteries from the dc busbar. Furthermore a two-level switch-mode inverter delivers electrical energy at a fixed frequency to the ac busbar.

## 2.1 Different topologies

There are several different topologies for a SC system. It depends on nominal voltage, power frequency on both grid and the ship's electrical system, cable handling devices, space requirements, harsh conditions, power requirements, local grid restrictions etc. Today's standards from IEEE, IEC, and ISO describe general requirements for high voltage shore connection (HVSC) systems [9] and a committee draft on low voltage shore connection (HVSC) systems [10]. Furthermore DNV GL provides rules of classification for electrical shore connections [11]. DNV GL does not differentiate between HVSC or LVSC and only the installation on board the vessel is covered. However some of the requirements described in the standards and classification is not applicable for ferries that have up to 30-40 connection each day. E.g. the SC solution on the battery ferry Ampere deviates from the proposed solutions in existing standards due to the requirement for a rapid and frequent connection. In order to achieve an equivalent safety level as in the standards, specialized solutions have been used.

#### 2.1.1 High voltage shore connection

The international standard IEC80005-1 Utility connections in ports - HVSC systems defines requirement for HVSC systems. The standard highlights both general

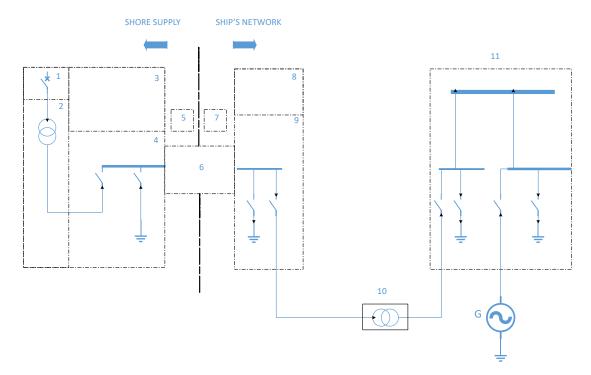

requirements and additional requirements for different ship's classes such as Ro-Ro passenger ships. The standard recommends using high voltage (HV) when the required power rating exceeds 1MW. The study [12] states that 52 ferry crossing in Norway need power ratings between 1MW to 10MW. Therefore HV systems are the most relevant if the international standards are to be followed. A typical HVSC system is shown in figure 2. From the block diagram there are several key elements described in the standard [9]:

Figure 2: A generic block diagram of a HVSC system. Adapted from [9]

- 1. Utility supply with associated circuit breaker.

- 2. The neutral point of the shore side transformer, feeding the shore-to-ship power, shall be earthed through a neutral resistor. An earth fault shall not create a step or touch voltage exceeding 30V at any location between the shore and ship. The nominal voltage levels is described either as 6.6kV or 11kV depending on the power ratings.

- Shore side protection system shall open all the poles in the circuit breaker in the event of: (a) Overcurrent, including short-circuit. (b) Over-voltage/undervoltage. (c) Reverse -power. Furthermore protection against transient overvoltage surges by means of surge arresters.

- 4. Shore-side earth switch and circuit breaker. The earth switch is to ensure that all energy in the shore connection cables is dissipated to ground before connection or disconnection between shore and ship side is conducted.

- 5. Control onshore consist of safety measures such as interlocks of HV circuit breakers, disconnectors and earthing switches.

- 6. Shore-to-ship connection and interface equipment. Consists of plugs and socket-outlets, cable handling equipment and connection cable. Data communication between shore and ship including information about shore transformer temperature, safety circuits, circuit breaker protection activation etc.

- 7. Control and monitoring of: (a) Cable tension and length. (b) Current unbalanced between multiple phases. (c) Equipotential bond created by the ship to shore connection cable shall be constantly monitored (d) Interlocks between earthing switches and circuit breakers.

- 8. Ship protection relaying shall be equipped with the same safety measurement as described in point 3 and also: (a) Over/under-frequency. (b) Phase sequence protection.

- On board shore connection SWBD shall be equipped with: (a) Voltmeter in all three phases. (b) Short-circuit devices. (c) Overcurrent devices. (d) Earthfault-indicator. (e) Unbalanced protection for systems with parallel cables.

- 10. Galvanic separation between the shore and ship's electrical systems is required either by a transformer on board or on shore. This is done to ensure that earth-fault-current from shore-to-ship or vice versa is eliminated. The transformer also supply the main SWBD on board with the desired voltage level.

- The synchronization process is performed at the main SWBD on board the ship. Instrumentation necessary to transfer load via parallel connection is: (a) Two voltmeters. (b) Two frequency meters. (c) One ammeter with a selector-switch to enable the current in each phase to be read. (d) Phase sequence indicator. (e) One synchronizing device.

#### 2.1.2 Low voltage shore connection

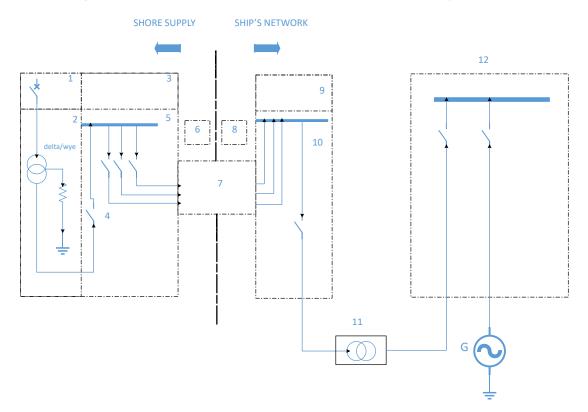

As mentioned in chapter 2.1 the committee draft IEC 8005-3 LVSC is the nearest international standard that exist for LVSC systems. If the apparent power ratings for the electric ferry are below 1MVA, the committee draft suggest the LVSC system. The committee draft describes a typical LVSC system as shown in figure 3. The block diagram is divided into different sections that describe key elements [10]:

Figure 3: A generic block diagram of a LVSC system. Adapted from [10]

- 1. Utility supply with associated circuit breaker.

- 2. The shore-side transformer shall be connected to a neutral grounding resistor (resistor may be omitted in IT-systems). An earth fault shall not create a touch or step voltage exceeding 25V any location between the shore and ship. Nominal voltage is either 400V, 440V or 690V, depending on the power ratings.

- Shore-side protection system shall open all the poles in the circuit breaker in the event of: (a) Overcurrent, including short-circuit. (b) Over-voltage/undervoltage. (c) Reverse-power. Furthermore protection against transient overvoltage surges by means of surge arresters is included.

- 4. Shore-side circuit breaker.

- 5. Shore-side feeders circuit breakers. The number of parallel connections varies according to the power transferred from shore to ship. E.g. 1000kVA power rating with a line voltage of 440V, requires 4 connections.

- 6. Control onshore, consist of interlocks that prevents connection of circuit breakers and disconnectors in case of: (a) Pilot contacts in the flexible shore-to-ship cable which signals correct connection. (b) Emergency-stop facilities such as push buttons. (c) Undervoltage coils both on shore and on board. (d) Others.

- 7. Shore-to-ship connection and interface equipment. Consists of plugs and socket-outlets, cable handling equipment and connection cable(s).

- 8. Control and monitoring of: (a) Cable tension and length. (b) Current unbalanced between multiple phases.

- Ship protection relaying shall be equipped with the same safety measurement as described in point 3 but also: (a) Over/under-frequency. (b) Phase sequence protection.

- Onboard shore connection SWBD shall be equipped with: (a) Voltmeter in all three phases. (b) Short-circuit devices. (c) Overcurrent devices. (d) Earthfault-indicator. (e) Unbalanced protection for systems with parallel cables.

- 11. Galvanic separation between the shore and ship's electrical systems is required, either by a transformer on board or on shore. This is done to ensure that earth fault from shore-to-ship or vice versa is eliminated. The transformer also supply the main SWBD on board with the desired voltage level.

- 12. The synchronization process is performed at the main SWBD on board the ship. Instrumentation necessary to transfer load via parallel connection is: (a) Two voltmeters. (b) Two frequency meters. (c) One ammeter with a selector-switch to enable the current in each phase to be read. (d) Phase sequence indicator. (e) One synchronizing device.

# **3** Rectifier systems

As discussed in section 2, a SC connection system is fairly complex with many components. The need for power electronic equipment for converting the utility voltage and/or frequency is often required. In this section different rectifier systems are presented and also control techniques are explained in detail. Challenges in regards to voltage quality will be explained and a rectifier system will be chosen.

## 3.1 Nonsinusoidal waveform in steady state

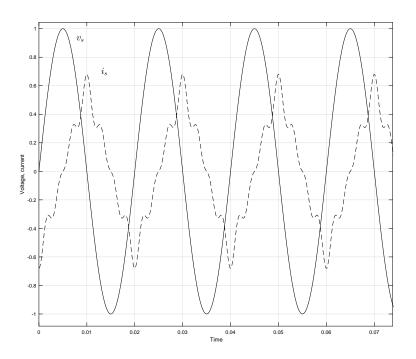

Power electronic circuits may draw highly distorted currents from the utility. Reasons for this phenomena is non sinusoidal loads such as rectifiers, inverters and switch-mode power supplies [13]. Figure 4 illustrates such a periodic waveforms that repeat with a time period *T* and frequency  $f = \frac{1}{T} = \frac{\omega}{2\pi}$ . Harmonic distortion

**Figure 4:** The example waveform shows that the voltage  $v_s$  have a sinusoidal waveform without any harmonic content. The current  $i_s$  is distorted with harmonic components.

in power systems can lead to undesirable effects such as overheating in transformers, cables, capacitors and motors. Circuit breakers may trip and equipment such as softstarters, depending of calculating the correct zero crossover point, might malfunction or fail. For distorted waveforms such as the current  $i_s$  in figure 4, it can be divided in a fundamental frequency component and harmonic components that are multiple of the fundamental frequency. These components can be calculated by means of Fourier analysis. A non sinusoidal periodic waveform f(t) with an angular frequency  $\omega$  can be represented by a trigonometric series defined by [14]

$$Ff(t) = \frac{1}{2}a_0 + \sum_{h=1}^{\infty} (a_h \cos(h\omega t) + b_h \sin(h\omega t))$$

(3.1)

The coefficients  $a_0$ ,  $a_h$  and  $b_h$  are defined respectively by

$$a_0 = \frac{1}{2\pi} \int_{0}^{2\pi} f(t) d(\omega t) = \frac{1}{T} \int_{0}^{T} f(t) dt$$

(3.2)

$$a_h = \frac{1}{\pi} \int_{0}^{2\pi} f(t) \cos(h\omega t) d(\omega t) \qquad h = 0, \dots, \infty$$

(3.3)

$$b_h = \frac{1}{\pi} \int_0^{2\pi} f(t) \sin(h\omega t) d(\omega t) \qquad h = 1, \dots, \infty$$

(3.4)

It should be noted from equation 3.2 that  $a_0$  is the average value of f(t) and is zero in figure 4. The coefficients  $a_h$  and  $b_h$  can be simplified in use of waveform symmetry (respectively even and odd symmetry). Each frequency component can be represented in term of its rms value. The rms magnitude is given by [14]

$$F_{h} = \frac{\sqrt{a_{h}^{2} + b_{h}^{2}}}{\sqrt{2}}$$

(3.5)

The total amount of distortion can be represented by a term called total harmonic distortion or simply THD. In terms of the current, it is defined as [14]

$$\% T H D_i = 100 \cdot \frac{I_{dis}}{I_{s1}} = 100 \cdot \frac{\sqrt{I_s^2 - I_{s1}^2}}{I_{s1}} = 100 \cdot \sqrt{\sum_{h \neq 1} \left(\frac{I_{sh}}{I_{s1}}\right)^2}$$

(3.6)

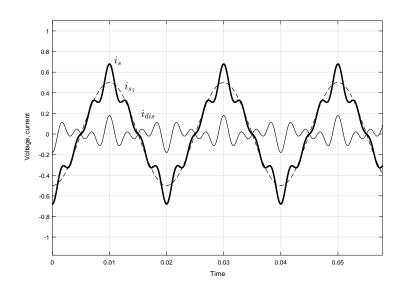

The expression for THD becomes clearer from figure 5. The line current  $i_s$ , its

**Figure 5:** Example of a distorted current with its decomposed values.  $i_s$  is the line current including the fundamental frequency component  $i_{s_1}$  and the distorted harmonic component  $i_{dis}$ .

fundamental frequency  $i_{s1}$  and its harmonic part  $i_{dis}$  is illustrated as function of time. The distorted line current component is expressed as [14]

$$i_{dis}(t) = i_s(t) - i_{s1}(t) = \sum_{h \neq 1} i_{sh}(t)$$

(3.7)

In term of rms values,

$$I_{dis} = \sqrt{I_s^2 - I_{s1}^2} = \sqrt{\sum_{h \neq 1} I_{sh}^2}$$

(3.8)

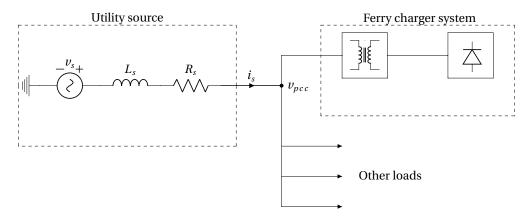

It should be noted that the line voltage  $v_s$  from the utility is assumed to be sinusoidal at the fundamental frequency. Also the average value or dc component is assumed to be zero in equation 3.6-3.8. The distorted line current affect the utility line voltage  $v_{pcc}$  at the point of common coupling (PCC) as illustrated in figure 6. The PCC in a ferry charger system is typically at the high voltage side of the transformer feeding the SC system. Other loads connected at the PCC will be affected by the distorted current drawn from the ferry charger. It is therefore crucial to install power electronic equipment such as the rectifier, which generates a small amount of harmonic distortion. The rms voltage at the PCC with a harmonic component

**Figure 6:** Interface between the utility source and the ferry charger at the PCC. Other loads connected to the PCC will be affected by the distorted current drawn from the ferry charger.

h injected to the ac source is expressed as [14]

$$V_{h_{PCC}} = h \left( R_s + j \omega L_s \right) I_h \tag{3.9}$$

The impedance  $Z_s$  can be calculated by the parameters given by the utility grid owner BKK in table 1. Considering only the scalar value of the  $V_{h_{PCC}}$  and the fact that

$$Z_s = R_s + j\omega L_s = R_s + jX_s \tag{3.10}$$

$$R_s = |Z_s| \cdot \cos \phi_{sc} \tag{3.11}$$

$$X_s = |Z_s| \cdot \sin \phi_{sc} \tag{3.12}$$

$$|Z_s| = \sqrt{R_s^2 + X_s^2} \tag{3.13}$$

yields

$$V_{h_{PCC}} = h \cdot |Z_s| \cdot I_h \tag{3.15}$$

The short circuit rms current in a per phase basis is expressed as (all three phases shorted to ground at PCC)

$$I_{sc} = \frac{\frac{S_k}{3}}{\frac{V_{LL}}{\sqrt{3}}} = \frac{S_k}{V_{LL}\sqrt{3}} = \frac{V_s}{|Z_s|}$$

(3.16)

where  $S_k$  is the three-phase short circuit capacity and  $V_{LL}$  is the line to line voltage.  $S_k$  and  $V_{LL}$  are given in table 1. Combining equation 3.15 and 3.16 yields

$$\% V_{h_{PCC}} = \frac{V_{h_{PCC}}}{V_s} \cdot 100 = h \frac{I_h}{I_{sc}} \cdot 100$$

(3.17)

Calculating the harmonic current components  $I_h$  in equation 3.5 and the short circuit current  $I_{sc}$  in equation 3.16, yields the harmonic voltage component  $\% V_{h_{pcc}}$ in equation 3.17. The calculation of total harmonic distortion is similar for the voltage compared to the current [14], and therefore by equation 3.6

$$\% T H D_{\nu} = 100 \cdot \frac{V_{dis}}{V_{s1}} = 100 \cdot \frac{\sqrt{V_s^2 - V_{s1}^2}}{V_{s1}} = 100 \cdot \sqrt{\sum_{h \neq 1} \left(\frac{V_{sh}}{V_{s1}}\right)^2}$$

(3.18)

### 3.2 Rectifiers

One of the main components in a SC system and the focus in this paper is the converter. More specific the converter is used as a rectifier in this case. The rectifier converts the sinusoidal line voltage from the utility grid to dc voltage. In this section different rectifiers will be presented with their operational principle in an idealized case.

#### 3.2.1 Diode rectifier

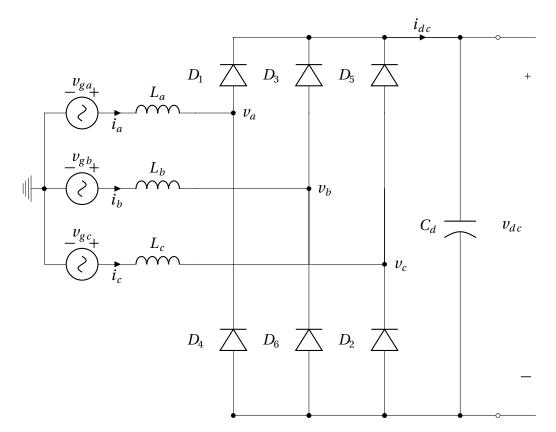

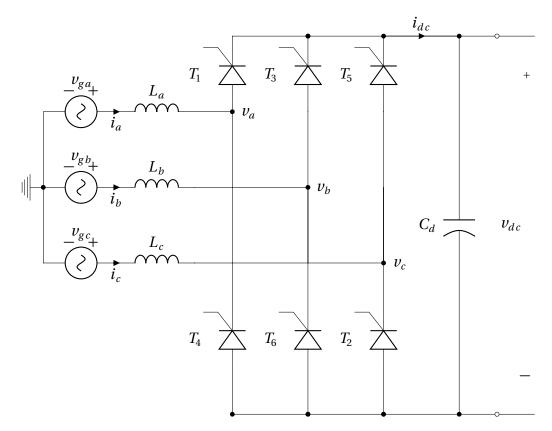

Line-frequency diode rectifiers are unidirectional and convert the utility ac voltage to an uncontrolled dc output voltage. A three-phase, full bridge diode rectifier is shown in figure 7. The diodes conduct in pairs, respectively D1 D2, D3 D4 and D5 D6. The diodes at the top group are at a common potential. Therefore the diode with it's anode at its highest potential will conduct  $i_{dc}$ . In the bottom group the diodes are also at a common potential and therefore the diode with its cathode at the lowest potential will conduct  $i_{dc}$ .

In an idealized case when the line inductances on the utility side  $L_a = L_b = L_c = 0$ and the load is replaced by a constant dc source, the waveform of the rectifier is as seen in figure 8. As illustrated, the instantaneous waveform of  $v_{dc}$  consist of

Figure 7: Three-phase full bridge diode rectifier. Adapted from [14].

six pulses and each diode conduct for 120°. The commutation interval is instantaneously in this idealized case. To obtain the average dc output value one of the six pulses is considered and its average value is calculated over an  $\frac{\pi}{3}$  interval. Arbitrarily the time origin t = 0 is chosen. From figure 8 it can be seen that

$$v_{dc} = v_{ab} = \sqrt{2} V_{LL} \cos(\omega t) \quad \text{where} \quad \omega t \in \left[-\frac{\pi}{6}, \frac{\pi}{6}\right]$$

(3.19)

and  $V_{LL}$  is the rms utility line to line voltage. The volt-second area *A* is averaged over the interval  $\frac{\pi}{3}$  and the dc output voltage is (*o* denotes idealized condition)

$$\nu_{dc_o} = \frac{3}{\pi} \int_{-\frac{\pi}{6}}^{\frac{\pi}{6}} \sqrt{2} V_{LL} \cos(\omega t) d(\omega t) = \frac{3}{\pi} \sqrt{2} V_{LL} = 1.35 V_{LL}$$

(3.20)

By using the definition of rms current and the waveform produced by the three-

**Figure 8:** Waveform for the circuit in figure 7. Note that the diode D1 in phase *a* stops to conduct when phase voltage  $v_{gb}$  is greater than  $v_{ga}$ . Also note that diode D4 stops to conduct when  $v_{ga}$  is greater than  $v_{gb}$ .

phase bridge, the phase current is

$$I_{s} = \sqrt{\frac{1}{\pi} \int_{\frac{\pi}{3}}^{\pi} I_{dc}^{2} d(\omega t)} = \sqrt{\frac{2}{3}} I_{dc} = 0.816 I_{dc} \quad \text{where } s \in \{a, b, c\} \quad (3.21)$$

The phase currents drawn from the utility grid are rich with harmonic components as illustrated in phase *a* in figure 8. To compute the fundamental frequency component  $I_{s1}$ , the Fourier series is calculated. The use of odd symmetry ( $I_s(-t) = -I_s(t)$ ) simplifies the calculation of the Fourier coefficients and is given by

$$a_{0} = a_{h} = 0$$

$$b_{h} = \frac{2}{\pi} \int_{\frac{\pi}{6}}^{\frac{5\pi}{6}} I_{dc} \sin(h\omega t) d(\omega t) = -\frac{2I_{dc}}{h\pi} \int_{\frac{\pi}{6}}^{\frac{5\pi}{6}} -h \sin(h\omega t) d(\omega t)$$

$$(3.22)$$

$$2I_{dc} \left( -\frac{1}{2} - \frac{1}{2} \right) \int_{\frac{\pi}{6}}^{\frac{5\pi}{6}} \int_{0}^{\frac{5\pi}{6}} \int_{0}^{\frac{5\pi}{6}} \int_{0}^{\frac{5\pi}{6}} \int_{0}^{\frac{5\pi}{6}} h(\omega t) d(\omega t)$$

$$(3.22)$$

$$= -\frac{2I_{dc}}{h\pi} (\cos(h\omega t)) \Big|_{\frac{\pi}{6}}^{\frac{5\pi}{6}} = \begin{cases} 0 & \text{if } h = 2,3,4,6,8,9,10,12,14,15 \\ \frac{2\sqrt{3}}{h\pi}I_{dc} & \text{if } h = 1,5,7,11,13,\dots \end{cases}$$

Therefore the Fourier series is expressed by

$$FI_{dc}(t) = \frac{2\sqrt{3}}{h\pi} \sum_{h=1,5,7,11,13,\dots}^{\infty} I_{dc} \sin(h\omega t)$$

(3.24)

Thus the fundamental frequency component in rms terms yields

$$I_{s1} = \frac{2\sqrt{3}}{\pi} I_{dc} \sqrt{\frac{1}{\frac{5\pi}{6} - \frac{\pi}{6}} \int_{\frac{\pi}{6}}^{\frac{5\pi}{6}} \sin^2(\omega t) d(\omega t)} = \frac{1}{\pi} \sqrt{6} I_{dc}$$

(3.25)

One major drawback with the diode rectifier are the harmonic content and is calculated from equation 3.6 and yields

$$\% THD_{i} = 100 \cdot \frac{\sqrt{I_{s}^{2} - I_{s1}^{2}}}{I_{s1}} = 100 \cdot \frac{\sqrt{\frac{2}{3} - \frac{6}{\pi^{2}}}}{\frac{\sqrt{6}}{\pi}} = 31.08\%$$

(3.26)

Another important quantity is the PF and is given by [14]

$$PF = \frac{I_{s1}}{I_s} DPF = \frac{I_{s1}}{I_s} \cos \phi = \frac{\frac{\sqrt{6}}{\pi} I_d}{\sqrt{\frac{2}{3}} I_d} = \frac{3}{\pi} = 0.955$$

(3.27)

with the assumption that the phase angle  $\phi$  between the utility voltage and the line current is zero.

#### 3.2.2 Thyristor rectifier

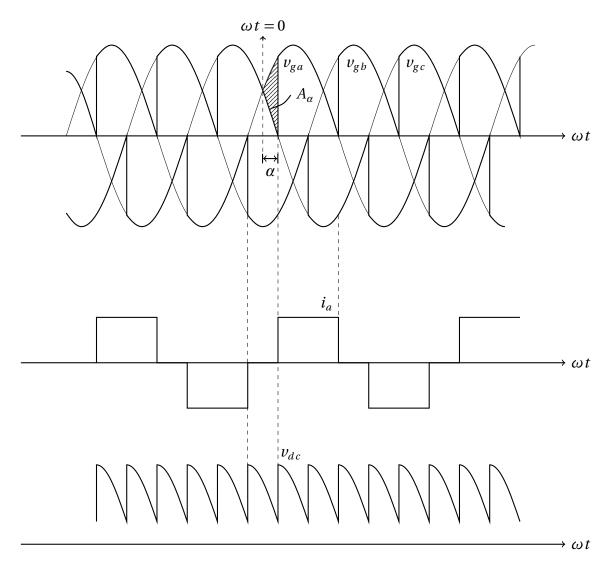

In application, such as battery chargers, it is necessary to control the dc voltage from the rectifier. To control the power flow there are several ways to produce a controlled dc voltage from the rectifiers output. A line-frequency phase-controlled thyristor is one solution and is shown in figure 9. The rectifier consists of three thyristor pairs, namely  $T_1$   $T_2$ ,  $T_3$   $T_4$  and  $T_5$   $T_6$ . A thyristor pair begins or ceases to conduct depending on the line-frequency ac voltage and the control inputs.

Figure 9: Three-phase full bridge thyristor rectifier. Adapted from [14].

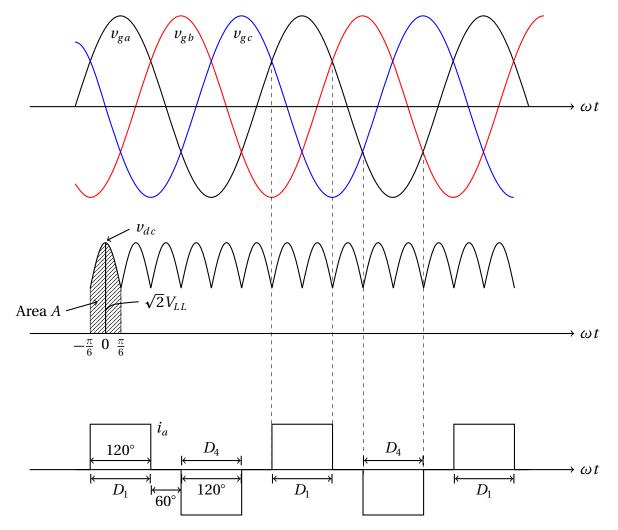

To analyze the circuit, some simplifications are made where the line inductances  $L_a = L_b = L_c = 0$  and assume that  $i_{dc}(t) = I_{dc}$ . The gate on each thyristor is controlled by the firing angle  $\alpha$ . If  $\alpha = 0^\circ$  then the thyristor bridge has the same functionality as the diode rectifier in section 3.2.1 and the dc output voltage

$$v_{dc_o} = \frac{3\sqrt{2}}{\pi} V_{LL} = 1.35 V_{LL} \tag{3.28}$$

When  $\alpha > 0^{\circ}$  some of the input ac voltage  $V_{LL}$  will be blocked and hence the output

**Figure 10:** Waveform of the three-phase full bridge thyristor rectifier in figure 9. Note that the area  $A_{\alpha}$  is blocked by the firing angle  $\alpha$ . The phase difference between the phase current and the phase voltage is  $\phi_1 = \alpha$ .

voltage  $v_{dc}$  will decrease. Waveforms of the rectifier when  $\alpha = 30^{\circ}$  is shown in figure 10. The commutating process is delayed by the firing angle and the volt-second area  $A_{\alpha}$  results in a reduction of the average dc output voltage by

$$v_{dc_a} = v_{dc_0} - \frac{A_a}{\pi/3}$$

(3.29)

The voltage reduction  $A_{\alpha}$  happens every 60° and is given by the integral of  $v_{an} - v_{cn} = v_{ac}$ . Where

$$v_{ac} = \sqrt{2} V_{LL} \sin \omega t \tag{3.30}$$

Therefore,

$$A_{\alpha} = \int_{0}^{\alpha} \sqrt{2} V_{LL} \sin \omega t \, d(\omega t) = \sqrt{2} V_{LL} (1 - \cos \alpha)$$

(3.31)

Combining equation 3.28 and 3.31 into 3.29 yields

$$v_{dc_{\alpha}} = \frac{3\sqrt{2}}{\pi} V_{LL} \cos \alpha = 1.35 V_{LL} \cos \alpha \tag{3.32}$$

When  $\alpha > 90^{\circ}$  the average dc voltage becomes negative and the converter acts as an inverter. The thyristor bridge is called a two-quadrant converter since it can operate as a rectifier and an inverter. This is in contrast to the diode bridge that only functions as a rectifier. This will not be discussed further.

From Fourier analysis the harmonic components is calculated from figure 10. Note that  $i_a$  is symmetric around the  $\omega t$ -axis, thus simplifying the calculations. The Fourier coefficients are expressed as

$$a_{0} = a_{h} = 0$$

$$b_{h} = \frac{2}{\pi} \int_{\frac{\pi}{6} + \alpha}^{\frac{5\pi}{6} + \alpha} I_{dc} \sin(h\omega t - \alpha) d(\omega t) = -\frac{2I_{dc}}{h\pi} \int_{\frac{\pi}{6} + \alpha}^{\frac{5\pi}{6} + \alpha} - h \sin(h\omega t - \alpha) d(\omega t)$$

(3.34)

$$= -\frac{2I_{dc}}{h\pi} (\cos(h\omega t - \alpha)) \Big|_{\frac{\pi}{6} + \alpha}^{\frac{5\pi}{6} + \alpha} = \begin{cases} 0 & \text{if } h = 2, 3, 4, 6, 8, 9, 10, 12, 14, 15, ... \\ \frac{2\sqrt{3}}{h\pi} I_{dc} & \text{if } h = 1, 5, 7, 11, 13, ... \end{cases}$$

Therefore the Fourier series is expressed by

$$FI_{dc}(t) = \frac{2\sqrt{3}}{h\pi} \sum_{h=1,5,7,11,13,\dots}^{\infty} I_{dc} \sin(h\omega t - \alpha)$$

(3.35)

Similar for the diode rectifier the fundamental frequency component in rms terms yields

$$I_{s1} = \frac{2\sqrt{3}}{\pi} I_{dc} \sqrt{\frac{1}{\frac{5\pi}{6} + \alpha - \frac{\pi}{6} - \alpha}{\int_{\frac{\pi}{6} + \alpha}^{\frac{5\pi}{6} + \alpha}}} \sin^2(\omega t - \alpha) d(\omega t) = \frac{1}{\pi} \sqrt{6} I_{dc}$$

(3.36)

The phase current and the THD yields the same result as the diode rectifier and hence

$$I_s = \sqrt{\frac{2}{3}} I_{dc} \tag{3.37}$$

$$\% T H D_i = 31.08\%$$

(3.38)

Furthermore the phase difference between the phase voltage and the phase current  $\phi_1 = \alpha$  in figure 10. Hence the PF is calculated as

$$PF = \frac{I_{s1}}{I_s} \cos \phi_1 = \frac{3}{\pi} \cos \alpha = 0.955 \cos \alpha$$

(3.39)

Another important aspect is how much average power the thyristor converter can deliver to the load and is given by

$$P = \frac{1}{T} \int_0^T p(t) dt = \frac{1}{T} \int_0^T \nu_{dc} i_{dc} dt$$

(3.40)

Assuming  $i_{dc}(t) = I_{dc}$  yields

$$P = I_{dc} \left( \frac{1}{T} \int_0^T v_{dc} \, dt \right) = V_{dc} I_{dc} = 1.35 V_{LL} I_{dc} \cos \alpha \tag{3.41}$$

The fundamental reactive power component drawn from the thyristor converter is expressed as

$$Q = 1.35 V_{LL} I_{dc} \sin \alpha \tag{3.42}$$

#### 3.2.3 Active Front End rectifier

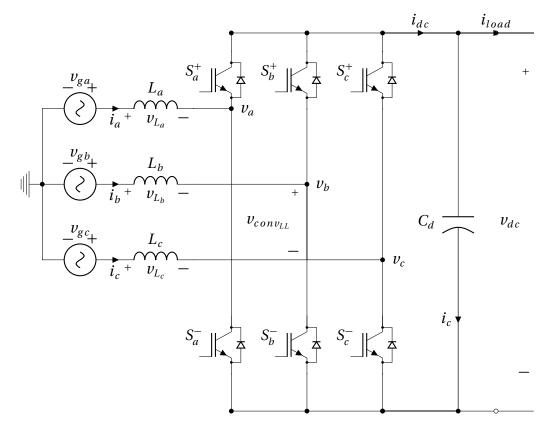

As briefly discussed in section 3.2.1 and 3.2.2 the rectifier schemes draw a highly distorted current from the utility grid. This is off course undesirable and can be improved in different ways. One solution is to install passive filters to filter out the low and high order harmonics. Nevertheless this makes the system bulky and costly. A more elegant solution is to install rectifiers with active filter techniques such as pulse with modulation (PWM) rectifiers. A basic circuit of a three-phase

PWM rectifier, called Active Front End (AFE) in this text, is shown in figure 11.

Figure 11: Three-phase Active Front End rectifier. Adapted from [14].

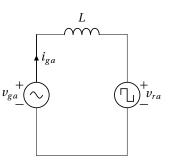

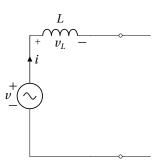

Each leg consists of two insulated gate bipolar transistors (IGBT),  $S_a^+$  and  $S_a^-$  for phase a. Each IGBT is connected in anti-parallel with a flyback diode. The capacitor  $C_d$  reduces the ripple content of the output dc voltage  $v_{dc}$  and the inductors  $L_a$ ,  $L_b$  and  $L_c$  represent the line inductances. The switching frequencies of the IGBTs are several kHz and therefore the voltages over an inductive load  $v_L = L \frac{di}{dt}$  will become large and the potential difference between the IGBTs and the inductor will produce a voltage spike. To eliminate this problem the flyback diodes give the current  $i_{dc}$  a return path and therefore protect the IGBTs from destruction.

The voltage and current equations from figure 11 (assuming  $L_a = L_b = L_c = L$ ) are derived from Kirchhoff's voltage law (KVL) and Kirchhoff's current law (KCL) and is expressed by

$$\begin{bmatrix} v_{ga} \\ v_{gb} \\ v_{gc} \end{bmatrix} = L \frac{d}{dt} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + \begin{bmatrix} v_a \\ v_b \\ v_b \end{bmatrix}$$

(3.43)

$$C\frac{d_{v_{dc}}}{dt} = (S_a i_a + S_b i_b + S_c i_c) - i_{load}$$

(3.44)

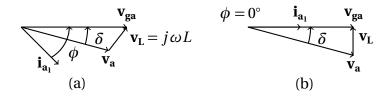

$S_a$ ,  $S_b$  and  $S_c$  are the duty cycle for its respective phase. The phasor diagram for phase a is given by figure 12a, where the fundamental component of the phase current  $\mathbf{i}_{a_1}$  lags the source voltage  $\mathbf{v}_{ga}$  with an arbitrary angle  $\phi$ . Switching frequency harmonics is neglected for simplicity. The net real power P supplied to the converter from the three-phase ac source is expressed by (assuming balanced supply)

$$P = 3\mathbf{v_{ga}}\mathbf{I_{a_1}}\cos\phi = 3\frac{\mathbf{v_{ga}}^2}{\omega L} \left(\frac{\mathbf{v_a}}{\mathbf{v_{ga}}}\sin\delta\right)$$

(3.45)

Similar from figure 12a, the net imaginary reactive power *Q* supplied to the converter from the three-phase ac source is

$$Q = 3\mathbf{v_{ga}}\mathbf{I_{a_1}}\sin\phi = 3\frac{\mathbf{v_{ga}}^2}{\omega L} \left(1 - \frac{\mathbf{v_a}}{\mathbf{v_{ga}}}\cos\delta\right)$$

(3.46)

To control the supply of net power S (S = P + jQ) to the converter, phase voltages  $\mathbf{v}_{a}$ ,  $\mathbf{v}_{b}$  and  $\mathbf{v}_{c}$  has to be controlled in both magnitude and phase angle  $\delta$ . Operating the converter in rectifying mode, it is often desired to achieve UPF as seen in figure 12b.

Figure 12: For phase a; (a) general phasor diagram; (b) rectifier at UPF

The dc output voltage  $v_{dc}$  is an important parameter and is regulated by the duty cycle of each IGBT switch. The switching scheme of the IGBTs can be quite complex and will be discussed in section 3.3.

## 3.2.4 Choosing the rectifier topology

There are several different rectifier solution that also could be considered. A particular interesting one is the Vienna rectifier. It is a three-level rectifier with the capability of PF correction and reduced switching losses [15]. However, due to limited time in this project the Vienna rectifier will not be presented in detail. The advantages and disadvantages for the rectifiers in section 3.2.1, 3.2.2, 3.2.3 and the Vienna rectifier are shown in table 3.

Table 3: Features for the different rectifier topologies discussed in this thesis.

| Rectifier | Harmonic distortion | Controllable dc voltage | Power factor | Bi-directional power flow |  |

|-----------|---------------------|-------------------------|--------------|---------------------------|--|

| Diode     | High                | No                      | Low          | No                        |  |

| Thyristor | High                | Yes                     | Low          | No                        |  |

| AFE       | Low                 | Yes                     | High         | Yes                       |  |

| Vienna    | Low                 | Yes                     | High         | No                        |  |

A practical diode and thyristor rectifier have a very poor PF due to the line current being far from sinusoidal and hence the need for filters is increased [14]. The Vienna and AFE rectifier on the other hand draws almost perfectly sinusoidal currents from the utility grid if the rectifier system is designed properly. It is also possible to achieve UPF with these systems. However only the AFE rectifier is capable to utilize bi-directional power flow and can be used as a static compensator (STATCOM). This can be favorable if the PF at the PCC is low and thus the STATCOM delivers reactive power back to the grid. Furthermore the reactive power contributes maintaining the grid voltage level at the PCC. Therefore were the AFE rectifier topology chosen for the ferry charger solutions.

## 3.3 Control of rectifiers

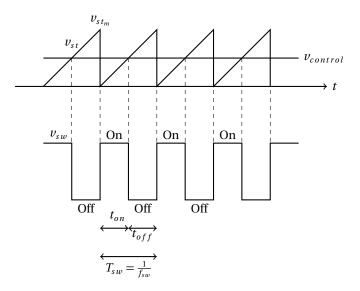

To control the switching scheme of the two-level AFE rectifier in figure 11 several techniques are discussed in the literature [16–20]. The IGBT switches are controlled in an on/off fashion and therefore the switch-mode rectifier is a descriptive term. However, in this text the switch-mode rectifier is called AFE rectifier. The basic conversion method applied for AFE rectifiers is PWM techniques. Historically one of the best known methods is carrier based PWM (CB-PWM). This technique is shown in figure 13.

**Figure 13:** The control signal  $v_{control}$  is compared to the sawtooth signal  $v_{st}$  and yields a digital output signal  $v_{sw}$  to the gate of the IGBTs. Adapted from [14].

The sawtooth signal  $v_{st}$  is compared with the control signal  $v_{control}$ . From the waveform it can be seen that the switch control signal  $v_{sw}$  is either on or off by the following expressions

$$v_{control} \ge v_{st} \qquad v_{sw} = 1 \tag{3.47}$$

$$v_{control} < v_{st} \qquad v_{sw} = 0 \tag{3.48}$$

To control phase *a*,*b* and *c* it requires three control signals which again sets the switch position of the IGBTs in relation to

$$v_{control_{u}} \ge v_{st}$$

$S_{u}^{+} = 1$   $u \in \{a, b, c\}$  (3.49)

$$v_{control_u} < v_{st} \qquad S_u^+ = 0 \tag{3.50}$$

Furthermore is  $S_u^+$  always complementary according to  $S_u^-$ . Some important definitions and parameters have to be defined, which characterizes PWM methods:

$$m_a = \frac{\nu_{control}}{\nu_{st_m}} \tag{3.51}$$

$$m_f = \frac{f_{sw}}{f_1} \tag{3.52}$$

$m_a$  is the modulation index and for sinusoidal modulation  $0 < m_a < 1$ .  $m_f$  is the

frequency modulation,  $f_{sw}$  is the switching frequency and  $f_1$  is the frequency for the control signal  $v_{control}$ . The switching frequency  $f_{sw}$  is kept constant and is normally chosen to span from a few kilohertz to few hundred kilohertz [14]. The duty cycle is calculated from figure 13 and is expressed as

$$D_s = \frac{t_{on}}{T_s} = \frac{\nu_{control}}{\nu_{st}}$$

(3.53)

Today's basic power processing technique uses space vector pulse with modulation (SVPWM) after advances in microprocessing developments [21]. Several rectifier systems use SVPWM, such as voltage oriented control (VOC) and virtual flux oriented control (VFOC). Other control techniques such as direct power control (DPC) and virtual flux power control (VF-DPC), use switching tables but have several similarities to VOC and VFOC. After the work done by M. Malinowski in [22], was it decided to control the rectifier for the ferry charger with VOC. To fully understand VOC, transformation techniques and SVPWM are presented respectively in section 3.3.1 and 3.3.2.

#### 3.3.1 Clarke and Park transformation

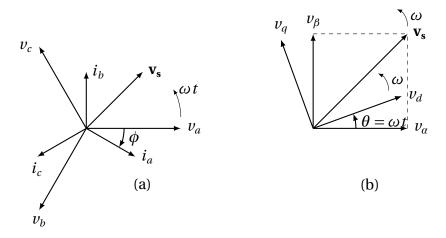

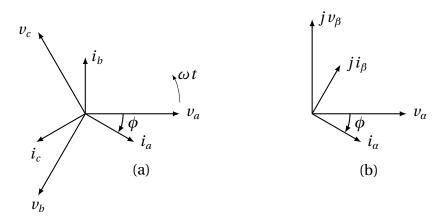

Several of the PWM techniques in the literature measure the phase voltages and/or the line currents from the utility grid. These quantities are controlled against set values to ensure that the dc output voltage from the rectifier is at the desired range. To ease the control system the ac values is transformed to dc values. The transformation can be done in two separated transformations named Clarke and Park transformation [23, 24]. The ac voltages and currents from the utility grid are illus-

**Figure 14:** (a) Phase voltages and line currents in a three-phase stationary reference frame; (b) Phase voltages in a two-phase stationary reference frame compared to synchronously rotating reference frame.

trated in figure 14 (a) and are defined as

$$v_a = V_m \sin(\omega t) \tag{3.54}$$

$$v_b = V_m \sin(\omega t - \frac{2\pi}{3}) \tag{3.55}$$

$$\nu_c = V_m \sin(\omega t + \frac{2\pi}{3}) \tag{3.56}$$

$$i_a = I_m \sin(\omega t + \phi) \tag{3.57}$$

$$i_b = I_m \sin(\omega t - \frac{2\pi}{3} + \phi)$$

(3.58)

$$i_c = I_m \sin(\omega t + \frac{2\pi}{3} + \phi)$$

(3.59)

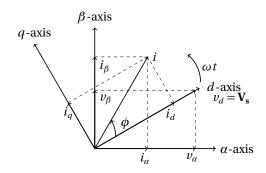

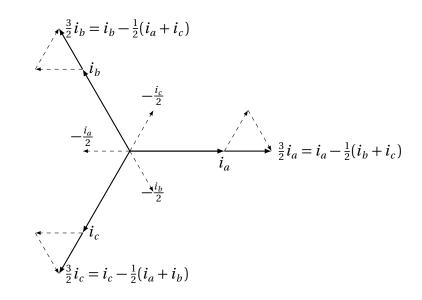

where  $V_m$  and  $I_m$  are the amplitude value of the phase voltages and line currents. Instead of representing the line currents and the phase voltages in a three-phase stationary reference frame, can it be transformed to a two-phase stationary reference frame,  $\alpha$  and  $\beta$  also called the Clarke transformation. Only the transformation for the voltage components will be derived, but the procedure for the line currents derivation is the same. First the term space vector is defined as

$$\mathbf{v}_{\mathbf{s}} = \frac{2}{3} \left( \nu_a + \nu_b e^{\frac{j2\pi}{3}} + \nu_c e^{\frac{j4\pi}{3}} \right) = \nu_s e^{j\theta}$$

(3.60)

The Clarke transform is directly related to the space vector and is defined as

$$\mathbf{v}_{\alpha\beta} = \nu_{\alpha} + j\,\nu_{\beta} = \mathbf{v}_{\mathbf{s}} \tag{3.61}$$

where the subscripts  $\alpha$  and  $\beta$  are the real and imaginary part of the complex number and are given by

$$v_{\alpha} = \frac{2}{3} \left( v_{a} - \frac{1}{2} (v_{b} + v_{c}) \right)$$

(3.62)

$$\nu_{\beta} = \frac{2}{3} \left( 0 + \frac{\sqrt{3}}{2} (\nu_{b} - \nu_{c}) \right)$$

(3.63)

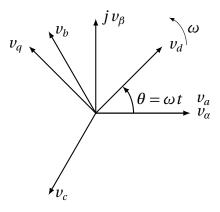

The space vector is rotating with an angular velocity  $\omega$  in a stationary reference frame as shown in figure 14 (b). It is convenient to transform the stationary reference frame to the rotating space vector in a synchronously rotating reference frame with an angular velocity  $\omega$ . This results in that both the space vector and the reference frame rotates with the same angular velocity. The foregoing discussion is called the Park transform and is expressed as

$$\mathbf{v_s} e^{-j\left(\omega t - \frac{\pi}{2}\right)} = \mathbf{v_{dq}} = v_d + j v_q \tag{3.64}$$

where the real and imaginary part are expressed as

$$v_d = v_\alpha \sin \theta + v_\beta \cos \theta \tag{3.65}$$

$$v_q = -v_\alpha \cos\theta + v_\beta \sin\theta \tag{3.66}$$

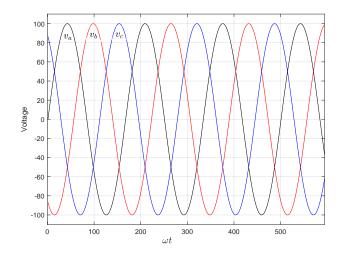

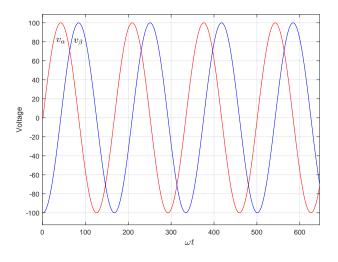

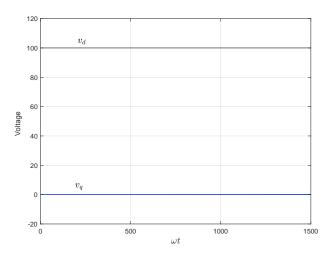

To clarify the foregoing discussion, the waveforms for  $v_a$ ,  $v_b$ ,  $v_c$ ,  $v_a$ ,  $v_\beta$ ,  $v_d$  and  $v_q$  are plotted in figure 15. For more detailed derivation see appendix A.

(a) Three-phase ac voltages  $v_a, v_b$  and  $v_c$  as a function of  $\omega t$ .

(b) Two-phase ac voltages  $v_{\alpha}$  and  $v_{\beta}$ . Note that  $v_{\beta}$  is lagging 90° in respect to  $v_{\alpha}$

(c) Dc voltages  $v_d$  and  $v_q$  in a synchronous rotating reference frame. Note that  $v_q$  is zero.

**Figure 15:** The effect of Clarke and Park transformation on a three-phase voltage source.

## 3.3.2 Space vector modulation

To achieve stable dc output voltage  $V_{dc}$  at a desired PF has the control system to be reliable. Before describing complete solutions for the VOC system in section 4.1, is SVPWM discussed in detail.

The gate terminal of the IGBTs in figure 11 receives switching commands from the space vector modulator. The principle of SVPWM is to create a reference vector  $\mathbf{V}^*$  in compliance with the difference or error signal between measured values on the ac side and the dc side of the rectifier. The error signal can for example be the phase currents  $i_d$  and  $i_q$  from the utility grid compared with the reference currents  $i_d^*$  and  $i_a^*$  set by the control system.

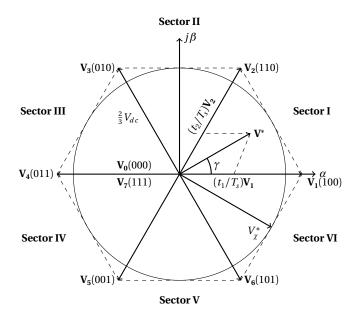

The switching states for the IGBTs are constricted to eight unique combinations. This is to ensure that the input lines cannot be shorted and continuous current flow is maintained. Each switching combination is illustrated as a vectors in figure 16. The *abc* three-phase reference frame is transformed to the  $\alpha$  and  $\beta$  reference frame by equation 3.62 and 3.63. The plane is given by six active vectors  $V_1, V_2, ..., V_6$  and two zero vectors  $V_0$  and  $V_7$  [25].

Figure 16: Space vector representation given by six active vectors and two zero vectors. Adapted from [21].

The active vector divide the plane in six sectors, where the reference vector  $\mathbf{V}^{\!*}$  is

obtained by two adjacent vectors. To control the magnitude of  $V^*$ , proper duty cycles are required for both the active adjacent vectors and the two zero vectors. The switching scheme for symmetrical modulation will be explained further in this text. The key advantages with this method is lower THD, due to the use of both zero vectors. The disadvantages is more switching losses compared to asymmetric modulation that only uses one zero vector, but also generate more THD. The general switching scheme with phase voltages and line voltages is shown in table 4. The phase voltages are calculated according to

$$V_{dc} \left( v_a \cos \gamma + v_\beta \sin \gamma \right) =$$

$$V_{dc} \left[ \cos \gamma \left( \frac{2}{3} v_a - \frac{1}{3} v_b - \frac{1}{3} v_c \right) + \sin \gamma \left( \frac{1}{\sqrt{3}} v_b - \frac{1}{\sqrt{3}} v_c \right) \right]$$

(3.67)

where  $\gamma$  is the angle referred to the  $\alpha$ -axis in figure 16. For symmetrical modulation

**Table 4:** Switching table for SVPWM. Note that the switches in each rectifier branch are complementary of each other. Adapted from [25].

| Vector        | $S_a^+$ | $S_b^+$ | $S_c^-$ | $S_a^-$ | $S_b^-$ | $S_c^-$ | v <sub>a</sub>       | $v_b$                | $\nu_c$              | v <sub>ab</sub> | $v_{bc}$        | V <sub>ca</sub> |

|---------------|---------|---------|---------|---------|---------|---------|----------------------|----------------------|----------------------|-----------------|-----------------|-----------------|

| $V_0 = (000)$ | off     | off     | off     | on      | on      | on      | 0                    | 0                    | 0                    | 0               | 0               | 0               |

| $V_1 = (100)$ | on      | off     | off     | off     | on      | on      | $\frac{2}{3}V_{dc}$  | $-\frac{1}{3}V_{dc}$ | $-\frac{1}{3}V_{dc}$ | V <sub>dc</sub> | 0               | $-V_{dc}$       |

| $V_2 = (110)$ | on      | on      | off     | off     | off     | on      | $\frac{1}{3}V_{dc}$  | $\frac{1}{3}V_{dc}$  | $-\frac{2}{3}V_{dc}$ | 0               | V <sub>dc</sub> | $-V_{dc}$       |

| $V_3 = (010)$ | off     | on      | off     | on      | off     | on      | $-\frac{1}{3}V_{dc}$ | $\frac{2}{3}V_{dc}$  | $-\frac{1}{3}V_{dc}$ | $-V_{dc}$       | V <sub>dc</sub> | 0               |

| $V_4 = (011)$ | off     | on      | on      | on      | off     | off     | $-\frac{2}{3}V_{dc}$ | $\frac{1}{3}V_{dc}$  | $\frac{1}{3}V_{dc}$  | $-V_{dc}$       | 0               | V <sub>dc</sub> |

| $V_5 = (001)$ | off     | off     | on      | on      | on      | off     | $-\frac{1}{3}V_{dc}$ | $-\frac{1}{3}V_{dc}$ | $\frac{2}{3}V_{dc}$  | 0               | $-V_{dc}$       | V <sub>dc</sub> |

| $V_6 = (101)$ | on      | off     | on      | off     | on      | off     | $\frac{1}{3}V_{dc}$  | $-\frac{2}{3}V_{dc}$ | $\frac{1}{3}V_{dc}$  | V <sub>dc</sub> | $-V_{dc}$       | 0               |

| $V_7 = (111)$ | on      | on      | on      | off     | off     | off     | 0                    | 0                    | 0                    | 0               | 0               | 0               |

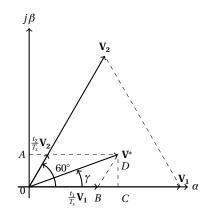

let's consider the reference vector  $V^*$  in figure 16. To determine the switching time duration of sector I, the reference vector is decomposed and multiplied with a given duty cycle according to

$$\int_{0}^{T_{s}} \mathbf{V}^{*} dt = \int_{0}^{t_{0}} \mathbf{V}_{0} dt + \int_{t_{0}}^{t_{0}+t_{1}} \mathbf{V}_{1} dt + \int_{t_{0}+t_{1}}^{t_{0}+t_{1}+t_{2}} \mathbf{V}_{2} dt + \int_{t_{0}+t_{1}+t_{2}}^{T_{s}} \mathbf{V}_{7} dt$$

(3.68)

$$\mathbf{V}^{*} = \mathbf{V}_{\mathbf{0}} \frac{t_{0}}{T_{s}} + \mathbf{V}_{\mathbf{1}} \frac{t_{1}}{T_{s}} + \mathbf{V}_{\mathbf{2}} \frac{t_{2}}{T_{s}} + \mathbf{V}_{7} \frac{t_{7}}{T_{s}} = \mathbf{V}_{\mathbf{1}} \frac{t_{1}}{T_{s}} + \mathbf{V}_{\mathbf{2}} \frac{t_{2}}{T_{s}}$$

(3.69)

$t_1$ ,  $t_2$ ,  $t_0$  and  $t_7$  are the time each respective switch is turned on and  $T_s$  is the switching time period. To determine the duty cycles,  $|\mathbf{V_1}|$  and  $|\mathbf{V_2}|$  has to be calculated

Figure 17: Adjacent boundary vectors in sector I.

first. Sector I is enhanced in figure 17 and the length of the reference vector  $|\mathbf{V}^*|$  is decomposed by

$$\frac{t_1}{T_s} |\mathbf{V}_1| = |\mathbf{V}^*| \cos \gamma - BC = |\mathbf{V}^*| \cos \gamma - DC \tan 30^\circ$$

$$= |\mathbf{V}^*| \cos \gamma - |\mathbf{V}^*| \sin \gamma \tan 30^\circ$$

$$= |\mathbf{V}^*| (\cos \gamma - \frac{1}{\sqrt{3}} \sin \gamma) = \frac{2}{\sqrt{3}} |\mathbf{V}^*| (\sin 60^\circ \cos \gamma - \cos 60^\circ \sin \gamma)$$

$$= \frac{2}{\sqrt{3}} |\mathbf{V}^*| \sin(60^\circ - \gamma)$$

$$\frac{t_2}{T_s} |\mathbf{V}_2| = \frac{AO}{\cos 30^\circ} = \frac{2}{\sqrt{3}} |\mathbf{V}^*| \sin \gamma$$

(3.70) (3.71)

The switching time for  $V_1$  and  $V_2$  are therefore given by

$$t_1 = \sqrt{3} T_s m_a \sin(60^\circ - \gamma)$$

(3.72)

$$t_2 = \sqrt{3}T_s m_a \sin(\gamma) \tag{3.73}$$

since  $|\mathbf{V}_1| = |\mathbf{V}_2| = \frac{2}{3}V_{dc}$  and  $m_a = \frac{|\mathbf{V}^*|}{V_{dc}}$ . The angle  $\gamma$  in sector I is restricted by  $\gamma \in [0^\circ, \dots, 60^\circ]$ .

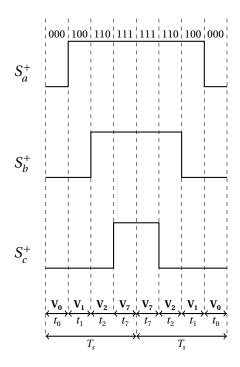

The switching pattern of  $V^*$  in sector I is shown in figure 18. The two zero vectors  $V_0$  and  $V_7$  are included to reduce THD and the magnitude of  $V^*$ .

In principle, the generation of reference vectors in the five other sectors are much

**Figure 18:** Pulse pattern of vectors in sector **I**. After the first switching period  $T_s$  is completed, the switching combination is reversed. Adapted from [25].

alike. The active voltage vectors are given by

$$\mathbf{V}_{\mathbf{k}}^{*} = \begin{cases} \frac{2}{3} V_{s} e^{j(k-1)\frac{\pi}{3}} & \text{if } k = 1, 2, \dots, 6\\ 0 & \text{if } k = 0 \text{ or } k = 7 \end{cases}$$

(3.74)

The angle  $\gamma$  between the adjacent vectors  $\mathbf{V}_k$  and  $\mathbf{V}_{k+1}$  in sector k is calculated by

$$\gamma = \arctan\left(\frac{V_{\beta}}{V_{\alpha}}\right) \tag{3.75}$$

and the magnitude of the voltage vector

$$|\mathbf{V}^*| = \sqrt{V_{\alpha}^2 + V_{\beta}^2} \tag{3.76}$$

$V_{\alpha}$  and  $V_{\beta}$  are calculated by the control system and will be discussed in section 4.1. The duration of  $t_1$  and  $t_2$  are generally expressed by

$$t_1 = \sqrt{3} T_s m_a \sin(k60^\circ - \gamma)$$

(3.77)

$$t_2 = \sqrt{3}T_s m_a \sin(\gamma - k60^{\circ})$$

(3.78)

Calculation of  $t_0$  and  $t_7$  are given by

$$t_0 = t_7 = \frac{T_s - t_1 - t_2}{2} \tag{3.79}$$

The switching time for each sector is given in table 5 [25].

Table 5: Switching times for sector I to VI.

| Sector | Switches branch a                   | Switches branch b                   | Switches branch c                   |

|--------|-------------------------------------|-------------------------------------|-------------------------------------|

| Ι      | $S_a^+ = t_1 + t_2 + \frac{t_0}{2}$ | $S_b^+ = t_2 + \frac{t_0}{2}$       | $S_c^+ = \frac{t_0}{2}$             |

| 1      | $S_a^- = \frac{t_0}{2}$             | $S_b^- = t_1 + \frac{t_0}{2}$       | $S_c^- = t_1 + t_2 + \frac{t_0}{2}$ |

| п      | $S_a^+ = t_1 + \frac{t_0}{2}$       | $S_b^+ = t_2 + \frac{t_0}{2}$       | $S_c^+ = \frac{t_0}{2}$             |

|        | $S_a^- = t_2 + \frac{t_0}{2}$       | $S_b^- = \frac{t_0}{2}$             | $S_c^- = t_1 + t_2 + \frac{t_0}{2}$ |

| III    | $S_a^+ = \frac{t_0}{2}$             | $S_b^+ = t_1 + t_2 + \frac{t_0}{2}$ | $S_c^+ = t_2 + \frac{t_0}{2}$       |

|        | $S_a^- = t_1 + t_2 + \frac{t_0}{2}$ | $S_b^- = \frac{t_0}{2}$             | $S_c^- = t_1 + \frac{t_0}{2}$       |

| IV     | $S_a^+ = \frac{t_0}{2}$             | $S_b^+ = t_1 + \frac{t_0}{2}$       | $S_c^+ = t_1 + t_2 + \frac{t_0}{2}$ |

| 1V     | $S_a^- = t_1 + t_2 + \frac{t_0}{2}$ | $S_b^- = t_2 + \frac{t_0}{2}$       | $S_c^- = \frac{t_0}{2}$             |

| v      | $S_a^+ = t_2 + \frac{t_0}{2}$       | $S_b^+ = \frac{t_0}{2}$             | $S_c^+ = t_1 + t_2 + \frac{t_0}{2}$ |

|        | $S_a^- = t_1 + \frac{t_0}{2}$       | $S_b^- = t_1 + t_2 + \frac{t_0}{2}$ | $S_c^- = \frac{t_0}{2}$             |

| VI     | $S_a^+ = t_1 + t_2 + \frac{t_0}{2}$ | $S_b^+ = \frac{t_0}{2}$             | $S_c^+ = t_1 + \frac{t_0}{2}$       |

| VI     | $S_a^- = \frac{t_0}{2}$             | $S_b^- = t_1 + t_2 + \frac{t_0}{2}$ | $S_c^- = t_1 + \frac{t_0}{2}$       |

The maximum amplitude of the reference vector before overmodulation mode is restricted by the radius of the circle in figure 16 and is expressed by

$$V_{\chi}^* = \frac{2}{3} V_{dc} \cos 30^\circ = \frac{V_{dc}}{\sqrt{3}}$$

(3.80)

Exceeding  $V_{\chi}^*$  causes over modulation and will not be discussed further.

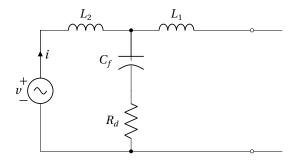

## 4 Design of the onboard rectifier system

The design of the onboard charging system is limited to the design of an AFE rectifier system with UPF consideration. To satisfy the demands from BKK in regards to the voltage quality, the design must satisfy the limits in table 2. Voltage drops must not increase beyond the demand mentioned in supply safety regulation [4] and in section 1.1. From the ferry owner perspective the demand for high efficiency and UPF is also taken in consideration. This section explains two different AFE rectifier systems based on VOC with L-filter and LCL-filter design.

## 4.1 Voltage orientated control

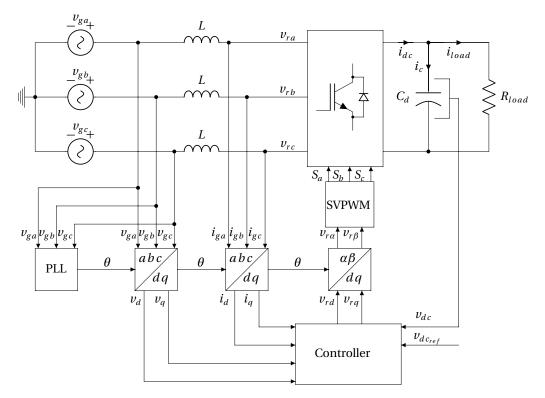

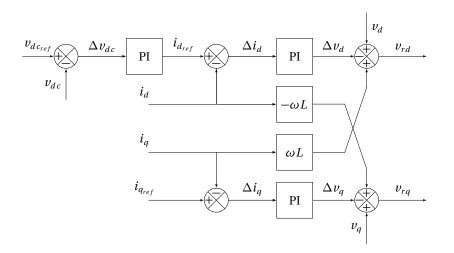

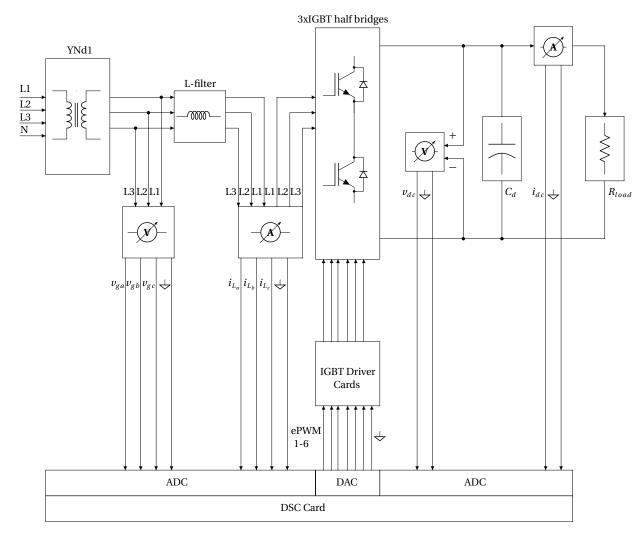

VOC is based on the transformation from a three-phase stationary reference frame to a synchronously rotating reference frame. The block scheme for the VOC AFE rectifier system is illustrated in figure 19. The grid currents  $(i_{ga}, i_{gb}, i_{gc})$  and voltages  $(v_{ga}, v_{gb}, v_{gc})$  are measured and transformed to dc values according to the Clarke and Park transformation explained in section 3.3.1. To obtain correct angular position  $\omega t$  is a phase lock loop (PLL) implemented. If the grid experiences frequency deviations from nominal value (50Hz), regulates the PLL  $\omega t$  according to the deviation. Dc voltage  $v_{dc}$  is measured on the dc side of the rectifier and is fed to the controller with the grid side values included a reference value for the dc voltage  $v_{dc_{ref}}$ . The controller's outputs  $v_{rd}$  and  $v_{rq}$  are transformed to a two-phase stationary reference system explained in section 3.3.1.  $v_{ra}$  and  $v_{r\beta}$  is fed to the SVPWM module which generates switching signals to the IGBTs.

The mathematical model from the block scheme in figure 19 are derived from KVL and KCL and are expressed as

$$\begin{bmatrix} v_{ga} \\ v_{gb} \\ v_{gc} \end{bmatrix} = L \frac{d}{dt} \begin{bmatrix} i_{ga} \\ i_{gb} \\ i_{gc} \end{bmatrix} + \begin{bmatrix} v_{ra} \\ v_{rb} \\ v_{rc} \end{bmatrix}$$

(4.1)

**Figure 19:** Configuration of VOC AFE rectifier with L-filter. The controller is described in detail in figure 20. Adapted from [21].

$$C\frac{d_{v_{dc}}}{dt} = (S_a i_{ga} + S_b i_{gb} + S_c i_{gc}) - i_{load}$$

(4.2)

where  $S_a$ ,  $S_b$  and  $S_c$  are the switching signal to the gate terminal on each IGBT branch. The switching signal is either one or zero. Equation 4.1 and 4.2 can be transformed by the Clarke transform described in equation 3.62-3.63 and thus yielding

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = L \frac{d}{dt} \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} v_{r\alpha} \\ v_{r\beta} \end{bmatrix}$$

(4.3)