# Design of an Embedded Readout System for the ALOFT Gamma-Ray Detector Instrument

A thesis by

Mats Fredrik Heigre

for the degree of

Master of Science in Physics

Department of Physics and Technology

University of Bergen

September 2018

#### Abstract

Birkeland Center for Space Science has proposed a campaign known as the Airborne Lightning Observatory for FEGS & TGFs (ALOFT) to study Terrestrial Gamma-Ray Flashes (TGFs). TGFs are the most energetic natural phenomena occurring in the Earth's atmosphere, and are important to our knowledge about the relationship between the Earth and space. The ALOFT campaign will use a gamma-ray detector instrument built by the University of Bergen which will be mounted to the NASA ER-2 High-Altitude Airborne Science Aircraft.

This work covers the design and development of the embedded software used to offload and operate the detector readout system of said instrument. A similar instrument was built and flown in 2017. The new instrument differs from this by being implemented on a System on a Chip (SoC) embedded platform, reusing relevant modules from the old instrument. The software has been implemented with the FreeRTOS Realtime Operating System (RTOS). Design considerations to limit complexity, and the impact of the radiation environment the instrument is to be operated in, has been performed trough implementation of a checksum algorithm, cyclic rewriting of registers, and modular design strategies.

A verification system has been realized with a prototype hardware setup, in which test systems has been added to process synthetic TGF-events in the software and hardware. Test with emulated data and a Telnet control interface has been successfully implemented. The current implementation focuses on modularity, and thus offers a very good framework for further development of the instrument when campaign specifications are decided.

# Preface

The following work was accomplished at the Department of Physics and Technology at the University of Bergen in the period between August 2017 and September 2018. The work of this thesis marked an unofficial beginning of the development of ALOFT, and thus no information and documentation existed except for that of the FEGS-II campaign. Developing such a complex system was done without much prior experience, and no hands-on experience with the C programming language and embedded systems was present at the beginning of the work.

# Acknowledgments

First and foremost, my two supervisors Associate Professor Johan Alme and Professor Kjetil Ullaland, have both inspired and influenced my work, in which i would like to express my deepest gratitude. During the work, a personal highlight was witnessing the UiB-built MXGS instrument being launched to the International Space Station. Getting to work in an environment with the passion witnessed from both the space physics group and the microelectronics group that day, has been one of the most rewarding experiences during my stay at the University of Bergen.

On the work related to the space physics, much of it would not have been possible without the help I received from Associate Professor Martino Marisaldi and PhD Candidate Chris Alexander Skeie. Senior Engineer Shiming Yang has provided invaluable insight into the FEGS BGO instrument, and Researcher Boris Wagner gave advices which helped during the steep learning curve of learning to program in a new language.

I would like to express my gratitude for my fellow co-workers whom I shared office with at room 312, and other PhD candidates from the microelectronics group. I hope I will be able to stay in contact with all of you as these two years have been a very enjoyable experience. I would also like to thank my family and friends for keeping my spirit high. Especially *Alexander Nikolai Nesse*, *Hogne Andersen*, and *Håvard Skibenes* have played central roles to this. An extra special thanks goes to *Chris Alexander Skeie*, *Magnus Rentsch Ersdal*, and *Martino Marisaldi*, for proofreading both during the drafting period and final revisions.

Most importantly, my lovely *Marie Aadland* has provided me with encouragement and support. Thank you for always being there. This work would really not have been without you.

Mats Fredrik Heigre

# Contents

|          | Prefa | ace                                                       | ii         |

|----------|-------|-----------------------------------------------------------|------------|

|          | Nom   | $enclature \ . \ . \ . \ . \ . \ . \ . \ . \ v$           | ii         |

| A        | crony | ms i                                                      | x          |

| 1        | Intr  | oduction                                                  | 1          |

|          | 1.1   | History                                                   | 1          |

|          | 1.2   | Background and Motivation                                 | 2          |

|          | 1.3   | Objective of this Thesis                                  | 2          |

|          | 1.4   | Thesis Outline                                            | 3          |

|          | 1.5   | Citation Principles                                       | 4          |

| <b>2</b> | Higl  | n-Energy Atmospheric Phenomena and the Radiation Environ- |            |

|          | men   |                                                           | <b>5</b>   |

|          | 2.1   | Terrestrial gamma-ray flashes                             | 5          |

|          | 2.2   |                                                           | 0          |

|          | 2.3   |                                                           | 1          |

|          | 2.4   |                                                           | 4          |

|          | 2.5   | Radiation Design Considerations for ALOFT                 | 6          |

| 3        | FEG   | S BGO Instrument - Readout System 1                       | 9          |

|          | 3.1   | System Architecture                                       | 9          |

|          | 3.2   | BGO Data Acquisition Unit                                 | 20         |

|          | 3.3   | Readout Control Unit                                      | 21         |

|          | 3.4   | Data Processing Unit                                      | 23         |

|          | 3.5   | Operation of FEGS BGO during Flight Campaigns 2           | 25         |

|          | 3.6   | Review                                                    | 25         |

| 4        | ΔΤ.   | 0FT Design 2                                              | 27         |

| •        | 4.1   |                                                           | 27         |

|          | 4.2   | • -                                                       | 28         |

|          |       | · ·                                                       | 30         |

|          | 4.4   |                                                           | <b>B</b> 1 |

|          | 4.5   | - 0 0                                                     | 32         |

|          | 4.6   | 0                                                         | <b>3</b> 4 |

|          | 4.7   | *                                                         | <b>3</b> 4 |

|          | 4.8   | -                                                         | 35         |

|          | 4.9   | -                                                         | 35         |

|          |       |                                                           | <b>3</b> 6 |

|          | 1.10  |                                                           | 0          |

|              | 4.11 GPS interface                                                                                                              |                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

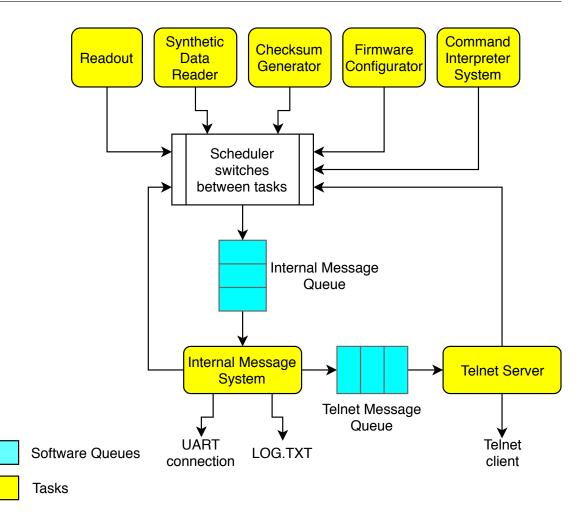

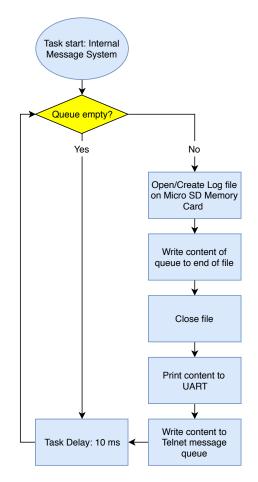

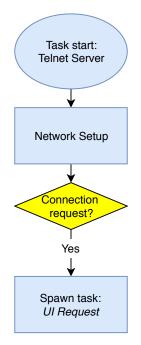

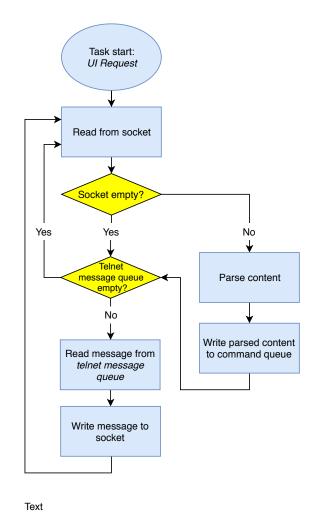

| 5            | Embedded Readout Development5.1System architecture                                                                              | <b>39</b><br>39<br>42<br>44<br>47<br>51<br>52<br>56<br>59<br>61 |

| 6            | Testing6.1Prerequisites for the tests6.2Synthetic data read-in6.3Test of Readout6.4Test of System in Stand-Alone Mode6.5Summary | <b>63</b><br>64<br>66<br>67<br>69<br>70                         |

| 7            | Conclusion and Outlook7.1Conclusion                                                                                             | <b>71</b><br>71<br>72                                           |

| A            | ppendices                                                                                                                       | 75                                                              |

| $\mathbf{A}$ | Coding Style                                                                                                                    | 77                                                              |

| В            | Git Repository - Directory Tree                                                                                                 | 79                                                              |

| С            | Methodology and Software OverviewC.1C.2Debugging and Version Control                                                            | <b>81</b><br>81<br>81                                           |

| D            | Operating manual                                                                                                                | 83                                                              |

| Ε            | Command Sheet & System Message CodesE.1Command Sheet                                                                            | <b>85</b><br>85<br>85                                           |

| F            | TutorialsF.1FreeRTOS Bootloader generation in Xilinx SDKF.2Example project with AXI4 Lite peripheral on the Zynq-7000           | <b>89</b><br>89<br>89                                           |

# Acronyms

**ADC** Analog to Digital Converter.

**ALOFT** Airborne Lightning Observatory for FEGS & TGFs.

**ASIM** Atmosphere-Space Interactions Monitor.

**BATSE** Burst and Transient Source experiment.

**BGO** Bismuth Germanate Oxide.

**BRAM** Block RAM.

CGRO Compton Gamma Ray Observatory.

CMOS Complementary Metal-Oxide Semiconductor.

**DAU** Data Acquisition Unit.

**DHCP** Dynamic Host Configuration Protocol.

**DMA** Direct Memory Access.

**DPU** Data Processing Unit.

**DRAM** Dynamic RAM.

ECP Cockpit Experiment Control Panel.

EGSE Electric Ground Support Equipment.

**FEGS** Fly's Eye GLM Simulator.

FEGS BGO Fly's Eye GLM Simulator (FEGS) Bismuth Germanate Oxide (BGO).

FIFO First In First Out.

FPGA Field Programmable Gate Array.

**FSBL** First Stage Boot Loader.

GOES-R Geostationary Operational Environmental Satellite-R.

- **GPIO** General Purpose I/O.

- GUI Graphical User Interface.

- **IP** Internet Protocol.

- **ISR** Interrupt Service Routine.

- LEO Low Earth Orbit.

- LVDS Low Voltage Differential Signaling.

- LwIP Light-weight Internet Protocol.

- MIO Multiplexed I/O.

- **MMIA** Modular Multi-spectral Imaging Array.

- MUX Multiplexer.

- MWC Memory Write Command.

- MXGS Modular X- and Gamma-ray Sensor.

- **NOAA** National Oceanic and Atmospheric Administration.

- **PMT** Photomultiplier Tube.

- **PPS** Pulse Per Second.

- **RAM** Random Access Memory.

- **RCU** Read-Out Control Unit.

- **RDP** Remote Desktop Protocol.

- **RHESSI** Reuven Ramaty High Energy Solar Spectroscopic Imager.

- **RREA** Relativistic Runaway Electron Avalanche.

- **RTOS** Realtime Operating System.

- SCDP Scientific Data Packet.

- **SEE** Single-Event Effect.

- **SLC** Single Level Cell.

- SoC System on a Chip.

- **SPI** Serial Peripheral Interface.

- SRAM Static RAM.

- TCP Transmission Control Protocol.

- **TGF** Terrestrial Gamma Ray Flash.

- **TLC** Tripple Level Cell.

- **TLE** Transient Luminous Event.

- **UART** Universal Asynchronous Receiver-Transmitter.

- ${\bf UDP}~{\rm User}$  Datagram Protocol.

- ${\bf USB}\,$  Universal Serial Bus.

### Chapter 1

# Introduction

### 1.1 History

Lightning and its loud vibrant sound is something most people are familiar with. Ancients believed the bolt of light coming down from the heavens was a sign of furious and enraged gods, such as Thor from Norse mythology and Zeus from Greek mythology. It was not until the 16th century that the true nature of this phenomenon was revealed. The legend has it that Benjamin Franklin was the one who conducted the experiment resulting in the scientific breakthrough. The experiment consisted of a kite attached to a leyden jar using a silk string, an iron key, and some thin metal wire. The goal was to confirm the hypothesis that lightning was an electric phenomenon, by accumulating charge into the leyden yar.

In 1845 Michael Faraday linked electromagnetic radiation with electromagnetism by showing that polarized light traveling through transparent materials responded to magnetic fields. This discovery was later in the 1860s explained by James Clerk Maxwell through four equations that unified electricity and magnetism as the same force. It explained how a time-varying electric field acts as a magnetic field, *the electromagnetic spectrum*.

Then, in 1886 so called "whistlers" were heard on a 22 km telephone line in Austria. These "whistlers" are *Very Low Frequency* radio signals now associated with lightning discharges. They are audible in audio-frequency range as alternating whisteling from a high to low frequency of about 1000 cycles per second. [1]

This brought on a new type of radio science, and with it, a tool to unlock the mysteries of thunderclouds was born.

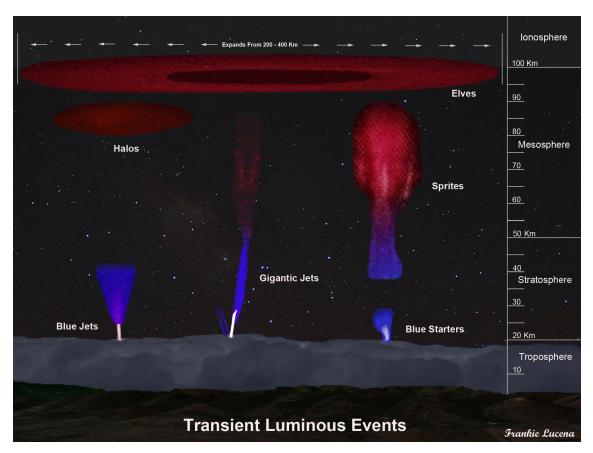

Over the time it has been realized that lightning is not the only electric phenomena occurring in the Earths atmosphere. Transient Luminous Events are one type of such phenomena. TLEs happen at a much greater altitude than regular lightning and have the property of being visible to the naked eye just as lightning, although very faint. Due to their relatively short duration, actually spotting them without any equipment can be hard. Figure 1.1 displays a compilation of various photographed TLEs and their relative sizes. Although visually impressive, there is no evidence that TLEs emit any energetic radiation [2].

Figure 1.1: A compilation of various photographed TLEs and their relative sizes. *Credits: Frankie Lucena, Spaceweathergallery.com*

# 1.2 Background and Motivation

Understanding the relationship between the Earth's magnetic field and the atmosphere is the primary goal of the *Birkeland Center for Space Science*. Currently, four different groups of scientists are working on separate research areas to understand this relationship.

The focus of one of the groups is to understand the mechanism behind gamma radiation detected from thunderclouds. By flying aircraft and spacecraft platforms equipped with scientific instruments above thunderclouds, the goal is to understand high-energetic natural occurring phenomena of the atmosphere, such as Transient Luminous Events and *Terrestrial Gamma Ray Flashes*, or TGFs for short.

Detecting these phenomena is non-trivial, as they are happening on a sub-microsecond scale. Thus, building detectors with fast readout systems that can sustain the harsh environments found in and at the edge of space, are required to properly resolve the event spectra.

# 1.3 Objective of this Thesis

The primary scope of this thesis is to initiate the process of developing and designing software for an embedded readout system for the Airborne Lightning Observatory

for FEGS & TGFs (ALOFT). ALOFT is an instrument which will be built by the University of Bergen, and its primary goal is to aid in the study of Terrestrial Gamma Ray Flashes. ALOFT will also be used to study other weaker atmospheric phenomena.

ALOFT will be very similar to the FEGS BGO instrument which flew in the summer of 2017 on the NASA ER-2 High-Altitude Airborne Science Aircraft. FEGS BGO is a scintillator based instrument with a decentralized readout system. ALOFT will also be scintillator based, but implemented on a single embedded System on a Chip (SoC) platform. The SoC will contain a processor, and programmable logic in the form of an FPGA module. This thesis will primarily focus on the software executed on the processor.

The instrument will be flown at an altitude of 20 km, and thus will be operated in an environment with higher radiation levels than the ones found at ground levels. Determining the severity of this environment's impact on the electronics used in the instrument, and making design considerations accordingly, if any, should be done.

This thesis aims to define which parts of the instrument that should be implemented on the programmable system. As many as possible of these functions are also implemented. The instrument must be able to store the data gathered by the detectors to a storage device. The bandwidth of the write operation to the storage device must exceed the expected maximum data rate of 1.98 MB/s. A user interface accessible trough ethernet for instrument control, should be implemented. The status of the system should also be logged to a log file on the storage device, for retrieval postflight. A test system should be implemented by which synthetic data can be read from a file, and used to simulate data output from the scintillator detectors. Feasibility of implementing the software in an operating system environment contrary to a bare bone environment should also be studied.

When successfully implemented, the end product is a system capable of receiving data from a synthetic data file, process it the same way as the FEGS BGO instrument, and store it on a storage device. Albeit implemented on a single SoC, using less power and with higher performance and reliability.

### 1.4 Thesis Outline

#### Chapter 2: High-Energy Atmospheric Phenomena and the Radiation Environment

The first part of this chapter provides the necessary background to give a brief understanding of the physics behind TGFs. This is required to understand the type and usage of instrumentation which is described in the second part of the chapter. The second part also covers some of the campaigns which are currently used in research related to TGFs. In the third part, the radiation environment at the operating altitudes of ALOFT, and its impact on the electronics of ALOFT are investigated.

#### Chapter 3: FEGS BGO Instrument - Readout System

This chapter provides a summary of the readout system and Electric Ground Support Equipment (EGSE) of the FEGS BGO instrument. The chapter is provided due to the importance of the FEGS BGO instrument to the design of ALOFT, and should give a better understanding of the parts or functionalities migrated to ALOFT.

#### Chapter 4: ALOFT Design

This chapter provides a comprehensive discussion and documentation for the hardware and software to be used in the ALOFT readout system. The chapter covers the system requirements, elaborates on the choice of hardware and software, reuse of parts from FEGS BGO, and gives an introduction to the operating system being used by the readout system.

#### Chapter 5: Embedded Readout Development

This chapter documents the software side of the readout system, along with the readout architecture. The chapter aims at giving an in-dept understanding of how the different software modules work, and documents the overall software architecture.

#### Chapter 6: Testing

This chapter covers the testing of the system, along with the results and a description of setups used when performing the tests.

#### Chapter 7: Conclusion and Outlook

In this chapter the ALOFT readout system with emphasis on the software side is reviewed. Results from chapter 6 are discussed, and a conclusion is provided. The chapter also includes information on work that is yet to be completed, or should be implemented based on the conclusion.

#### Appendices

This part of the thesis contains appendices which contains extra details of how the system works. They can prove useful for an operator of ALOFT, or for future developers to review the system.

### 1.5 Citation Principles

Citation principles for this thesis are that all references that are listed before the sentence punctuation is a reference to the original content of the information provided in that specific sentence only. References after a sentence punctuation are referring to the information provided in all the sentences prior to the reference, up to the last reference, or beginning of the paragraph. For larger sections containing multiple paragraphs that all uses the same reference only, a small text is provided which cites the reference.

#### Chapter 2

# High-Energy Atmospheric Phenomena and the Radiation Environment

# 2.1 Terrestrial gamma-ray flashes

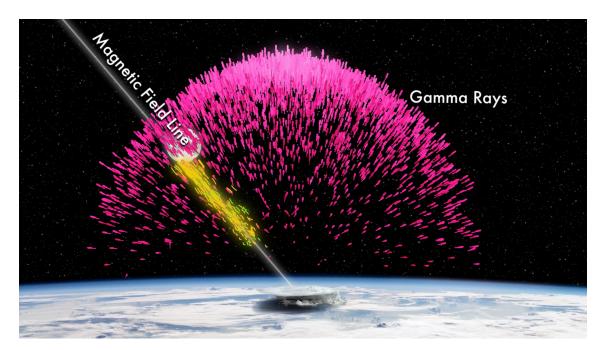

In 1991, scientists discovered something strange. The Compton Gamma Ray Observatory (CGRO) along with its payload Burst and Transient Source experiment (BATSE), originally intended to measure photons from galactic gamma-flashes picked up signals coming from the Earth [3]. The gamma-ray flashes BATSE observed originated from thunderclouds down on Earth. Although energetic radiation had previously been detected radiating from thunderclouds, this was a brand new phenomenon [4]. The Terrestrial Gamma Ray Flash (TGF) had been discovered. Figure 2.1 gives an artists illustration of how a TGF may appear. Gamma radiation (pink) is being radiated into space, and electrons (yellow) and positrons (green) lines up to follow along the Earths magnetic field lines due to them having electric charge.

Figure 2.1: An artists illustration of a TGF event. The TGFs originates from regions lower than 20 km and typical duration is in the order of a millisecond [2, chap. 4.1, 4.6]. Gamma-rays in pink, electrons in yellow, and positrons in light green. *Credits:* NASA

#### 2.1.1 Origin of runaway electrons

The following section is based on [2].

The most common mechanism for generating energetic radiation such as x- and gamma-rays in the atmosphere, is through *bremsstrahlung*. Other mechanisms exist as well, such as nuclear decay. In the atmosphere bremsstrahlung occurs between so-called *runaway free electrons* and the atoms present in air. Runaway electrons are electrons with a high amount of kinetic energy. Actually they are so energetic that they behave relativistic. Bremsstrahlung will be further explained in section 2.1.2.

The runaway mechanism was first proposed in 1925 by C.T.R Wilson. He discovered that electrons could become high-energetic when placed in electric fields. If the energy gained from the field exceeded the loss from interacting with other particles in the air, the electron will "run away". Electric fields where the energy gain becomes positive is known as break-even fields, and can be calculated by equation 2.1 where n is the relative air density compared to that of sea level.

$$E_b = 2.18 \cdot 10^5 V/m \cdot n \tag{2.1}$$

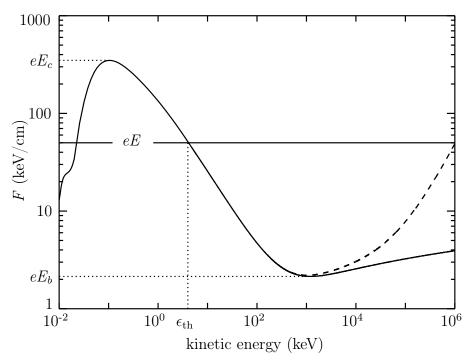

For runaway electrons to propagate large distances, a field strength about 30% higher than  $E_b$  is required. This field strength is at comparable level to the maximum field strengths seen in thunderclouds. The graph in figure 2.2 shows energy loss of an electron per unit length as a function of kinetic energy. Energy loss comes from the effective frictional force. eE (horizontal line) shows the force produced by a strong

electric field. For an electron to reach a "runaway state", the loss from frictional forces must be less than the energy gained. This is the case when the kinetic energy of an electron surpasses the energy threshold  $\epsilon_{\rm th}$ . Such electrons are often referred to as "seed" electrons.

Figure 2.2: The effective frictional force experienced by a free electron (or positron) moving through air at standard temperature and pressure as a function of kinetic energy. [2].

It is suggested that seed electrons are provided by cosmic radiation- or radioactive decay-sources. The seed electrons may cause an electron avalanche known as a Relativistic Runaway Electron Avalanche (RREA). RREAs result in runaway of a high number of electrons. However, if the electric field strength exceeds the maximum frictional force  $eE_c$ , all free electrons may runaway without the need of an external seed particle. This is known as "cold" or "thermal" runaway, and is thought to happen during the propagation of lightning.

#### 2.1.2 Bremsstrahlung

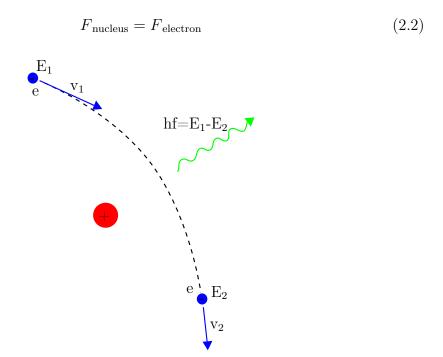

One very interesting property of matter can be observed when a fast moving electron such as a runaway electron gets within close proximity of an atomic nucleus. As the nucleus has a positive electric charge and the electron is negative, the coulomb force will make the electron and the nucleus attract each other [5, p. 154]. Comparing the mass of a nucleus with that of an electron, the former is larger by order of magnitudes. When applying Newton's third law (2.2), it becomes evidently that the electron will undergo the greatest deviation from its state of movement when in the electrical field of the nucleus. The path of the electron will start curving towards the nucleus. Velocity is a vector quantity consisting of speed and direction, meaning that the electron experiences a change in velocity although the speed is constant. This radial acceleration produces some captivating properties, as the electron starts emitting electromagnetic radiation. It should be noted that when the emission happens, the electron speed is decreased to keep the conservation of energy. [6, cap. 34-5].

Figure 2.3: Relativistic electron passing by a positive nucleus, resulting in Bremsstrahlung-emission. Illustration by Trex2001 under public domain.

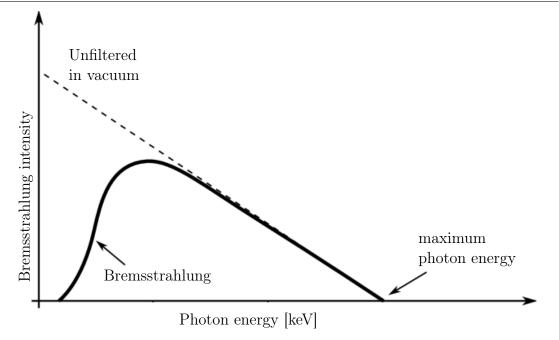

This type of radiation is known as breaking radiation, or by its more common german name *bremsstrahlung*. The amount of energy the photon obtains from the incoming electron depends only on the kinetic energy of the electron, and its distance to the nucleus when passing. The closer the electron gets to the nucleus, the more energy gets released via the photon. As there are almost endless combinations of distances and electron energies, the energy of bremsstrahlung emissions take form of a continuous spectrum as seen in figure 2.4 with low energies being the most abundant. This is caused by electrons having a higher probability to pass a nucleus from a larger distance, thus giving off less energy. [7]

Figure 2.4: Bremsstrahlung intensity as a function of photon energy. The maximum photon energy is limited by the incoming photon's energy loss when passing the nucleus. The sharp decrease in low energy emission is due to absorption in the detector materials. [7]

Usually photons produced by bremsstrahlung are classified as x-rays. The classification comes from it being an energetic photon with an energy exceeding 1 keV and the generating source is an electron. If the source of generation is from nuclear decay, the high energetic photons are called gamma-rays. [2] An alternative classification is to categorize gamma-rays as all photon energies above 1 MeV.

TGFs are the most energetic photon phenomenon with natural origin on Earth, with energies up to tens of MeV [8]. With such high energies, they are classified as gamma-rays, even though the source mechanism fits with the classification of x-rays. The energies does also extend down to tens of keV for less energetic events.

### 2.2 Instrumentation

This section covers the instrumentation used to detect the photon emissions coming from TGFs. The section source is primarily [9].

#### 2.2.1 Scintillators

Scintillators are a widely used material that combined with read-out and front-end electronics can be used as an instrument in high-energy physics research, dosimetry, medicinal physics, and environmental radiation protection. It takes use of a phenomenon known as luminescence which describes the illumination of a material without the material being heated. In scintillators, luminescence is caused by a particle that hits the scintillator medium. The particle passes through the medium and excites or ionizes some of the atoms in the medium. The excited atoms will emit photons upon deexcitation. The emitted photon energy range depends on the medium used, and the emitted light intensity is proportionally dependent on the energy deposited.

This way, scintillators are useful for converting deposited energy into light, or downconverting photon frequencies to values easier to survey. For this thesis, the gammaand x-ray photons emitted from TGFs are the incoming particles of interest. By the use of a scintillator with a medium of Bismuth Germanate Oxide (BGO), the large energy deposited by high frequency gamma- and x-ray photons can be converted to light in the near visible spectrum.

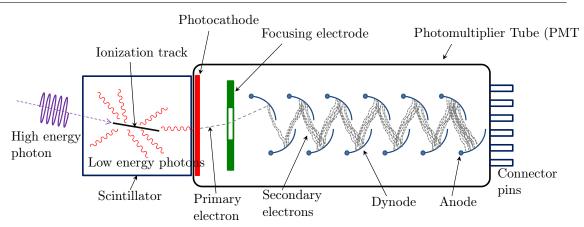

#### 2.2.2 Photomultiplier Tubes

Scintillators produces a number of low energy photons for each particle it gets bombarded with, and the goal now is to convert these photons into a sufficient strong electric signal so that it can be further handled. Figure 2.5 shows a schematic of a Photomultiplier Tube (PMT) connected to a scintillator that outputs low energy photons. PMTs converts the photons into electrons by the use of the photoelectric effect. When the photon is converted, multiple electrodes called dynodes accelerates the electrons towards the anode by means of a high voltage. When an electron bumps into the dynodes, it knocks loose more electrons and essentially causes an avalanche of electrons. These "new" electrons are known as secondary emission and increases the current measurable at the anode.

# CHAPTER 2. HIGH-ENERGY ATMOSPHERIC PHENOMENA AND THE RADIATION ENVIRONMENT

Figure 2.5: Schematic of a photomultiplier tube showing the inner workings and arrangement of components. As has been described, the primary electron causes an avalanche producing a lot of secondary electrons that increases the current at the anode. *Source: Wikipedia, Page name: Photomultiplier*

# 2.3 Research and Ongoing Campaigns

The Birkeland Center for Space Science located in Bergen is a Norwegian Center of Excellence with the objective of understanding the relationship and interactions between Earth and Space. There are currently two big science campaigns related to TGF detection and understanding, FEGS BGO and ASIM, with FEGS coming to an end. A new campaign, ALOFT, will continue were FEGS left off.

#### 2.3.1 Atmosphere-Space Interactions Monitor - ASIM

Figure 2.6: Computer aided design model of the Atmosphere-Space Interactions Monitor (ASIM) [10]

The Atmosphere-Space Interactions Monitor (ASIM) contains two instruments, the Modular X- and Gamma-ray Sensor (MXGS) and the Modular Multi-spectral Imaging Array (MMIA) seen in red and orange in figure 2.6. MXGS was developed at the Birkeland Center for Space Science and carries two sets of detectors for different energy ranges. The low energy detector is a 128 by 128 pixelated CZT (CdZnTe)-detector sensitive to the 15 keV to 400 keV spectral band. The pixelation combined with a coded mask in front of this detector makes it possible to determine the TGF source direction. For high energies, BGO detectors sensitive to the 200 keV to 40 MeV spectral band is used. [10]

One of the main questions for Atmosphere-Space Interactions Monitor (ASIM) to answer, is to find out how common TGFs are. BATSE detected 10 TGFs annually, while the Reuven Ramaty High Energy Solar Spectroscopic Imager (RHESSI) detected 100 annually [11]. ASIM was successfully launched and mounted to the Columbus module on the International Space Station in April 2018, with operations ongoing. With preliminary results, it will detect around 800 TGFs annually.

Figure 2.7: ASIM can be seen mounted on the far right of the Columbus module on the International Space Station in this illustration. *Credits: ESA Concurrent Design Facility*

#### 2.3.2 Fly's Eye Geostationary Lightning Mapper Simulator -FEGS-II

The Fly's Eye GLM Simulator (FEGS) instrument was originally built to test and validate lightning sensors to be used on National Oceanic and Atmospheric Administration (NOAA)'s Geostationary Operational Environmental Satellite-R (GOES-R) series of weather satellites. FEGS was mounted to a Lockheed ER-2 High-Altitude Airborne Science Aircraft operated by NASA, which flied over thunderclouds to validate the sensors. ER-2 is the civilian successor of the well famous U2 "dragon lady" aircraft called U-2S. It is capable of operating at mission altitudes exceeding 70,000 feet and thus can be flown above the originating altitudes of TGFs. [12]

# CHAPTER 2. HIGH-ENERGY ATMOSPHERIC PHENOMENA AND THE RADIATION ENVIRONMENT

The University of Bergen was offered some of the spare room allocated to FEGS to piggyback their own instrument. This has later been known as the FEGS BGO instrument. FEGS BGOs mission is to study TGFs along with other weaker atmospheric phenomena. It is built of three BGO-detectors of the same type as the MXGS instrument. FEGS flew during April and May 2017, with the data obtained from these flights having an ongoing review at the time this thesis was written.

Figure 2.8: The ER-2 aircraft during a NASA campaign. Credits: NASA

### 2.3.3 The Airborne Lightning Observatory for FEGS & TGFs - ALOFT

The Airborne Lightning Observatory for FEGS & TGFs (ALOFT) campaign is the successor of FEGS BGO and will use the same NASA ER-2 High-Altitude Airborne Science Aircraft platform to perform its mission. Even though the ASIM instrument is operational, there is still a lot of need for an aircraft mounted instrument. The main reason for this is that ASIM is in Low Earth Orbit (LEO) and therefore needs to peek through a lot of atmosphere to detect atmospheric phenomena. This dense atmosphere blocks out many of the dimmer phenomena.

With an instrument mounted to an aircraft, the distance between the detector and phenomena, and thus also the amount of atmosphere between them gets decreased. This means that a greater signal to noise ratio can be achieved, and ALOFT is therefore capable of detecting phenomena which would be bellow the noise floor of ASIM.

In this thesis, the name ALOFT will be referring to the BGO detector instrument which is developed in this thesis and flown in the ALOFT campaign. Technically, the correct name of the instrument would be a separate name in the ALOFT II suite, as the instrument suite of FEGS-II as a whole was named ALOFT. However, as no name has been given to the new instrument, and to avoid further confusion to anyone involved in the project, the single new BGO detector instrument will be referred to as ALOFT only.

#### 2.4 The Radiation Environment

As will be seen in section 2.5, radiation can cause many undesirable behaviours in electronics. There are also very important considerations to make regarding the use of humans in radiation environments, for instance astronauts. Therefore, applications that are going to operate in radiation environments must be designed to tolerate the radiation exposure with satisfying results.

For high-altitude atmospheric and LEO space applications, there are many design similarities and considerations that can be made, as the environmental conditions regarding radiation are quite similar. These similar environmental conditions comes from both application taking place partially or totally outside of the atmosphere, which at lower altitudes would acts as a shield against high-energetic particles. As both applications are also within Earth's magnetic field, they are still shielded to some degree from high-energetic cosmic radiation.

The substantial source of radiation in an airborne or space-based instrument is cosmic radiation. Cosmic radiation is a collection of particles originating from the universe, with the Sun being the major contributor to the amount received on the Earth. The amount originating from the Sun can be seen heavily increased during a *Solar Particle Event*, such as a *flare* or *Coronal Mass Ejection*. Outside of the atmosphere, the cosmic radiation consists of 85% protons, 13%  $\alpha$ -particles, and 2% heavy ions. The received dose from cosmic radiation at 1600 and 5000 meters above sea level is twice and seven times the dose received at sea level, respectively. [13]

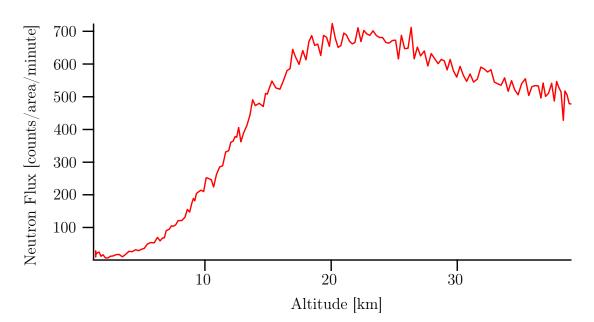

Some of these particles can cause problems by their own, but they can also interact with atoms in the atmosphere, causing secondary emission such as gamma-rays through bremsstrahlung, high-energetic neutrons, protons, and pions. Secondary emissions increases the total number of radiation particles as they go through the atmosphere, but at lower altitudes the atmospheric density is high enough to absorb most of the particles. This can be seen in figure 2.9 which shows the relative neutron flux as a function of altitude, obtained from a balloon flight experiment [14].

Figure 2.9: Neutron flux as a function of altitude, measured from a balloon flight experiment. The effects of secondary emissions and atmospheric absorption can clearly be seen. [14]

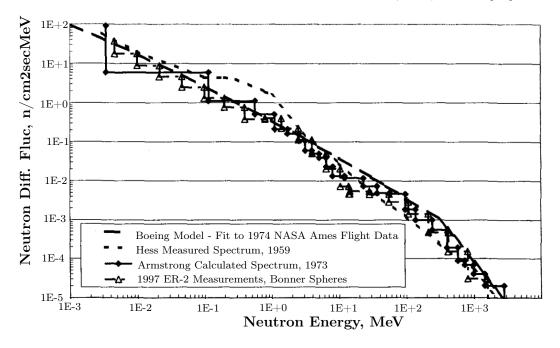

Neutrons have the highest flux of the secondary emission particles. Figure 2.10 shows the neutron energy spectrum measured and calculated at 40,000 Feet above ground [15]. At 60,000 Feet which is similar to the flight altitude of the ER-2 Aircraft, the neutron flux has been measured to be around 1.3 neutrons/cm<sup>2</sup>/second [16].

Figure 2.10: Neutron energy spectrum in the atmosphere at 40000 feet above sea level. [15]

As charged particles travels along the magnetic field lines of Earth's magnetic field,

radiation flux levels are higher at larger latitudes. Measurements at jet aviation altitudes during a solar minimum have shown a 2.5 to 5 times increase in radiation flux, in the polar regions compared with flights at equatorial latitudes. [17]

# 2.5 Radiation Design Considerations for ALOFT

When designing an instrument to be operated at high altitudes or in space, proper consideration to the radiation environment must be taken to avoid the undesirable effects of radiation. During the 2017 FEGS-campaign the ER-2 aircraft was operated at 20 km altitude. The flight trajectory was between Georgia and Colorado in the Continental United States [18]. For this trajectory, radiation is evidently lower than a trajectory were the aircraft is flown at higher latitudes. However, as seen in section 2.4, any equipment at these altitudes will be exposed to much higher radiation intensity than at sea level. In addition to the radiation with cosmic origin, the ER-2 will also be exposed to the radiation originating from the TGFs. As was described in section 2.1.2, TGFs can have photon energies of tens of MeV. They do, however, have such a low occurrence that it it believed that their impact on the electronics can be neglected.

The effects of radiation can be divided into two categories; Long-term effects, and Single-Event Effect (SEE). As the name indicates, long-term effects happens over a longer time period than SEEs, and encompasses effects caused by the *Total Ionizing Dose* accumulated, and *displacement damages*. Displacement damages are not particularly applicable to Complementary Metal-Oxide Semiconductor (CMOS) microelectronics, and due to the relatively short mission periods of ALOFT, the long term effects are in general not applicable to the electronics discussed in this thesis and will therefore not be discussed further. [19]

#### 2.5.1 Single Event Effect (SEE)

SEEs are caused by the interaction with single charged particles and can cause great problems in electronics. Their effects can be divided into soft and hard errors. Soft errors are recoverable although they may have corrupted the data content in registers and other memory devices. Hard errors however, induces permanent damage to the device. [19]

Some hard error effects are *Latchup*, *Burnout*, and *Gate Rupture*. Latchups causes permanent loss of functionality due to low-resistance paths forming between  $V_{DD}$  and GND in CMOS chips. Limiting the occurrence of latchups can only be performed through changes to the CMOS design, and is therefore outside of the scope of this thesis. Burnouts and Gate rupture effects on sub-micron metal-oxide-semiconductor transistors are rare and minimal, but can contribute to a reduction in lifetime expectancy which is not important to ALOFT. [20]

#### Single-Event Upsets and Single-Event Transients

With the introduction of Dynamic RAM (DRAM) that used semiconductor technology in the 70's, vendors were perplexed with the discovery of bits on the devices randomly being flipped. Intel later identified the events being caused by  $\alpha$ -particles

# CHAPTER 2. HIGH-ENERGY ATMOSPHERIC PHENOMENA AND THE RADIATION ENVIRONMENT

originating from trace amounts of uranium and thorium in the microelectronics package colliding with the silicon. When an  $\alpha$ -particle strikes silicon, it generates an electron-hole as the particle loses energy. These electron-holes act as carriers, and if collected into the diffusion terminals of transistors, charge can be collected. This increase in charge causes a current spike which is known as a *Single-Event Transient*. If the charge is of comparable size to the node charge of the transistor, the bit value stored on the transistor can be flipped. If the bit is flipped, the event is categorised as a *Single-Event Upset*. Both single-event transients and single-event upsets are classified as "soft errors". [21]

Single-event upsets caused by  $\alpha$ -particles have the approximate same occurrence on the ground as in aircraft, as the particles originate from the package. The problem can be reduced by using high-quality materials for the package production. However, single-event upsets caused by high-energetic neutrons with energies larger than 10 MeV are 300 times more probable in the atmosphere than on the ground. When compared, the contribution of single-event upsets caused by  $\alpha$ -particles in atmospheric applications are insignificant compared to the ones caused by high-energetic neutrons. Incidents caused by  $\alpha$ -particles are also quite rare, and therefore in general can be neglected. [15]

#### 2.5.2 Calculating the risk of SEEs

SEEs poses a risk to ALOFT, as they may alter register and storage values. Equation 2.3 gives the number of SEEs per hour, were  $N_{bits}$  is the number of configuration bits on the device,  $\sigma_{bit}$  is the bit cross section given in cm<sup>2</sup>/bit, and  $\phi_{neutron}$  is the neutron flux per cm<sup>2</sup>.

$$\frac{SEE}{hour} = N_{\text{bits}} \cdot \sigma_{\text{bit}} \cdot \phi_{\text{neutron}} \cdot 3600 \tag{2.3}$$

ALOFT will be implemented on a 7 series FPGA from Xilinx. This is further described in chapter 4. The bit cross section of this FPGA series is  $6.99 \cdot 10^{-15} cm^2/bit$  [22]. In section 2.4, the neutron flux at 60,000 feet was found to be around 1.3 neutrons/cm<sup>2</sup>/second. The bitfile used for the FPGA has a size of 16.8 million bits. Only a smaller fraction of these bits are actually used in the design, but to make a conservative estimate all are assumed critical to the system.

For an 8 hour flight, this makes the probability of one single SEE to be around 4%. Conservative design rules do, however, suggest that design considerations should be taken on the assumption of a case ten times worse. This means that the design should be implemented with the assumption on a 4% likelihood of an SEE occurring during a flight.

These numbers are very low, especially as the ALOFT instrument is non-critical to the safety of the pilot of the ER-2, or any equipment for that matter. As will be seen later in the thesis, some radiation design precautions have however, been implemented in the software.

#### Chapter 3

# FEGS BGO Instrument - Readout System

The development of the ALOFT readout system is the main scope of this thesis, but as discussed in section 2.3, the design and architecture of ALOFT will be heavily inspired by the FEGS BGO instrument due to their mission similarities. This chapter will explain the readout system of the FEGS BGO instrument. Figures and the majority of the information is based on [23].

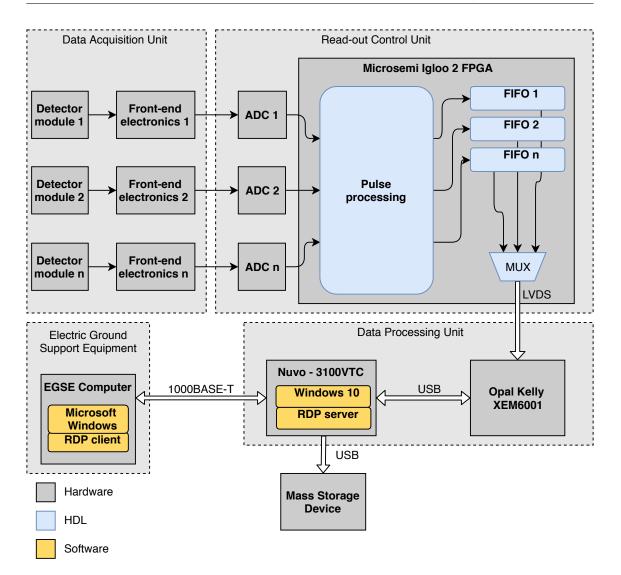

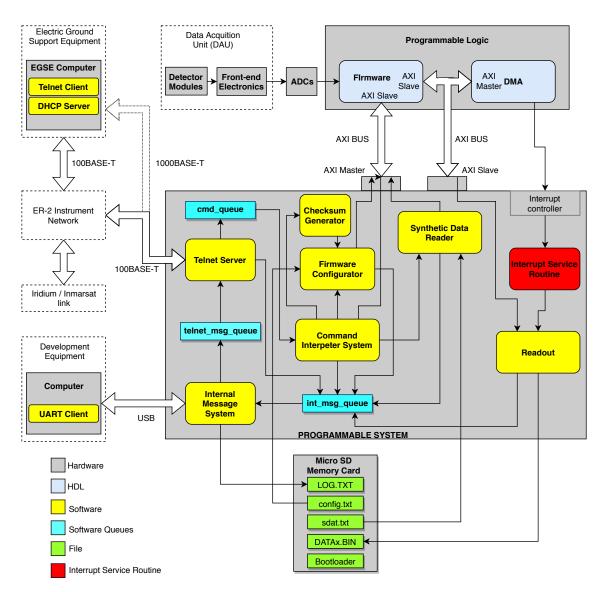

#### 3.1 System Architecture

Figure 3.1 illustrates the readout and system architecture of FEGS BGO. There are three major blocks in addition to the external Electric Ground Support Equipment (EGSE). The major blocks are dotted and colour coded in light grey to represent abstract components, namely the Data Acquisition Unit (DAU), the Read-Out Control Unit (RCU), and the Data Processing Unit (DPU). Each will be further explained in their respective subsections. In each of the major blocks, dark grey blocks illustrates hardware with either firmware or software if present.

Figure 3.1: Block diagram of the FEGS BGO instrument readout and system architecture. The three major blocks in light grey encompasses the Data Acquisition Unit (DAU), Read-Out Control Unit (RCU), and Data Processing Unit (DPU), in addition to the Electric Ground Support Equipment (EGSE).

# 3.2 BGO Data Acquisition Unit

The DAU is a mechanical construction of three BGO *detector modules*, one fast *detector module*, and voltage dividers. Each BGO detector module is a separate BGO scintillator crystal with a PMT.

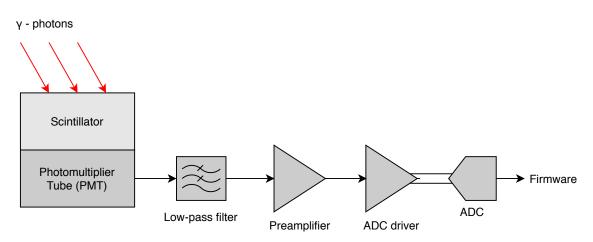

The output from the PMTs are low-pass filtered with a corner frequency of around 20 MHz. This is to remove any high-frequency components before each PMT-signal is amplified by a preamplifier. The relative position in the readout-chain of the *preamplifier*, *low-pass filter* and *detector module* can be seen in figure 3.2. The figure also contains the Analog to Digital Converter (ADC) and ADC driver modules which are described in section 3.3.

Figure 3.2: Relative position of the detector modules, front-end electronics, and ADCs in the FEGS BGO instrument.

### 3.3 Readout Control Unit

The RCU contains three ADCs and a *Microsemi Igloo 2* Field Programmable Gate Array (FPGA).

As the PMTs outputs analogue signals, it is necessary to convert them into digital signals to efficiently process and handle them. This is done by the three ADCs, one for each PMT channel. Each ADC runs in a differential signaling setup. By using differential signaling, common mode noise and interference gets rejected. The overall performance is also increased as the signaling is balanced, and the dynamic range gets increased by a factor of two.

To create the differential signaling from the single ended analog PMT output, an ADC driver is placed in front of the ADC in the readout-chain. This is illustrated in figure 3.2. The ADCs used are the 12 bit RHF1201, operating at a 36 Msps sample rate which is the same frequency as the main oscillator in the system.

The RCU is also connected to a GPS receiver called Copernicus II from the company Trimble. The receiver provides a 1 Hz Pulse Per Second (PPS)-signal accurate within 60 ns rms. [24]

#### 3.3.1 Firmware

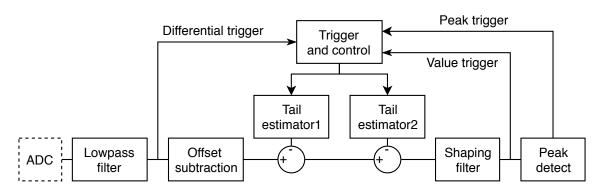

Each ADC outputs a 12-bit data stream which is fed into the firmware running on the flash based Igloo 2 FPGA. Figure 3.3 provides a block diagram of the various pulse processing performed in the firmware. Each PMT channel is handled concurrently in the firmware.

Figure 3.3: Block diagram of the pulse processing performed in the FEGS BGO firmware, implemented on the Igloo 2 FPGA. Solid blocks are implemented on the FPGA.

Interfacing the firmware is performed through a set of registers. Each module in the firmware contains a control register, and some also have a status register. The control registers are 8 bit with 14 bit addresses.

#### Scientific Data Packets

Data from each of the firmware data channels are outputted in the form of a 48 bit data packet called a Scientific Data Packet (SCDP). Table 3.1 displays the SCDP normally outputted from the firmware.

| 2 bits    | 4 bits  | 1 bit | 1 bit | 1 bit  | 1 bit | 6 bits        | 12 bits | 20 bits  |

|-----------|---------|-------|-------|--------|-------|---------------|---------|----------|

| Flag bits | Address | OVF   | Fast  | Valley | Spare | Fast time tag | Energy  | Time tag |

| ,00,      | 00 AA   | '0'   | '0'   | '0'    | '0'   | FF FFFF       | EEEE    | TTTT     |

| 47 46     | 45 42   | 41    | 40    | 39     | 38    | 37 32         | 31 20   | 19 0     |

| Table | 3.1: | Normal | SCDP. |

|-------|------|--------|-------|

|-------|------|--------|-------|

The normal SCDP is transmitted for any gamma ray event were a sufficient delay exists between two events. The first two bits are set depending on the OVF and *Fast* flags. The address bits indicate which BGO detector module the data originates from. Each SCDP contains a *fast time tag* and a *course time tag*. These are set using the PPS-signal generated by the GPS receiver. The *fast time tag* has a resolution of 27.78 ns, and the course time tag has a 1 µs resolution. The *energy*-field is the detected energy with a value range from 0 to 4095.

When the *OVF* and *Fast* flags are set, the generated SCDPs are called *Fast SCDP*, *Overflow SCDP*, and *ADC Sample SCDP*. Table 3.2 illustrates the different SCDPs based on the flags.

| OVF | Fast | Туре       |

|-----|------|------------|

| 0   | 0    | Normal     |

| 0   | 1    | Fast       |

| 1   | 0    | Overflow   |

| 1   | 1    | ADC Sample |

Table 3.2: SCDP types.

Fast SCDP only differs from the normal SCDP by the Fast flag being set. Fast SCDPs are created when the time between two event-pulses are too close to be separated. The Overflow SCDP is transmitted when the ADC overflows for more than one clock cycle. The fast time tag is then unused, and the energy-field is replaced by the number of clock cycles the overflow exists.

| 2 bits    | 4 bits  | 1 bit | 1 bit | 1 bit  | 1 bit | 6 bits | 12 bits           | 20 bits  |

|-----------|---------|-------|-------|--------|-------|--------|-------------------|----------|

| Flag bits | Address | OVF   | Fast  | Valley | Spare | Unused | Overflow duration | Time tag |

| Table 3.3: | Overflow | SCDP. |

|------------|----------|-------|

|------------|----------|-------|

The ADC Sample SCDP is transmitted when the RCU is commanded to operate in *continous* or *triggered* sample mode. In these modes, the raw unfiltered 12 bit ADC value is included in the SCDP. Table 3.4 displays the ADC Sample SCDP.

| 2 bits    | 4 bits    | 1 bit | 1 bit | 1 bit | 1 bit    | 6 bits |    | 12 b | oits | <b>20</b> k | oits  |

|-----------|-----------|-------|-------|-------|----------|--------|----|------|------|-------------|-------|

| Flag bits | Address   | OVF   | Fast  |       | Sample r | number |    | Ener | ·gy  | Time        | e tag |

| ,00,      | 00 AA     | '1'   | '1'   | N     | N        | NN NN  | •  | EE.  | EE   | TT          | TT    |

| 47 46     | $45 \ 42$ | 41    | 40    | 39    | 38       | 37     | 32 | 31   | 20   | 19          | 0     |

| Table $3.4$ : | ADC | Sample | SCDP. |

|---------------|-----|--------|-------|

|---------------|-----|--------|-------|

SCDPs for each respective channel are placed in separate First In First Out (FIFO) memories. A Multiplexer (MUX) operated with round-robin scheduling is then used to mux through the different FIFOs and makes the data available on a Low Voltage Differential Signaling (LVDS) serial data line. The round-robin scheduling assigns the total available time equally to each separate channel.

# 3.4 Data Processing Unit

The DPU is connected to the RCU using the LVDS link. The DPU consists of the OpalKelly XEM6001 FPGA, and the Nuvo-3100VTC in-vehicle computer.

### 3.4.1 OpalKelly XEM6001

Communication to and from the Nuvo computer is handled over Universal Serial Bus (USB), so the OpalKelly XEM6001 is used as an interfacing adapter between the RCU LVDS and USB interface. The LVDS link provides a maximum data transfer rate of 330 k packets per second. Saturation is only possible when the instrument is running in the continuous sample mode, and equals to a data rate of 1.98 MB/s for 48 bit SCDPs.

XEM6001 features the Xilinx Spartan-6 FPGA, which is well equipped to handle the LVDS interfacing work. [25].

Figure 3.4: Opal Kelly XEM6001 mounted in the FEGS BGO instrument.

### 3.4.2 Nuvo-3100VTC

The Nuvo-3100VTC is a fan-less in-vehicle computer that features small dimensions and the required specifications to operate as DPU in FEGS BGO. With the used hardware configuration it has been budgeted to use up to 47 W. The Nuvo is used as DPU by writing the SCDPs received from the RCU onto a storage medium. The Nuvo also handles firmware configuration through the register interface, and system monitoring. This is performed by a C# software program called EGSE-software. The Graphical User Interface (GUI) of the program can be seen in figure 3.5.

| File Tools Window                                                          |                                            |

|----------------------------------------------------------------------------|--------------------------------------------|

| #RUNONLOAD                                                                 | Execute                                    |

| Set up environment                                                         | Command                                    |

| script logtofile true                                                      |                                            |

| script logfile C:\FEGS\FEGS-cmdlog-@y-@m-@d-@h.log                         | Step Forward                               |

| let DURATION 900                                                           | Run Stop                                   |

| print Running script.                                                      | Start Acquire                              |

| print                                                                      | Our trains                                 |

|                                                                            | Stop dumping                               |

| Start HK background script                                                 | Never                                      |

| print Starting HK script                                                   | Packets                                    |

| exec bg toggle                                                             | 0 🗘 num                                    |

| print                                                                      | Time                                       |

|                                                                            | 0 = sec                                    |

| Starting to collect data                                                   | 0 🗘 sec                                    |

| print Starting to collect data. New file every \$DURATION seconds.         |                                            |

| Collecting data                                                            | Dump information                           |

| for i in 1 to inf                                                          | Duration : 0 s                             |

| let CNT read t \$DURATION 1 0 C:\FEGS\FEGS-@y-@m-@d-@h-@n-\$i.dmp          | Total SCDPs : 0                            |

| print Acquired \$CNT SCDPs                                                 | SCDP/sec : 0 1/s 0 1/s                     |

| done                                                                       | DAU 1 : 0 1/s 0 1/s<br>DAU 2 : 0 1/s 0 1/s |

|                                                                            | DAU 3 :0 1/s 0 1/s                         |

|                                                                            | DAU 4 : 0 1/s 0 1/s<br>Filesize : 0 MB     |

|                                                                            | Filesize : 0 MB<br>Max filesize : 0 MB     |

|                                                                            | Hachoald . o Ho                            |

|                                                                            |                                            |

|                                                                            | ~                                          |

| GDLS: 12520004PD                                                           | ∧ Clear                                    |

| Successfully connected<br>13:39:01 Running script.                         |                                            |

| 13:39:01                                                                   |                                            |

| 13:39:01 Starting HK script                                                |                                            |

| 13:39:01<br>13:39:01 Starting to collect data. New file every 900 seconds. |                                            |

| 13:54:01 Acquired 939132 0 0 12 SCDPs                                      |                                            |

| 14:09:01 Acquired 940444 0 0 6 SCDPs                                       |                                            |

| Background script                                                          | ÷                                          |

Figure 3.5: GUI of the FEGS BGO instrument Electric Ground Support Equipment (EGSE).

The operating system on the Nuvo is a Realtime Operating System (RTOS)-version of Microsoft Windows 10 which is configured to accept Remote Desktop Protocol (RDP)-connections necessary for remote access by the EGSE.

The Nuvo also features watchdog functionality. Watchdog is a hardware mechanism

which works by software resetting a timer before it reaches a predefined value. If the software hangs or otherwise fails to reset the timer, the hardware will automatically restart. This ensures that the Nuvo restart if the software behaves abnormally.

For storage of the acquired data, an industrial grade Single Level Cell (SLC) USB flash drive is used. The flash drive is connected to the Nuvo using USB version 2.0.

# 3.5 Operation of FEGS BGO during Flight Campaigns

To test and configure the FEGS BGO instrument, a cable harness connected to the Nuvo can be pulled through the payload bay so that it is accessible at the aft. External equipment connected to the instruments and airplane itself are normally termed EGSE, but in this thesis the term will only reference systems connected to the FEGS BGO and later the ALOFT instrument. The harness consists of an HDMI video out cable to connect a monitor to the Nuvo, a USB-B extension cable for easier access connecting and removing the USB flash drive, and a category 5E ethernet cable. By connecting an external computer to the ethernet cable, an ad-hoc network using static Internet Protocol (IP)-addressing can be created.

When connected, the EGSE-computer can connect to the Nuvo using RDP. RDP does a pass-through of the display and audio of the Nuvo to the EGSE, and sends mouse- and keyboard-input from the EGSE to the Nuvo. The RDP-connection is primarily used to control the EGSE-software running locally on the Nuvo.

# 3.6 Review

Development of the FEGS BGO instrument was designed with reuse of software and hardware from the ASIM campaign in mind. Reuse is great for shortening the development time of an instrument, but if not done properly can make for a less elegant solution. This is what happened to FEGS BGO.

As the new ALOFT campaign is built on the FEGS campaign, this is an excellent opportunity to revise the design of the FEGS BGO instrument for it to better accommodate the campaign requirements. In short, revising should remove the use of proprietary software, and move the design onto a more efficient hardware solution.

### Chapter 4

# ALOFT Design

In section 1.3 it was introduced that the Airborne Lightning Observatory for FEGS & TGFs (ALOFT) will be an embedded version of the FEGS BGO instrument for which the readout system was described in chapter 3.

FEGS BGO was presented as a decentralized system, with functionality spread over multiple separate devices. ALOFT will use the same detector modules, but the firmware and DPU will be implemented on a System on a Chip (SoC) embedded platform.

Due to the expected mission similarity and reuse of firmware, detector modules, and DPU functionality, the proposed design is based on the assumption of ALOFT having overall similar requirements as those valid for FEGS BGO.

### 4.1 System On a Chip

Due to the constantly development of ever more complex systems, the use of SoCdesigns has become increasingly common. SoC is the term of systems combining different hardware modules through a common bus, on a single chip. Example of such modules could be memory units, I/O-peripherals, or a microprocessor. [21]

As the hardware modules are placed closer together than in conventional systems, delays are much smaller, and higher bandwidth can be obtained. This reduces some of the problems associated with building high-speed systems. Typically the modules can be interchanged as they have been individually pre-designed, adding a high degree of customizability-options for the system designer. SoC-designs with an FPGA-block also increases customizability as additional blocks can be implemented on the FPGA logic after the actual chip has been produced. From a designers perspective, using a SoC-design increases the time that can be used in the *behavioral* and *structural* design domains. These domains concern how the system behaves and which parts that needs to be added to fulfill the desired behavior. Consequently, less time is needed in the physical domain where tasks such as floorplanning and actual chip geometry-design takes place. See for example [21].

Naturally, development time is reduced as sophisticated systems can be designed without going through the hassle of coming up with every single subsystem design. SoC designs also aids in making the final product hierarchical, and decreases development time.

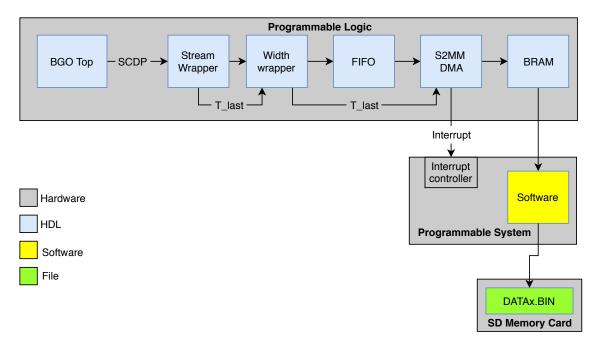

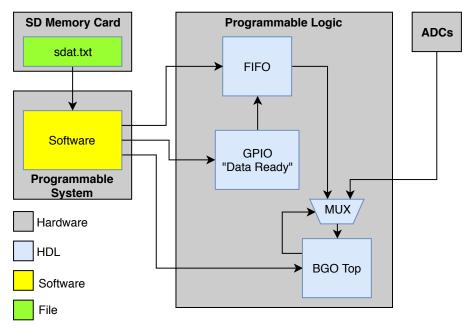

The SoC used for ALOFT is a dual-core microprocessor system embedded on an FPGA. The microprocessor system in such systems are referenced as the *programmable system*, and the FPGA as the *programmable logic*.

ALOFT uses the firmware from the FEGS BGO RCU, and much of the same functionality as was found on the FEGS BGO DPU. As the firmware is already written in the hardware description language VHDL, and thus intended to run on an FPGA, it will be ported to the ALOFT programmable logic. This is currently being done at the University of Bergen, and the results should be available in [26] when published. Functionality earlier handled by the DPU are easiest implemented using software, and thus wil be executed on the programmable system.

With most of the readout system implemented as VHDL and software on the embedded SoC platform, it can easily be customized to meet additional mission and design requirements later in the development. The remaining part of this thesis will primarily focus on the design and implementation of the software responsible for the DPU-like functionality.

# 4.2 System Requirements

The required functionality of the software can be divided into four tasks. The primary task is data storage. This means to receive SCDPs from the firmware and store them safely to a mass storage device. It is important to perform this task with sufficient speed to avoid introduction of any bottlenecks, which would result in data loss.

The second task is firmware configuration. As has been elaborated in section 3.3.1, the firmware is interfaced through a set of configuration and status registers. ALOFT's software must be able to configure the firmware through this interface, preferably from a configuration table easy accessible when operating the instrument.

The third task is to log the status and health of the system. As the software is in control of both the firmware and the rest of the readout system, it has a very good position for monitoring the overall status of ALOFT. The log must be written to a nonvolatile memory to ensure its survival, should the instrument be power cycled.

The fourth and final task is to provide a user interface to the instrument. The interface must report information about ALOFT, and provide a way of manually controlling the instrument. The interface should be easily accessible even when the instrument is mounted in the ER-2 Aircraft. Preferably, the user interface should also be available from ground services while in-flight through the ER-2 Instrument Network described in section 4.9.

These four tasks must all be started automatically when power is connected.

### 4.2.1 Reliability

ALOFT will have fairly limited human interaction capabilities while in-flight. The only interaction available will be through the user interface covered in section 4.9

and the pilot operated Cockpit Experiment Control Panel (ECP) which is covered in section 4.10. In essence, this means that the instrument needs to be highly reliable. Reliability is defined as the probability of a system or component to function as intended for a specified period of time, and generally it is as relevant for software as it is hardware.

Hardware reliability in ALOFT is mostly relevant to the burn in phase, as the general life time of electronics surpasses the use of the instrument. Extensive hardware testing must be performed to ensure the removal of weak components.

The failure rate of software is at its peak during the *test and debugging* phase. When this phase is completed and the software is deployed, the probability of failures are usually at a minimum. The failure rate is constant beyond this point if no changes are made. Upgrades can add additional complexity which will increase the overall failure rate. In addition, as complexity increases, the maintainability decreases, which again increases the probability of failure when the software is upgraded. [27]

Focus has been on keeping complexity low to increase maintainability. This has to a large degree been achieved through regularity and the use of a hierarchical design strategy. Regularity and hierarchical design are further explained in appendix C.1.

#### 4.2.2 Hardware requirements

#### Data storage

The data storage requirements are based on two factors; required data rate, and total amount of data. As seen in section 3.4, the FEGS BGO instrument had a maximum data rate of 1.98 MB/s. This maximum data rate was, however, only reached when the instrument operated in the continuos sample mode. As the limiting factor in FEGS BGO has been removed in ALOFT the transfer rate is no longer limited to the same rates. Higher data rates are not required for ALOFT, but it should be emphasized that capabilities beyond the required data rate will ensure a lower possibility of the software to induce a bottleneck in the readout chain.

ER-2's maximum mission duration is 8 hours, providing about 7 hours of data collection at the desired altitude. Normal missions last around 6.5 hours giving 5.5 hour of data collection. Theoretically, the instrument could generate around 50 GB of data if operated in the continuous sampling mode for a max duration flight. 50 GB is, however, an unrealistic overestimation. Results from the FEGS campaign indicates that even very conservative estimates does not surpass 7 GB of data. In addition to the collected data, some space must be reserved for the system logging, configuration table, and as will be introduced in section 4.7, a bootloader. These files are negligible in terms of size compared to the collected data.

#### 4.2.3 Software requirements

It has been decided that the software will be written in the programming language C. C has the quite unique capability of providing syntax for both high- and lowlevel programming. It is also architecture-independent and thus suited as a general purpose language which is needed to perform the four main functionalities assigned to the ALOFT software. C++ would be another option, but is not truly supported by the FreeRTOS operating system introduced in section 4.4 without making changes to the kernel.

# 4.3 Xilinx Digilent Zybo SoC Trainer Board

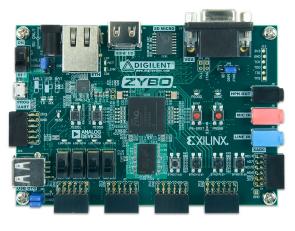

A Xilinx Digilent Zybo SoC Trainer Board has been chosen to be used during development. The board contains the Z-7010 SoC discussed in section 4.3.1. It also features peripherals such as gigabit ethernet, SD memory card capability, USB with On The Go support, HDMI, Audio in/out, Multiplexed I/O (MIO)- and General Purpose I/O (GPIO)-ports.

Figure 4.1: Xilinx Digilent Zybo board [28]

#### Nonvolatile memory

The Zynq-7000 contains two Serial Peripheral Interface (SPI) bus controllers. These can be used to interact with SD memory cards with serial mode support or other hardware such as various sensors, real-time clocks, etc. [29]

On the Zybo development board, a micro SD connector can be found on the reverse side of the board. Enabling the SPI controller in Xilinx' software program *Vivado* enables use of a connected micro SD memory card both as a mass storage device by any application running on the board, and as a boot medium. To use the micro SD memory card as a boot medium, the Mode jumper (JP5) must be positioned to select "MicroSD", and the card must contain a bootloader on a FAT 16/32 file system. [30]

Bootloaders are further covered in section 4.7.

#### 4.3.1 Zynq-7000 Architecture

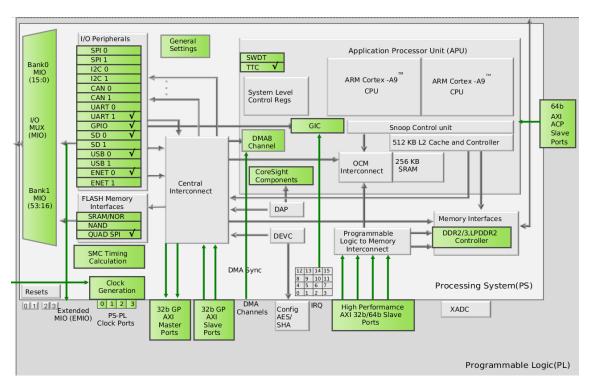

For development, the smallest member of the Xilinx Zynq-7000 All Programmable SoCs-family, the Z-7010 has been used. The Z-7010 features a dual-core ARM<sup>®</sup> Cortex<sup>TM</sup>-A9 MPCore<sup>TM</sup> based programmable system, and a high performance, low-power Xilinx programmable logic, built with 28 nm process technology. A block diagram of the Z-7010 architecture is seen in figure 4.2, with the *programmable*

system embodied in light grey, and the programmable logic in dark grey. [29]

Figure 4.2: Block diagram exported from Xilinx Vivado of the Zynq-7000 architecture. The *programmable system* containing many of the subsystems is contained in a light grey block, while being interconnected with the *programmable logic* marked in dark grey.

The Zynq-7000 system has two gigabit peripherals. They can be seen in figure 4.2 as ENET0 and ENET1. ENET0 will be used to provide the network required for the user interface further described in section 4.9. On the Zybo development board, a Realtek RTL8211E-VL PHY controller is used to provide a 10/100/1000BASE-T ethernet connection interface to the peripheral.

# 4.4 FreeRTOS - A Realtime Operating System

Each of the software tasks described in section 4.2 could by varying degree be implemented directly on the programmable system without an operating system. However, due to the complexity of having multiple different functionalities that may not require the same priority in terms of processing time, it becomes very hard to find arguments against the use of an operating system.

An effective step in cutting down on complexity is to use multithreading. Multithreading will be explained in section 4.5.

FreeRTOS, or Free Real Time Operating System, is essentially an operating system to run bare bone applications with full multithreading support. It does not offer much more than that, and this separates it from running a Linux distro such as PetaLinux on the system. Using a Linux distro would probably cut some development time as there are quite a lot of resources and "out of the box"-solutions easily implemented to do the job asked by ALOFT. A Linux distro would however draw more resources than FreeRTOS, as the solutions would not be specifically designed for the task at hand, but be adapted to fit in a "good enough"-solution.

As FreeRTOS is an RTOS, it can operate under strict defined time constraints. FreeRTOS seems like a perfect compromise between constraining computing- and power-resources, and providing an efficiently platform for development of a complex system. FreeRTOS' core source files are also conform to MISRA coding standard guidelines [31].

# 4.5 Multithreading

The following section along with subsections are based on [32].

Applications can contain multiple tasks which themselves can occupy separate threads. For a single core system only one task can run at a time, but multithreading makes it possible to switch between these tasks so that they behave as if they were running concurrently. The actual speed is, however, limited to the execution of one task at a time. Dual core systems, such as the one found on the ARM Cortex-A9, enables the possibility of running two concurrent tasks. This could be beneficial if the system will ever require data rates which saturates the single core. For now, ALOFT is designed to only use one of the cores, as it should provide enough performance. Designing ALOFT for single core usage also cuts down on system complexity and challenges related to development.

### 4.5.1 Scheduler

As only one task can be executed at a given time in a single core system, a framework for deciding which task to be executed is essential to a multithreading system. This decision process is known as *scheduling*. To help in deciding which task to execute, the tasks are marked with a priority. There will also always be an *idle*-task created by the operating system's kernel that will have the lowest priority. For tasks to be able to run, they need to have a higher priority than the idle task. Scheduling is handled by a "scheduler", and FreeRTOS has one built into the kernel. It operates in a *round-robin* policy mode, meaning that each task of the highest priority will be executed by turn. It does not, however, guarantee that the available processing time will be spread equally between them.

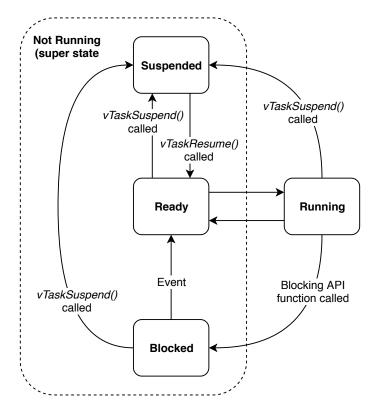

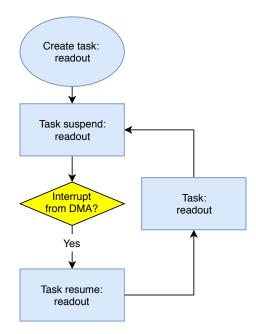

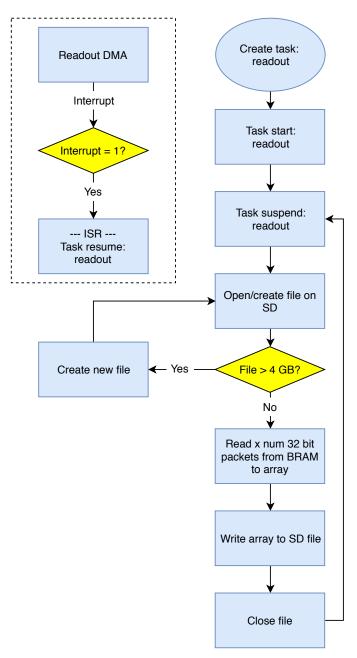

Up until now, a simplified view of tasks being either in a *running* or *not running* state has been described. The reality of the FreeRTOS kernel is however somewhat more complex, as there are actually four different task states; *Running, Ready, Suspended*, and *Blocked*. Figure 4.3 illustrates how task transitions are performed when different functions are called. If all tasks with the highest priority are placed in the blocked or suspended state, the scheduler will move on to the tasks with the second highest priority.

Figure 4.3: State machine for the four different task states available in FreeRTOS, Running, Ready, Suspended, and Blocked. Modified figure from [32].

For ALOFT, the scheduler algorithm is in a *prioritized pre-emptive scheduling with time slicing*-configuration. This means that if a higher priority task is put into the ready state when a lower priority task is in the running state, the lower priority task will immediately be pre-empted out of the running state so that the state is available for the high priority task. Maximum task priority is set to 8.

To avoid the highest priority tasks in ALOFT starving the lower priority tasks of run-time, all tasks are put into the suspended state for a limited time period when they have reached the end of instructions, unless deleted. Putting tasks into the suspended state is done with the vTaskDelay() function call. It takes a number of clock-cycles as input. If the function is combined with the  $pdMS\_TO\_TICKS()$ -function, suspending can be defined in milliseconds.

#### Idle task

When the scheduler is started upon boot, the idle task will be created automatically. As it has the lowest priority of all the tasks, it will only execute when there are no other tasks in the ready state. The idle state can be used as a way to measure how much of the processing time that is actually used by the system. As it does not process any significant work, it reduces the processor's power usage when operating in the running state.

### 4.6 Memory allocation

In programming, there are three ways of allocating memory. *Static, automatic,* and *dynamic.* Automatic and dynamic allocates the memory at run-time, therefore making it nearly impossible to determine the actual memory footprint. They can also produce some nasty thread-behavior if not used with great care, as the program might run into memory leaks or prove non-deterministic with regard to execution time. Static allocation allocates the application writer's requested amount of memory at compile time. Usage of static allocation creates a deterministic memory footprint, and execution time can be specified by the application writer.

As the MISRA-C guidelines have been applied to this project, no use of dynamic memory allocation is permitted unless great care is taken [33, p. 34, Dir. 4.12]. This also covers automatic allocation. To comply, all usage of memory in the ALOFT software has been statically allocated to its greatest extent.

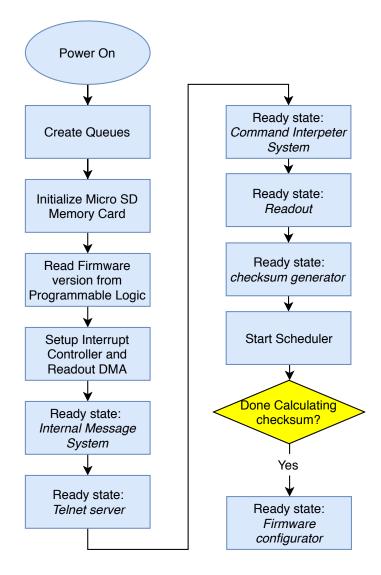

# 4.7 First Stage Boot Loader

References for this section can be found in [29].

The configuration of the programmable logic is stored in Static RAM (SRAM)type internal latches, and thus is volatile. This means it has to be reloaded every time power is cycled on the Zynq-7000 device. Reloading can be performed by the programmable system using a bitstream-file.

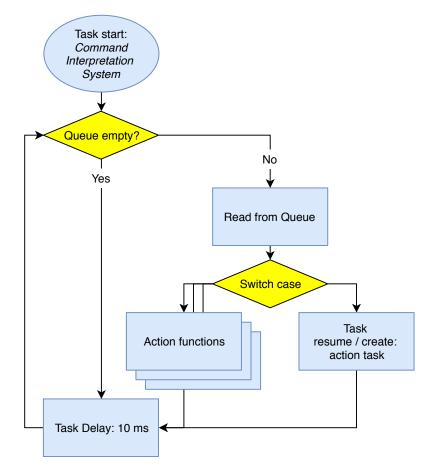

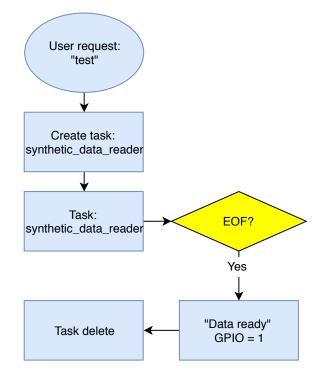

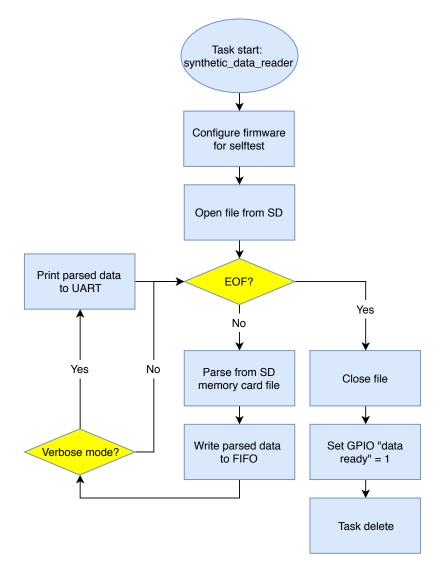

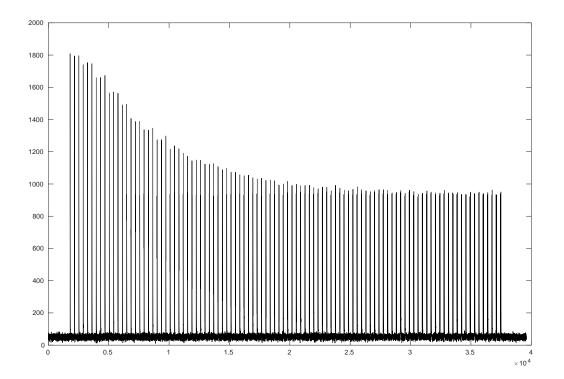

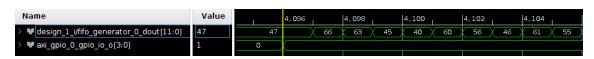

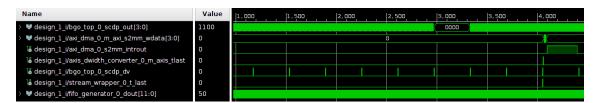

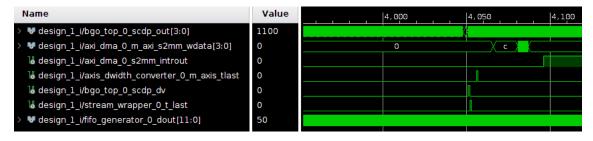

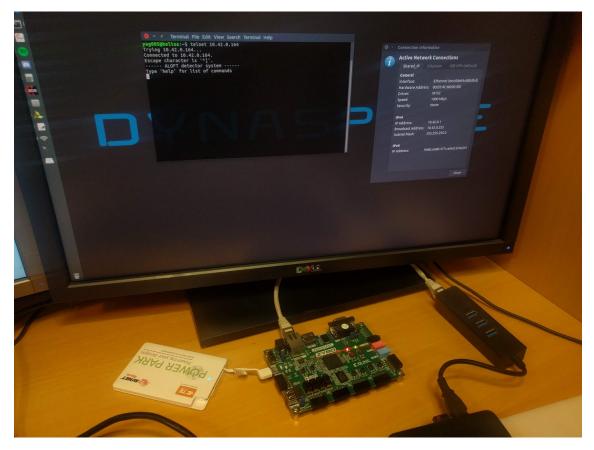

The application running on the programmable system is stored in a memory module known as the *On-Chip Memory*. The Zynq 7000 uses a power-on reset function which resets all reset-capable registers when power is connected. Thus the application must be uploaded to the on-chip memory every time power is cycled. Uploading to the on-chip memory is handled by a *Read-Only Memory* known as the BootROM.