# FW implementation of SMILE SXI Radiation Shutter Control System

Anders Lerum Alme

Master of Science in Physics

University of Bergen

June 2019

© Author

2019

FW implementation of SMILE SXI Radiation Shutter Control System

Anders Lerum Alme

http://bora.uib.no/

# Abstract

In 2023 a Solar Wind Magnetosphere Ionosphere Link Explorer (SMILE) satellite is set to launch to explore how solar wind interacts with the earth's magnetosphere and ionosphere. The SMILE space mission is a joint operation between the European Space Agency (ESA) and the Chinese Academy of Science, where scientists and industry are contracted to provide the satellite and its instruments.

A Soft X-ray Imager (SXI) which is one of those instruments, is designed to detect low energy electrons in this interaction. As the satellite will orbit the earth, it will during a percentage of the orbit come within the radiation belt of the earth, where there are high energy particles. To protect the detectors in the SXI instrument from the high energy radiation near the earth, a radiation shutter is being developed by a team at the University of Bergen to enclose the detector inside the satellite when needed.

This device is split into the radiation shutter mechanics (RSM) and the radiation shutter electronics (RSE) that is going to control the operation of the RSM. This work covers the continued development, implementation, testing and verification of the RSE.

This thesis explains the functionality of the RSE and the implementation of that system on a field-programmable gate array (FPGA). The RSE will be commanded by a central master that oversees the operation of the whole SXI instrument. A reliable communication protocol is designed and implemented to be able to communicate with the master. The RSE will be able to perform different operations, including opening and closing the shutter, reading different sensors related to the shutter operations and it will be able to protect the SXI detectors should the master data process unit (DPU) fail.

The system has been tested with both simulations with a test bench and on a breadboard. These tests have been done to check that the RSE operates as desired and that a breadboard version of the shutter will be able to open and close.

# Acknowledgements

First and foremost, I would thank my supervisor and the man responsible for the design and development of the Radiation Shutter Electronics, *Professor Kjetil Ullaland*. He has been a tremendous help with developing an actual useful design and excellent guidance in writing this thesis, especially when I was struggling at different times. I would thank him for unbeknownst to me, nominating me to be in charge of buying in snacks and drinks for the Christmas party, which I assume is the highest honour a student of his can achieve.

I give my thanks to *Ove Lylund*, whose work this thesis continues, *Chief Engineer Bilal Hasan Qureshi* who have both tested my design and collaborated with me in the testing of the RSM, and *Senior Engineer Shiming Yang* for his development of the hardware I got to use. I would also thank *Senior Engineer Georgi Genov*, who helped us set up the measurements and the rest of the SMILE team for their work with the SMILE project.

For tips, tricks and solutions to problems, both *Ola Grøttevik* and *Associate Professor Johan Alme*, who also helped with my thesis, have my gratitude. Also, *Magnus Rentsch Ersdal* has my thanks. He helped me with making a working test program when I was handed a python program for the first time in my life.

At last, I would like to thank my friends and my family for support and encouragement. My time at the University would not have been the same without them.

# Content

| 1 | Int                      | Introduction |                              |    |  |

|---|--------------------------|--------------|------------------------------|----|--|

|   | 1.1                      | Bac          | Background                   |    |  |

|   | 1.2                      | Abo          | out this thesis              | 11 |  |

|   | 1.3                      | The          | sis outline                  | 12 |  |

| 2 | Re                       | equire       | ments for the electronics    | 14 |  |

|   | 2.1                      | Obj          | ective                       | 14 |  |

|   | 2.2                      | Soft         | t X-ray Imager Instrument    | 15 |  |

|   | 2.2                      | 2.1          | Electronics box              | 16 |  |

|   | 2.3                      | Rad          | liation Shutter Mechanics    | 16 |  |

|   | 2.3                      | 3.1          | Rotary actuator              | 17 |  |

|   | 2.3                      | 3.2          | Hold Down Release Mechanism  | 19 |  |

|   | 2.3                      | 3.3          | End Switch                   | 19 |  |

|   | 2.3                      | 3.4          | End Stops                    | 19 |  |

|   | 2.4                      | Rad          | liation Shutter Electronics  | 20 |  |

|   | 2.4                      | 4.1          | Radiation considerations     | 21 |  |

|   | 2.4                      | 4.2          | FPGA                         | 22 |  |

|   | 2.4                      | 4.3          | Stepper Motor                | 22 |  |

| 3 | RS                       | SE De        | velopment                    | 27 |  |

|   | 3.1 Software vs Hardware |              |                              | 27 |  |

|   | 3.1                      | 1.1          | FPGA                         | 27 |  |

|   | 3.1                      | 1.2          | Embedded system              | 28 |  |

|   | 3.1                      | 1.3          | FPGA or CPU                  | 31 |  |

|   | 3.2                      | Stat         | e machine                    | 32 |  |

|   | 3.3                      | VH           | DL development strategy      | 33 |  |

|   | 3.3                      | 3.1          | Waterfall development method | 33 |  |

|   | 3.3                      | 3.2          | Lean development method      | 35 |  |

|   | 3.3                      | 3.3          | Choosing a strategy          | 36 |  |

| 4 | Fu                       | nctio        | nality                       | 38 |  |

|   | 4.1                      | Des          | ign - VHDL                   | 38 |  |

|   | 4.2                      | Reg          | jisters                      | 38 |  |

|   | 4.2                      | 2.1          | Status registers             | 39 |  |

|   | 4.2.2 |        | Control registers         | .41  |

|---|-------|--------|---------------------------|------|

|   | 4.2.  | .3     | Debug registers           | . 44 |

|   | 4.2.  | .4     | Command register          | . 45 |

|   | 4.3   | Ope    | erational procedures      | . 45 |

|   | 4.3   | .1     | Emergency closure         | . 45 |

|   | 4.3   | .2     | Temperature reading       | . 46 |

|   | 4.4   | Cor    | nmand operations          | . 46 |

|   | 4.4   | .1     | Motor commands            | . 48 |

|   | 4.4   | .2     | Other commands            | . 49 |

|   | 4.5   | Cor    | nmunication               | . 49 |

|   | 4.6   | RSI    | E protocol                | . 52 |

|   | 4.6   | .1     | Character level           | . 52 |

|   | 4.6   | .2     | Package level             | . 53 |

| 5 | Firi  | mwa    | re implementation         | . 59 |

|   | 5.1   | Тор    | evel design               | . 59 |

|   | 5.2   | UA     | RT                        | . 60 |

|   | 5.3   | RSI    | E protocol                | . 62 |

|   | 5.4   | Smi    | ile register bank         | . 65 |

|   | 5.5   | Deb    | pugging module            | . 66 |

|   | 5.6   | Clo    | ck generator              | . 66 |

|   | 5.7   | Hea    | urtbeat                   | . 67 |

|   | 5.8   | HD     | RM                        | . 67 |

|   | 5.9   | Res    | et generator              | . 68 |

|   | 5.10  | S      | tepper motor modules      | . 68 |

|   | 5.11  | S      | witch debounce            | . 69 |

|   | 5.12  | Р      | ulse width modulator      | . 69 |

|   | 5.13  | S      | ettling time period       | . 70 |

|   | 5.14  | Н      | Ialf step synchroniser    | . 70 |

|   | 5.15  | S      | tepper control            | .71  |

|   | 5.16  | S      | tepper driver             | .71  |

| 6 | Tes   | st and | d development             | .75  |

|   | 6.1   | Dev    | velopment of the firmware | .75  |

|   | 6.2   | DPI    | U simulator               | . 77 |

|            | 6.2.1 RSE Register Window updates |                                   | . 78 |  |

|------------|-----------------------------------|-----------------------------------|------|--|

|            | 6.2.2                             | RSE Command Window updates        | . 78 |  |

|            | 6.2.3                             | RSE Log Window updates            | . 79 |  |

| 6          | .3 Hai                            | dware tests                       | . 79 |  |

|            | 6.3.1                             | Testing of communication on board | . 80 |  |

|            | 6.3.2                             | RSM bench test                    | . 81 |  |

|            | 6.3.3                             | Settling time                     | . 81 |  |

|            | 6.3.4                             | Chopping                          | . 85 |  |

|            | 6.3.5                             | Motor current                     | . 89 |  |

| 7          | Summa                             | ry and conclusion                 | . 92 |  |

| References |                                   |                                   |      |  |

|            | RMAP over RBDP protocol97         |                                   |      |  |

# Abbreviations

| SMILE | Solar Wind Magnetosphere<br>Ionosphere Link Explorer | TID  | Total-Ionising Dose                                                       |

|-------|------------------------------------------------------|------|---------------------------------------------------------------------------|

| ESA   | European Space Agency                                | EBB  | Elegant breadboard                                                        |

| SXI   | Soft X-ray Imager                                    | RAM  | Random-Access Memory                                                      |

| RSM   | Radiation Shutter Mechanics                          | CPU  | Central Processing Unit                                                   |

| RSE   | Radiation Shutter Electronics                        | VHDL | Very High-Speed Integrated Circuit<br>Hardware Description Language       |

| DPU   | Data Process Unit                                    | PWM  | Pulse Width Modulator                                                     |

| PSU   | Power Supply Unit                                    | RoR  | Remote Memory Access Protocol<br>over Regular Byte stream DAQ<br>Protocol |

| HDRM  | Hold Down Release<br>Mechanism                       | UART | Universal Asynchronous Receiver-<br>Transmitter                           |

| РСВ   | Printed Circuit Board                                | SPI  | Serial Peripheral Interface                                               |

| SEL   | Single-Event Latch-up                                | VVC  | VHDL Verification Component                                               |

| CMOS  | Complementary Metal-<br>Oxide-Semiconductor          | GUI  | Graphical User Interface                                                  |

# **1** Introduction

## 1.1 Background

The radiation from the sun makes it possible for life to be sustained on earth, but the radiation has immense destructive powers too. In 2012 a solar flare just missed the earth [1]. This flare could have caused a mass blackout. In 1989 a solar storm took out the power transmission system in Quebec, Canada [1]. To be able to understand these and be better able to forecast events, the space weather must be studied. Space weather is phenomena that are the constant interactions between the sun and the magnetosphere of the earth.

ESA has a vision of getting a better understanding of these effects. The SMILE mission is planned to launch as a mission to further explore the full connection between the sun and the earth. The satellite will be placed outside the magnetosphere to observe. There, an SXI will be used to map the magnetosphere and look at the emission from the solar wind. [2]

## **1.2 About this thesis**

The objective of this thesis is to continue the development and implementation of a control unit called the radiation shutter electronics (RSE). Lylund and the SMILE team started the development of this project in [3]. The RSE will control the RSM which will enclose the detectors of the SXI instrument when the satellite is within the radiation belt of the earth, as there are high energy particles there which can damage the detectors. As such, the instrument and the RSM will be explored before the requirements of the RSE is explained in Chapter 2. The RSE's primary purpose is to drive the stepper motor in the RSM, so a stepper motor and how to drive it and how power will be saved will be explained. Also, the FPGA that is going to be used will be explained.

The development of the RSE is then focused upon. This thesis moved the project from using a microcontroller to utilise an FPGA. The microcontroller was abandoned in favour of an FPGA because it has not featured in many space missions, which results in a lack of space heritage. The FPGA has been used in previous space missions, so it is proven to work reliably in space.

The fundamental pieces of the RSE are the stepper driver, the register bank which stores all necessary information, and the communication module that lets the central master of the instrument command the RSE. To be able to communicate with the RSE efficiently and reliably, a new small communication protocol was developed to reduce the overhead from the communication standard used previously. The commands that are going to be used to control the RSM need to be well defined and are explained in Section 4.4.

The RSE shall perform different tasks that need to be well defined. Therefore, the different modules have been properly developed to work independently and having a simple hierarchy in order to get a simple and understandable design. The design has been developed with care to ensure that the modules were behaving as expected. The system has also been tested continuously in simulation. The RSE has been developed with a version control tool and is stored on the University of Bergen's git lab repository. Finally, the system has been tested on the bench with an elegant breadboard of the RSE and RSM. A master DPU simulator was modified and used to test by sending signals in accordance with the communication protocol.

## 1.3 Thesis outline

#### **Chap 2: Requirements for the electronics**

This chapter describes the objective of this work. The SXI instrument and the RSM will be looked at and explained first as these provide the fundament for the RSE. From this, the RSE is described with the radiation considerations, the FPGA that is selected and a close look will be had on the stepper motor as the main purpose is to drive it.

#### **Chap 3: RSE development**

In this chapter, the choices that were done for the development will be explored. First, why the microcontroller was abandoned for an FPGA will be explained, before a more general outlook on FPGAs and microcontrollers will be had. Then one of the main features of a sequential system, the state machine, will be looked on. The chapter rounds of with a discussion of developments strategies.

### **Chap 4: Functionality**

The functionality of the RSE will be defined in this chapter. The core design will first be looked upon before the register that is to be used are defined. Then the procedures and commands will be established before the communication protocol that has been developed is explained.

### **Chap 5: Firmware and implementation**

This chapter describes the firmware that has been developed to satisfy the requirements. How the different modules are working and implemented are gone through in detail. First, the top-level design is looked at before the individual modules are described.

### **Chap 6: Test and development**

How the development of the system was done is explained first in this chapter. Then the modified DPU simulator is explained, and the modifications are highlighted. The rest of the chapter describes how the tests on board were done, and the results of those tests are shown.

### **Chap 7: Summary and conclusion**

In the final chapter, the work is summarised, and the results of the test are discussed.

### Appendix A

This appendix explains the communication protocol that was used in the previous iteration.

# **2** Requirements for the electronics

## 2.1 Objective

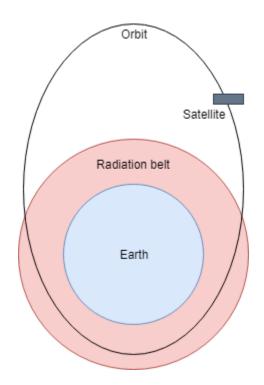

In the SXI Instrument document [4] the SXI's energy band is described to extend up to 5 keV. As seen in Figure 1, the SMILE satellite will orbit the earth and come within the earth's radiation belt. In the radiation belt around the earth, some protons reach above 10 MeV and electrons reaching above 0.5 MeV [5]. The SXI instrument must be protected against these particles when the satellite is within reach of the radiation belt of the earth, as radiation there can degrade or destroy the instrument. The satellite might have to perform manoeuvres to calibrate different instruments, and the SXI needs to be protected against stray particles. To protect the instrument from stray particles and high energy radiation, a Radiation Shutter is required.

#### Figure 1 SMILE satellite's orbit illustration

An internal team at the University of Bergen called the SMILE team develops the mechanical part of the Radiation Shutter. The main objective of this work is to create an electronic system to be able to operate the RSM from commands.

## 2.2 Soft X-ray Imager Instrument

On ESA's webpage about the instruments belonging to the SMILE mission, they describe the SXI like this:

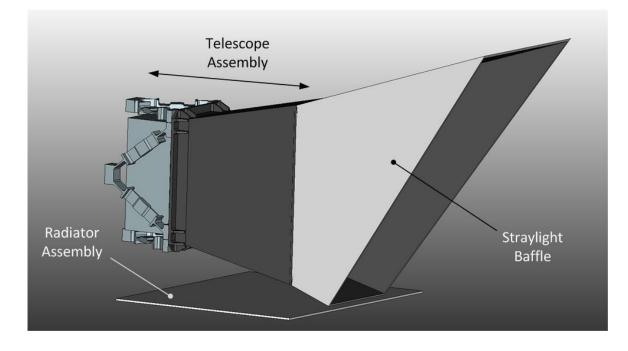

"The SXI is a wide-field lobster-eye telescope using micropore optics to spectrally map the location, shape, and motion of Earth's magnetospheric boundaries, including the bow shock, magnetopause, and cusps, by observing emission from the solar wind charge exchange (SWCX) process. The SXI is equipped with two large X-ray-sensitive CCD [Charge-Coupled Device] detectors covering the 0.2 keV to 2.5 keV energy band, and has an optic field of view spanning  $15.5^{\circ} \times 26.5^{\circ}$ ." [6]

According to [4] the scientific objective of the SXI is to image the X-ray emission produced when solar wind ions interact with neutral atoms in the exosphere of the Earth. These X-ray lines have intensities that peak in the cusps and magnetosheath. The flow of solar wind and energy into the magnetosphere can be imaged from the density boundaries of the X-ray emissions. The SXI telescope combines imaging with spectroscopy to obtain information on the composition of the solar wind that generates the solar wind charge exchange X-ray emission. This way changes in the solar wind reaching the magnetosphere can be detected. [4] The SXI is illustrated in Figure 2.

Figure 2 3D rendering of the SXI instrument. One of two possible configurations [4]

The SXI instrument has four units in addition to the x-ray imager instrument itself. These are explained in the instrument interface control document [4] as:

- Straylight baffle: Avoid light into the system from the Sun or the Earth.

- Telescope Assembly: Optical telescope structure

- Radiation Shutter: Shutter mechanism

- Focal Plane Assembly: CCD detectors and front end electronics

## 2.2.1 Electronics box

In addition to these components, there is a separate chassis containing all the backend electronics. In there is the DPU, the power supply unit (PSU) and the radiation shutter control electronics (RSE).

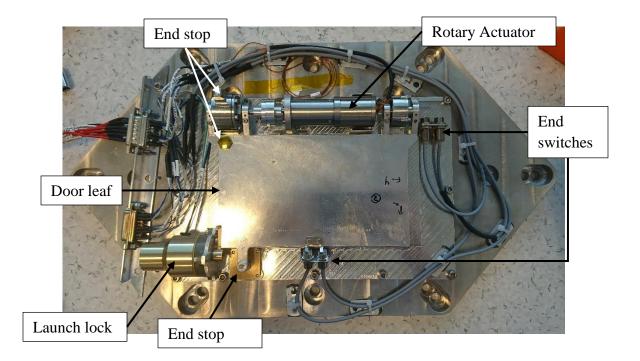

## 2.3 Radiation Shutter Mechanics

This section is mainly based on the RSM design report [7] from the SMILE team. The RSM is the shutter itself, as shown in Figure 3. The RSM frame is mounted in the telescope assembly. The RSM Rotary Actuator on the top of the figure in rotates the RSM Door Leaf in with the bearings on each side of the Rotary Actuator. The RSM Launch Lock is a pin puller that keeps the Door Leaf in place during launch. Besides, there is the RSM End Switches, the RSM End Switch Trigger and the RSM End Stops.

#### Figure 3 RSM prototype

The main components of the RSM are made from aluminium. Where the door leaf is in temporary physical contact with other elements like the end stops are made from INERMET (Heavy tungsten alloy) and hardened stainless steel. These places where there is contact are prone to cold welding.

When a metal surface impacts another metal surface, there is a natural oxide level on the surface that is impacted. This layer would naturally re-oxide on earth. In space, this layer is broken irreversibly. Breaking this layer will create a pure metal to metal contact, and this enables welding. This layer is either degraded over time from impacts or broken from vibrations might lead to oscillating movements that also enables welding, called fretting. These processes are called cold welding [8], and may happen on the RSM during launch as the door leaf might vibrate heavily.

## 2.3.1 Rotary actuator

The rotary actuator is the motor that is used to rotate the door leaf. It consists of a phySPACE stepper motor and a gearbox that comes preassembled from the manufacturer Phytron. Some parameters of the phySPACE stepper motor are listed in Table 1. The stepper motor allows the use of a relatively simple control system to drive it. How a stepper motor works are explained in 2.4.3.

The gearbox has a small diameter and gives a high torque/mass ratio. A drawback of the high ratio is that the gearbox has many mechanical components.

| Parameter                        | Value | Note                      |

|----------------------------------|-------|---------------------------|

| VSS stepper motor                | 200   | full steps per revolution |

| Pole pairs                       | 50    |                           |

| Half-step mode, phases           | 8     |                           |

| Electrical half-steps            | 400   |                           |

| RS Opening angle, °              | 100   |                           |

| Gearbox ratio                    | 192   |                           |

| Half-step speed, s <sup>-1</sup> | 500   |                           |

| Opening time, s                  | 44    |                           |

| Motor speed, RPM                 | 75    | or $75/60 = 1.25  s^{-1}$ |

Table 1 phySPACE stepper motor parameters [7].

By knowing the key parameters of the stepper motor and the mechanism, we can determine the number of half steps per second and the rotational speed. With a half step speed of 500 steps per second, we obtain an opening time of around 41 seconds at a rotational speed of 75 rounds per minute. This is well within the recommended maximum speed of 100 rounds per minute for dry lubricated motors. A close-up picture of the rotary actuator is shown in Figure 4.

Figure 4 Close-up of the rotary actuator with bearing

## 2.3.2 Hold Down Release Mechanism

The purpose of the hold down release mechanism (HDRM), on the RSM Launch Lock, is to hold the door leaf secure in place during launch and then release it before the instrument starts operating. The door leaf will be at risk of moving around under launch if it is not held in place. The HDRM pin is inserted before launch. In the locked position the leaf will be in contact with the end stop. This contact might lead to cold welding. To reduce this risk, a bronze hub is used for the leaf/pin interface. Should the end stop and leaf fuse, the rotary actuator must be driven at max torque to try to force the shutter open. A close up picture of the HDRM is shown in Figure 5.

Figure 5 Close-up of Hold Down Release Mechanism

## 2.3.3 End Switch

End switches are used to signal that the leaf has reached the end position. The two redundant systems each have its pair of end switches for the two end states. Upon contact with the leaf, the switches will be activated. There is some slack in the switches after they activated to allow for a gap between the nominal end position and the end stops.

## 2.3.4 End Stops

In case the end switches should stop working, the rotation of the shutter needs to be stopped, and the end stops mechanically stops the leaf from rotating. The end stop also uses a spring to preload the leaf against the stop during launch.

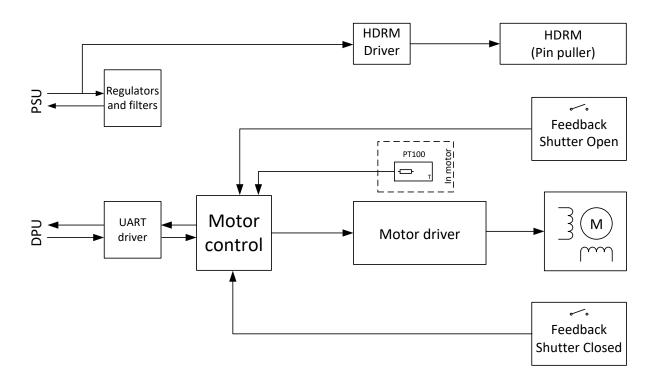

# 2.4 Radiation Shutter Electronics

The purpose of the RSE is to control the RSM described in detail in [7], which includes:

- Operation of RSM Rotary Actuator (a stepper motor with gearbox)

- H-bridge motor driver circuit

- Sensor read-out for the temperature sensor

- Sensor read-out for the RSM Sensors ("Shutter open" and "Shutter closed"-switches)

- A communication link between the DPU and the RSE

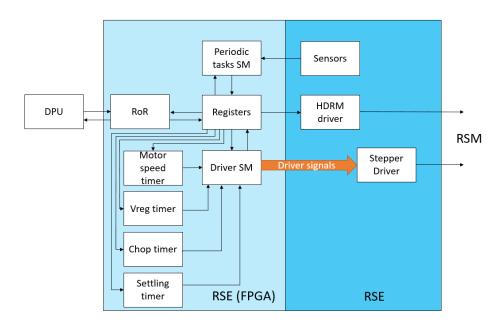

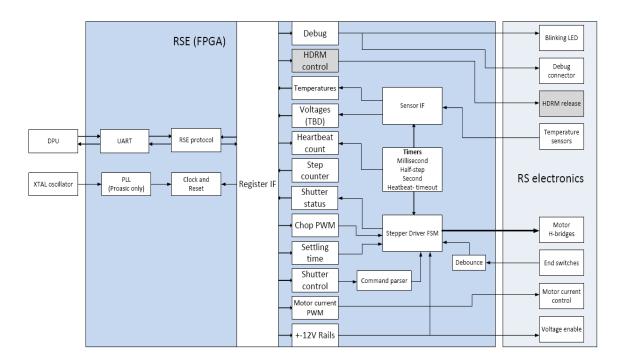

The RSE needs to be an independent system. To accommodate its purposes the necessary circuits and an FPGA is placed on a printed circuit board (PCB), where the FPGA can control the other circuits. A system overview produced by the SMILE team is shown in Figure 6, where the motor control and the motor driver are central to the RSE. In the earlier stages of the project, the DPU through the RSE was supposed to control the HDRM.

The Radiation Shutter is designed to be fully redundant. I.e., the stepper motor (RSM Rotary Actuator) has a double set of windings, and a double set of temperature sensors, enabling independent control from two individual electronics boards. All feedback switches and actuators, as well as communication channels, are also redundant.

For the RSE in the electronics box, this means that there are two independent PCBs connected to their redundant PSUs and DPUs. There are no cross connections between the dual redundant systems, and only one redundant system will be powered at the time.

Figure 6 RSE overview

## 2.4.1 Radiation considerations

Radiation effects are divided into two main effects. The first effect is Single Event Effects, that is a stochastic effect that can happen anytime. As the name implies, these effects happen in a single event as either a non-destructive effect such as corrupting data or as a destructive effect where the corruption permanently damages or destroys the circuit. An example of a non-destructive effect is single event upsets, where a radiation effect occurs in a memory node. This stored data will be in an erroneous state but can be overwritten with new valid data. A destructive effect is a single-event latch-up (SEL) where an ion-generated charge triggers the bulk of complementary metal-oxidesemiconductor (CMOS) technology to produce a low-impedance path between ground and power. This path can create a feedback loop that maintains a high current through the path [9].

The other effect is the total-ionising dose (TID). This is the energy that is absorbed by the technology per mass when the technology is exposed to ionising radiation. This is measured in rad. This effect is an accumulated effect as that degrades the performance and potentially the functionality of material like insulators that are common in CMOS technology [9].

The RSE needs to be protected and able to withstand these effects as it will break otherwise. Therefore all SMILE electronics shall be immune to destructive SEL and protected against other Single Event Effect. All electronic components must also be able to withstand a TID of 60 krad [10]. In case critical components are marginally tolerant to the applicable dose, spot shielding will be applied.

#### 2.4.2 FPGA

The FPGA that is going to be used needs to be able to meet the requirements for radiation tolerance. In addition, it needs to be reliable and not draw too much power. The choice of using an FPGA is explained in Section 3.1.3.

An anti-fuse FPGA from Microsemi will be used for the main motor controller, either RTAX250 or RTAX1000, depending on design needs. NanoXplore NG-MEDIUM (NX1H35S) FPGA is kept as an option, but this is a brand-new component, so little or no space heritage exists for it.

#### Microsemi RTAX250

The RTAX family is the second generation of Microsemi's products for space applications. The RTAX250 FPGA has registers that are hardened for single event upsets. Being hardened, the registers are immune against single event upsets at a linear energy transfer of less than 37 MeV/cm<sup>2</sup>/mg. The FPGA will survive a TID up to 300 krad, which is above the demand of 20 krad. It is also immune against SEL with a linear energy transfer up to 117 MeV/cm<sup>2</sup>/mg. The RTAX series also comes with a low power option, which saves up to 80% of static current compared to the standard versions in the worst-case scenario [11].

#### 2.4.3 Stepper Motor

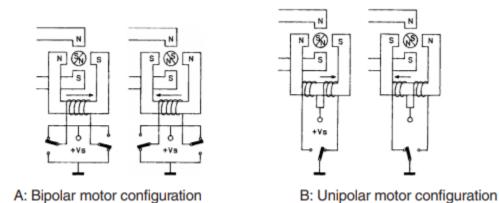

A stepper motor is an electrical motor that moves a single step when the magnetic field changes as a consequence of switching the direction of the current flow in the field coils. There are two principal types of stepper motors, as illustrated in Figure 7. The bipolar stepper motor, which has one coil per phase and needs two switches for each phase. The unipolar stepper motor, which has one coil for each phase and one switch for each phase. The current flow in the coil is reversed by flipping the switches [12].

#### Figure 7 Stepper motor configuration [12].

Our motor uses a bipolar configuration, and the advantage of the bipolar configuration is that there is only one coil with low winding resistance. The unipolar has a double winding with a higher winding resistance because of the thinner wire that is required. The advantage of the unipolar configuration is that is can have a simpler driver circuit for switching, whereas the bipolar requires a more complex driver circuit [12]. As previously discussed, the stepper motor used in the RSM is a phySPACE stepper motor. This stepper motor is bipolar and needs a driver circuit that fits it. By switching the direction of the current flow through the two coil pairs, the stepper motor is driven.

#### Stepper driver circuit

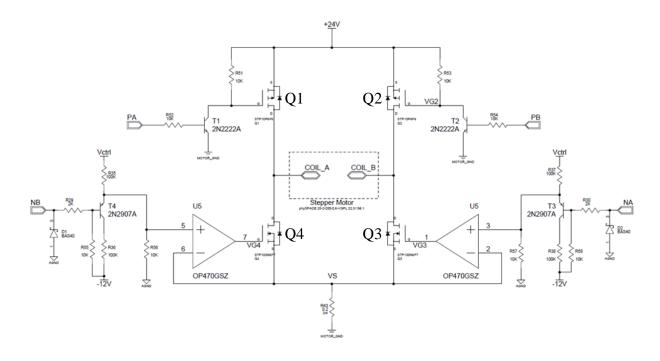

A common way to operate the two coil pairs is by using an individual H-bridge for each coil, as shown in Figure 8. This circuits main components are the four transistors and the coil forming an H-shape in the middle. The transistors have their own regulatory circuits that set the voltage on them to turn them on and off.

#### Figure 8 Stepper motor driver circuit H-bridge

The current through the transistors will excite the coils which in turn steer the stepper motor. Current will flow through the transistor pair Q1 and Q3, or Q2 and Q4. Q3 and Q4 are also forming constant current sources, enabling a controlled current flow in the inductors. The controlled current is set by the  $V_{ctrl}$  pulse, which is derived from a filtered pulse width modulator (PWM) source, connected to the FPGA. The current through the power transistors results in a voltage drop over  $R_{sense}$ , which is fed back via the operational amplifiers to control the power transistors. The terminals labelled PA, PB and NA, and NB is connected to the FPGA, again one set for each coil.

#### Step sequence

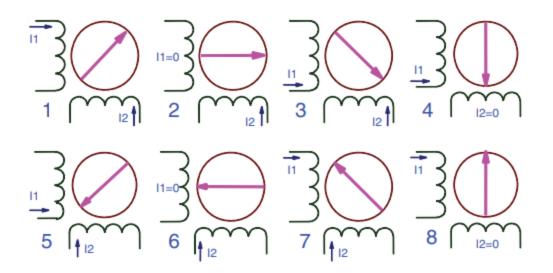

A change in the current through the coils will produce a step in the motor. With one pole pair to move the stepper, there are four full steps in each electrical cycle. Typically for stepper motors, each step will move 1.8° or 7.5°. With full steps, there will always be current through both the coils. Instead, the current can be turned off before switching to the other side as an intermediate step. This method is called half-step and gives eight half-steps instead of four full steps, as seen in Figure 9 [12].

Figure 9 Half-step sequence for a two-phase bipolar motor [12]

Using half steps effectively doubles the resolution of the stepper motor but comes at the cost of getting only about 70% torque [12]. The torque margin is more than large enough for us, and we can get a smoother operation with less mechanical stress by using half-step mode.

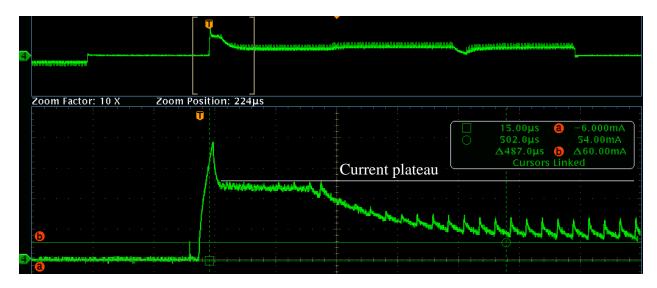

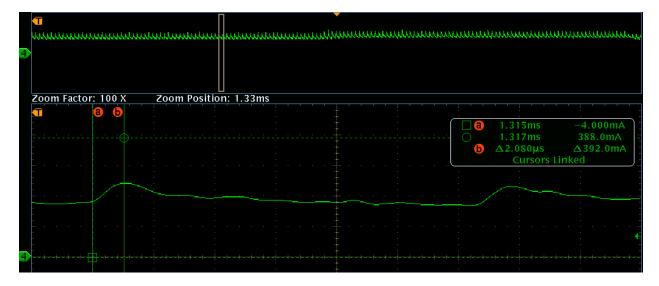

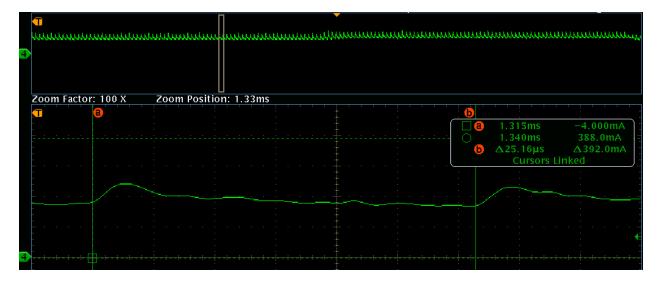

As shown in Figure 9, the current in one coil is sustained in one direction for three out of eight phases before turning off, and changing direction. Each motor-on sequence is always started by a programmable length settling time, in which transistor Q3 or Q4 is fully on, and the current limiter circuit controls the full current as described earlier. After that, current chopping is enabled, where transistor Q3 or Q4 is turned off and on again at regular programmable intervals, resulting in a current decay determined by the motor coil inductance, before the appropriate transistor is turned on again. By turning the inductor current on and of faster than the inductor manages to change the current significantly, we can hold the current at a nearly constant level. The current level will fall and be raised again to the current plateau where the current is at the set motor current level, before being allowed to fall again. This chopping of the motor current results in a significant reduction in average power as the power source will deliver less current in total.

As the settling time only is needed to get the motor current up to the desired current plateau where the current will stay if the corresponding transistor is on, it will have little effect on the torque the motor produces. The chopping is used to save current while simultaneously holding the inductor current near constant. As long as the inductor current stays at the current plateau and do not fall towards zero, the torque should be constant. The torque will have a breakpoint where the chopping causes a significant drop in the inductor current. As the current then will go towards 0, there will not be any power to create the torque. As torque will be a function of the inductor current, the main component of increasing the torque will then be the motor current as this sets the inductor current.

To be able to operate the motor with half steps, the transistors in the driver circuits needs to be turned on in the correct order, as shown in Figure 10. The driver needs to go through eight stages, corresponding to the eight half-steps. In order to reverse the motor direction, we need to run the half step sequence in the opposite direction by switching the A and B coil's driving sequence. As eight steps are needed for each direction, a state machine will need at least 16 states to drive the stepper motor.

Figure 10 H-bridge electrical cycle states for coil A and coil B for 8 half step phases

# 3 **RSE Development**

## 3.1 Software vs Hardware

In the first iteration of the RSE, a stepper driver breadboard was developed with a driver software placed on a microcontroller to drive a stepper motor. In this iteration, an elegant breadboard (EBB) was designed by the SMILE team, that is closer to the real version but still using commercial components. When this iteration of the RSE is done, an Engineering Qualification Model can be created, where the identical components to the ones used in flight will be used to test the functionality and the fit. At last, a Pre-Flight Model is made with the components that are going to used, and when it has passed the tests, it is upgraded to the Flight Model, which will be launched.

The RSE needs a firmware to control the stepper driver circuits as described in Section 2.3. There is no official definition of firmware, but in general, the term firmware is used about a code that is placed onto a device to control the low-level functions of the device. Typically, this is a software code that uses a microcontroller to execute the code. Another way of looking at this is to say that a hardware description language is also a firmware as it is synthesised and place onto an FPGA. At the core, it is, however, hardware instead of software.

## 3.1.1 FPGA

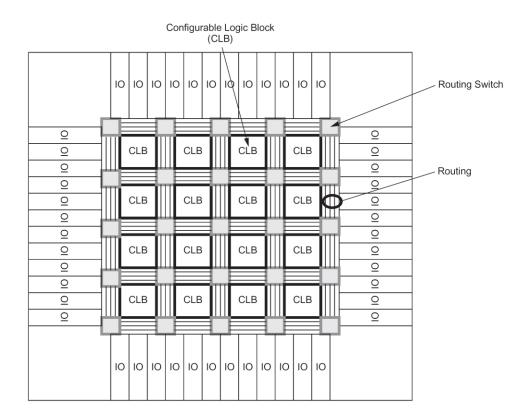

FPGA is an integrated circuit that consists of configurable logic blocks. These logic blocks are built up by using two different methods. Our FPGA uses anti-fuses to program the FPGA. The use of anti-fuses makes the FPGA one-time programmable. Other FPGAs can use static Random-Access Memory (RAM) or flash memory to hold the configuration of the logic blocks. A simplified FPGA floorplan is illustrated in Figure 11.

Figure 11 Simplified FPGA floorplan [13, p. 630]

Vendors sell the FPGA without a configuration, and the customer can then program the FPGA as desired. In our project, a reconfigurable FPGA is used to test the firmware. One-time programmable FPGA is often used in space projects, as they have proven to be reliable in a radiation environment [14].

## 3.1.2 Embedded system

"An embedded system is a microprocessor based system that is built to control a function or a range of functions", see for example [15]. The embedded system is a part of a larger system where its job is to control a function. One such microprocessor-based system is a microcontroller. "A microcontroller (sometimes called an MCU or Microcontroller Unit) is a single Integrated Circuit (IC) that is typically used for a specific application and designed to implement certain tasks" [16].

A microcontroller consists of multiple components as a Central Processing Unit (CPU), Integrated memory such as RAM and peripheral interfaces such as I/O ports. The CPU is the brain of the system that controls everything that happens.

Microprocessors come in different bit sizes, which indicate how wide the data bus is. As such an 8-bit microcontroller will utilise an 8-bit data bus. The bit size will limit the register widths, address bus and that every single instruction has a set range to work within. An 8-bit microcontroller can only work on 8 bits at a time, while a 32-bit microcontroller can work with 32 bits. This makes the smaller microcontroller useful if we want to save power. Whereas the larger microcontroller can use a more significant number of bits in its calculations, to get a more accurate result, or a number higher than the smaller microcontroller can handle. Being more precise comes with increased size, power usage, memory and price of the microcontroller.

The previous RSE design used an ATmega128 microcontroller, which is a low-power AVR 8-bit microcontroller. Microchip has a space version of the ATmega128 microcontroller called ATmegaS128. It is the same chip as the ATmega128 but has improved radiation toleration, and its main features are shown in Table 2. The original thought was to make a prototype on the ATmega128 and then transfer the system over to an ATmegaS128.

Table 2 Features of ATmegaS128 [17]

| Features                 | ATmegaS128                                        |

|--------------------------|---------------------------------------------------|

| Flash (KB)               | 128                                               |

| SRAM (KB)                | 4                                                 |

| EEPROM (KB)              | 4                                                 |

| External Memory (KB)     | 64                                                |

| General Purpose I/O pins | 53                                                |

| SPI                      | 1                                                 |

| USART                    | 2                                                 |

| ADC                      | 10-bit, up to 76.9ksps (15ksps at max resolution) |

| ADC channels             | 8                                                 |

| 8-bit Timer/Counters     | 2                                                 |

| 16-bit Timer/Counters    | 2                                                 |

| PWM channels             | 6                                                 |

| Operating voltage        | 3.0-3.6V                                          |

| Max operating frequency  | 8 MHz                                             |

| Temperature range        | -55°C to 125°C                                    |

The ATmegaS128 has "[n]o Single Event Latch-up below a LET threshold of 62.5 MeV/mg/cm2@125°C[, and is] tested up to a Total Ionizing Dose of 30 krads(Si) according to MIL-STD-883 Method 1019" [17]. Microchip also states that the microprocessor "has been developed and manufactured according to the most stringent requirements of MIL-PRF-38535 International Standards and Aerospace AEQA0239 specification" [17]. MIL-PRF-38535 is the US military's performance specification that "establishes the general performance requirements for integrated circuits or microcircuits and the quality and reliability assurance requirements, which are to be met for their acquisition" [18].

## 3.1.3 FPGA or CPU

Since this project will go onto a satellite that will be launched into space, we need a technology that is approved for usage in space. The previous RSE utilised a microcontroller as described in Lylund [3]. An appropriate microcontroller for the mission was found, the ATmegaS128. The main problem with the ATmegaS128 for us is that it does not have space heritage. Space heritage means that none or few space missions have used this microcontroller. Having used a particular technology multiple times proves that it performs reliably in space. Besides, ESA has a rigorous set of test procedures to test software and technology that are lacking space heritage. This would have meant that we would have to prove that the microcontroller would work.

Some alternative microcontrollers with increased bit sizes were considered, but those would also come at an increased cost and system complexity. An external memory might also have been necessary. There are, however, multiple FPGAs with space heritage that we could then use instead. As these FPGAs have space heritage and hardware would be used instead of software, we would have an easier time to get the design approved, as hardware are easier to get accepted by ESA's test procedures. In this project, the lack of space heritage and the easier test procedures made us abandoned the microcontroller, and switch to an FPGA.

In addition to the reasons above we wanted to take a more general view on an FPGA vs an embedded system. In embedded systems, the microcontroller reacts to stimuli on the different inputs, and from the incoming data and stored information, the system creates the desired output. The FPGA on the other side has dedicated logic to respond to the stimuli coming into the system. So, while the microcontroller would have to let the incoming data got through the CPU to create an output, the FPGA creates a logic block directly between the input and the output to speed up the response scientifically. To create this configuration, a hardware description language is required. VHDL (Very High-Speed Integrated Circuit Hardware Description Language) is one such language. A general comparison of a CPU and an FPGA is shown in Table 3.

Table 3 Comparison of CPU and FPGA adopted from [19]

|             | CPU                                                                                                     | FPGA                                                                                                                                                                                                            |

|-------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview    | Traditional sequential processor<br>for general purpose<br>applications                                 | Flexible collection of logic elements and IP blocks that can be configured                                                                                                                                      |

| Processing  | Single- and multi-core MCUs<br>and MPUs, plus specialized<br>blocks: FPU, etc.                          | Configured for application; SoCs include<br>hard or soft IP cores (e.g., Arm)                                                                                                                                   |

| Programming | OSes, APIs run a huge range of<br>high-level languages; assembly<br>language                            | Traditionally HDL (Verilog, VHDL)                                                                                                                                                                               |

| Peripherals | Wide choice of analogue and<br>digital peripherals in MCUs;<br>MPUs include digital bus<br>interfaces   | SoCs may include many transceiver blocks, configurable I/O banks                                                                                                                                                |

| Strengths   | Versatility, multitasking, ease<br>of programming                                                       | Configurable for a specific application;<br>configuration can be changed after<br>installation; high performance per watt;<br>accommodates massively parallel operation;<br>wide choice of features: DSPs, CPUs |

| Weaknesses  | OS capability adds high<br>overhead; optimized for<br>sequential processing with<br>limited parallelism | Relatively difficult to program; long<br>development time; difficult for floating-<br>point operations                                                                                                          |

# 3.2 State machine

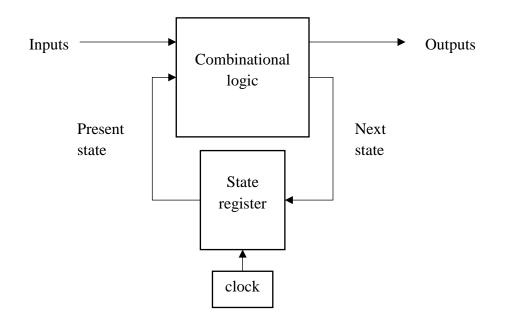

One of the core components of a sequential digital system is a state machine. A finite state machine is a sequential system that consists of combinational logic and a state register, as illustrated in Figure 12. The outputs of the FSM are a function of the current inputs and past inputs. The state gives information about previous data. The present state stored in the state register is the culmination of everything that has happened thus far, see for example [20].

Figure 12 Synchronous finite state machine block diagram [20]

The state machine can be asynchronous or synchronous. So, either the state and the outputs only update on the triggering clock edge, or it updates as soon as one input changes value.

## 3.3 VHDL development strategy

To be able to create a design and implement it, we need a plan so we can prioritise and stage the development. There are a lot of different strategies for developing a firmware system. Various approaches were considered to be able to develop the firmware efficiently.

## 3.3.1 Waterfall development method

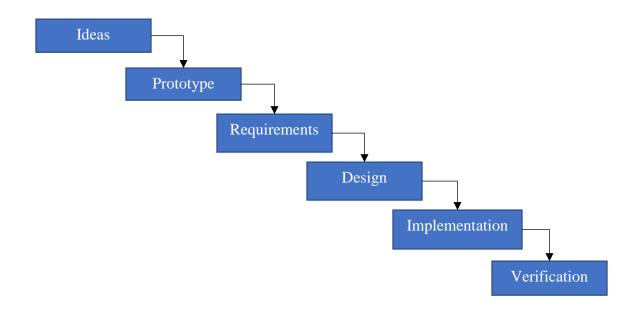

A common technique to use when developing a project is the so-called waterfall design strategy. The waterfall strategy bases itself upon that the requirements of the design need to be figured out before anything can be done. From these requirements, a design can be proposed. If the design is accepted, it can then be implemented.

At last, the implementation needs to be verified. No steep can be done before the completion of the previous. By going through the development step by step and locking down the different aspects before moving onto the next task, one can achieve good flow.

In the article "Understanding the pros and cons of the Waterfall Model of software development" Melonfire [21] comes with this explanation of the waterfall model:

"Essentially, it's a framework for software development in which development proceeds sequentially through a series of phases, starting with system requirements analysis and leading up to product release and maintenance. Feedback loops exist between each phase, so that as new information is uncovered or problems are discovered, it is possible to "go back" a phase and make [an] appropriate modification. Progress "flows" from one stage to the next, much like the waterfall that gives the model its name."

Tutorialspoint [22] says that the "[w]aterfall approach was first SDLC [Systems Development Life Cycle] Model to be used widely in Software Engineering to ensure [the] success of the project. (...) In this Waterfall model, typically, the outcome of one phase acts as the input for the next phase sequentially." A typical waterfall is shown in Figure 13.

#### Figure 13: Waterfall model

There is an ideas phase where people pitch the goals of design formulated and different designs, and from that, the development of a prototype is possible. These two phases are often presumed to have already happened in the waterfall model. An idea about what the system is and how it should function must be given in advance. From these ideas, a prototype can be developed to see if the proposals are possible and find out what requirements are needed. If there is not a lot of external

demands on the system, it can be hard to start with coming up with the requirements list. In a large software project, it is often useful to create a smaller version in a more straightforward language like python at first to get a feel for the solution. Such a prototype lets the developers have a look at the system and figure out what precisely the customer desires. Often it is hard to know precisely what is desired at an early stage.

A modification upon the waterfall strategy is to split the design up into different modules and create localised "waterfalls" where we go through the four aspects for a single module which exist in a bigger system which is the main "waterfall".

The main problem with the waterfall strategy is that requirements might change during the development. Such changes would be difficult to implement since one has to go back and change the previously done work.

### 3.3.2 Lean development method

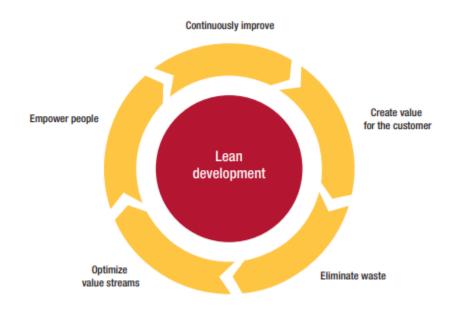

Another strategy is the lean software development method. According to Poppendieck and Cusumano [23], lean is more about a set of principles that are applied to development, and not a distinct practice.

Poppendieck and Cusumano [23] go on to explain the seven principles that lean is based upon. "Optimise the whole" is about seeing the software as a part of a larger system. Only then can the developer understand what the customer needs and want. "Eliminating waste" is the need to remove anything that does not contribute value to the customer or gives more or better knowledge about how to deliver value more effectively. "Build quality in" is also called "top-downprogramming". This method is about how smaller modules are continuously integrated into larger systems. "Learn constantly" is about how development is about developing knowledge and then placing that knowledge into a product. There are two ways to go about this. Either to learn first, or continuously learning throughout the development.

"Deliver fast" is how there are multiple in-house releases or releases to the customer. These releases are designed, developed and delivered repeatedly with small changes. "Engaging everyone" means that the software is only a part of a bigger system. There is different knowledge around in different departments and value might be lost if no one sees the system as a whole.

Decisions should be taken by the people who have the power and the knowledge about what they are deciding. "Keep getting better" is to realise that the known specific practices are often not the best for the current problem and that the system needs to adapt and improve over time [23]. How a development will flow is shown in Figure 14.

Figure 14 Lean development [24, p. 23]

## 3.3.3 Choosing a strategy

The Bergen SMILE team has put forth the ideas behind the system. From these ideas, Lylund has developed a software prototype to be used on a breadboard. They figured out most of the requirements during the creation of the prototype. This prototype was working and could run a stepper motor according to the current specifications at the time.

Since the SMILE project and the requirements for the RSE are changing during the development, the lean manufacturing strategy was selected. This project is the second iteration of the whole RSE project. Lylund and the SMILE team pitched the ideas and developed a prototype to work with a breadboard in the first iteration. The lean strategy bases itself upon reducing waste and focus on the value for the customer. In our case, this means that we focus on the necessary parts first and foremost. We will make a minimum viable product which can be accepted, and then we add functionality to it by continually adding changes and small new parts. This way, each step could

be designed, implemented, tested and accepted. This method let the requirements be nailed down for the barebone design. With a barebone design, we can expand upon it. While developing the system, we will learn about new situations and problems that we need additional requirements to solve.

# **4** Functionality

# 4.1 Design - VHDL

In the conclusion of Lylund [3], a potential FPGA design based upon his software design was proposed by the SMILE team, as shown in Figure 15. This design was our fundament. There are three primary tasks the design must accomplish. We need a method for communicating with the DPU, some way of storing essential information and a method for driving the motor. The components that make these three tasks possible is our barebone design. From that design, more functionality was added to protect the RSE.

Figure 15 FPGA design proposed by the SMILE team [3]

# 4.2 Registers

If the DPU is going to be able to retrieve or send any data to the RSE, the RSE needs some registers to store information. The registers are composed of multiple flip flops to store a logic vector. With various registers, they can be defined in order with addresses. Individual bits can also be specified. Via specified registers with set address and given content, the DPU can reliably access the RSE to read or write data. Typically, on the hardware side, these registers are situated in the register bank and can be probed from other modules.

### 4.2.1 Status registers

The DPU needs to know the status of the RSE and the RSM in order to be able to perform operations. The status registers will always be readable, but not writeable for the DPU, as the RSE maintains them. Most of these registers will come directly from the corresponding modules and therefore, be updated immediately. The status registers are shown in Table 4.

#### Table 4 Status registers

| Register                   | Address | Bits | Purpose                                               |

|----------------------------|---------|------|-------------------------------------------------------|

| Firmware Version           | 0x00    | 0-7  | FPGA firmware revision number                         |

| Motor Temperature          | 0x01    | 0-7  | Monitor motor temperature                             |

| Electronics<br>Temperature | 0x02    | 0-7  | Monitor electronics/heat-sink temperature             |

| Shutter status             | 0x03    | 0    | Shutter is closed                                     |

|                            |         | 1    | Shutter is open                                       |

|                            |         | 2    | Shutter closure in progress                           |

|                            |         | 3    | Shutter opening in progress                           |

|                            |         | 4    | Shutter emergency closure initiated                   |

|                            |         | 5    | Motor too hot                                         |

|                            |         | 6    | Electronics too hot                                   |

| HDRM status                | 0x04    | 0    | HDRM is armed                                         |

|                            |         | 1    | HDRM is activated (only valid for 1 sec)              |

| Performed steps L          | 0x05    | 0-7  | Number of steps performed for ongoing operation (LSB) |

| Performed steps H          | 0x06    | 0-7  | Number of steps performed for ongoing operation (MSB) |

| Heartbeat count            | 0x07    | 0-7  | Incremented for every heart-beat register request     |

| Processor status           | 0x08    | 0    | Heartbeat missing                                     |

|                            |         | 1    | Reset armed                                           |

#### Firmware version

The firmware version register contains the current firmware revision number so that any revisional changes can be detected. The set number also gives the DPU something stable to read during testing as the value is not changed. During testing on board, we can read this register, and since we know what to expect, we can detect any errors in the communication.

#### Motor temperature

This register is the current sampled motor temperature. The motor temperature will be regularly updated as long as the  $\pm 12V$  rails are enabled. The heat will be measured with a periodic readout of the thermistor voltage. The motor temperature will increase if a motor operation is in progress. Rest of the time, nothing should be happening, so there should be no generation of heat. So, most of the time, the temperature should be following structural temperature.

#### **Electronics temperature**

The electronics temperature register is the current sampled temperature of the electronics driving the motor. The temperature is read together with motor temperature in the same procedure. Like the motor, the driver electronics temperature should increase when the motor is running, and other than that, the temperature should be stable.

#### Shutter status

To keep track of the shutter operation and position, we need a register to keep up with the state of the shutter. The definition of every single bit in the shutter status register is shown in Table 4. We need to know if the shutter is open or closed. The easiest way of knowing this is to see if the corresponding end switch is engaged. Should the end switches stop working, the last run command needs to be remembered by the DPU. If an operation is running, no other operation can be accepted, so the current running operation must be able to be read by the DPU. At last, the DPU needs to know if the motor or electronics temperature is exceeding safe limits.

#### **HDRM** status

This functionality will not be used beyond the EBB. The HDRM status register indicates the status of the HDRM, as described in Table 4. There are only flags indicating if HDRM has been armed or activated, as no sensors are measuring the HDRM. The HDRM must be armed before it can be

activated. The HDRM will stay armed for 1 sec. If any other write command than HDRM activate is performed, the HDRM will disarm. The point of arming the HDRM is to ensure that the shutter is not released before the satellite is in place. The HDRM active will only be active for one second.

#### Performed steps L/H

These two registers count the number of steps the motor has taken during the ongoing or last operation. The low register contains the least significant byte, and the high register contains the most significant byte. When the maximum number these two registers can hold is reached, the number will wrap-around back to 0.

#### **Heartbeat count**

The primary purpose of this register is the safety handling of the radiation shutter. This heartbeat count is set up to protect the instrument by closing the shutter in case of a DPU failure. The DPU must access this register minimum every 30 sec or the RSE will initiate an emergency closure. This register will start with a 0, and each access will increment the content. In order to prevent overflow, the number will wrap-around.

#### **Processor status**

The status of the RSE firmware system, as described in Table 4. The two signals here are the heartbeat missing, which indicates that the heartbeat has gone 30 sec without having been read and that an emergency closure is initiated. The reset functionality is designed the same way as the HDRM. This means that there is a reset armed signal that needs to be set before the system can be reset to prevent any accidental resets.

#### 4.2.2 Control registers

The DPU needs to be able to control the operation and to do that we need some control registers. These registers need to be read/write register. The control register is shown in Table 5.

Table 5 Control registers

| Register                                  | Address | Default<br>value | Purpose                                                                                                         |

|-------------------------------------------|---------|------------------|-----------------------------------------------------------------------------------------------------------------|

|                                           |         | value            |                                                                                                                 |

| Motor current                             | 0x20    | 100              | Set stepping current. 0xFF for max available current                                                            |

| Settling time                             | 0x21    | 20               | Ramp up time allowed to reach set motor<br>current before chopping start, in steps of 4<br>microseconds         |

| Chop duty cycle                           | 0x22    | 150              | Step Motor chop duty cycle time in units of clock cycles relative to 256                                        |

| Max acceptable motor<br>temperature       | 0x23    | 170              | For motor protection. 0xFF for no temperature protection                                                        |

| Max acceptable<br>electronics temperature | 0x24    | 170              | For electronics protection. 0xFF for no temperature protection                                                  |

| Max steps for operation L                 | 0x25    | 255              | Number of steps allowed before the operation is aborted (LSB)                                                   |

| Max steps for operation<br>H              | 0x26    | 255              | Number of steps allowed before the operation is aborted (MSB)                                                   |

| Enable ±12 V                              | 0x27    | 0                | Set to 1 to enable ±12 V rails                                                                                  |

| Max motor current                         | 0x28    | 205              | Maximum allowed motor current. In order to<br>set motor current higher, this register must be<br>changed first. |

#### Motor current

The motor current register controls the duty cycle of a PWM, in order to set the current level for the motor driver. The output of the PWM is the  $V_{ctrl}$  shown in Figure 8. The PWM starts with an output of '1' and counts until the motor current value is reached, where it switches to '0'. The register can contain 0-255, where 255 will be the maximum current.

#### Settling time

The settling time register is in control of the duty cycle of a PWM, but this PWM will only send one pulse on each start and not wrap around for a new pulse. As the settling time signal will only be used in the start of turning on a new set of motor driver transistors, it is is easier to give the settling time a reset signal that initiates a single pulse instead of having to ignore the rest of the pulses.

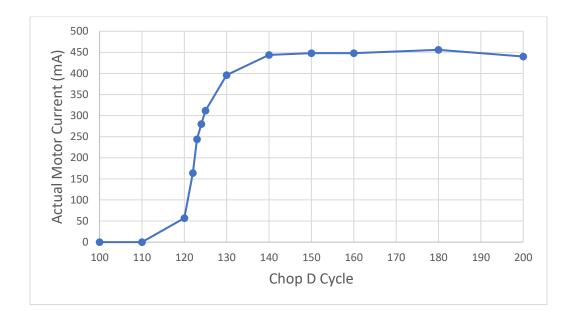

#### Chop Duty cycle

Chop Duty cycle controls the duty cycle of another ordinary PWM, in order to control the current chopping. Chopping is described in Section 2.4.3. The chopping will start with a '1' and switch to a 0 when the register value is reached. Should the register be set to the maximum value 255, then there will be no chopping so that the current from the transistors will be DC.

#### Max acceptable motor temperature

This register contains the maximum allowed motor temperature. The measured temperature is compared to the maximum allowed, and should it exceed the maximum the motor operation will have to wait to let the motor cool down. This maximum limit is to ensure that the motor does not overheat and degrade consequently. Should we want to ignore the temperature measurement, the maximum acceptable temperature is set to the maximum register value, as no measured value can exceed it.

#### Max acceptable electronics temperature

The max acceptable electronics temperature is set as the mac acceptable motor temperature, to protect the driver circuit electronics. The driver transistors will degrade and might stop working should they overheat. The temperature is measured and compared to the maximum the same way the max acceptable motor temperature works, and also halt any running operation should the temperature exceed the maximum allowed.

#### Max steps for operation

The max steps for operation limit the open/close shutter - max number of steps operation. The operation will run until it reaches the maximum number of steps where it will end. The operation is explained in Section 4.4.1.

#### Enable ±12 V

The LSB of this register will turn on and off the power rails to the driver circuits. Turning off the power will stop any commands from happening as a driving current cannot be created. Not having the power on will also stop any leakage through the transistors so that power is saved.

#### Max motor current

Max motor current acts as a safeguard on the motor current register, so that the motor current cannot be set above the max current without increasing the max motor current. The maximum current should be set so that the motor and the driver electronics don't overheat to extensively.

### 4.2.3 Debug registers

A debug register can be written or read-back for verification. These registers, as shown in Table 6, are used for various RSE debugging tasks.

| Register             | Address | Default<br>value | Read/<br>Write | Purpose                                                   |

|----------------------|---------|------------------|----------------|-----------------------------------------------------------|

| Disable blinking LED | 0x30    | 0                | R/W            | 0x01 Disable the blinking LED                             |

| Seconds since access | 0x31    | NA               | R              | Number of seconds since last<br>heartbeat register access |

Table 6 Debug registers

#### **Disable blinking LED**

To be able to easily check that that communication works while testing the system on board the disable blinking LED register is used. This register will be used to control a blinking LED on a test pin on the breadboard. The blinking LED will be on when the FPGA is programmed or reset. If the LED is blinking the system is properly reset and functioning. Then the disable blinking LED register can be written to, to disable the blinking led. If the LED stops blinking, then the communication is working.

#### Seconds since access

This register enables monitoring of the heartbeat register timer during testing, for example, to see that it counts the correct amount before initiating the emergency closure.

### 4.2.4 Command register

A command is used to perform RSE operations like opening the radiation shutter and closing it, by writing to the control register. The register is automatically reset to zero after receiving a new command and will therefore always read 0x00, and is shown in Table 7.

Table 7 Command registers

| Register         | Address | Default value | Purpose                                               |

|------------------|---------|---------------|-------------------------------------------------------|

| Command register | 0x40    | 0             | Register to take commands. Commands listed in Table 8 |

# 4.3 Operational procedures

After power-up and initialisation of the RSE, the DPU should check the RSE status registers to confirm normal operation. In particular, the heartbeat counter register should be accessed regularly to prevent emergency closure of the RSM, see Section 4.2.1. After that, the DPU should configure the parameters of the control registers according to specifications and requirements. Then, after renewed confirmation of nominal conditions, the commanding of RSM opening or closure can be performed.

### 4.3.1 Emergency closure

The heartbeat function work as a register that needs to be accessed to safeguard the system. The RSE is dependent on commands from the DPU to perform operations. Should the DPU malfunction or the communication link not work, the RSE will need to protect the SXI instrument as the RSE does not know if the satellite is within the radiation belt of the earth or not. Should this happen, an emergency closure needs to be performed.

The emergency closure will be initiated 30 seconds after the last heartbeat was received. At this point, the power rails to the driver circuit are dependent on the enable  $\pm 12V$  rails register. The

register needs to be overridden as the rails could be either on or off. When turning the power rails one, we need to wait one additional second to ensure the power rails are fully on, as they will have some delay turning on. During this if the DPU can reaccess the RSE it should be able to cancel the emergency closure and return to normal operation, as being able to access the RSE at this stage should indicate the DPU is still working.

After the power rails have been on for a second, an emergency closure will be initiated. This closure will go on until the end switch is engaged. This operation will also be able to cancel, as to more rapidly get the shutter open again should the DPU be able to access the RSE quickly after the emergency procedure was initiated. When the shutter is closed, or the operation was cancelled, the RSE will wait for a new heartbeat before any new motor operation is allowed.

An emergency closure will adhere to the max acceptable temperature registers, to not destroy the radiation shutter. Should the temperature be disregarded, the max acceptable temperature needs to be set to the maximum register value. This way the operators of the satellite will be able to select if they want a fast closure at the expense of the degradation of the radiation shutter, or if a slower closure with the risk of degrading and damaging the instrument be acceptable. As destroying the radiation shutter will either shut the instrument inside or leaving it exposed to high energy radiation, while saving the radiation shutter can damage the instrument.

#### 4.3.2 Temperature reading

Two temperatures need to be read: the motor and the driver electronics. There is a pt100 thermistor on each that is connected to an analogue-to-digital converter. The minimum and maximum temperature allowed on the motor are from -150°C to 70°C [7] and on the electronics -55°C to 80°C [10]. The value of the two temperatures will be sampled each second as long as the power rails are on.

### 4.4 Command operations

A command will result in activation of the required procedure, or an error response, as discussed in Section 4.6. If, for example, the motor or electronics temperature is too high, the operation is not permitted, but if the motor or electronics temperature becomes too high during RSM closure/opening, the RSE will suspend the operation until the temperature is below the threshold. In the latter case, no intervention is required from the DPU side, but in case of an emergency, the operation may be aborted, in order to adjust the temperature thresholds before reissuing the RSM operation.

There is a set of sporadic operations that operates the stepper motor or the HDRM or are used to reset the RSE. These commands can be performed at any time, from the DPU. The command register is made to accept these commands into it and then perform the corresponding action. The command register is a write-only register, which clears directly after having been written to. All commands are shown in Table 8.

| Register        | Address | Command<br>identifier | Purpose                                      |

|-----------------|---------|-----------------------|----------------------------------------------|

|                 | 0.40    |                       |                                              |

| Open Shutter    | 0x40    | 0x01                  | Open Shutter, run motor until end stop       |

| Stop at end     |         |                       | detected                                     |

| Close Shutter   | 0x40    | 0x02                  | Close Shutter, run motor until end stop      |

| Stop at end     |         |                       | detected                                     |

| Open Shutter    | 0x40    | 0x04                  | Open Shutter, run maximum no of step         |

| Max no of steps |         |                       | regardless of end-stop detection             |

| Close Shutter   | 0x40    | 0x08                  | Open Shutter, run maximum no of step         |

| Max no of steps |         |                       | regardless of end-stop detection             |

| Emergency close | 0x40    | 0x10                  | Close Shutter as fast as possible, run motor |

| Stop at end     |         |                       | until end stop detected                      |

| Arm Reset       | 0x40    | 0x20                  | Arm Reset Function                           |

| Reset           | 0x40    | 0x22                  | Reset RSE FW                                 |

| Arm HDRM        | 0x40    | 0x40                  | Arm Activate Hold Down and Release           |

|                 |         |                       | Mechanism                                    |

| Activate HDRM   | 0x40    | 0x42                  | Activate Hold Down and Release Mechanism     |

| Cancel command  | 0x40    | 0x80                  | Cancel any ongoing command                   |

#### Table 8 Commands

Five commands start the motor, two that are necessary to reset the RSE, two for activating the HDRM and a final command that cancels whatever is ongoing. The HDRM commands will not be used after the EBB, as they are not needed.

#### 4.4.1 Motor commands

The motor needs to have at least one open and one close shutter command. Since the shutter has end switches for open and closed, these can be used to end a command. In case of a malfunction in one of the end switches, there needs to be an alternative set of commands to open and close the shutter. These operations will be suspended should a temperature reading exceed the maximum allowed temperature, to allow the electronics and/or the motor to cool down. Temperature readings will be performed regularly so that the operation can continue.

#### **Open/Close Shutter – Stop at end**

These commands are designed to be utilised during the regular operation. The purpose of these is to open or close the shutter. This operation is performed until the end switch is engaged.

#### **Open/Close Shutter – Max no of steps**

The stop at end commands is reliant on that the end switches work. In case the end switch stops working, there needs to be another method of getting the shutter open and closed. These two commands work independently of the end switch and will then work if the end switches fail. The max number of steps command uses a set control register to run. The operation will start and count the number of steps. It will run until it reaches the set maximum number of steps, before ending the operation.

#### Emergency close – Stop at end

The emergency close – stop at end command operates the same way that the normal close shutter stop at end command. It was held as an option that this command could ignore temperature readings, but it was decided that the command should wait if the motor or electronics got too hot. Therefore, this command is now identical to the regular close shutter command. If the motor or electronic temperature should be ignored, then the max allowed temperature registers should be set to max.

#### 4.4.2 Other commands

There is a couple of other commands that are not directly related to the stepper motor.

#### Arm Reset & Activate Reset

The arm reset command will arm the reset function. This signal will hold reset armed for 1 sec, where it will be unarmed if nothing is written to the RSE. If anything, other than a activate reset is written, it will unarm. The activate command will activate the armed reset signal. Only when the reset is armed and activated within 0 seconds after it was armed, will a reset of the RSE be performed.

#### Arm HDRM & Activate HDRM

Arm HDRM arms the HDRM signal, in the same way, the arm reset work. After 1 second or should any other write operation than activate HDRM be performed, the HDRM signal will be unarmed. The activate HDRM command needs to come within that time limit to activate the armed HDRM signal. The two HDRM commands will only be used on the EBB as they are not needed after. After EBB the PSU will activate the HDRM.

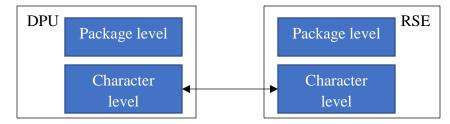

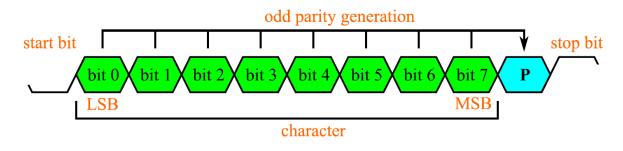

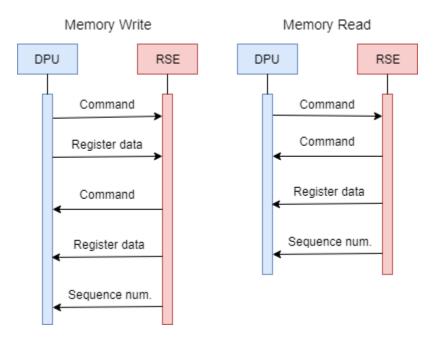

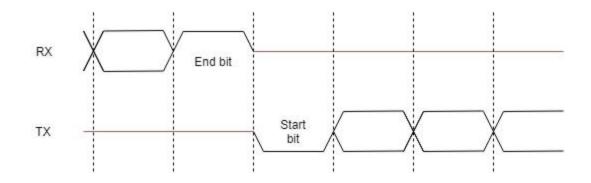

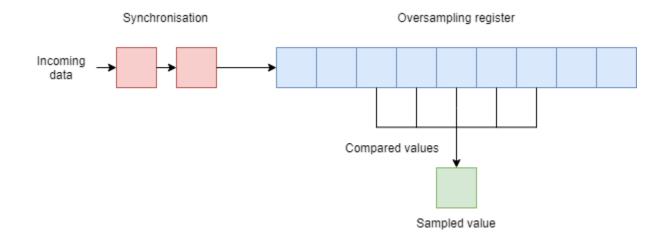

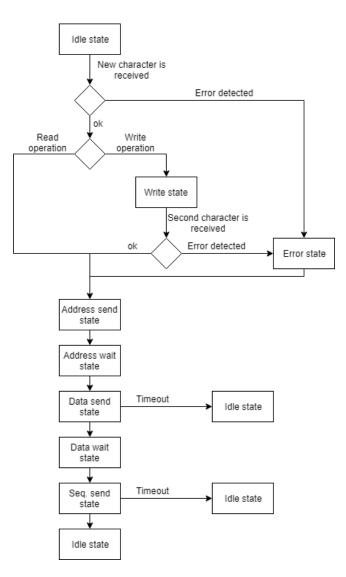

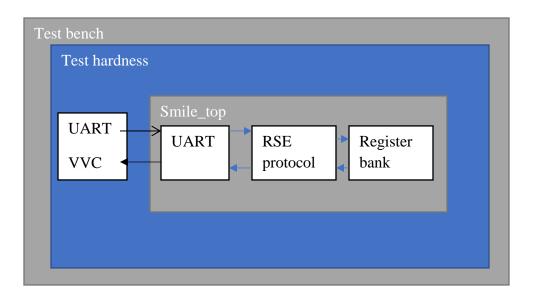

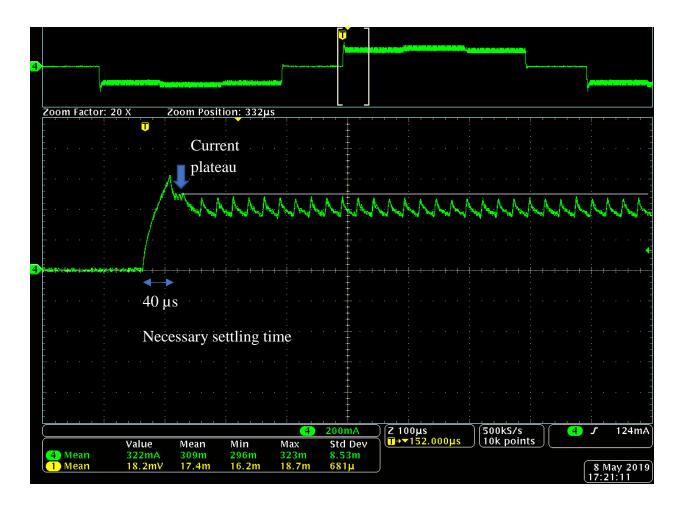

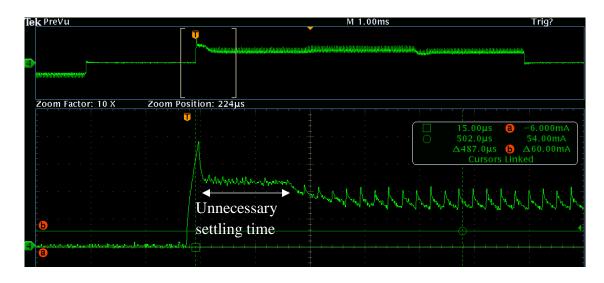

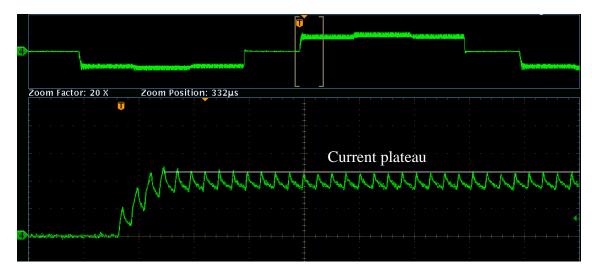

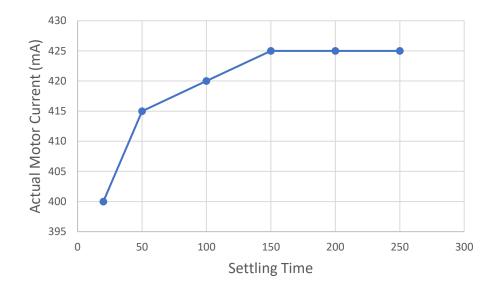

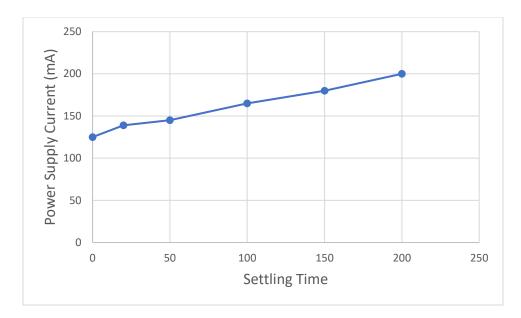

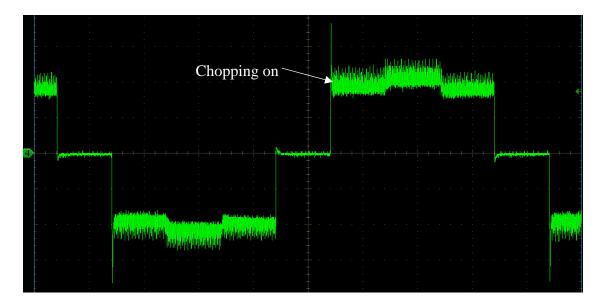

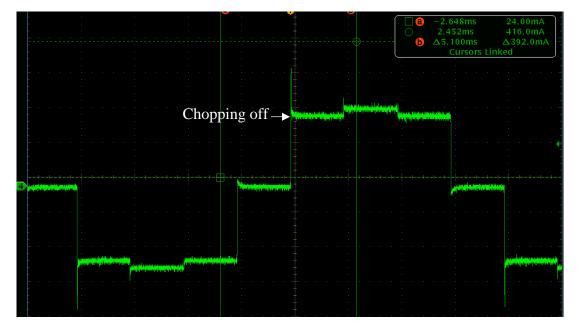

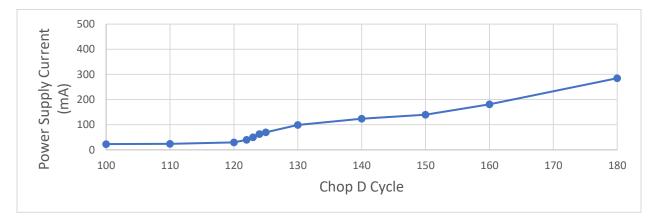

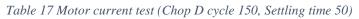

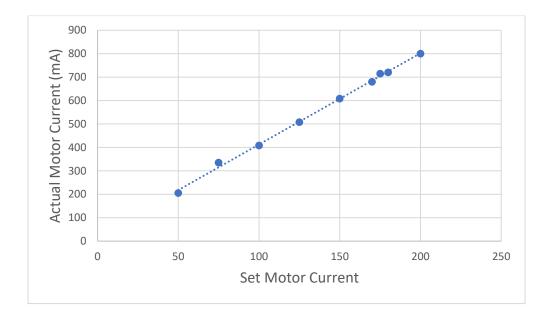

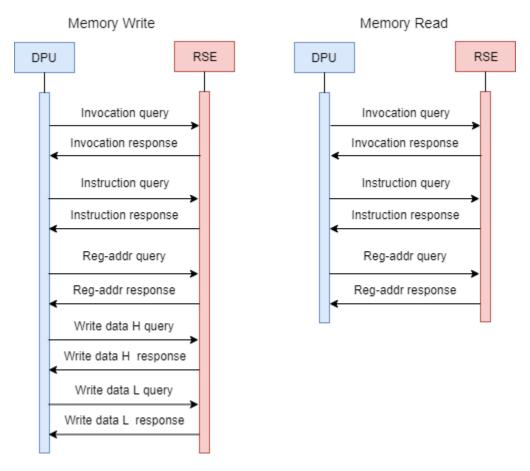

#### **Cancel command**