# Design, Verification and Testing of a Digital Signal Processor for Particle Detectors

Arild Velure

Thesis for the degree of Philosophiae Doctor (PhD) University of Bergen, Norway 2019

UNIVERSITY OF BERGEN

## Design, Verification and Testing of a Digital Signal Processor for Particle Detectors

Arild Velure

Thesis for the degree of Philosophiae Doctor (PhD) at the University of Bergen

Date of defense: 14.08.2019

#### © Copyright Arild Velure

The material in this publication is covered by the provisions of the Copyright Act.

| Year:  | 2019                                                                                  |

|--------|---------------------------------------------------------------------------------------|

| Title: | Design, Verification and Testing of a Digital Signal Processor for Particle Detectors |

|        |                                                                                       |

|        |                                                                                       |

Name: Arild Velure

Print: Skipnes Kommunikasjon / University of Bergen

### Acknowledgements

This work has been carried out within the Microelectronics Research Group and the Experimental Nuclear Physics group at the Department of Physics and Technology, University of Bergen, during the period of May 2013 to May 2017.

I would like to thank my supervisors Kjetil Ullaland and Dieter Röhrich for guidance and support throughout the work of this thesis.

I would additionally like to extend my thanks to the SAMPA team for an excellent collaboration. Bruno Sanches, Hugo Daniel Hernandez Herrera and Alex Kluge for which without, this project would have been pale in comparison. Marco Bregant, Marcelo Gameiro Munhoz, Wilhelmus Van Noije and Armando Ayala Pabon for well-executed project organization. And also a special thanks to the rest of the Brazil team, Heitor Neves, Raul Acosta Hernandez, Tiago Oliveira Weber, Dionisio Carvalho, Danielle Moraes, Stelvio Barboza, Shiroma Montali, Heiner Grover Alarcon Cubas, Arthur Lombardi Campos and Andre Luis Do Couto.

I extend my thanks to the detector groups, which I have interacted with during my work and their help in testing the chip to prove its potential. The TPC group; Kenneth F. Read, Charles L. Britton, LLoyd G. Clonts, Anders Oskarsson, Ulf Mjörnmark, David Silvermyr, Jonathan Adolfsson, Torsten Alt, Sebastian Klewin, Matthias Richter, Christian Lippman. The MCH group; Valerie Chambert, Khaing Mon Mon Tun-Lanoë, Hervé Borel, Christophe Suire, Cristophe Flouzat, Clément de Barbarin, Patrice Russo, Emmanuel Rauly, Gwenaël Brulin and Noël Guillaume. Tonko Ljuibicic at the STAR detector and Alexander Pilyar at the Dubna group.

For introducing me to the wonders of the S-ALTRO, I would like to thank Paul Aspell and Tiina Sirea Naaranoja.

Finally I would like to thank my collaborators and colleagues at the University of Bergen and Oslo whom I have shared a great time with; Ganesh Jagannath Tambave, Johan Alme, Sohail Musa Mahmood, Ketil Røed, Attiq Ur Rehman, Chengxin Zhao, Lars Bratrud, Kristian Smeland Ytre-Hauge, Anders Mikkelsen, Anders Østevik, Kristian Philip Engeseth, Christian Torgersen, Inge Nikolai Torsvik, Damian Wejnerowski, Håvard Rustad Olsen, Simon Voigt Nesbø, Shiming Yang, Øyvind Lye, Hans Schou, Magnus Pallesen and Kavitha Østgaard.

I will always be indebted to my colleagues Ryan Hannigan and Matteo Lupi for their services rendered in proofreading of this thesis.

### Abstract

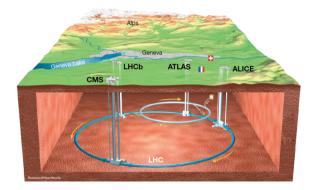

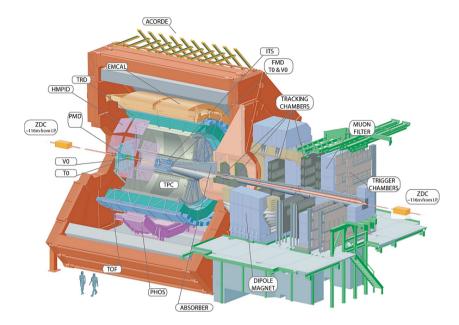

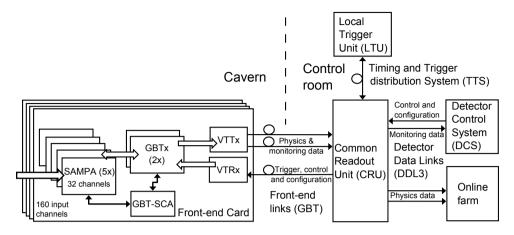

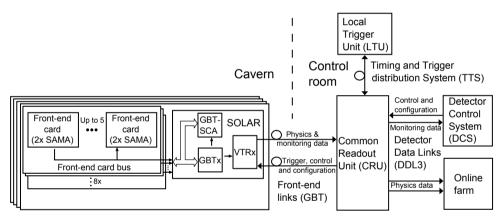

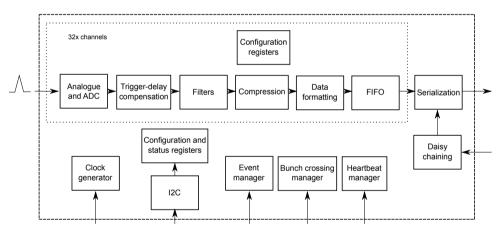

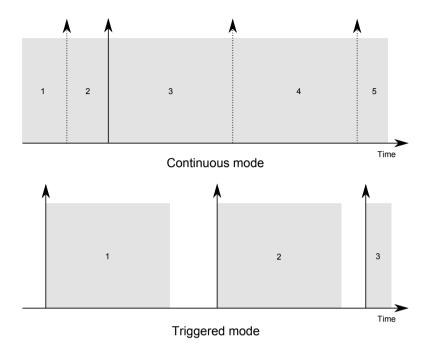

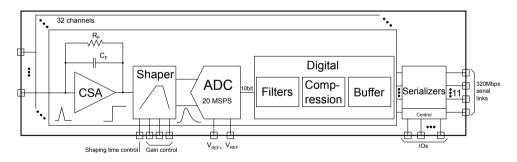

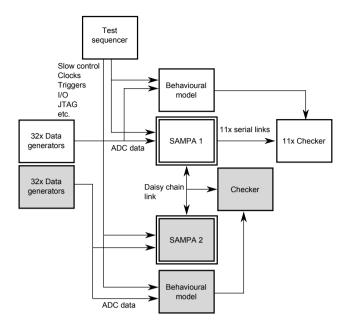

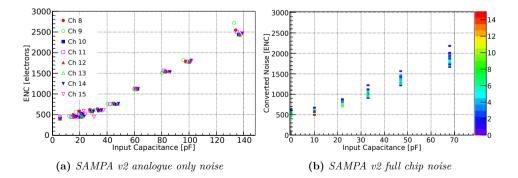

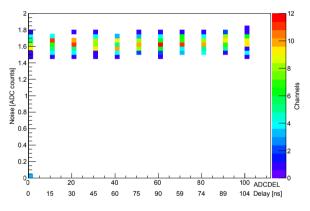

The A Large Ion Collider Experiment (ALICE) at the Large Hadron Collider at CERN is upgrading two of its sub-detectors, the Time Projection Chamber and Muon Chambers, with new front-end electronics to handle the expected higher Pb–Pb collision-rates in the next running period (Run 3) foreseen to start in 2021. The higher collision rate requires the detectors to employ a continuous readout of the data from the front-end, in contrast to the previous triggered readout. The devices currently employed for the readout of the detectors can only operate in triggered mode and need to be replaced. A new 32-channel integrated circuit called SAMPA has been designed to match the requirements of both detectors. The SAMPA device contains a charge sensitive amplifier, a pulse shaper, and a 10-bit 10 MHz analogue to digital converter for each channel and a common digital signal processor part. The digital signal processor provides various signal filtering and conditioning operations to improve on the data compression ability. Acquisition can be done in either triggered or continuous mode and the data is offloaded through 320 Mbps differential serial links, allowing a data throughput of up to 3.2 Gbps.

The first prototype of the SAMPA was delivered in 2014, the second in 2016 and the third was delivered in end of 2017. The final production run was done in mid-2018 and completed the testing at the end of 2018. Front-End Card production and testing is underway and the Muon Tracking Chamber (MCH) and Time Projection Chamber (TPC) are ready for installation in mid-2019.

The main purpose of this thesis has been to specify, design, test and verify the digital signal processing part of the SAMPA device to encompass the needs of the detectors involved. Innovative solutions have been employed to reduce the bandwidth required by the detectors, as well as adaptations to ease data handling later in the processing chain.

By means of simulations, test procedures, verification methods and applied

methods for design of reliable systems, a major part of the work has been on qualifying the design for submission to production. Since the design submission process and the following production time of the device is quite long and as the only means of verifying and reading out data from the analogue front-end and the analogue to digital converter is through the digital part of the device, it is of the essence to have a complete functioning prototype of the digital design before submission.

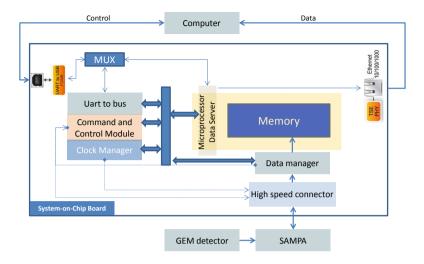

A high-speed data acquisition system was developed to enable test and verification of the produced devices. It has been used in all facets of qualification of the device for use by the detectors.

Three rounds of prototypes have been produced and tested. Only minor modifications to the digital design were added between the second and third prototype. The final production of about 80 000 devices has been completed with the same design as for the third prototype. No major issues have been found in the final design.

The design and test features implemented in the design have been utilized in the production testing and a final yield of close to 80% have been reached.

## Contents

| A        | ckno  | wledge         | ements                          | i    |

|----------|-------|----------------|---------------------------------|------|

| A        | bstra | nct            |                                 | iii  |

| A        | crony | $\mathbf{yms}$ |                                 | xvii |

| 1        | Intr  | oducti         | ion                             | 1    |

|          | 1.1   | The A          | ALICE experiment                | . 1  |

|          |       | 1.1.1          | Physics goals                   | . 2  |

|          |       | 1.1.2          | Detector and sub-detectors      | . 2  |

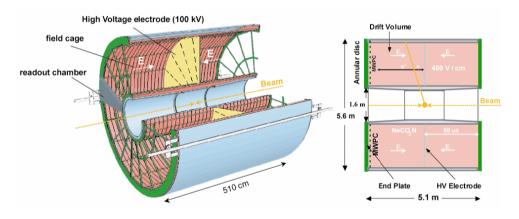

|          |       |                | 1.1.2.1 Time Projection Chamber | . 3  |

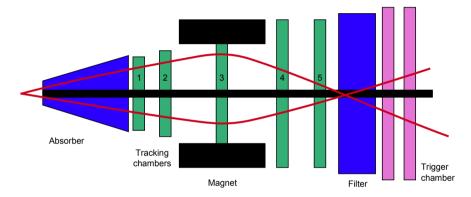

|          |       |                | 1.1.2.2 Muon Spectrometer       | . 4  |

|          |       | 1.1.3          | Current front-end electronics   | . 5  |

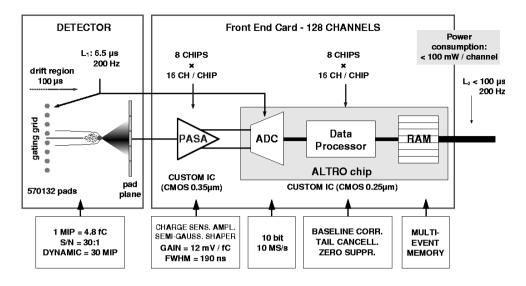

|          |       |                | 1.1.3.1 Time Projection Chamber | . 6  |

|          |       |                | 1.1.3.2 Muon Tracking Chambers  | . 7  |

|          | 1.2   | LHC I          | Run 3 upgrades                  | . 8  |

|          |       | 1.2.1          | Motivation for TPC upgrade      | . 8  |

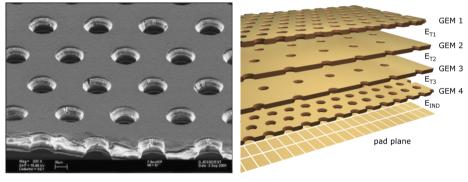

|          |       | 1.2.2          | Principal operation of GEMs     | . 9  |

|          |       | 1.2.3          | Motivation for MCH upgrade      | . 10 |

|          | 1.3   | Prima          |                                 | . 10 |

| <b>2</b> | Fro   | nt-end         | electronics                     | 13   |

|          | 2.1   | Herita         | ıge                             | . 13 |

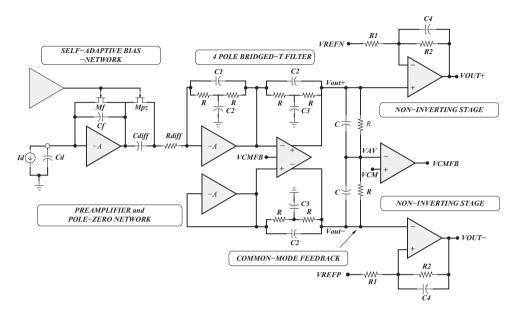

|          |       | 2.1.1          | PASA                            | . 14 |

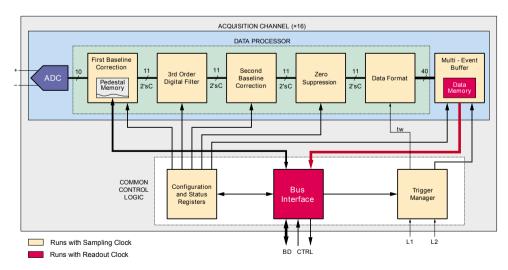

|          |       | 2.1.2          | ALTRO / S-ALTRO                 | . 16 |

|          | 2.2   | Comm           | non readout electronics         | . 17 |

|          | 2.3   | Design         | n requirements                  | . 18 |

|     | 2.3.1  | TPC rea     | adout electronics                                 | 20 |

|-----|--------|-------------|---------------------------------------------------|----|

|     | 2.3.2  | MCH re      | eadout electronics                                | 21 |

|     | 2.3.3  | Commo       | n requirements                                    | 22 |

|     |        | 2.3.3.1     | Technology                                        | 22 |

|     |        | 2.3.3.2     | Noise                                             | 22 |

|     |        | 2.3.3.3     | Data compression using zero suppression           | 23 |

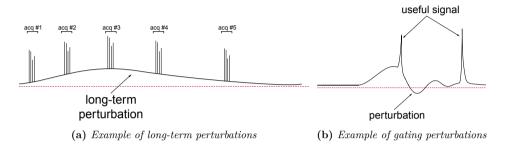

|     |        | 2.3.3.4     | Baseline correction                               | 23 |

|     |        | 2.3.3.5     | Power consumption                                 | 24 |

|     |        | 2.3.3.6     | Slow-control                                      | 24 |

|     |        | 2.3.3.7     | Reliability                                       | 25 |

|     |        | 2.3.3.8     | Design for testability                            | 25 |

|     | 2.3.4  | TPC sp      | ecific requirements                               | 25 |

|     |        | 2.3.4.1     | Digital filter                                    | 26 |

|     |        | 2.3.4.2     | Other compression scenarios                       | 26 |

|     |        | 2.3.4.3     | Readout ordering                                  | 26 |

|     |        | 2.3.4.4     | Interfaces                                        | 27 |

|     | 2.3.5  | TPC sp      | ecific requirements, revised architecture         | 27 |

|     |        | 2.3.5.1     | Direct readout serialization                      | 28 |

|     | 2.3.6  | MCH sp      | pecific requirements                              | 28 |

|     |        | 2.3.6.1     | Daisy chaining                                    | 29 |

|     |        | 2.3.6.2     | Data compression using zero suppression and clus- |    |

|     |        |             | ter summing                                       | 29 |

|     |        | 2.3.6.3     | Physical size                                     | 29 |

|     | 2.3.7  | Other d     | etectors                                          | 30 |

|     |        | 2.3.7.1     | RHIC STAR                                         | 30 |

|     |        | 2.3.7.2     | NICA MPD                                          | 31 |

| 2.4 | Digita | l specifica | ation                                             | 32 |

|     | 2.4.1  | Event n     | nanagement                                        | 32 |

|     | 2.4.2  | Interfac    | ing                                               | 34 |

|     | 2.4.3  | Serial li   | nk data protocol                                  | 35 |

|     |        | 2.4.3.1     | Lossless encoding                                 | 38 |

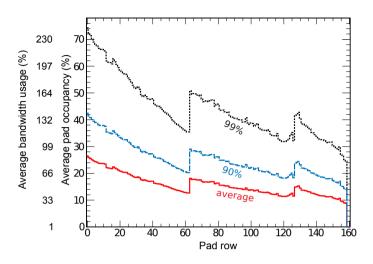

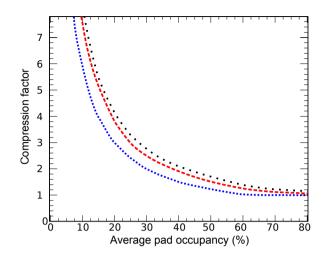

|     |        | 2.4.3.2     | Bandwidth TPC                                     | 40 |

|     |        | 2.4.3.3     | Bandwidth MCH                                     | 42 |

| 3 | SAI | MPA c  | hip impl   | ementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>47</b> |

|---|-----|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 3.1 | Archit | ectural ov | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47        |

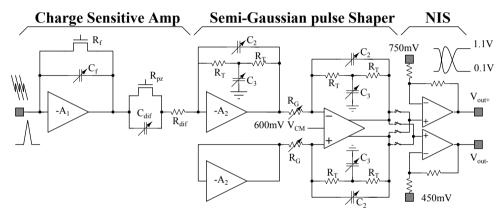

|   |     | 3.1.1  | Analogue   | e front-end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48        |

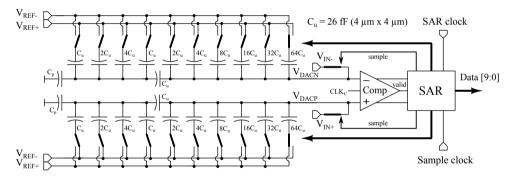

|   |     | 3.1.2  | Analogue   | e to digital converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49        |

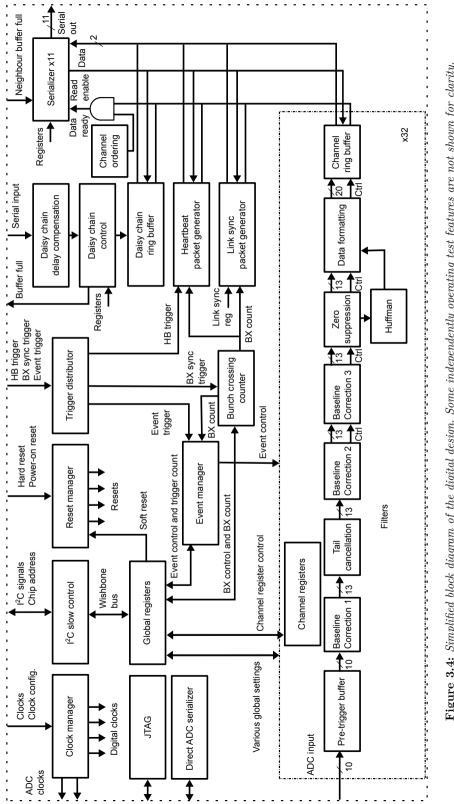

|   | 3.2 | Digita | l impleme  | ntation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50        |

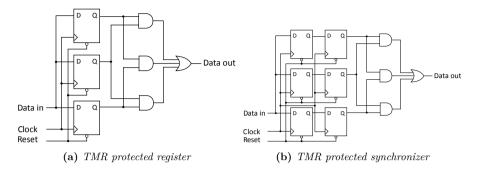

|   |     | 3.2.1  | System s   | ervices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53        |

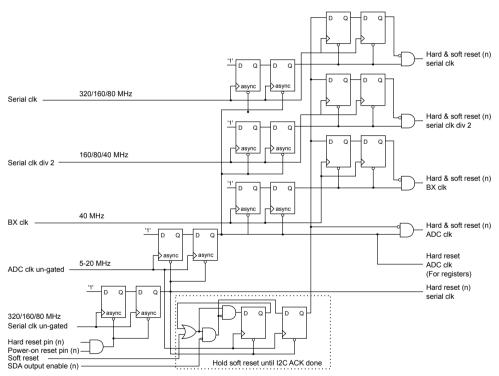

|   |     |        | 3.2.1.1    | Clock management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53        |

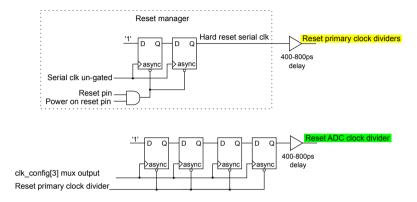

|   |     |        | 3.2.1.2    | Reset management $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57        |

|   |     | 3.2.2  | Slow con   | trol and configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60        |

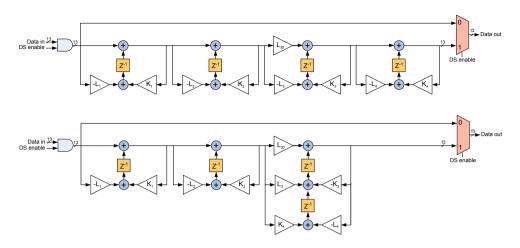

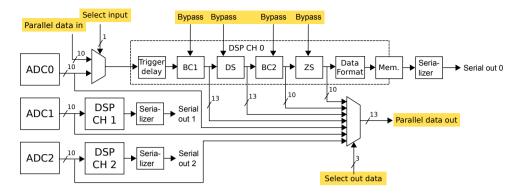

|   |     | 3.2.3  | Digital si | ignal conditioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64        |

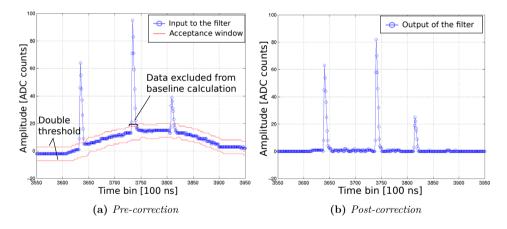

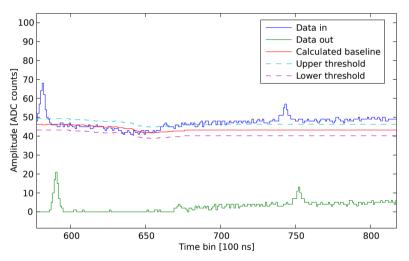

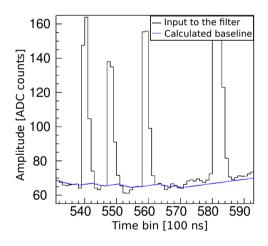

|   |     |        | 3.2.3.1    | First baseline correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64        |

|   |     |        | 3.2.3.2    | Digital shaper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67        |

|   |     |        | 3.2.3.3    | Baseline correction 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69        |

|   |     |        | 3.2.3.4    | Filter changes and improvements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71        |

|   |     |        | 3.2.3.5    | Baseline correction 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72        |

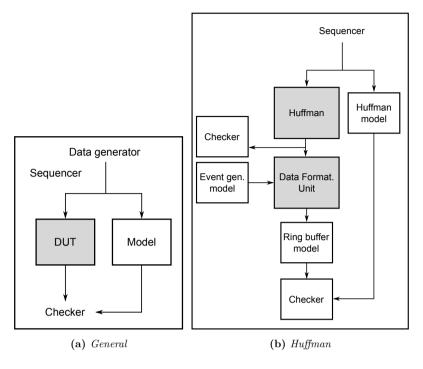

|   |     | 3.2.4  | Data con   | npression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74        |

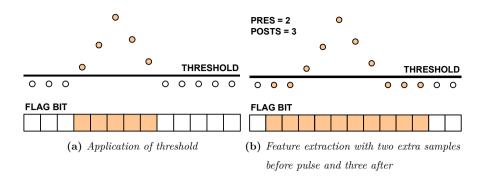

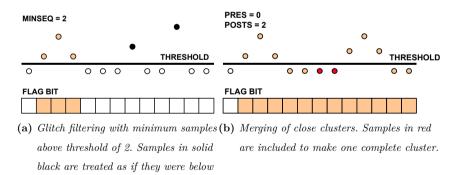

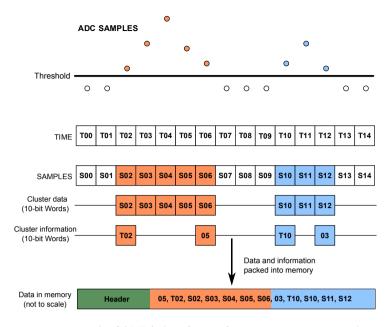

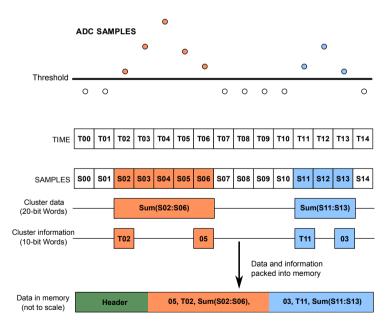

|   |     |        | 3.2.4.1    | Zero suppression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74        |

|   |     |        | 3.2.4.2    | Lossy data compression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76        |

|   |     |        | 3.2.4.3    | Alternative lossy data compression $\hdots \hdots $ | 78        |

|   |     |        | 3.2.4.4    | Huffman compression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79        |

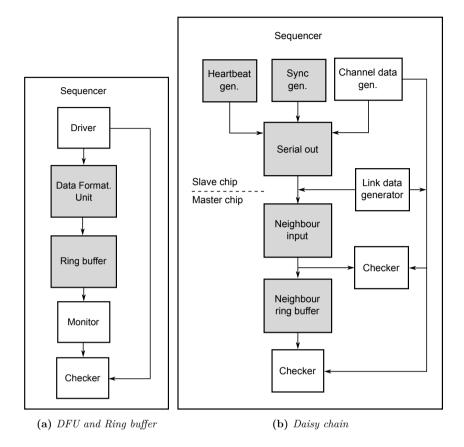

|   |     | 3.2.5  | Event ma   | anagement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 79        |

|   |     |        | 3.2.5.1    | Ring buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81        |

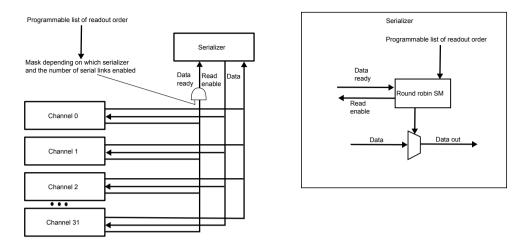

|   |     | 3.2.6  | Readout    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82        |

|   |     |        | 3.2.6.1    | Serialized data readout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82        |

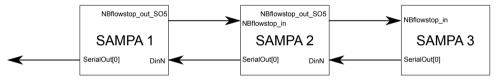

|   |     |        | 3.2.6.2    | Daisy chained readout $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84        |

|   |     |        | 3.2.6.3    | Direct readout - serialization $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86        |

|   |     |        | 3.2.6.4    | Direct readout - combinatorial $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 88        |

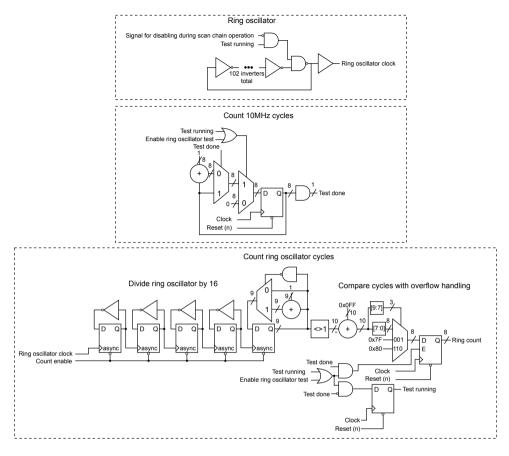

|   | 3.3 | Design | for test . |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88        |

|   |     | 3.3.1  | Scan cha   | in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89        |

|   |     |        | 3.3.1.1    | Scan observability $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91        |

|   |     | 3.3.2  | Memory     | built-in self-test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91        |

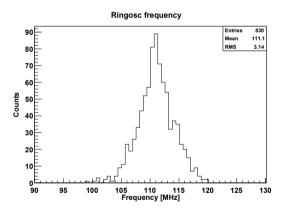

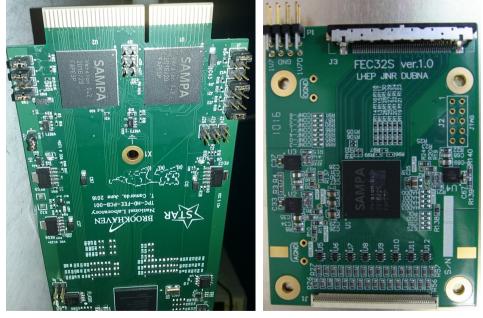

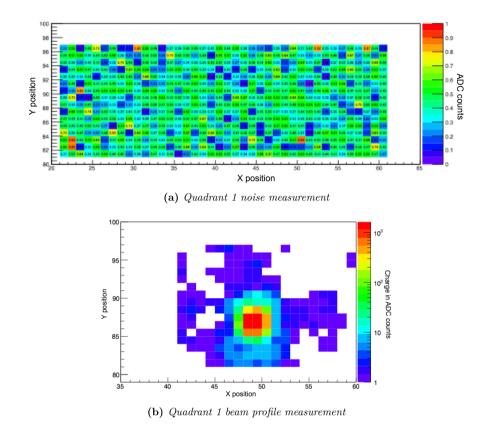

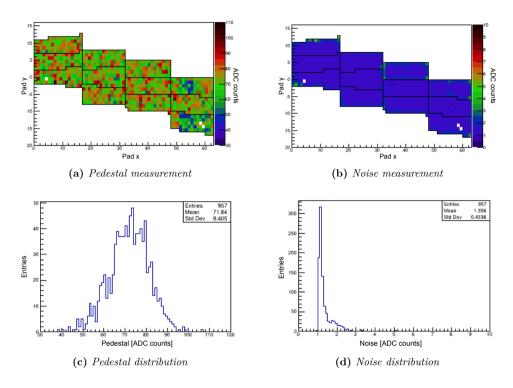

|   |     | 3.3.3  | JTAG be    | oundary scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95        |