# Design, implementation and testing of SRAM based neutron detectors

# **Arild Velure**

**Master Thesis**

Department of Physics and Technology University of Bergen

June 2011

# **Preface**

The work of this thesis has been carried out within the Microelectronics and Nuclear Physics Research Group at the University of Bergen between May 2010 and May 2011.

I would like to thank my supervisors Kjetil Ullaland and Dieter Röhrich for guidance and support throughout the work of this thesis.

Further I would like to thank Eivind Larsen and Kristian Ytre-Hauge for great cooperation throughout this work.

A great thanks needs to go to Ketil Røed and Markus Brugger for letting us come and test together with them at PTB and CERF and for their guidance and support resulting in usable data.

A special thanks goes to Odd Harald Odland for support, and for letting us frequently use the cyclotron at HUS for testing of the equipment throughout this work. This has greatly contributed to the results. Thanks to Jan Salbu for assisting us on testing at the cyclotron at HUS.

Further I would like to thank Amir Hasanbegovic for sharing his beam-time with us for our second measurements at OCL.

Thanks to Ralph Nolte, Stefan Löb and Christian Pignard for assistance in the testing at PTB. Jon C. Wikne, Eivind A. Olsen and Magnus Lode Roscoe for the assistance in the testing at OCL. Chiara La Tessa and Christoph Schuy for assistance in the testing at GSI. Sverre Hval and Espen Graffer for assistance in the testing at IFE.

Thanks to Njål Brekke for helpful discussions and for developing the first prototype of the detector before my work started. Thanks to Dominik Fehlker for extended assistance.

Bergen, May 2011

Arild Velure

ii Preface

# **Abstract**

Neutrons of thermal and high energies can change the value of a bit stored in a Static Random Access Memory (SRAM) memory chip. The effect is non destructive and linearly dependent on the amount of incoming particles, which makes it exploitable for use as a neutron detector. Detection is done by writing a known pattern to the memory and continuously reading it back checking for wrong values. As the SRAM memory is immune to gamma radiation it is ideal for use in for instance medical linear accelerators for detection of neutron dose to a patient.

The intention of this work has been twofold: (1) Testing of different SRAM devices of different bit-sizes, manufacturers, feature sizes and voltages for their sensitivity to neutrons of different energies from thermal to high energies. (2) Design and implement detector hardware, firmware and its accompanying readout system for successful use in irradiation testing.

The work has been done in close collaboration with Eivind Larsen, whose main contributions has been related to the nuclear physics aspect of the work in addition to arrangements in regard to beam setup and experimentation.

Testing have been done at the Physikalisch-Technische Bundesanstalt (PTB) facility in Braunschweig Germany in a quasi-monochromatic neutron beam of 5.8 MeV, 8.5 MeV and 14.8 MeV, finding a dependence of the sensitivity on the energy. In addition there have been testing conducted in the high energy hadron field at CERF at CERN, finding that by using the results from the other experiments an estimated range of the saturation cross section could be determined. Testing was also conducted at two occasions in the 29 MeV proton beam at Oslo Cyclotron Laboratory (OCL) in Oslo Norway, where it was found that the detector could be used as a reference detector for beam monitoring and for beam profile characterization. The cross sections of the detectors were found to be comparable to the 14.8 MeV cross section found at PTB. Thermal neutron testing of the devices was done in the thermal neutron field of the nuclear reactor at Institute for Energy Technology (IFE) at Kjeller Norway. All the devices were found to be sensitive to the field.

Detector electronics, adapted to the different devices, has been built which can withstand the same radiation as the memory device without malfunctioning. There has been a focus on using Commercial Off The Shelf (COTS) components for reducing the total cost of the detector to about 100–200\$US. The use of COTS SRAM memory devices also simplifies the reproducibility and availability of spares.

The detector currently uses a two way communication between the detector and

iv Abstract

the readout computer over two pair of cables reducing the amount of cabling needed for experiments. The detectors can be connected to the communication link in a bus fashion, currently enabling a total of 14 detectors to be tested simultaneously from 100 m away, over the same cable.

Single Event Latch-up (SEL) and problems with irregular count rate of SRAMs created in the 90 nm fabrication node has created problems during testing. Some solutions and techniques to mitigate these in hardware and firmware are presented in this work.

# **Contents**

| Pr | reface |                                                              | i   |

|----|--------|--------------------------------------------------------------|-----|

| Al | bstrac | t                                                            | iii |

| A  | crony  | ms                                                           | ix  |

| 1  | Intr   | oduction                                                     | 1   |

|    | 1.1    | Existing applications                                        | 1   |

|    |        | 1.1.1 RadMon Radiation Monitoring System for the LHC and the |     |

|    |        | experimental caverns at CERN                                 | 2   |

|    |        | 1.1.2 NEUTOR - Neutrons Monitor for Radiotherapy             | 2   |

|    | 1.2    | Primary objective and main contributions                     | 2   |

|    | 1.3    | Outline                                                      | 4   |

| 2  | Rad    | iation effects in semiconductor devices                      | 5   |

|    | 2.1    | Radiation interaction with matter                            | 5   |

|    |        | 2.1.1 Interaction of charged particles with matter           | 5   |

|    |        | 2.1.2 Interaction of neutral particles with matter           | 7   |

|    | 2.2    | The influence of radiation on semiconductor devices          | 9   |

|    |        | 2.2.1 Cumulative effects                                     | 9   |

|    |        | 2.2.2 Single Event Effects                                   | 9   |

| 3  | Mer    | nory based semiconductor devices                             | 15  |

|    | 3.1    | Static RAM                                                   | 15  |

|    |        | 3.1.1 SEU susceptibility                                     | 16  |

|    |        | 3.1.2 Critical charge                                        | 17  |

|    |        | 3.1.3 SEFI susceptibility                                    | 17  |

|    | 3.2    | Dynamic RAM and Synchronous Dynamic RAM                      | 17  |

|    |        | 3.2.1 SEU susceptibility                                     | 18  |

|    |        | 3.2.2 Critical charge                                        | 19  |

|    |        | 3.2.3 SEFI susceptibility                                    | 19  |

|    | 3.3    | Ferroelectric RAM                                            | 20  |

|    |        | 3.3.1 SEE susceptibility                                     | 20  |

|    | 3 /    | Magnetoresistive RAM                                         | 20  |

vi CONTENTS

|   |      | 3.4.1 SEE susceptibility                | 21 |

|---|------|-----------------------------------------|----|

|   | 3.5  |                                         | 21 |

|   |      | 3.5.1 SEE susceptibility                | 22 |

|   | 3.6  |                                         | 22 |

|   |      |                                         | 23 |

|   | 3.7  |                                         | 23 |

|   |      |                                         | 23 |

|   | 3.8  |                                         | 24 |

| 4 | Neu  | tron detector implementation            | 27 |

|   | 4.1  |                                         | 27 |

|   | 4.2  | Hardware                                | 28 |

|   |      | 4.2.1 SRAM packages                     | 29 |

|   |      | 4.2.2 Voltage control                   | 30 |

|   |      |                                         | 30 |

|   | 4.3  | Firmware                                | 32 |

|   |      | 4.3.1 SEU hardening                     | 33 |

|   |      | 4.3.2 Hierarchy, regularity, modularity | 34 |

|   |      | 4.3.3 SEU detection in SRAM             | 35 |

|   |      | 4.3.4 SEU transmission                  | 37 |

|   |      | 4.3.5 Scintillator counter              | 37 |

|   | 4.4  | Software                                | 38 |

|   | 4.5  | Master interface                        | 38 |

|   |      | 4.5.1 Firmware                          | 39 |

|   | 4.6  | Improvements and future outlook         | 40 |

|   |      | 4.6.1 MCU detection                     | 40 |

|   |      | 4.6.2 Stuck bits mitigation             | 41 |

|   |      |                                         | 42 |

| 5 | Faci | lity description and setup              | 45 |

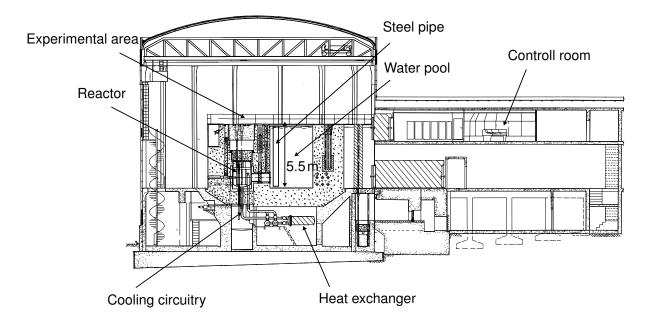

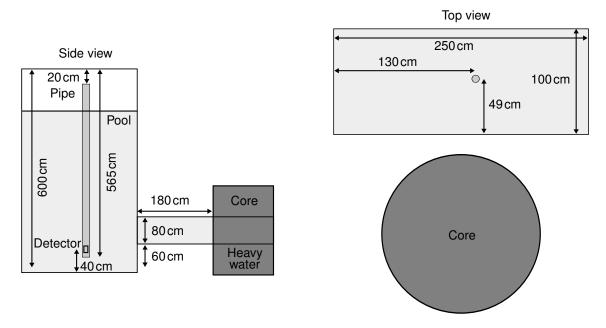

|   | 5.1  | $\mathcal{E}$                           | 45 |

|   | 5.2  | Physikalisch-Technische Bundesanstalt   | 46 |

|   |      | 5.2.1 Purpose of tests                  | 46 |

|   |      | 1                                       | 46 |

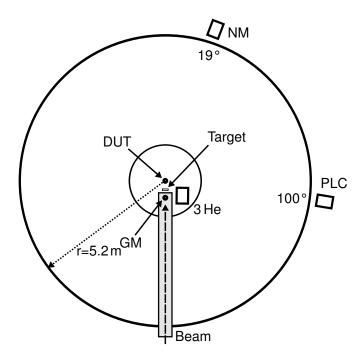

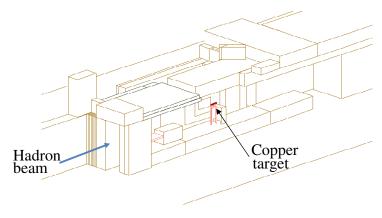

|   | 5.3  | CERN-EU High Energy Reference Field     | 49 |

|   |      | 5.3.1 Purpose of tests                  | 50 |

|   |      | 5.3.2 Experimental setup                | 51 |

|   | 5.4  | Oslo Cyclotron Laboratory               | 54 |

|   |      | 5.4.1 Purpose of tests                  | 54 |

|   |      |                                         | 55 |

|   | 5.5  |                                         | 59 |

|   |      |                                         | 59 |

|   |      | _                                       | 60 |

CONTENTS vii

| 6 | Ana  | lysis and results                        | 63  |

|---|------|------------------------------------------|-----|

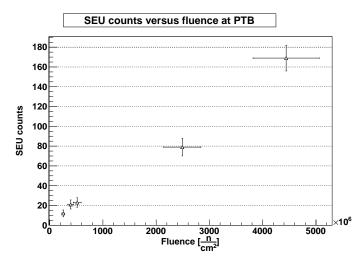

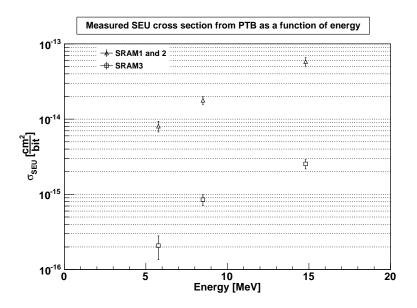

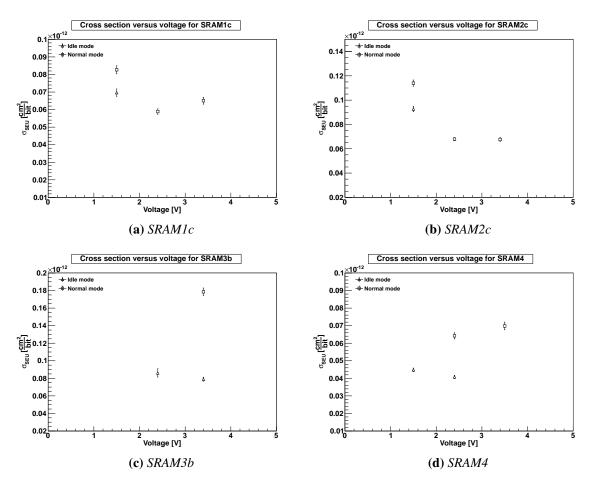

|   | 6.1  | Accelerated neutron-beam testing at PTB  | 63  |

|   |      | 6.1.1 Analysis of data                   | 64  |

|   |      | 6.1.2 Results                            | 64  |

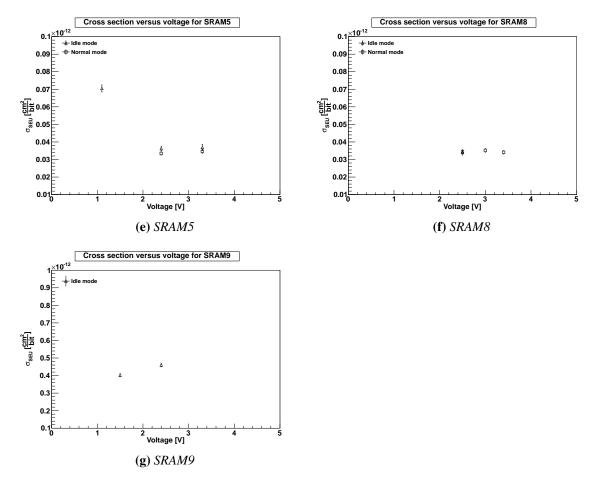

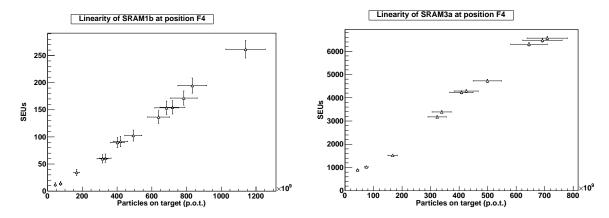

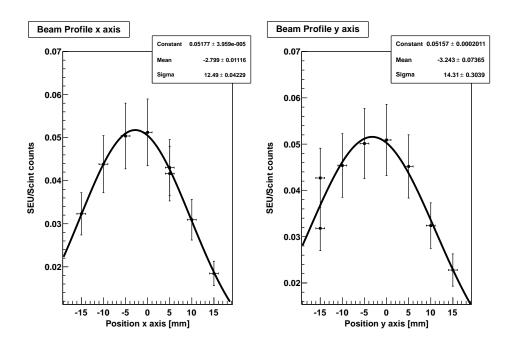

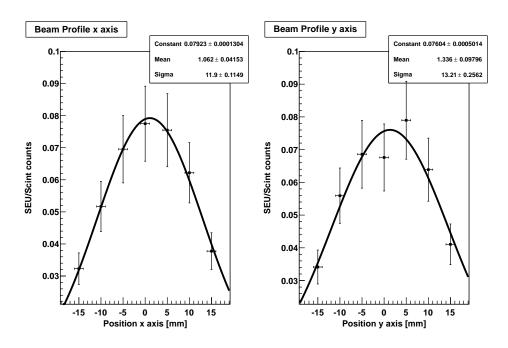

|   | 6.2  | Accelerated proton-beam testing at OCL   | 66  |

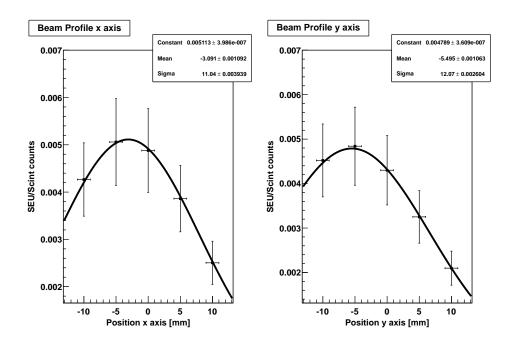

|   |      | 6.2.1 Analysis of data                   | 67  |

|   |      | 6.2.2 Results                            | 68  |

|   | 6.3  | High energy hadron-field testing at CERF | 70  |

|   |      | 6.3.1 Analysis of data                   | 70  |

|   |      | 6.3.2 Results                            | 72  |

|   |      | 6.3.3 SRAM1a and b                       | 72  |

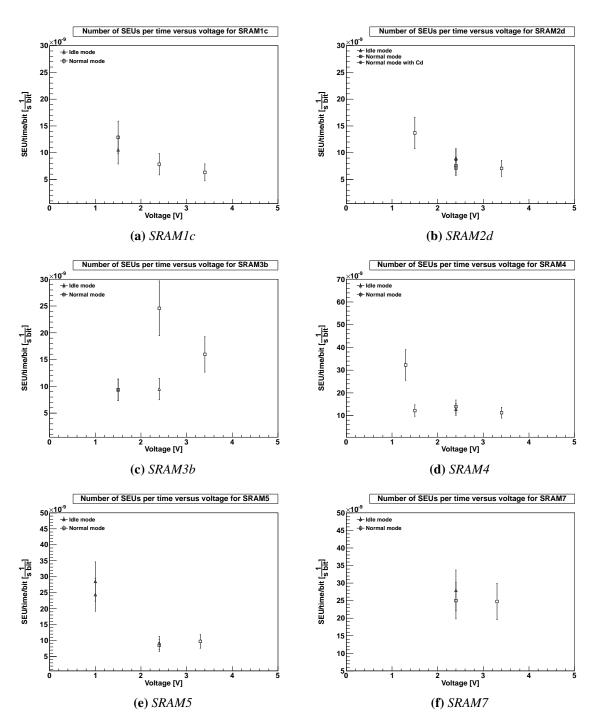

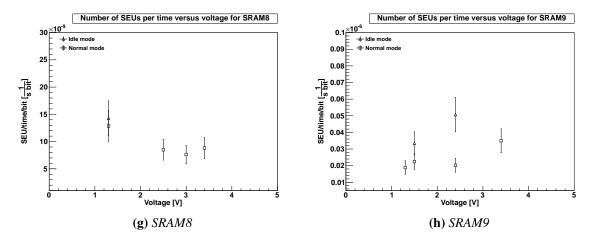

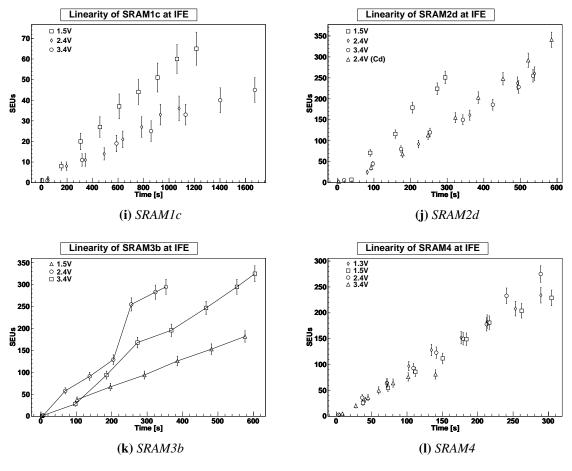

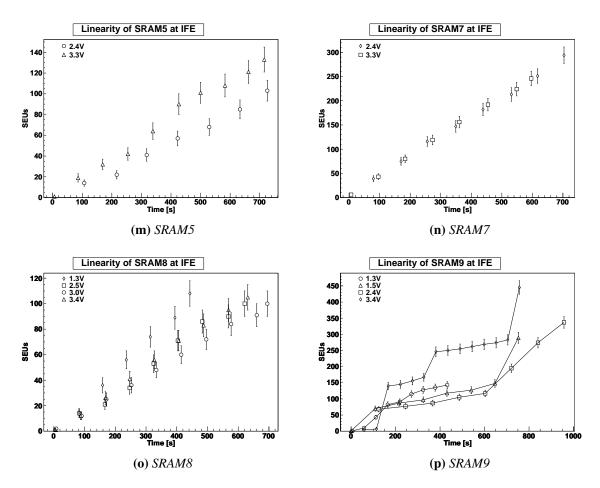

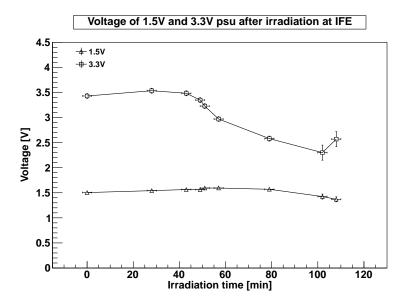

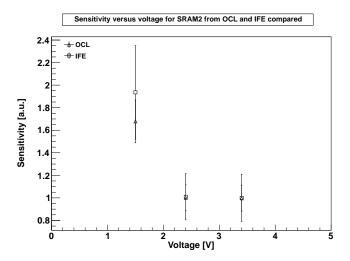

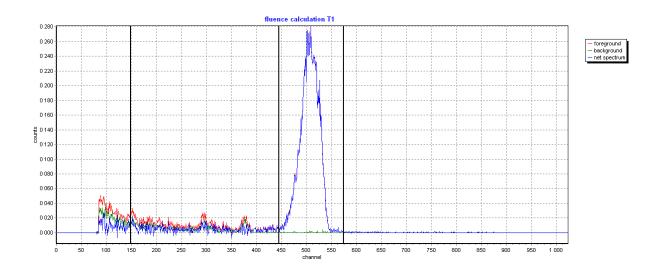

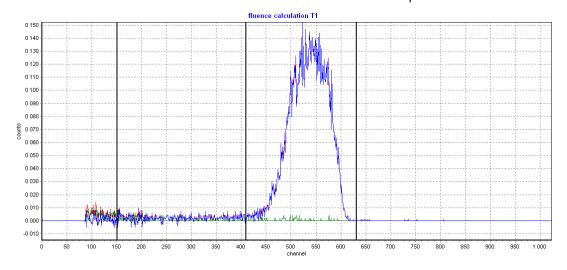

|   | 6.4  | Thermal neutron testing at IFE           | 74  |

|   |      | 6.4.1 Analysis of data                   | 76  |

|   |      | 6.4.2 Results                            | 77  |

|   |      | 6.4.3 Linearity                          | 80  |

|   |      | 6.4.4 TID problems                       | 80  |

|   | 6.5  | Summary                                  | 81  |

|   |      | •                                        |     |

| 7 | Con  | clusion and outlook                      | 83  |

|   | 7.1  | Conclusion                               | 83  |

|   | 7.2  | Outlook                                  | 85  |

| A | PTB  | Calibration Data                         | 87  |

|   | A.1  | PTB calibration report for 1st run       | 87  |

|   | A.2  | PTB calibration report for 2nd run       | 89  |

|   | A.3  | PTB calibration report for 3rd run       | 90  |

|   | A.4  | PTB calibration report for 4th run       | 91  |

|   | A.5  | PTB calibration report for 5th run       | 92  |

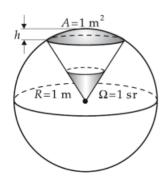

| В | Defi | nition of steradian                      | 93  |

|   |      |                                          |     |

| C | Sran | n Calibration                            | 95  |

| D | Com  | plete data tables for irradiation tests  | 101 |

|   | D.1  | Accelerated neutron-beam testing at PTB  | 101 |

|   | D.2  | HEH testing at CERF                      |     |

|   | D.3  | Accelerated proton-beam testing at OCL   |     |

|   |      | D.3.1 Cross section tables               |     |

|   |      | D.3.2 18. November 2010                  |     |

|   |      | D.3.3 8. December 2010                   |     |

|   |      | D.3.4 9. December 2010                   |     |

|   | D.4  | Thermal neutron testing at IFE           |     |

| E | VHI  | OL code                                  | 111 |

| •••  | COMPENIE |

|------|----------|

| VIII | CONTENTS |

|      |          |

Bibliography 124

# **Acronyms**

**ADC** Analog to Digital Converter

**API** Application Programming Interface

**a.u.** Arbitrary Units

**C-RAM** Chalcogenide RAM

**CCD** Charge-Coupled Device

**CERF** CERN-EU High Energy Reference Field

**CERN** Conseil Européen pour la Recherche Nucléaire

**CMOS** Complementary Metal Oxide Semiconductor

**COTS** Commercial Off The Shelf

**DAQ** Data Acquisition

**DRAM** Dynamic Random Access Memory

**DUT** Device Under Test

**EEPROM** Electrically Erasable Programmable Read-Only Memory

**EPROM** Electrically Programmable Read-Only Memory

**FBGA** Fine-Pitch Ball Grid Array

**FC** Faraday Cup

**FIFO** First-In, First-Out

**FPGA** Field Programmable Gate Array

**FRAM** Ferroelectric RAM

**GSI** Gesellschaft für Schwerionenforschnung

**HEH** High Energy Hadrons

x Acronyms

**IFE** Institute for Energy Technology

**IGBT** Insulated Gate Bipolar Transistor

**LED** Light-emitting diode

**LET** Linear Energy Transfer

**LHC** Large Hadron Collider

MBU Multi-Bit Upset

MCU Multi-Cell Upset

MOS Metal Oxide Semiconductor

**MRAM** Magnetoresistive RAM

New Monitor

**OCL** Oslo Cyclotron Laboratory

**OSI** Open Systems Interconnection model

**PCB** Printed Circuit Board

**PCRAM** Phase-Change RAM

**PIC** Precision Ionization Chamber

**PLC** Precision Long Counter

**p.o.t.** Particles On Target

**PTB** Physikalisch-Technische Bundesanstalt

**RadMon** Radiation Monitor

**RAM** Random Access Memory

**SDRAM** Synchronous DRAM

**SEB** Single Event Burnout

**SECDED** Single Error Correction, Double Error Detection

**SEE** Single Event Effects

**SEFI** Single Event Functional Interrupt

**SEGR** Single Event Gate Rupture

**SEL** Single Event Latch-up

**SET** Single Event Transient

**SEU** Single Event Upset

**SPS** Super Proton Synchrotron

**SRAM** Static Random Access Memory

**SSRAM** Synchronous SRAM

**TFBC** Thin Film Breakdown Counter

**TID** Total Ionized Dose

**TMR** Triple Modular Redundancy

**TQFP** Thin Quad Flat Pack

**TSOP1** Thin Small-Outline Package 1

**TSOP2** Thin Small-Outline Package 2

**TSOP** Thin Small-Outline Package

**USB** Universal Serial Bus

**VFBGA** Very Fine-Pitch Ball Grid Array

VHDL VHSIC Hardware Description Language

xii Acronyms

# **Chapter 1**

# Introduction

Ionizing radiation has an impact on everything around us. This also applies to electronics, where a single particle can cause the malfunction of a complete system by corrupting data or by altering functions. The problem is growing for every new generation of chips as the size of the integrated transistor is rapidly shrinking, reducing the charge needed from the incoming particle to affect the transistor's operation.

Electronic memory is vulnerable to Single Event Upsets (SEUs) which are caused by an ionizing particle depositing enough charge in the silicon to flip a bit in the memory from zero to one or from one to zero. The bit flips are non destructive and the data can be restored by rewriting the bit. The probability of an upset is random in time and it is linearly correlated with the amount of incoming particles. Knowing this, it is possible to make a radiation detector by writing a known pattern to the memory and continuously reading it back, checking for alterations from the original pattern.

Neutrons are not ionizing themselves, but have the ability to create secondary particles through nuclear interactions which are ionizing and which in turn can create SEUs in memory.

One of the many benefits of using electronic memory as a neutron detector is that they do not produce SEUs in response to gamma or beta radiation, which is often present in radiation environments where neutrons are present. Another benefit is that COTS memory can be bought cheaply, pushing the cost of a complete detector down to a 100–200\$US.

## 1.1 Existing applications

Some neutron detectors based on COTS SRAM are already in use today for various applications. This section gives an example of two of the possible uses or these detectors.

2 Introduction

# 1.1.1 RadMon Radiation Monitoring System for the LHC and the experimental caverns at CERN

In the Large Hadron Collider (LHC), a large amount of electronics is needed to control everything from bending magnets to cooling systems. In a harsh radiation environment like this, electronics will start to fail much more rapidly than it would under normal circumstances. Failing electronics can cause damage to other electronics when it breaks down which can lead to long unwanted beam stops needed to fix the damaged electronics. To combat this, nearly 300 RadMon radiation monitoring devices have been mounted on strategic places to give an early warning of when radiation levels have reached a critical level and the equipment needs to be exchanged. The RadMons are connected together in a network providing on-line measuring of the amount of radiation at any given time.

The RadMon is equipped with two Radfets for measurement of the Total Ionized Dose (TID), three PIN photodiodes for measurement of the 1 MeV neutron fluence and four 4Mb SRAM devices for detection of SEUs caused by high energy hadrons above 20 MeV [1].

#### 1.1.2 NEUTOR - Neutrons Monitor for Radiotherapy

During radiation treatment by the use of a medical linear accelerators (linacs), commonly used for treatment of cancer, the dose received from the secondary particles produced by the shaping of the beam can increase the risk of secondary tumors in the patient. The NEUTOR is a device that can actively monitor the neutron dose around the linac and is thus able to determine the neutron dose received by the patient. Due to the pulsed nature of the beam and the large amount of scattered photons, other forms of active neutron detectors are not suitable for use in this environment.

The NEUTOR is equipped with eight boards, each having 16 SRAM devices of 512kb for a total of 64Mb [2]. The SRAMs were particularly chosen for their higher content of <sup>10</sup>B, which have a large capture cross section for thermal neutrons.

### 1.2 Primary objective and main contributions

The main purpose of this thesis has been to investigate the applicability of various SRAM devices for use as an active neutron detector. For this to be done, the devices need to be tested in neutron beams at different energies where the flux of the beam is known for which the device can then be calibrated against. The sensitivity of the device for neutrons of a certain energy can then be found. This sensitivity is referred to as the single event upset cross section,  $\sigma_{SEU}$ . When the sensitivity of a device to a range of energies have been found, an energy dependent spectrum can be created. By knowing the radiation environment where the device should be used, the flux at the position of use can be determined.

To be able to test a wide range of SRAM devices during accelerated irradiation testing with high stability and predictability, an in situ electronic readout that can be adapted to all the different devices without much reconfiguration is needed. An in situ detector removes the uncertainty, due to packet loss or bad connections, which comes by the use of a communication link for direct readout of the memory. It also adds the possibility of using more than one memory device on the same detector, and testing more than one detector at the same time.

A focus in this thesis has been to use Commercial Off The Shelf (COTS) components, both for cost reasons and to make the detector easily reproducible. This enables the detector to be produced at the cost of one tenth of the price of other commercial neutron detectors.

For the detector to be characterized as an active detector, some form of readout communication and software is still needed. The readout software enables the user to monitor the amount of Single Event Upsets (SEUs) in real time and also any errors reported in addition to other information available from the detector.

All these aspects have been treated in this thesis, and the main contributions are listed below.

- Investigation into SRAM and other memory devices' applicability as a neutron detector is presented in chapter 3.

- Development of firmware and hardware for testing of nine different SRAM detectors is presented in chapter 4.

- Development of firmware and hardware for testing of two Synchronous DRAMs (SDRAMs) was completed in the early stages of development. Only minor testing was done on them with the cyclotron at Haukeland University Hospital where they were compared to three other SRAMs. Only one upset was detected on one of them compared to more than 1000 on each of the SRAMs and they were thus deemed not suitable. This development will not be further discussed in this thesis as the radiation environment at the cyclotron is not sufficiently known and a proper cross section could not be determined for the SDRAMs.

- Development of hardware, firmware and software for communicating with the detectors is presented in chapter 4.

- Accelerated beam testing at PTB in Braunschweig Germany in 5.8 MeV, 8.5 MeV and 14.8 MeV neutron beams. This is presented in section 6.1 and this part of the work was done in collaboration with Eivind Larsen [3].

- Testing in a high energy hadron field at the CERN-EU High Energy Reference Field (CERF) at CERN. The results are presented in section 6.3 and were done in collaboration with Eivind Larsen.

- Two accelerated beam tests at the OCL in a 29 MeV proton beam. The results are presented in section 6.2 and were done in collaboration with Eivind Larsen.

4 Introduction

• Calibration and beam profiling for two ASIC tests at OCL in addition to repurposing of the detector hardware and development of new firmware for SEU in one of the ASICs. This will be further discussed by Magnus Lode Roscoe [4].

- Testing of the detectors in a thermal neutron field at the IFE at Kjeller. The results are presented in section 6.4 and were done in collaboration with Eivind Larsen.

- Testing the detectors ability to detect the neutron field in a linear accelerator (linac) at the Haukeland University Hospital. The linac produces secondary thermal and high energy neutrons when used with photon energies above 7 MeV to 8 MeV. This happens through interaction of the photons from the linac with the tungsten/lead collimators. The detectors were found to be sensitive to the field and the results will be further discussed by Eivind Larsen [3].

- Testing of the detectors applicability as a detector for the neutron dose in carbon ion treatment of cancer. This was done at GSI in Germany in a 400 MeV carbon beam on a human tissue equivalent phantom. The work was done in collaboration with Eivind Larsen and Kristian Ytre-Hauge. The results will be further discussed by Larsen [3].

#### 1.3 Outline

This thesis is divided into seven chapters including the current one. In order to understand the behavior of electronics exposed to radiation, some knowledge is needed on how these effects occur. Chapter 2 gives a brief overview of the interaction of radiation with matter and continues with an introduction to the single event effects relevant to memory devices. As there currently are many memory devices available today that may be potentially used as radiation detectors, a look at what separates them from each other and how effective they could be as a radiation detector is needed. Chapter 3 reviews the functionality and behavior of mostly all the different types of memory devices commercially available today. An examination of their susceptibility to the different single event effects is included and is followed by a discussion on their applicability as a neutron detector. The second part of this thesis addresses the development of a neutron detector and the testing needed for calibration. Chapter 4 presents the design and implementation of a neutron detector. In chapter 5 the irradiation test setup is introduced for all the different test cites and setups, an added focus is given to the monitoring and calibration of the beam at each test cite. Chapter 6 presents the results for the irradiation tests and lastly the thesis is summarized and concluded in chapter 7.

# **Chapter 2**

# Radiation effects in semiconductor devices

Radiation effects are present in all types of electronic devices. As the industry moves to smaller feature sizes, lower voltages and higher densities, these problems will probably escalate. This chapter presents some of the more common radiation effects in electronics and how they effect memory based electronics. The information is mostly based on Knoll [5] and Nicolaidis [6] if not otherwise noted.

#### 2.1 Radiation interaction with matter

To be able to detect or measure any type of radiation, we need to make it interact with matter in some way and then analyze the resulting change in the matter's properties. As all particles carry some energy with them, either in the form of charge or momentum, they are capable of interacting with matter in the form of particle interactions.

We distinguish between two main groups of particle interactions, charged particle interactions and neutral particle interactions. Alpha particles, beta particles, heavy ions and protons are charged particles while neutrons and photons (gamma rays, X-rays) are neutral.

We also differentiate between ionizing and non-ionizing radiation. Ionization is the process of removing an electron from an atom resulting in charged particles, a negatively charged electron and a positively charged ion. For this effect to occur the particle hitting the atom needs to have an energy above the electrons binding energy, typically a few eV. Non-ionizing particles are thus particles that don't have enough energy to displace these electrons.

#### 2.1.1 Interaction of charged particles with matter

Charged particles can be divided between heavy and light charged particles. Ions, protons and alpha particles are considered heavy charged particles, while beta particles are considered light.

Charged particles moving through a material mainly interacts with the negative electrons through the Coulomb forces. As a result they continuously lose energy through

each interaction and will finally stop after tens of thousands of collisions.

Beta particles which are three orders of magnitude lighter than a proton, may lose all their energy in a single collision with an atomic electron as it involves a collision between two particles of the same mass. They may also scatter to large angles and end up with a zig-zag trajectory. In contrast to heavy charged particles which lose a small amount of energy in each collision and end up with a more or less straight trajectory.

Charged particles can interact with the nuclei of the target material leading to the particle being deflected through elastic scattering or fragmented through inelastic scattering. Depending on the target material and projectile energy, the secondary fragment created can be a proton, neutron or a heavier particle.

The rate at which a charged particle moving through matter lose energy is generally referred to as the *stopping power* of the material. It is defined as the amount of energy lost per unit length of the material being transversed and is given in MeV/cm. Charged particles can have either nuclear or Coulomb interactions and the total stopping power is then the sum of these.

$$S_{total} = -\frac{\mathrm{d}E}{\mathrm{d}x} \tag{2.1a}$$

$$-\frac{\mathrm{d}E}{\mathrm{d}x} = S_{col} + S_{nuc} \tag{2.1b}$$

The amount of energy absorbed by the matter through Coulomb interactions is referred to as the Linear Energy Transfer (LET) and is equivalent to the stopping power of Coulomb interactions but with an opposite sign. The LET is usually denoted in respect to the density  $(\rho)$  of the material being traversed and is so given in MeV/mg/cm<sup>2</sup>.

The stopping power is described by the *Bethe formula*, see for instance [5].

$$-\frac{dE}{dx} = \frac{4\pi e^4 z^2}{m_0 v^2} NB \tag{2.2}$$

where

$$B = Z \left[ \ln \frac{2m_0 v^2}{I} - \ln \left( 1 - \frac{v^2}{c^2} \right) - \frac{v^2}{c^2} \right]$$

(2.3)

| Symbol   | Definition                                        |

|----------|---------------------------------------------------|

| e        | Electron charge                                   |

| z        | Charge of primary particle                        |

| $m_0$    | Electron rest mass                                |

| v        | Velocity of primary particle                      |

| N        | Number density of target material                 |

| Z        | Atomic number of target material                  |

| I        | Mean excitation potential for the target material |

| <u> </u> | Speed of light                                    |

As long as the primary particle is non-relativistic ( $v \ll c$ ) only the first term in B is significant. It can then be seen that the stopping power for a given non-relativistic particle varies with  $1/v^2$ , or inversely with the particle energy. For different particles of the same velocity the stopping power is mainly depended on  $z^2$ , which means heavier particles, like an alpha, will lose energy at a greater rate than for instance a proton.

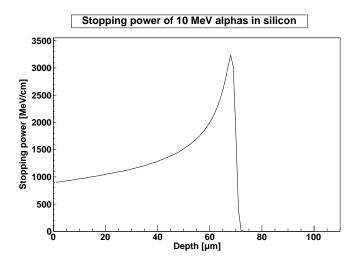

As a charged particle nears the end of its track it starts interacting more with the surrounding matter and will start to lose energy faster, resulting in a maximum energy loss at the end of the track. This is illustrated by the *Bragg curve* in figure 2.1 showing the specific energy loss of a charged particle traversing a matter. The peak of the energy loss is referred to as the *Bragg peak*. After the Bragg peak the energy loss of the particle falls off sharply due to electron pickup.

**Figure 2.1:** As an example of the Bragg curve, the stopping power of 10MeV alphas in <sup>28</sup>Si is shown here as simulated by the SRIM code [7].

#### 2.1.2 Interaction of neutral particles with matter

Two types of neutral particles are neutrons and photons. As none of them have any charge they do not interact with the Coulomb force.

#### Interaction of photons with matter

Photons, which can be gamma rays, X-rays, UV etc., are an example of electromagnetic radiation. They travel at the speed of light and have zero rest mass and charge. They interact with matter mainly in three ways: photo electric absorption, Compton scattering and pair production. In photo electric absorption the photon interacts and gets absorbed by an atom which emits an energetic photo-electron from one of its bound shells. In Compton scattering the photon interacts with a weakly bound electron in the absorbing material. In the process the photon direction is deflected and some of its energy is

transfered to the electron. In pair production the energy of the photon is absorbed and used to create an electron-positron pair.

#### Interaction of neutrons with matter

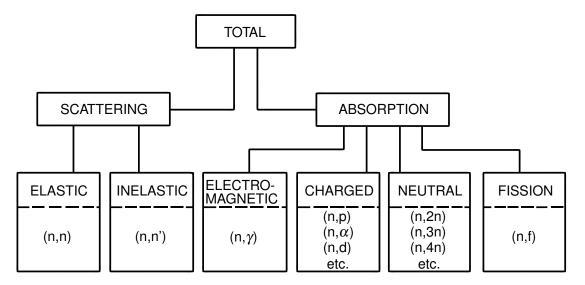

Neutrons interact with nuclei only through the strong nuclear force. For this to happen the neutron has to pass very close to the nucleus and since the distance between the nuclei in normal dense matter is large, the neutron has a deep penetration depth in matter. The ways the neutron interacts with the nuclei can be divided into scattering and absorption as seen in figure 2.2. In scattering reactions the neutron interacts with the nucleus, but both particles reappear after the reaction though with a different direction and energy. In absorption the neutron disappears, but one or more heavy charged particles will appear after the reaction. The total probability that a reaction will occur is depends on the cross section,  $\sigma_t$ . The cross section is strongly depended upon the energy of the neutron and the atomic number of the target nucleus.

Neutrons can be classified according to their energy and for our practical purpose can be divided into thermal neutrons and fast neutrons. Thermal neutrons have an energy below  $0.5\,\text{eV}$  which also is the energy of which an abrupt drop can be seen in the cross section of cadmium (the cadmium cutoff energy). This property can be utilized to differentiate between thermal and fast neutrons in neutron detection. Due to the small kinetic energy of thermal neutrons, they lose and gain only minor amounts of energy through elastic scattering with the nucleus, but will eventually get absorbed. Fast neutrons have higher energy and can deposit more energy in each interaction with the nucleus.

**Figure 2.2:** Overview of different neutron interactions. The letters separated by commas in the parentheses show the incoming and outgoing particle [8].

#### 2.2 The influence of radiation on semiconductor devices

Radiation effects experienced in semiconductor devices can range from displacement of atoms in the structure to corruption of stored data due to charge injection. The different effects are usually classified into two groups, cumulative effects and single-event effects.

#### 2.2.1 Cumulative effects

Cumulative effects are potentially destructive effects that are caused by accumulated dose over time.

#### **Displacement Damage**

Displacement damage is the result of nuclear reactions, typically scattering, that can cause changes in the semiconductor lattice altering the crystal's electrical characteristics. Any incident particle or photon capable of imparting an energy of about 25 eV to a silicon atom can dislodge it from the lattice site [9]. The displacement damage is usually measured in neutrons/cm<sup>2</sup>, the same as for the neutron fluence.

#### **Total Ionizing Dose**

Total Ionizing Dose is the dose accumulated by the device due to ionizing radiation over time and is measured in *Grays* (Gy). As the ionizing particle is creating electronhole pairs, there is a probability that the electrons and holes will not recombine in the presence of a field due to the slow movement of the holes. This can cause the holes to be trapped in the oxide or the oxide-silicon interface creating a net positive charge.

#### 2.2.2 Single Event Effects

Single Event Effects (SEE) group all effects caused by interaction of a single particle with an electronic component. These effects are usually again grouped into *soft* and *hard* errors. Soft errors are effects that causes some form of corruption of a stored element or glitches in the device's operation. They are non destructive and can be corrected be rewriting the affected element with a correct value, resetting or power cycling the device. These errors concern SEU, Multi-Bit Upset (MBU), Multi-Cell Upset (MCU), Single Event Transient (SET), Single Event Functional Interrupt (SEFI) and SEL.

Hard errors are destructive errors that are non-recoverable. These can be Single Event Burnout (SEB) or Single Event Gate Rupture (SEGR) in power MOS devices, IGBT or power bipolar transistors. These effects are only seen in high voltage/current devices and are not applicable to memory devices.

Single event effects are measured by a cross section. This is analogous to the nuclear cross section and is measured in cm<sup>2</sup>. It is given by

$$\sigma = \frac{\text{No. of SEE}}{\phi \cdot s} = \frac{\text{No. of SEE}}{\Phi}$$

(2.4)

Where  $\sigma$  is the Single Event Upset (SEU) cross section,  $\varphi$  is the flux in number of particles per square cm per second and  $\Phi$  is the fluence which is the integrated flux.

Single Event Effects (SEE) manifest themselves in different ways in different devices and will therefore be further discussed in chapter 3 for each respective device. This part will give an introduction to the subject.

#### **Single Event Upsets**

A Single Event Upset (SEU) occurs when an ionizing particle hits the sensitive area of a storage cell, changing its electrical state and causing the wrong value being presented when the cell is read back. A rewriting of the value will return the storage cell to the correct state. A SEU can occur in any device containing latches or other storage cells.

An increase in SEUs can be seen over time for a device in a radiation environment due to increased TID creating leakage currents lowering the required charge to upset the node [10].

SEUs can experimentally be studied by writing a known pattern to the storage cells and continuously reading the pattern back during irradiation to look for changes.

#### Multi Bit Upsets/Multi Cell Upsets

When an ionizing particle causes more than one bit flip to occur, it is referred to as a Multi-Cell Upset (MCU). If the bit flips occur in a single word it is referred to as a Multi-Bit Upset (MBU). Multiple errors can occur if a particle crosses between two sensitive zones of different cells or if the free carriers from the ionizing strike can be collected by different junctions of transistors. The amount of multiple upsets increases with more lateral angles of the impinging ionizing particle and is the lowest at a 90° angle from the plane [11].

In resent devices the words are interleaved, ensuring that cells belonging to the same word are physically apart and in so reducing the possibility of a MBUs occurring [12].

If the cell layout of a device is not known it can be hard to determine if two upsets detected are an MCU or two separate SEUs. But if the flux is relatively low and the readout speed is high the probability of two ionizing particles hitting within the specified time-window is low.

$$P(MCU/MBU) = (T_{readout} \cdot \varphi \cdot \sigma \cdot \text{No. of bits})^{2}$$

(2.5)

Where  $T_{readout}$  is the time to read through a whole device,  $\varphi$  is the particle flux and  $\sigma$  is the cross section per bit.

#### **Single Event Transients**

Single Event Transients (SETs) are momentary voltage or current pulses created from an ionizing particle disturbing combinational logic. An SET may propagate from the output of a gate throughout the circuit and can in the end cause an SEU. For this to happen some criteria must be met [6].

- The particle strike must generate a transient capable of propagating through a circuit.

- There must be an open logic path through which the SET can propagate to reach the latch or memory element.

- The SET must have a sufficient amplitude and duration to change the state of the latch or memory element.

- Depending on the operation of the device, the SET must arrive at the latch during the latching edge of the clock for a synchronous device, or during a read or write command for an asynchronous device.

The probability of an upset increases linearly with the clock or access frequency of the device as the time between the time-windows for latching of data decreases.

Determining if a device is suffering from SET effects in a device containing memory elements can be hard as it will be difficult to separate them from regular SEUs, but if the device is seen to have an increased SEU rate at higher frequencies this could indicate the presence of a SET effect.

#### **Single Event Latchups**

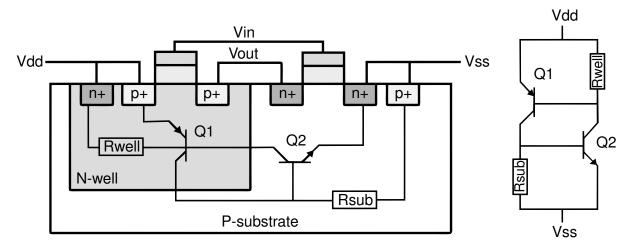

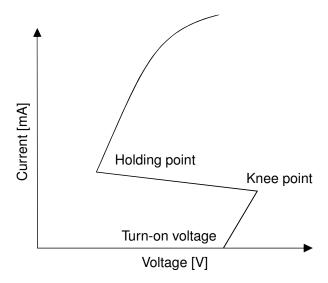

SELs are originating from the interaction of an ionizing particle with a parasitic PNP and NPN transistor structure in bulk CMOS. As seen in figure 2.3, they are combined into a PNPN thyristor structure where if a large enough current is induced in to the circuit to turn on the thyristor, it will remain on until the power is cycled. The point where the thyristor starts to turn on is referred to as the knee point, the voltage to keep the thyristor turned on is called the holding voltage as illustrated in figure 2.4. The ion can strike at any position in the structure, including regions far away from I/O terminals which are normally immune to electrical induced latchups [13]. The effectiveness of the heavy ion to create a SEL depends on the position of the strike in the n-well.

Triggering of the SEL can be separated into four steps [13]:

1. A transient current is induced by a heavy ion within the well-substrate junction. This current flows from the well contact to the substrate contact and produces a voltage drop within the well. The voltage drop depends on the distance from the strike to the well contact and a strike closer to the well contact will produce a smaller voltage drop and will not induce a SEL.

- 2. If the voltage drop is sufficiently large the vertical transistor (Q1) will be forward biased, producing a much larger current which will flow from the emitter of the vertical transistor to the substrate.

- 3. A voltage drop in the substrate from the higher current in step 2 will forward bias the lateral transistor (Q2) causing it to turn on as well starting the regenerative process.

- 4. The regenerative condition causes both transistors to saturate and allows the structure to remain latched after the triggering occurred.

The Vdd supply voltage needed for the holding voltage is the sum of the three forward voltage of the PNPN structure, where the middle one is reverse biased, plus the voltage over the substrate/well resistor. This would amount to about 1.0 V to 1.5 V, but it implies that the two transistors are in saturation, which is not always the case. One transistor in active mode will increase the absolute value of the reverse biased junction giving a higher holding voltage.

By lowering the main supply voltage for the device it is possible to reduce the probability of an SEL occurring [14]. As the device supply voltage gets lower for newer devices, SEL will eventually disappear.

A SEL is commonly accompanied by a SEU, but it might also trigger SEUs in several bit-arrays. This is believed to be because a short circuit between the Vdd contact or the p-source occurs so that the Vdd line in a large region of the chip is brought down below the voltage needed to retain the memory content [10].

**Figure 2.3:** *PNPN parasitic structure in an N-well bulk CMOS inverter structure* [6].

#### **Single Event Functional Interrupts**

A Single Event Functional Interrupt (SEFI) is the result of a SEU or SET creating an upset that alters the operation of the device. This is usually present in more advanced

**Figure 2.4:** The latchup I-V characteristic [15].

devices where an upset can make the device go into reset, change into a test mode or other mode that alters the device's functionality.

To experimentally detect SEFI it is possible to continuously run an operation on the device that creates a predictable output and then look for alterations in the output and restarting the device if an error occurs. An error from a SEFI can usually be distinguished from a SEL by monitoring the current of the device during the experiment. An abrupt increase in current indicates a SEL.

# **Chapter 3**

# Memory based semiconductor devices

Different techniques exists for storing a bit in a CMOS structure. The most common today are flash, SRAM, DRAM and EEPROM, but new technologies like PCRAM, FRAM and MRAM are emerging. This chapter gives an overview of the different technologies and their SEE susceptibility and applicability as a neutron detector.

#### 3.1 Static RAM

A SRAM cell has the ability to store one bit in a latched structure created by two inverters in a loop. The data does not need to be refreshed and is retained as long as the power is retained, if the power is lost the data will be corrupted. This is referred to as the device being *volatile*.

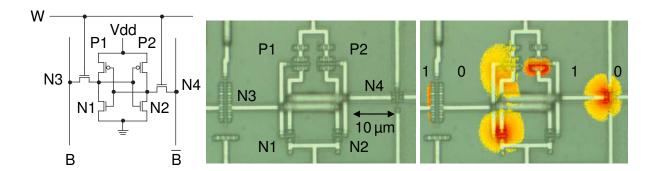

The cell structure can be built from either four transistors or six transistors, referred to as 4T and 6T cells, see figure 3.1 for example of a 6T cell. The 4T cell uses two poly-silicon resistors in the giga-ohm range for pull-up instead of the two p-type transistors. The advantage of using a 4T structure is the lower area consumption, but it has the disadvantage of having a higher power consumption due to the current constantly flowing through the pull-up resistors. The devices used in this thesis contain only 6T cells.

To read from the 6T cell both the bit (B) and  $\overline{\text{bit}}$   $(\overline{B})$  line must be pre-charged to a high value. The wordline (W) is then pulled high enabling the access transistors (N3) and (N4) causing the bit line connected with the node of the cell having 0 volt to be pulled low. A sense amplifier detects the voltage change and propagates the value to the outside.

Writing to the cell is done by forcing a high on one bit line and a low on the other while enabling the wordline overpowering the p-type transistor and changing the state of the cell.

SRAMs come in different configuration, there is asynchronous, synchronous, special types and non-volatile.

• The asynchronous is managed by three control signals. Chip enable (CE) or chip select (CS) selects or de-selects a chip. When the chip is de-selected it sets the

**Figure 3.1:** Image on left shows a standard 6T SRAM cell [16]. Center shows the same cell laid out in a 0.8 µm AMS BiCMOS technology, the spacing between transistors are exaggerated for testing purposes. Image on right shows the sensitive areas as mapped by a pulsed laser with energy from 10 pJ to 1193 pJ, darker color indicates higher sensitivity [17].

output pins in high impedance and stops responding to input signals. The write enable (WE) pin enables writing to the device. The output enable (OE) pin enables outputting of data from the selected address. As there is no clock source to control the device, a constant minimum-delay is needed between each command to the device. Typical speeds are from 10MHz to 100MHz.

- The synchronous device (SSRAM) has its read and write cycles synchronized with a clock from the readout device, this enables it to work with high-speed devices, typically hundreds of MHz.

- Special SRAMs are First-In, First-Out (FIFO) or serial SRAM, where the addressing is controlled by the SRAM itself, and dual-port SRAM which provide the ability to write and read from the device at the same time by an extra set of access transistors.

- Non-volatile SRAM either contain a battery for retaining memory or it uses flash memory in parallel with the SRAM memory.

The special SRAMs and the battery backed SRAMs share much of the same principal architecture as the asynchronous or synchronous SRAM.

#### 3.1.1 SEU susceptibility

To flip a bit in an SRAM, the ionizing particle needs to strike either the drain region of the NMOS or PMOS transistor which currently is in the off position. This can be seen in figure 3.1 where the drain of N1 and P2 have a high sensitivity. The access transistor N4 can also be seen to have some sensitivity as it is reverse biased in this case.

Because of the higher mobility of electrons than holes, and since the PMOS transistor is created weaker than its complimentary NMOS transistor, a strike in the drain of

the NMOS transistor will have a higher probability of creating a SEU than if it would hit the PMOS.

The strike on one of the critical nodes will create a transient, which if it reaches the other inverter and has enough charge to turn on the appropriate transistor will lock the new value and the bit will be flipped.

#### 3.1.2 Critical charge

The critical charge needed to flip a bit is depended on the size of the critical node, the voltage of the cell and the feedback time of the cell. This is formulated in the simple model first proposed by Roche et al. [18]

$$Q_{crit} = C_N \cdot VDD + I_{DP} \cdot T_F \tag{3.1}$$

Where  $C_N$  is the node capacitance, VDD is the supply voltage,  $I_{DP}$  is the max PMOS drain conduction current and  $T_F$  is the flipping time of the cell.

From this one can see that lowering the voltage of the device will lower deposited charge needed to be generated from the incoming ion and thus increasing the SEU susceptibility. Moving to a smaller feature size will also increase the SEU susceptibility as it will reduce the size of the node capacitance, but the sensitive area will also be somewhat smaller which counteracts it. Both effects have been found experimentally, see for instance Flament et al. [19].

When reaching certain levels of critical charge new ionizing secondary particles that before had too little initial energy to upset a node can now displace enough energy to flip the bit. This creates a jump in the SEU sensitivity compared to a similar device in the previous feature size. But in recent technologies, the fraction of the effective interactions reaches 90% and only small changes will be seen in the future [6].

### 3.1.3 SEFI susceptibility

Asynchronous SRAMs do not normally suffer from SEFIs as there is little control logic embedded in the device. But an upset in the sense amplifiers or the address decoders might enable the readout of a wrong value or the wrong address. This can be avoided by reading out three times from the same address and doing a majority vote on the read data.

Synchronous SRAMs might suffer from other SEFI as it uses registers to store the address and other control bits. An upset in one of these registers might create a wrong value being read.

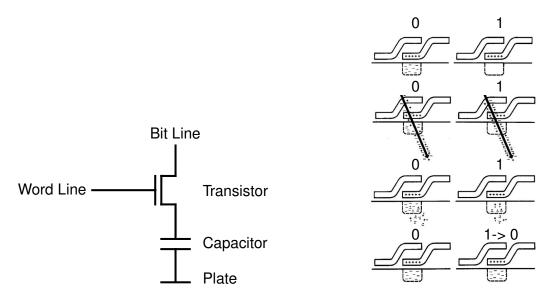

### 3.2 Dynamic RAM and Synchronous Dynamic RAM

The Dynamic Random Access Memory (DRAM) stores a bit as a charge on a capacitor. An access transistor is connected to the capacitor and isolates it from the rest of the

| Feature size | SRAM property        |         |                       |  |

|--------------|----------------------|---------|-----------------------|--|

| reature size | Normalized cell area | Density | Normalized $Q_{crit}$ |  |

| [ nm ]       | [ a.u. ]             | [ Mb ]  | [ a.u. ]              |  |

| 250          | 7.45                 | 4       | 12.8                  |  |

| 180          | 3.84                 | 8       | 6.4                   |  |

| 130          | 2.01                 | 16      | 3.2                   |  |

| 90           | 1.00                 | 32      | 1.6                   |  |

| 65           | 0.49                 | 64      | 0.8                   |  |

| 45           | 0.24                 | 128     | 0.4                   |  |

| 32           | 0.12                 | 256     | 0.2                   |  |

| 22           | 0.06                 | 512     | 0.1                   |  |

**Table 3.1:** Assumed roadmap of scaling in SRAM [20]. The size of a cell in 130nm, 90nm and 65nm is on average  $2 \mu m^2$ ,  $1 \mu m^2$  and  $0.5 \mu m^2$  respectively [21] and the critical charge of a 90nm has been found from simulation to be 1.4fC [22] so the numbers are within range.

circuitry as seen in figure 3.2. When the capacitor is not read or written from, this charge will leak off the capacitor due to the sub-threshold leakage current in the access transistor. This causes a need for the cell to be rewritten many times per second.

To read from the cell the bit line is precharged to VDD/2 and when the word line is enabled the charge stored on the capacitor is shared with the bit line causing a change in voltage on the bit line which can be detected by a sense amplifier. A read disturbs the content of the cell and thus it needs to be rewritten after every read.

To write to the cell, the desired value is force on the bit line while the word line is enabled, effectively charging or discharging the capacitor to the new value.

Due to the fewer number of transistors compared to the SRAM, a smaller area is needed per cell. The smaller area enables higher bit density per device and thus is more economic to use when high densities are required, even though the DRAM is inherently slower than SRAM due to the constant need for refreshing.

The Synchronous DRAM (SDRAM) differentiates it self from the DRAM by being a synchronous device, meaning the read and write from the device is synchronized to a clock. The SDRAM also contains all the circuitry needed to refresh a cell inside the device so that only a command is needed to tell it to refresh all the cells.

Other types of DRAM exists, but they mostly inherit their properties from SDRAM and mostly differ in the communication with the readout device.

#### 3.2.1 SEU susceptibility

The primary cause of SEUs in DRAM is due to cell discharge from an ionizing particle. Any disruption of the charge on the device will be latent until a refresh is performed on the cell. To flip the bit, the ionizing particle does not need to fully deplete the capacitor, only enough to lower the charge below the noise margin of the sense amplifier.

**Figure 3.2:** Schematic drawing of 1T DRAM cell [16].

**Figure 3.3:** An alpha particle hitting a DRAM can primarily flip a bit from 1 to 0 [23].

Another upset possibility is if the ionizing particle hits the bit line during a read when the bit line is precharged.

#### 3.2.2 Critical charge

The charge needed to upset a cell is constantly changing due to the leakage, but can generally be expressed as

$$Q_{crit} = C_{cell} \cdot (V_c - V_b) \tag{3.2}$$

Where  $C_{cell}$  is the capacitance of the cell,  $V_c$  is the voltage currently on the capacitor and  $V_b$  is the level at which the bit line is precharged to when reading, usually Vdd/2.  $V_b$  can at most be Vdd.

Mueller et al. [24] set the cell voltage at 1.4 V and the cell capacitance to 30 fF for a 90 nm device. This gives a Q<sub>crit</sub> of 21 fC, an order of magnitude higher than the 1.4 fC for a 90 nm SRAM reported by Naseer et al. [22].

### 3.2.3 SEFI susceptibility

The SDRAM has both mode registers, address registers and refresh counters embedded, and a SEU in any of these will create a SEFI. There are different results from a SEFI in a SDRAM, hitting the address register might create a read or write to a wrong row or column. A hit in the mode register might put the device into a test mode, preventing read and write until the correct mode is rewritten. A hit in the refresh counter or other places in the mode register might create a SEFI where the device needs to be power cycled to work again.

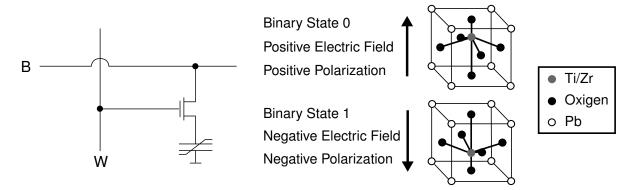

#### 3.3 Ferroelectric RAM

Ferroelectric RAM (FRAM) is similar in construction with the DRAM but uses a ferroelectric layer instead of a dielectric layer in the capacitor to provide non-volatile storage. There is no leakage from the capacitor and hence it doesn't need to be refreshed. A ferromagnetic material has a nonlinear relationship between the applied electric field and the apparent stored charge which results in a hysteresis curve. When an external electric field is applied over the capacitor, ions in the ferroelectric material shift their position to one of two positions depending on the polarization of the electric field applied. When the electric field is removed, the ions remain polarized in the same position as when the electric field was present [25].

Ferroelectric materials switch only in an electric field and are not affected by magnetic fields.

**Figure 3.4:** Schematic drawing of 1T FRAM cell [16].

**Figure 3.5:** *Two stable states in a ferroelectric material* [25].

#### 3.3.1 SEE susceptibility

Since FRAM is a relatively new technology and has only recently become affordable in respect to flash, DRAM and SRAM there has been little interest by the space industry, which are the main main driving force for testing of COTS devices, to investigate SEE susceptibility.

Some testing has been done by Scheick et al. [26] and it has been found that FRAMs are sensitive to SEUs and SELs and should be excluded from use in severe radiation environments.

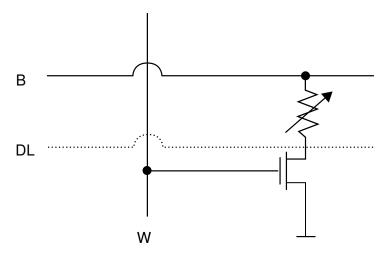

### 3.4 Magnetoresistive RAM

Magnetoresistive RAM (MRAM) uses two ferromagnetic plates separated by a thin insulating layer to store its data. One element is a permanent magnet with a fixed magnetic polarization, the other one can be polarized by an external field. When both magnets

have the same polarization they create a low resistance path, when they have opposite polarization they create a high resistance path.

Reading from the cell is accomplished by measuring the current when enabling the word line and setting the bit line high. A high current indicates a '0', a low current indicates a '1'.

Writing is accomplished by passing a current through the bit line (B) and the digit line (DL), which lie perpendicularly to each other, causing an induced magnetic field at the junction where the cell is.

Figure 3.6: Schematic drawing of 1T MRAM cell.

#### 3.4.1 SEE susceptibility

The same argument about the low amount of available data for SEE susceptibility of FRAM also apply for MRAM. Since the cells do not rely on charge to store a bit, they should not be vulnerable to SEUs, but the sense amplifiers and the programming circuitry probably are [27]. Resistance against TID effects and SEL effects are found to be rather good in new devices [28].

### 3.5 Phase Change RAM

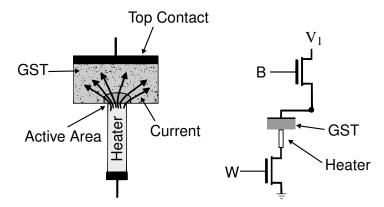

Phase-Change RAM (PCRAM), also known as PRAM, Chalcogenide RAM (C-RAM) and Ovonic Unified Memory, employs a chalcogenide material, such as a Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> alloy (GST), to store its data. This material has the ability to change between a amorphous and a polycrystalline form when heated and cooled [29]. In the amorphous state, the material features a high resistivity while in the polycrystalline form, it is characterized by a low resistance value.

Figure 3.7 shows the schematic of a PCRAM cell composed of a heater and the GST material. To write a '1' (SET state), the GST material is heated to a temperature between

200 °C to 400 °C which is above the crystallization point, but below the melting point. In this state the material has a low resistance.

To write a '0' (RESET state), the GST is heated to above the melting point of 600 °C. This turns it back into a amorphous, an almost glass like, state which has a high resistance. The time to switch from one state to another is about 100 ns.

Reading the device is done in the same manner as with the MRAM. By putting a voltage over the cell, the amount of current flowing through it can be detected by a sense amplifier. A high current indicates a '1', and a low current indicates a '0'.

As the material is permanently in its present state until reheated, the data will not be lost when powering off the device making it a non-volatile memory.

Figure 3.7: Schematic drawing of a PCRAM cell.

#### 3.5.1 SEE susceptibility

The PCRAM has only recently become available commercially, but some SEE and TID testing has been done concluding that the only change seen are degradations of the select transistors causing a move in the characteristic current for '1' and '0' [29] [30]. The sensing circuitry was not tested, as it was placed external to the chip on this sample. Since it is based on Complementary Metal Oxide Semiconductor (CMOS) technology it might be sensitive to SET.

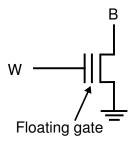

### 3.6 Electrically Erasable Programmable ROM

Electrically Erasable Programmable Read-Only Memorys (EEPROMs) can store a bit with a single transistor. This transistor is equipped with two gates separated by a thin insulating layer where the bottom gate is floating [16]. When applying a high voltage to the top gate and Vdd to the source, some electrons will flow from the channel through to the bottom gate due to the Fowler-Nordheim tunneling effect. Upon turning off the voltage, the electrons will be trapped in the floating gate causing the transistor to have a higher threshold voltage. The cell is now referred to as erased and will be recognized

3.7 Flash memory 23

by the readout circuitry as a '1'. To program the cell and remove the trapped electrons, a high voltage is applied to the source of the transistor with the gate grounded.

**Figure 3.8:** *Schematic drawing of a EEPROM cell.*

# 3.6.1 SEE susceptibility

Due to the construction and size of the floating gate in the EEPROM cell, removal or insertion of charge into a floating gate by an ionizing particle will be difficult. The EEPROM have been found to have a very low SEU cross section while reading and a somewhat higher for writing [31]. Though the readout circuitry is still vulnerable and can cause SEFI with a higher cross section [32].

# 3.7 Flash memory

Flash memory is similar in many ways to the EEPROM and got its name because it has the ability to erase whole blocks of memory at once instead of just one bit at a time like the EEPROM. The flash cell uses a floating gate transistor, similar to the EEPROM, and is commonly connected together in either a NAND or NOR configuration, as seen in figure 3.9. The NAND construction uses less layout space but is inherently slower as all the transistors are in series.

Due to the use of a more compact cell construction and because it utilizes a block configuration, the flash memory can achieve much higher densities and speeds than the EEPROM and hence it has become the most widely used non-volatile memory today.

# 3.7.1 SEE susceptibility

Due to the increased density and aggressive scaling of flash memory, the floating gate of the flash memory is becoming more vulnerable to SEUs from lower LET particles [33][34]. A 90 nm 1 Gb NAND flash was found to have a cross section of  $10^{-15}$  cm<sup>2</sup> bit<sup>-1</sup> at an LET of 10 MeV cm<sup>2</sup> mg<sup>-1</sup>. SEFIs are also present, but at 3–4 orders of magnitude lower cross section [35].

Recent devices also employ a page buffer for storing a complete block read from the flash memory. This page buffer is constructed from SRAM cells which have a relatively

**Figure 3.9:** *Schematic drawing of the flash NAND and NOR structures* [16].

high cross section per bit. But as the page buffers are small, with a size of some kilobit, the cross section per device becomes relatively small.

# 3.8 Applicability of different memories as a neutron detector

Some features of the memory is necessary to be present for it to be useful as neutron detector, listed here in descending order:

# **High SEU cross section**

A high SEU cross section per device is needed to get a detector with a high efficiency. To achieve this, the device can have a lower cross section per bit, but be available in a high density, or it should be cheap enough to be bought in quantities large enough to compensate for the low density.

#### Low amount of unwanted radiation effects

This includes SEL, SEFI, TID, stuck bits and destructive breakdowns. SEL can be mitigated on the hardware level by restarting the device upon a current increase, by using a current limiting device to avoid the latchup structure reaching its holding current or by running at a voltage too low for the latchup to occur, if the device allows it. Stuck bits can be mitigated in the firmware by writing back and re-reading the bit detected to have a SEU, to check if the written value sticks. SEFI can be mitigated by restarting the device upon detecting many errors in a row or other effects particular for the device under test. TID and breakdowns can not be mitigated. All these effects either creates dead-time for the detector or increases the probability of a wrong radiation level readout.

#### **High endurance**

Depending on the end use of the device, it might be needed to have a continuous

lifetime of at least a year or two. Two effects factor in here, the TID and normal aging. TID is not normally a concern if the device is not supposed to be used in a high radiation environment, as most devices can withstand an accumulated dose of more than 10krad. Aging effects depends on the type of memory, but most suffer at least from electromization and thermal damage. Floating gate memories have problems with degradation of the oxide between the floating gate and the channel, causing the cell eventually not to be programmable.

If a device has a readout time for the whole device of 100 ms, it would need an endurance of  $6 \times 10^8$  to survive two years.

## Fast read/write speed

Depending on the end application, having a delay of tens of seconds between a particle hitting the device and a SEU being detected by the readout can be unwanted. The device read-through speed is both dependent of the density and the bit read-write speed of the device.

|              | FRAM       | MRAM      | PCRAM    | Flash      | EPROM    | SRAM       | DRAM       | Ideal      |

|--------------|------------|-----------|----------|------------|----------|------------|------------|------------|

| Write Speed  | <150ns     | <40ns     | <150 ns  | <100 ns    | <10 µs   | <10ns      | <200 ns    | <60 ns     |

| Erase Speed  | <150ns     | <40ns     | <150ns   | >10ms      | >10 s    | <10ns      | <60 ns     | <200 ns    |

| Endurance    | $10^{12}$  | $10^{15}$ | $10^{6}$ | $10^{6}$   | $10^{5}$ | $10^{15}$  | $10^{15}$  | $10^{9}$   |

| Cost/Bit     | High       | High      | Med      | Low        | Med      | Med        | Low        | Low        |

| Bits/Dev     | $10^{6}$   | $10^{6}$  | $10^{8}$ | $10^{10}$  | $10^{6}$ | $10^{7}$   | $10^{8}$   | $10^{8}$   |

| SEU (bit)    | No         | No        | No       | Yes        | No       | Yes        | Yes        | Yes        |

| SEU (periph) | Yes        | Prob.     | Yes      | Yes        | No       | Yes        | Yes        | Yes        |

| SEU $\sigma$ | $10^{-16}$ | na        | na       | $10^{-17}$ | na       | $10^{-14}$ | $10^{-18}$ | $10^{-10}$ |

| SEL          | Yes        | Prob.     | Yes      | Yes        | Yes      | Yes        | Yes        | No         |

| SEFI         | Prob.      | Prob.     | Prob.    | Yes        | Yes      | Yes/No     | Yes        | No         |

**Table 3.2:** Overview of specifications for different RAM, partly based of Kayali [36]. Cross section of SEU is taken for protons at 50MeV. 'na' in the table indicates data was not available. Endurance is measured as number of read write cycles before problems arise.

Table 3.2 summarizes the features of each device. From what has been proposed above as the ideal detector, it can be seen that the MRAM and PCRAM can be dismissed, since they have not currently been found to be sensitive to SEU, testing could be done to determine this further. FRAM is currently available at too low densities and at a too high price to be useful at this time, but could be applicable in the future. Flash suffers from a lot of unwanted radiation effects and has in addition a low endurance. EEPROM are available at too low densities and has even lower endurance. This leaves DRAM and SRAM as viable contenders. The current density of DRAM do not make up for its low SEU cross section compared with the SRAM. A pre-study was done for this thesis, as noted in the section 1.2, with a SDRAM from an older technology node compared to a SRAM and it was found that it had a SEU cross section of at least three orders of magnitude lower than the SRAM.

For this work several different SRAMs have been picked for their various properties. Two synchronous SRAM from two different manufacturers were chosen to test if SEFI would hinder them from being used as a neutron detector. One device was picked for being able to run at voltages as low as 1.0 V, in contrast to 1.5 V as is normal for most of the other devices we have tested. A lower voltage reduces the charge needed to upset a memory cell and thus will increase a device's overall sensitivity. One device was chosen for its fast access speed of 10 ns, in contrast to 55 ns which was common for most of the other devices we tested. Access speed could possibly alter a device's sensitivity through for instance SETs. Another device was chosen for having the largest available bit size for an asynchronous SRAM of 64 Mb. A larger bit size means a larger sensitivity per device if the sensitivity per bit is not exceptionally low. The rest of the devices were chosen from the ultra low power series from Cypress to look for similarities between devices within the same series. The device with the high bit size is also a part of this series.

# **Chapter 4**

# **Neutron detector implementation**

This chapter focuses on the development of the hardware, firmware and software for a neutron detector.

# 4.1 Detector system overview

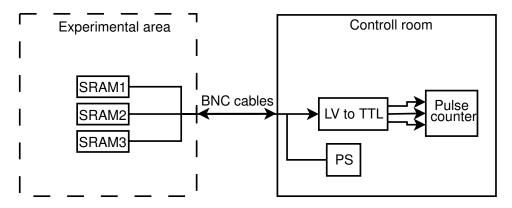

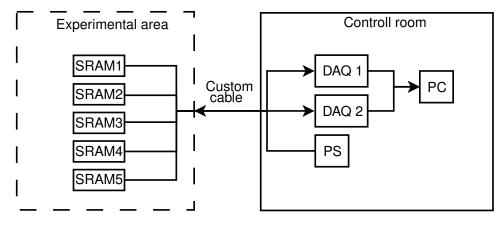

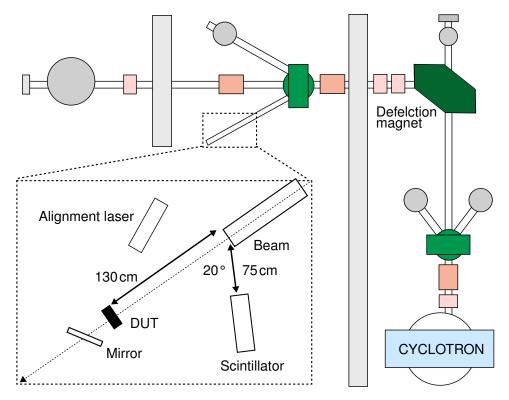

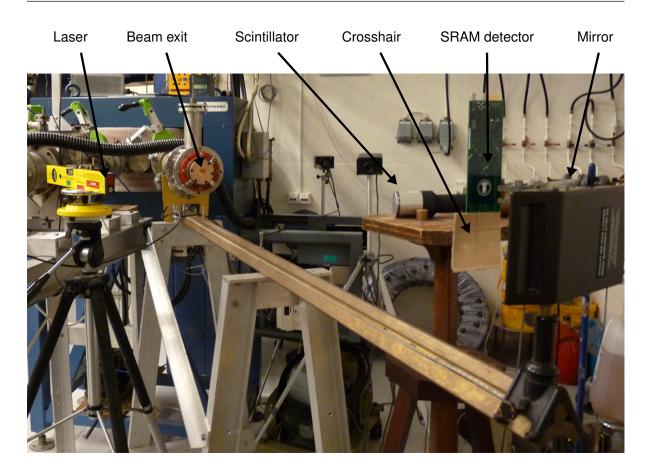

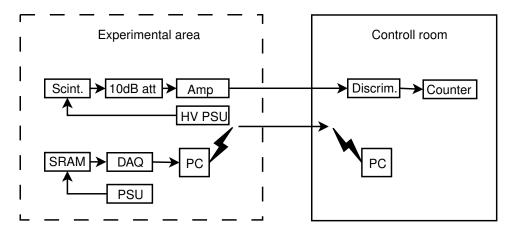

To have a setup for actively detecting neutrons, at minimum three things are needed. 1) A sensor to convert the energy deposited by the particle to a readable signal, 2) a preprocessor for detecting the signal and converting it to a signal which can be transmitted to the readout and 3) a device for collecting or reading out the number of counts from the detector. The last device can also be split into two, having a device in between that converts the signal to a readable signal for the device which counts the events from the detector. A general setup can be seen in figure 4.1.

Converting the energy deposited by the particle can be done in many ways, but in electronic memory this energy is converted to a flipped bit. This bit flip can be detected by writing a known pattern to the memory and continuously reading it back checking for alterations to the known pattern. The readout of the sensor can be done with for instance a microprocessor, an Field Programmable Gate Array (FPGA) or by use of basic electronic circuits. The readout device also needs to be able to transmit the number of events detected to the device collecting the events. This gives the device the functionality of a preprocessor of the sensed signal. Accompanying the preprocessor there are commonly also support electronics needed for the operation of the preprocessor and the sensor. This can be for instance power supplies, clock circuits, communication circuits or other sensors for temperature or current.

The device which should convert the signal from the detector to a readable signal by the data processing device is commonly either an Analog to Digital Converter (ADC), a Data Acquisition (DAQ) device or a direct communication link. The data is then fed to a device that post processes the data and stores it for later retrieval or it displays the data directly to the user. This device could be a pulse counter, a computer or a specificly designed hardware.

If we compare the general setup with a scintillator setup, we have the scintillator as

the sensor, the photo multiplier tube in combination with an amplifier as the preprocessor and a pulse shaper in combination with an ADC, inside a counter, as the converter. The signals can then be collected and displayed by a pulse counter.

**Figure 4.1:** Overview of a detector system.

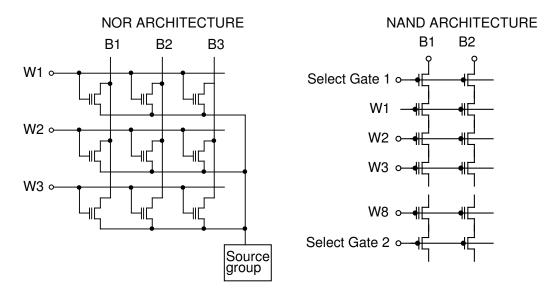

### 4.2 Hardware

An important aspect of creating hardware for a neutron detector is to avoid any additional components besides the SRAMs that suffer from Single Event Effects (SEE). Figuring out if a component is suitable can be determined by looking for radiation testes of the same component already completed by others or by picking suitable components and testing them yourself. COTS components have been used in the space industry for some time due to low availability of high performance semiconductors [37] and a large amount of test data of radiation hardness and SEE susceptibility have been accumulated over time. An example of such a database is the NASA Goddard Space Flight Center Radiation Test Database [38].

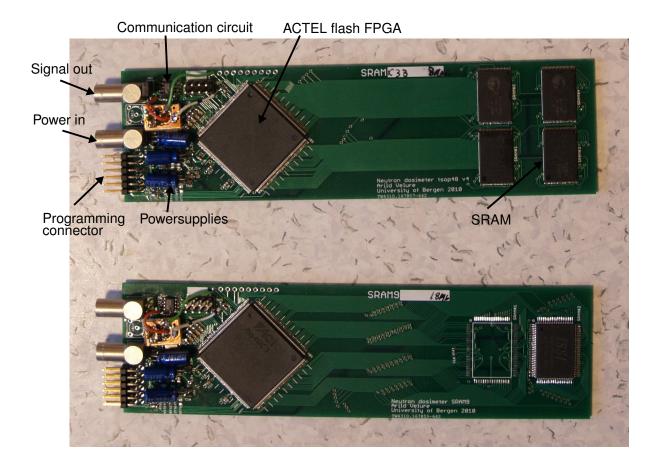

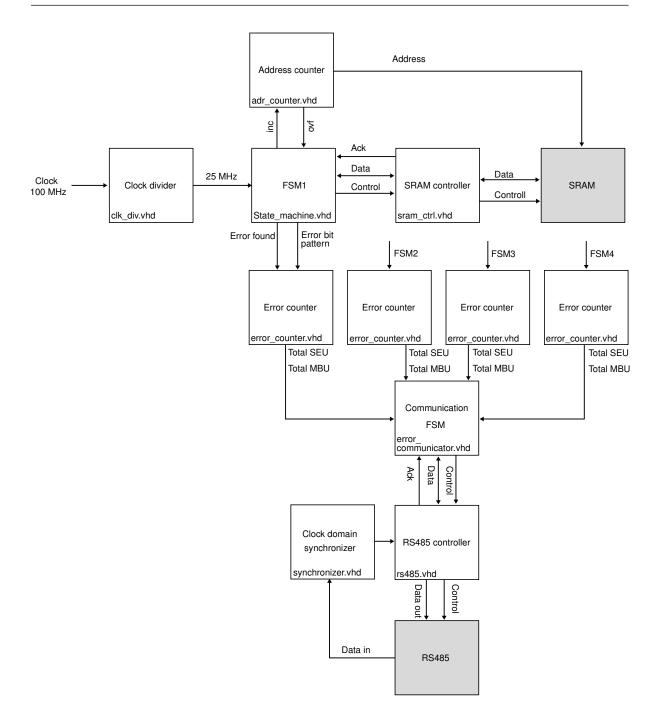

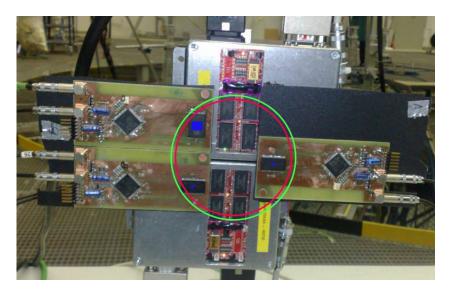

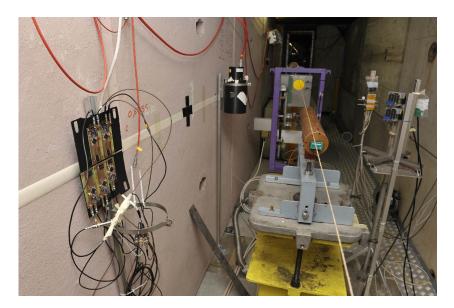

A schematic overview of the hardware can be seen in figure 4.2 and a picture of two of the detectors can be seen in figure 4.3.

The hardware exists in two revisions, but with only minor component differences. The first design is composed of a 100 MHz crystal oscillator providing the main clock, an Actel IGLOO nano IGLN250Z flash FPGA for controlling the read out of the SRAM and communicating with the PC, some step down voltage converters, two transistors acting as an inverter for pulsing out SEUs and the SRAM.

The second design adds the possibility of having four SRAMs on two separate buses. As this increases the number of pins beyond the 100 which are available on the Actel IGLOO, the IGLOO is exchanged by an Actel ProASIC3 A3P250 flash FPGA with 208 pins. The inverter is also replaced by a LTC1480 RS485 communication circuit. The inverter circuit can be added back by connecting an add-on board to some spare connections on the board.

The first design was used for testing at PTB and CERF and the second revision for the other tests.

4.2 Hardware 29

**Figure 4.2:** *Schematic overview of hardware for the detector.*

# 4.2.1 SRAM packages

Just as everything else, SRAMs come in different sizes and packages. From a designers point of view this means different placement of address/data-bus and different pin layouts. Most manufacturers adhere to the JEDEC Standard No. 21C [39], which describes the pin layout for many types of RAM devices, packages and sizes. But since not everything is specified in the standard, some qualified guesswork and comparison of different makes and models needs to be done to avoid making hardware modifications when later adding a new type of SRAM to an existing board.

The 2nd revision Printed Circuit Board (PCB) exist in five different designs created for five different packages, Thin Small-Outline Package 2 (TSOP2) 44 pin, Thin Small-Outline Package 1 (TSOP1) 48 pin, Very Fine-Pitch Ball Grid Array (VFBGA) 48 pin, Thin Quad Flat Pack (TQFP) 100 pin and Fine-Pitch Ball Grid Array (FBGA) 165 pin. To avoid some of the problems of pin compatibility, all of the pins that were not ground or power pins on the three first packages mentioned were all routed to the FPGA. The decision of which pins should be connected to what can now be done in firmware at a later stage.

To increase the number of SRAMs to be tested at once on the same board when there is a constrain on the number of pins available on the FPGA, it is possible to utilize a bus structure connecting two or more SRAMs in parallel. This is possible by having a separate connection to the chip enable pin for each SRAM. The chip enable pin makes the SRAM put it's data pins in high impedance mode avoiding interference with the other SRAM circuits. In addition it will also stop responding to write and read signals. The PCBs design for the two TSOP packages and the TQFP package utilizes this bus structure to connect two SRAMs to the FPGA.

**Figure 4.3:** *Picture of two of the detectors.*

# 4.2.2 Voltage control

Different SRAMs are specified to different core voltages and current consumptions. In addition it has previously been found by among others Flament et al. [19] that the cross section for SRAMs are dependent on the core voltage. This calls for a flexible voltage supply design which is handled by adding a variable voltage supply that can be controlled by changing resistor values. These resistors are connected to pins on the FPGA, enabling control of the voltage from the firmware during runtime.

The voltages and currents available are  $500\,\text{mA}$  down to  $1.2\,\text{V}$  and  $100\,\text{mA}$  down to  $0.6\,\text{V}$ , depending on the voltage controller used.

#### 4.2.3 Communication interface

To be able to monitor the detector from the control room during irradiation, the detector needs some form of hardware for transmitting its data over the communication link. Connecting the communication link directly to the FPGA is possible, but not advisable as a malfunction in the communication link could damage the FPGA directly. Some form of buffer or communication device in between the link and the FPGA is the best

4.2 Hardware 31

choice.

When choosing communication form, there is a choice between simplex, half-duplex or full-duplex communication. Simplex is the most trivial form, where the data can only flow in one direction. This communication form can be found in many particle detectors like for instance the scintillator, where a pulse is transmitted for every detected particle. In half-duplex communication both the detector and the receiver can communicate with each other over the same link, but only one at a time. The communication circuit would commonly use the same pair of wires for both sending and receiving. In full-duplex communication both detector and receiver can talk to each other at the same time without disturbing the communication.

If testing many device at the same time, a communication protocol which uses halfor full-duplex communication in a bus or ring topology would be the best as this would minimize the amount of cabling needed between the experimental area and the control room.

There are three main iterations in the firmware design for the communication which are described below.

#### Pulse counter design

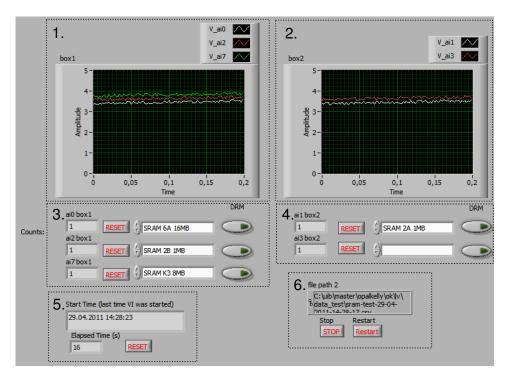

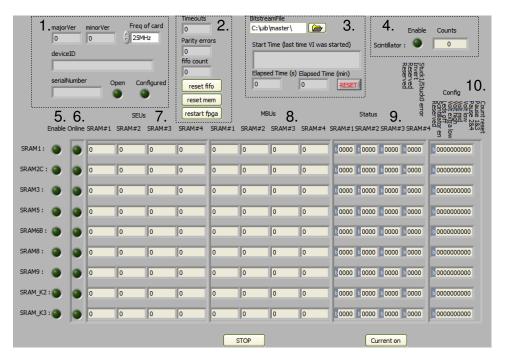

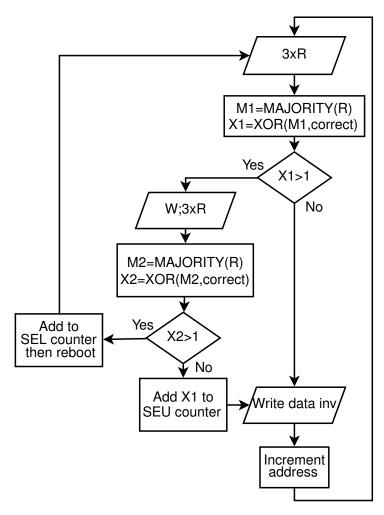

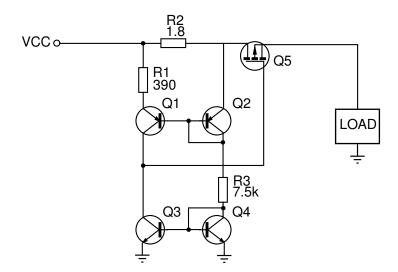

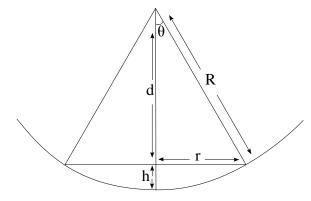

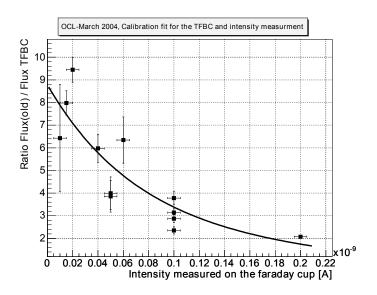

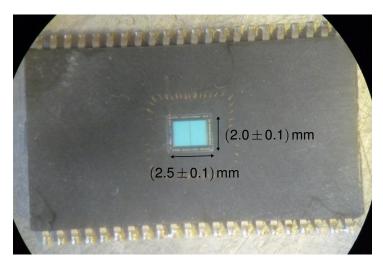

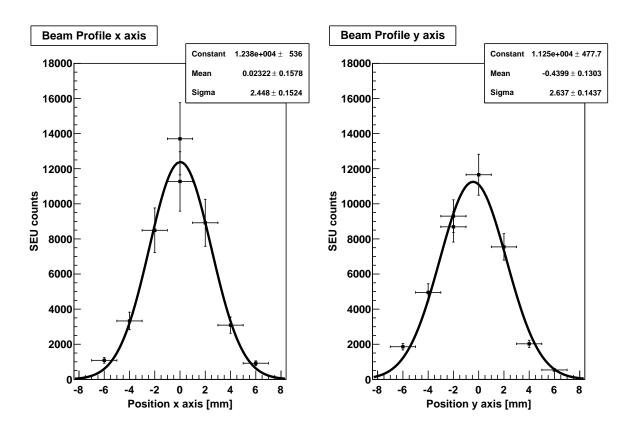

The first design used in accelerated irradiation testing at PTB, uses a simplex communication form. The detector sends out a short pulse for every SEU detected in the SRAM. The signal can be connected to a pulse counter to recorded the total amount of SEUs per run. A simple inverter, used as a buffer, is placed in between the FPGA and the communication link on the detector.