# Parallel Matching and Clustering Algorithms on GPUs

#### Md. Naim

Thesis for the degree of philosophiae doctor (PhD) at the University of Bergen

2017

Date of defence: June 27th, 2017

### Acknowledgements

First and foremost, I would like to thank my supervisor, Prof. Fredrik Manne, for giving me the opportunity to be his PhD student. He has always been encouraging and optimistic while guiding me through my studies. His enthusiasm and patience for countless discussions helped me significantly to finish my PhD projects. His door has always been open to discuss practical issues that I faced during my stay in Bergen. Last but not least, thank you for your patience in reading my thesis meticulously to correct my bad writing. I am deeply indebted to you for your time, encouragement and generosity.

Second, thanks to my colleagues at the department who created a friendly and welcoming environment. In particular, I would like to thank my officemates Torstein Strømme and Paloma Lima for a lively office. Thanks go to current and former master students at the algorithms group.

I want to thank my coauthors Antonino Tumeo, Håkon Lerring, Johannes Langguth and Mahantesh Halappanavar. Thanks to Jan Arne and Markus Fanebust Dregi for their valuable feedback after my presentations at the algorithms seminar.

Thanks to Antonino Tumeo and Mahantesh Halappanavar for inviting me at Pacific Northwest National Laboratory, USA, where I spent two wonderful summers. It was a great environment to learn from other researchers and make friends. Special thanks to Antonino and Johannes for giving me access to their parallel computers.

I would like to thank the administrative staff, Eli Ertresvaag, Ida Rosenlund, Liljan Myhr, Liv Rebecca A Aae, Maria Marta Lopez, Tor M. Bastiansen, and the former members who always helped in practical issues since I moved to Bergen.

Finally, thanks to my parents, siblings, friends and relatives for their continued support and patience.

Bergen, April 2017 Md. Naim

# Contents

| Ackno | wledgements                                    | iii |

|-------|------------------------------------------------|-----|

| 1     | Introduction                                   | 1   |

| 2     | Parallel Computing                             | 4   |

|       | 2.1 Shared Memory Programming                  | 5   |

|       | 2.2 Distributed Memory Programming             | 5   |

|       | 2.3 Heterogeneous Computing                    | 6   |

| 3     | GPUs For General Purpose Computing             | 6   |

|       | 3.1 The GPU Architecture and Programming Model | 9   |

| 4     | Generic Graph Analytics on GPUs                | 15  |

| 5     | Conclusion                                     | 16  |

| Paper | I                                              | Ι   |

| Paper | II                                             | II  |

| Paper | III                                            | III |

| Paper | IV                                             | IV  |

#### 1 Introduction

Combinatorial scientific computing (CSC) is an interdisciplinary field that deals with discrete algorithms involved in the efficient solutions of problems arising in computational science and engineering (CSE). Even though combinatorial algorithms have long played a crucial rule in CSE, the field formally came to be known as combinatorial scientific computing in 2002 [14]. The focus includes, but is not limited to, efficient parallelization and balanced load distribution of computational problems on large computing systems, optimization, fast implementation of sparse matrix routines, algorithmic differentiation for numerical computations, as well as combinatorial applications to analyze large-scale social networks [48].

Very often, computational models that are used to solve problems in science and engineering are expressed in terms of continuous mathematics. To solve these problems efficiently, research in CSC aims to identify and solve combinatorial subproblems of the models. The solution process often involves the design, analysis and implementation of graph or hypergraph algorithms to produce high performance software [8, 58]. Such algorithms must be able to solve the combinatorial subproblems efficiently or else these might become bottlenecks in the solution process. Since the involved datasets are often very large, a quadratic running time could be too slow to be useful. In such cases an approximation or a heuristic might be a better choice to provide a fast and sufficiently good solution. In addition, it is also often important that the solution method is amendable to parallelization as a sequential algorithm could dominate the overall computation even if it runs in subquadratic time.

Problems arising in scientific computing can be dauntingly large and often too compute intensive to be solved by a single processor. For this reason scientific computations has been one of the leading forces in developing ever larger and more powerful computing systems. But today it is not only supercomputers that offer parallel processing, this is now something that almost all computers and computing systems are capable of. However, in order to take advantage of multiple processing units, it is necessary to invest sufficient effort in developing code that can run in parallel. As a consequence there exists a long tradition within the scientific community for developing parallel methods and programs that can utilize these resources.

To minimize the overall execution time of a parallel program, a problem needs to be evenly subdivided among the available processors and with as little data dependencies as possible. In this way one can achieve an even load balance, while minimizing the amount of time spent on communication. Other important issues that must be considered are to maximize data locality and to reduce the number of cache misses. For dense and well structured problems much of this is well understood, but when solving sparse and more unstructured problems there are other additional concerns that must be addressed. Sparse matrices and

graphs are harder to partition evenly and dependencies between different parts of computations are typically more irregular. For these reasons it often becomes more challenging to obtain a balanced partitioning that preserves data locality.

Many of the involved problems in designing efficient parallel algorithms for sparse problems are combinatorial by nature. Mapping these to new types of hardware with massive computational power has over the last decade been one of the factors that has maintained and elevated the importance of CSC in the scientific community [14, 48].

Even though there has been a tremendous increase in compute power during the last decades, the fundamental way in which parallel systems are programmed has been fairly static. The two most commonly used programming models, MPI and OpenMP, have both been available for at least 20 years, and even though they have evolved over time, the underlying conceptual layout of shared and distributed memory computers has not changed much. However, one thing that has changed is that dedicated co-processors have become common in large scale systems. These processors are used by the central processing units (CPUs) to offload compute and data intensive parts for which they are particularly well suited. Graphic processing units (GPUs) are by far the most common co-processors. They are fundamentally different from traditional CPUs in that they can process up to thousands of independent threads simultaneously. Programming GPUs is challenging for several reasons. For instance, the hardware only supports synchronization between a limited numbers of threads and also introduces new issues related to memory usage. But due to the massive parallelism and compute power offered by GPUs, there has been a substantial interest in porting and also in developing new solutions onto such systems.

This thesis studies graph algorithms to solve some well known combinatorial problems on GPUs. In particular we study matching problems and the related stable marriage problem, both in which the object is to pair together vertices according to similarity measures. As a generalization of these problems we also study the Louvain clustering method [7]. For all of these problems we develop efficient GPU algorithms and show that this gives significant performance gains using fairly inexpensive hardware. For all considered problems we study issues related to resource utilization, synchronization and load balancing. The thesis consists of following four papers:

- I. Md Naim, Fredrik Manne, Mahantesh Halappanavar, Antonino Tumeo and Johannes Langguth. Optimizing Approximate Weighted Matching on Nvidia Kepler K40 In proceedings of the IEEE International Conference on High Performance Computing (HiPC), 2015.

- II. Md Naim and Fredrik Manne. Scalable b-matching on GPUs, Submitted, 2017.

- III. Md Naim, Fredrik Manne, Mahantesh Halappanavar and Antonino Tumeo. Community Detection on the GPU. Accepted for presentation at the IEEE International Parallel and Distributed Processing Symposium (IPDPS), 2017.

- IV. Fredrik Manne, Md Naim, Håkon Lerring and Mahantesh Halappanavar. On Stable Marriages and Greedy Matching, In proceedings of the Seventh SIAM Workshop on Combinatorial Scientific Computing (CSC), 2016. Best paper award.

Paper I presents a redesign and GPU implementation of a practical algorithm for the  $\frac{1}{2}$ -approximate edge weighted matching problem. The main focus is to address key challenges when implementing graph algorithms on modern GPU architectures. Through extensive experiments the paper documents the impact of synchronization and load balancing on the overall running time.

Paper II presents a new greedy algorithm for the maximum edge weighted b-matching problem. This is a generalization of the problem studied in Paper I. The algorithm is highly efficient for solving the problem on a single GPU. It also extends the implementation to multiple GPUs to handle large inputs. The algorithm avoids dynamic load balancing in order to reduce the burden of synchronization and also to increase the independence between threads.

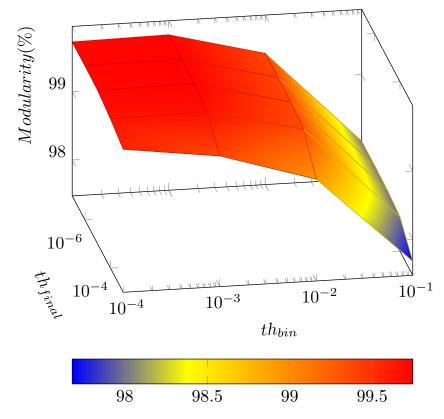

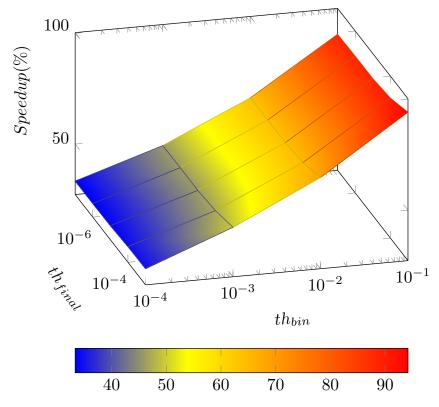

Paper III presents a new GPU algorithm based on the Louvain method for community detection. To maximize the utilization of resources, the presented algorithm parallelizes the access to individual edges rather than vertices. This provides an extra level of parallelism compared to previous implementations. In addition, the GPU algorithm scales the number of threads assigned to a vertex based on its degree. This helps to achieve a fine grained task distribution among the threads.

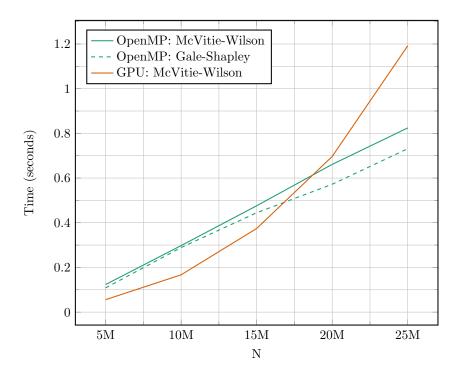

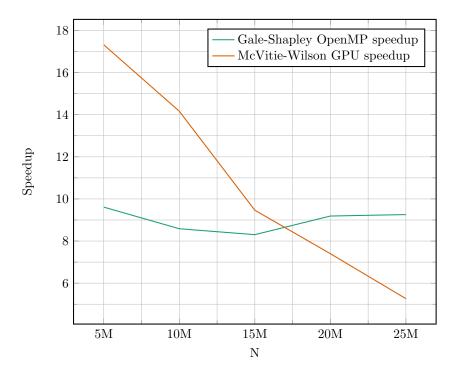

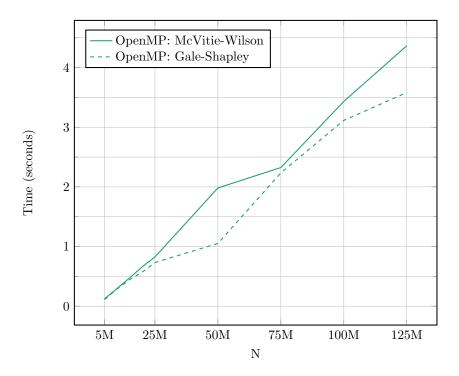

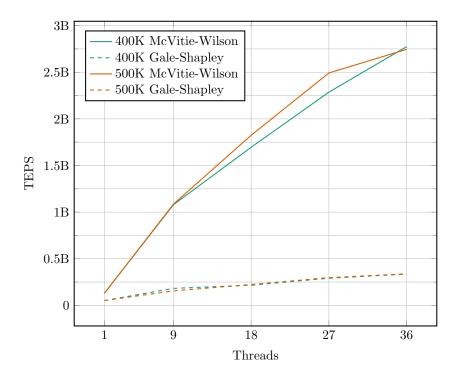

Paper IV focuses mainly on relating greedy matching with the well known stable matching problem. It shows that several practical matching problems can be formulated as stable marriage problems. In turn, algorithms for the stable marriage problem, can be parallelized using techniques developed for greedy algorithms for matching problems. The paper presents and tests efficient algorithms for the stable marriage problem both on shared memory computers and GPUs.

The remainder of this thesis consists of the following parts: Section 2 provides a short overview of parallel computing systems. Graphics processors are presented in Section 3. This section covers both the evolution of GPUs and also how current systems are designed and programmed. Section 4 contains a short introduction to generic graph libraries for solving graph problems on GPUs. Finally, Section 5 summarizes the main results of the thesis, before papers I-IV are presented.

#### 2 Parallel Computing

High Performance Computing (HPC) generally refers to the use of multiple processors to solve large and complex computational problems. But it's not limited to the use of multiple processors. In addition HPC also encompasses hardware systems, computing platforms, parallel programming tools, along with various other essential components that help tackle large compute and data intensive problems. To satiate the ever-growing demand for more computational power to solve larger problems in a reasonable amount of time, new technologies keep emerging which in turn change the concepts of HPC [62].

In the last three decades the clock speed of consumer processors has increased by a factor of 1000, from a few MHz in 1970s to a few GHz today. Even though it is not only the clock speed that has boosted the computational power, it has been one of the important contributors to performance, along with optimized execution and faster and larger system memory and caches. But in the last decade increased clock speed has not contributed much to extract more performance. This is due to various fundamental limitations such as power consumption and heat production. Since the introduction of Power4 [70], the worlds first multicore processor [59], the core count has increased from one to around ten to circumvent the need to operate at higher frequencies. Sophisticated instruction pipelining and multilevel cache hierarchies have become commonplace- altogether converting a consumer processor into a parallel processor [26, 62, 68].

Supercomputers and data centers have also obtained massive performance gains with improved processors. But most of the performance gain has come from the use of multiple processors, each with multiple cores. Parallel computer architectures are typically classified in two categories depending on their memory organization. In distributed memory systems, processors with local memory are connected through a network and communicate with each other by sending and receiving data. In shared memory systems, a multi-processor generally consists of one or more processing units that share the same system memory. Each such processing unit is normally composed of multiple physical cores. A processing unit can also have hardware capabilities to time-share the cores [12].

Recently, multiprocessors with significant higher number of cores (up to a few hundreds) have become available. These are known as *many-core* multiprocessors. Typically large systems are built by combining shared memory multiprocessors using a message passing network. These are known as hybrid systems. The current most powerful supercomputer in the world (as of November 2016), the Sunway TaihuLight [19], is built using a network of around fifty thousand *many-core* processors each with 260 cores [74].

#### 2.1 Shared Memory Programming

In a shared memory computing system, multiple cores belonging to one or more processing units (CPUs) share the same system resources. The most commonly used programming and execution model for such systems is the multi-threading model (and it's different variants) where each thread has its own private program counter and stack area while all threads share the same address space and system memory. Having common system memory where each thread has read and write access makes it easier to divide and assign the computational problem to participating threads based on their runtime IDs. Even though threads can communicate with each other through the shared memory, concurrent access from multiple threads to a memory location can cause data races when two or more threads access the same memory location. Depending on the chronological ordering of the operations performed on the location, the output of the computation can differ from run to run. Race conditions can be avoided using mutual exclusion, synchronization or locks that are implemented based on special hardware instructions. Similar kinds of techniques are used to protect memory locations and guide the execution flow to achieve correct computation results. Erroneous usage of mutual exclusions and barriers can cause a deadlock among a subset of participating threads and hence demands special attention while writing programs for multiple threads.

Different application program interfaces (APIs) that provide threading abstractions makes it easier to write programs for shared memory computers. One of the most common abstractions is OpenMP [17] which consists of compiler directives and runtime library routines. Using compiler directives, a programmer can specify parallel work sharing regions, mutual exclusions, locks, synchronization barriers, etc. The runtime library of OpenMP creates a thread pool consisting of a specified number of threads that are assigned with tasks created according to compiler directives in parallel work sharing regions.

#### 2.2 Distributed Memory Programming

Large problem instances might not fit in the limited memory of a single multiprocessor. It could also demand more computational power than that available on a single processor for the results to serve practical purposes. In such cases, a computational problem can be distributed across a network of multi-processors (i.e. a distributed memory system) connected using some type of interconnection network. In this computing paradigm, each independent unit of logical execution is referred to as a process. Typically one process is designated to read and then distribute the original problem to each participating process. It is also possible for each process to independently load its data at the start of the computation. During the course of execution, a process explicitly sends and receives data from other processes using either point-to-point or collective operations [66]. Any synchronization among the processes is achieved by the means of message passing. MPI is the most commonly used library for communication [23].

#### 2.3 Heterogeneous Computing

Shared memory, distributed memory and hybrid systems typically use processors with the same instruction set architecture and are therefore referred to as homogeneous systems. However, different architectures are often well suited for different kinds of tasks and hence employing a particular processor for particular computations can improve the overall performance in terms of time, power consumption and cost of hardware. The usage of processors with different instruction set architectures is known as heterogeneous computing. A heterogeneous system can consist of any combination of architectures, like CPUs, GPUs, field programmable gate arrays (FPGAs), digital signal processors (DSPs), many-core processors such as Xeon Phi and many others [9, 29, 31, 50]. After the emergence of GPUs for general purpose computations, a typical heterogeneous system consists of several CPUs and GPUs [11] where the GPUs are connected to the CPUs using technologies such as a PCI-Express bus [12, 51] or NV-Link [54, 15]. In this setting, a CPU is labeled as a host and a GPU as a device. The part of the application code that executes on the CPU is called host code while the part that executes on the GPU is called device code. The memory belonging to the host and the device are referred to as host memory and device memory, respectively. The relationship between the host and the device is typically a master-slave model, where the host initializes a heterogeneous application, allocates and manages data for the device and offloads highly parallel tasks on the device along with the associated data. The next section describes the CPU-GPU heterogeneous systems in more detail.

#### 3 GPUs For General Purpose Computing

The introduction of CPU-GPU heterogeneous systems has been a major change in the landscape of HPC in the last decade. Starting from the early 2000s, graphics processing units have evolved to become programmable and highly parallel processors with tremendous computational power.

In recent years, graphics processing units (GPUs) have played a major role both in supercomputers and in personal computers to speed up compute and bandwidth intensive applications across many areas of science including engineering, medicine, finance and others. Application developers and researchers have successfully used GPUs to solve problems that demand high throughput in the field of computer vision [18, 21, 28, 32, 36, 60, 65], machine learning [1, 5, 13, 32, 36, 65], computational fluid dynamics [6, 30, 37, 38, 73], ocean geography,

seismic analysis [20, 35], signal processing [25, 45, 79], climate modeling [3, 22, 39, 40] as well as other areas. The significant speedups that have been achieved with relatively low cost GPUs has lead to a sharply increasing trend of using more GPUs in supercomputers and data centers.

In order to understand how GPUs offer high computational throughput, it is helpful to know their evolution over time and how they have developed into their current forms.

Graphics processors were originally designed to perform bitmap operations to accelerate the display for graphical operating systems. In 1992, OpenGL [63, 64] was introduced with the intention of writing 3D graphics programs using platform independent library methods [49]. But it was not until the mid-1990s that the graphics processors had the capability to process 3D graphics.

In computer graphics, various stages of computations are performed to transform three dimensional object models into pixel values that are displayed on a computer screen. These stages are collectively known as the graphics pipeline. A typical set of stages includes transformation of geometry, triangulation, fragmentation of triangles and shading of fragments. The stages of the graphics pipeline that are responsible for the transformation of geometry and the shading of fragments are called vertex shaders [41] and pixel shaders [41], respectively. The vertex shaders typically transform vertices of graphics primitives into screen space while the pixel shaders compute color and other interpolated attribute values belonging to the interior of such primitives.

Until 1997, all of the stages of the graphics pipeline, except vertex shaders, were implemented inside the CPU. However, in the late 1990s, several improvements made it possible to implement more stages inside a graphics processor. For instance, in 1999 Nvidia introduced the GeForce 256, the first GPU with the capability to perform transformation and lighting [43]. This marked the start of moving the entire graphics pipeline inside GPU hardware. One of the most significant innovations from a programmers viewpoint was the introduction of programmable vertex and pixel shaders [77] by Nvidia in the GeForce 3 GPU in 2001 [43, 53]. This gave programmers more control of the computations in their display accelerators. Along with the graphics data, programmers could send programs (i.e. a set of instructions to perform on the data) to the GPUs.

With the advent of programmable shaders [51, 57, 61, 77] it became possible to perform general purpose computations on GPUs rather than just graphics rendering. However, the process was initially a bit tricky. The programmable pixel shaders were originally designed to compute the color values and other attributes of each pixel using input information like coordinate, color, texture and so on [71]. But these input values could be any numerical data and programmers could control how the computations were performed. As the standard graphics APIs were the only ways to program GPUs, programmers had to disguise their computational problems as rendering tasks. They had to reformulate com-

putations using graphics primitives provided by APIs like OpenGL [64, 49] and DirectX [42]. Since then this trend has been known as General-Purpose computation on Graphics Processing Units (GPGPU) within the scientific community [55, 69].

By the early 2000s, different stages of the graphics pipeline were performed by fixed purpose units of the graphics processors. These hardware units were composed of several simple (i.e. without complicated control flow circuities) but independent processing elements (i.e. cores), which gave them the capability to process multiple inputs (e.g. vertices and pixels) in parallel. Since the vertices and pixels have no dependencies among them, a graphics processor used all of its independent processing elements inside a fixed purpose unit. In addition, different fixed purpose units simultaneously processed different sets of vertices and pixels.

Even though very early programmable GPUs offered significant computational power over then-existing CPUs, writing general purpose programs was much more involved. Limited input options, missing capabilities for random memory access and lack of convenient ways to debug made it difficult to program such devices. On top of this, one not only had to learn OpenGL or DirectX, knowledge of graphics-only shading language [34] was also necessary to program shaders. Altogether, these restrictions limited the popularity and use of GPUs for general purpose computations [62]. To overcome these limitations several general purpose programming languages and APIs such as Sh [69], RapidMind [44] and Brook [10] were developed.

Until 2005 display accelerators had separate hardware units for vertex shaders and pixel shaders which led to under utilization and load imbalance in many circumstances [46]. In 2005 ATI Technologies introduced a GPU-unified shader architecture on the Xenos GPU [56] used in the Xbox 360 game console [2] allowing vertices and pixels to be processed on the same hardware unit. This was subsequently adopted by ATI Technologies's TeraScale and Nvidia's Tesla family of GPU micro-architectures as well as many other display accelerator manufacturers. Along with several other architectural enhancements, GeForce 8800 GTX had capabilities to perform general computations including single precision floating point arithmetics and scatter read-write access to memory [41]. In the GPU-unified shader architectures, vertex shaders, pixel shaders and other shaders are simply multi-threaded programs running on the same hardware cores. Nvidia's GPUs with the capability of running different shaders on the same cores are known as Compute Unified Device Architecture (CUDA)-enabled GPUs.

AMD released its GPU programming system CTM (Close To Metal) in 2006 [27, 56], providing a low-level hardware abstraction layer for several ATI GPUs. Subsequently, Nvidia released the CUDA [16] parallel computing platform and programming model that enabled application developers to write programs in C to utilize the massive computational power of CUDA-enabled GPUs [41]. Since then

the field has grown dramatically and successfully attracted developers from many domains of science and engineering with its advanced and easy to use libraries and tools. The current CUDA platform also supports other popular programming languages and open programming standard for parallel computing such as OpenACC [76]. This consists of compiler directives to use accelerators such as GPUs and other many-core processors to speed up the processing of loops and other parts of source code. In recent years, higher level of abstractions and frameworks such as OpenCL [47, 67] have become popular to harness the power of GPUs as well as other types of processors.

#### 3.1 The GPU Architecture and Programming Model

Historically GPUs have been composed of independent but similar components for parallel processing of graphics rendering, with more transistors allocated to arithmetic logic units (ALUs) compared to control logic and caching circuitries. The same set of operations is performed in parallel on each data element without any dependencies among them. This is what has made GPUs into an attractive hardware platform for data parallel applications with large data sets.

In recent years, Nvidia's GPUs have had a dominant position in HPC and big data applications. For this reason we now give a more detailed presentation of their current GPU hardware and computing platform. All work in this thesis has been conducted on Nvidia GPUs using the CUDA computing platform.

Nvidia has developed families of GPU hardware targeting different systems (e.g. GeFore for personal computers, Tesla for data centers and supercomputers, Tegra for mobile and embedded devices), but the architectural features are shared among the product families to accelerate compute intensive tasks.

The Tesla product family has since its introduction undergone significant changes. The code-names for the Tesla GPU micro-architectures are Tesla (same as the product family), Fermi, Kepler, Maxwell and Pascal (in chronological order). For problems presented in this thesis, we have used Kepler and Pascal GPUs and hence we focus on architecture features of these two. To highlight the architectural improvements, we sketch some relevant comparisons.

GPUs are mainly composed of several independent components called *streaming multiprocessors* (SMs). The number and configuration of the SMs differ from GPU to GPU.

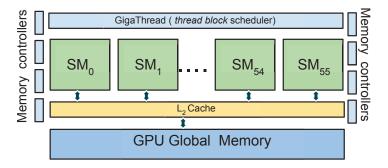

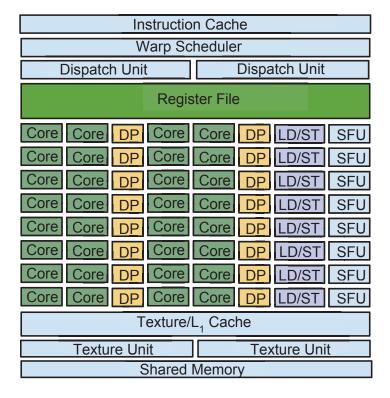

A block diagram of the Pascal GPU is shown in Figure 1. It mainly contains an array of SMs, memory controllers,  $L_2$  cache, global memory and a scheduler. Each memory controller is connected to part of the  $L_2$  cache (even though it's not shown in the figure) and is used to control global memory [15]. The configuration of a single Pascal SM is depicted in Figure 2. For clarity, only half of the SM is shown. Each SM consists of a set of cores, register file, different types of caches and other resources. Each of the cores on the SM supports single precision

Figure 1: Block diagram of a Pascal GPU

Figure 2: Block diagram of a Pascal SM

(32-bit) arithmetics. Double precision (64-bit) arithmetics are served by double precision units (DP)s while special function units (SFU)s execute intrinsic func-

tions. Load and store units (LD/ST) calculate source and destination addresses of the operands belonging to an instruction. The register file contains a set of registers.

As mentioned earlier, the CUDA programming model was developed to use the unified shader architecture for general purpose computing. It is used to program a heterogeneous system consisting of a host and one or more devices where both the host and the device has their own separate memory. In the model, the functions that are invoked from the host to be executed on the GPU are called kernels. The number of threads that execute in a kernel is specified during the kernel call. These threads are divided into thread blocks, each with a common shape. All the thread blocks belonging to a kernel call constitute a grid. Modern GPUs have the capability to run multiple grids concurrently which provides task parallelism to the programmer. As the kernels execute on device memory, the runtime of the CUDA programming model provides functions to allocate, copy and deallocate device memory. It also provides functions to transfer data between host memory and device memory [16, 52].

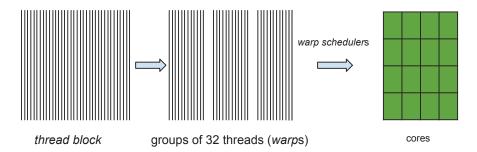

Threads are scheduled on the SMs as independent thread blocks. After a thread block has been scheduled on an SM, threads belonging to the thread block are executed in groups of 32. Such groups are called *warps*, while the hardware units that are responsible to schedule warps to cores are called *warp schedulers*. Once a warp scheduler selects a warp, instructions belonging to the warp are sent to the cores of the SM by the *dispatch units*.

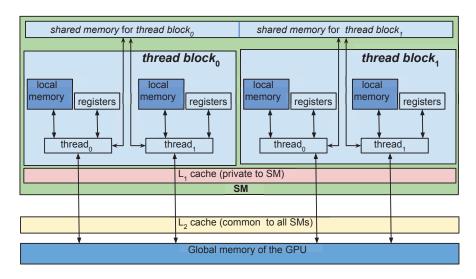

One important feature of the SMs is the programmable memory. This is fast memory that can be used by the threads as random access memory. Threads within a thread block share this memory and hence it is called *shared memory*. Both the shared memory and the register file are located on the GPU chip and are therefore called on-chip memory. In the Kepler GPU, the programmable memory is partitioned between the shared memory and  $L_1$  cache. In the Pascal GPU, there is separate memory for  $L_1$  cache that also caches texture data.

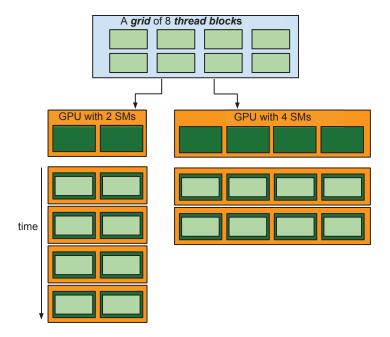

Each SM can run multiple concurrent thread blocks at the same time. A thread block is scheduled on only one SM and stays there until all the member threads of the thread block are done with the designated computations. As the thread blocks are completely independent and scheduled without any particular order, they can be scaled to a GPU with any number of SMs. The scalability of GPUs with varying number of SMs is shown in Figure 3. In the figure, two possible scenarios for the execution of a grid consisting of eight thread blocks is shown, when the grid is executed on a GPU with 2 SMs and on a GPU with 4 SMs. It is assumed that only one thread block can fit on an SM at a time and each of the thread blocks takes the same amount of time to execute. The execution time on a GPU with 4 SMs is then half the time of that on a GPU with 2 SMs.

Once a thread block is scheduled on an SM, on-chip resources such as registers

Figure 3: Scalability of CUDA program

and shared memory from the SM are allocated to it. A warp scheduler on the SM selects a warp when there are at least 32 idle cores on the SM and all the arguments to the current instruction to be executed are ready [12, 52]. The logical view of execution flow for a thread block is shown in Figure 4 where the thread block is divided into groups of 32 threads before being scheduled by the warp schedulers to the cores. If a warp is not ready (e.g. waiting for data), it is put into a stall state and other warps gets the opportunity to use the cores. One important point to note is that threads belonging to a stalled warp does not release their on-chip resources until the end of execution. This makes context switching faster than in traditional multi-threaded programming.

The threads within a *warp* execute the same instruction at the same time in a SIMD fashion, but each thread can have an independent execution path using a private instruction address counter [12, 41, 52].

The memory hierarchy of the CUDA programming model is shown in Figure 5. Only one SM with two concurrent thread blocks, each with two threads is shown in the figure. Registers are allocated per thread while shared memory is allocated to an entire thread block. The amount of registers and shared memory on the SM limits how many concurrent thread blocks and warps can run on it. Automatic variables and arrays that are indexed with constant expressions are

Figure 4: Mapping of a thread block to physical cores

eligible to be stored in registers. If a thread needs more registers than what is allocated to it, the corresponding data will be stored as private memory of the thread in the global memory of the GPU. This is referred to as *local memory* of the thread. Large private arrays and automatic variables that don't fit in registers are allocated in the local memory.

The amount of shared memory requested by thread blocks is specified during the kernel call. In the CUDA programming model, this amount has to be the same for all thread blocks. Based on the requested amount, the on-chip shared memory of an SM is partitioned among the active thread blocks on the SM [52]. The shared memory of a thread block can be logically divided to its warps or to its threads. If a thread block of a program needs more shared memory than what is available in an SM, the program cannot run on the GPU. Threads within a thread block can cooperate by sharing data in the shared memory. Access to shared memory must be synchronized to avoid race conditions, something which the CUDA API has support for. It is important to note that threads within a thread block can be synchronized but there is no mechanism for inter-thread block synchronization.

The largest and slowest memory of a GPU is the global memory. Each and every thread belonging to any thread block has access to the global memory. Global memory is normally used to store application data and results. As shown in Figure 5, each SM has its private  $L_1$  cache while all SMs inside a GPU share  $L_2$  cache. Memory loads from the global memory are cached while memory stores are not [12]. For simplicity, other forms of memory like texture memory and constant cache have been omitted from the figure.

When the threads in a warp are mapped to the cores of an SM, they can share data between themselves using separate store and load operations in shared memory. Starting from Kepler, subsequent GPUs implement shuffle instructions that makes it possible for the threads within a warp to share data without going through shared memory. The shuffle instructions enable a thread to read from any other thread in the same warp. We found this instruction to be quite useful

Figure 5: The memory hierarchy on the Pascal GPU

in many of our implementations. A typical scenario would be when each thread within a warp had a separate value that needs to be reduced to a single value using an operator such as sum or min. The use of shuffle instructions helps to reduce the amount of shared memory required per thread and offers improved performance as store-and-load operations are carried out in a single step [15]. When multiple warps inside a thread block are involved in a reduction, the threads inside each warp of the thread block can use shuffle instructions to find a local reduced value and then write this to the shared memory of the thread block. Finally, the values written by the warps can be reduced to a single value.

Atomic operations are important for concurrent programming where multiple threads read and write shared data structures without any predefined order. To ensure a correct result, it is essential that the modification of the same memory location by multiple threads does not lead to different outcomes depending on the order in which these operations are carried out. Fermi and Kepler supports atomic operations that are implemented using a lock-update-unlock pattern while Maxwell and Pascal come with native hardware support for shared memory atomics [15]. Atomic operations are supported both in global and shared memory. For our implementations we used atomic-compare-and-swap (atomicCAS) and atomic add.

Multiple independent SMs inside a GPU, multiple thread blocks inside an SM and multiple threads inside a thread block- this kind of hierarchy directs to split a computational problem into coarse-grained and independent sub-problems that

can be processed in parallel by thread blocks, and each such sub-problem into fine-grained parts that can be processed in coordination by all threads within a thread block [16, 52]. All together, a high number of cores and hardware level parallelism by the means of independent SM units enables modern GPUs to achieve computational throughput for data parallel applications that is competitive compared to traditional shared memory and distributed memory multiprocessors.

Parallel computing systems containing multiple GPUs is already a common trend in HPC. The current way of designing multi-GPU systems is either to have separate GPUs with the same host or to have multiple hosts, each with their own GPU(s) with communication between the hosts handled using MPI. In 2016, Nvidia released their DGX-1 server, a standalone computing node that uses 8 Pascal GPUs connected via fast interconnections to provide up to 85 Tera flops in single precision. This has successfully been used in machine learning and computer vision to reduce the training time to build neural networks [1, 24, 15, 72]. The advantage of the training process is that it mainly involves matrix-vector multiplications and computation of intrinsic functions, something which the GPU architecture has support for.

#### 4 Generic Graph Analytics on GPUs

There has been a substantial effort to develop graph algorithms for GPUs. This has mostly been done for systems with only one GPU, but also for multi-GPU systems. Popular problems that have been studied include breadth-first search (BFS), single-source shortest path (SSSP), betweenness centrality (BC), PageRank (PR) and connected components (CC). Common to all of these is that they can be implemented as some type of graph traversal. When performing a graph traversal there are some common operations that are needed.

- Advance Move from one set of vertices to their neighbors.

- Filtering Remove specific elements from a set of vertices or edges based on some condition.

- Compute A compute operator defines an operation on all vertices or edges in the current input frontier.

As these operations occur in many graph algorithms there has been several efforts to develop generic packages that implement these on GPUs. The intention is then that it will become easier to construct new graph algorithms on GPUs. Medusa was one of the first such generic systems for operating on graphs [80]. It has been tried on PR, BFS, SSSP and maximal bipartite matching. This system can use multiple GPUs connected to the same host. When using multiple GPUs it is advisable to use some kind of graph partitioning software to reduce

the amount of inter GPU communication. Gunrock is a more recent library for developing graph algorithms on a single GPU [75]. This uses a bulk synchronous programming model (BSP) where one performs iterative computational steps interleaved with communication. This has been tried on BFS, SSSP, BC, PR, CC and triangle counting. The BSP model requires synchronization between the computational steps something that might cause threads to idle. To overcome this, the Groute system was developed to support an asynchronous multi-GPU programming environment [4]. In this system the user first sets up a dataflow graph that defines how data is to be moved between the computational devices. During execution the system will then transfer data between these as directed by this graph. Experiments on BFS, SSSP, PR and CC show that it scales on some instances when using up to 8 GPUs connected to a single host. Finally we note the GBTL-CUDA package [78]. This is part of the GraphBLAS effort that aims to reformulate graph problems in the language of linear algebra [33]. It has so far been used to implement BFS and SSSP on a single GPU. This work is a proof of concept that has not yet been optimized for speed.

We note that the algorithms considered in the papers of this thesis do not follow the graph traversal style of programming. One common operation in the considered matching and marriage algorithms is to repeatedly find the current best neighbor for every vertex to match with using a reduction operation. In our work on community detection we also perform a reduction operation on the neighbors of each vertex. But here the neighbors are first reduced to multiple values depending on which community they belong to and then from the set of neighboring communities we pick the best one. It is also important for performance that these operations can be done in an asynchronous fashion while still achieving a deterministic result. Although it might have been possible to implement some of the operations in our algorithms using existing packages, we do not believe that this would have resulted in efficient algorithms.

#### 5 Conclusion

The main focus of this thesis is on developing efficient algorithms on GPUs for certain matching and clustering problems. Through extensive experiments we show that sparse and unstructured problems can benefit greatly from using GPUs as long as the algorithms are carefully designed. Even though none of the presented algorithms are fundamentally new, they still require significant redesign to make them efficient on GPUs. Common to all the developed algorithms is that they emphasis achieving an even load balance and high degree of parallelism, while at the same time avoiding the use of time consuming synchronization operations. Through extensive experiments we verify the performance of the suggested algorithms. In some cases, even a single GPU can outperform tens of multiprocessors

on a state-of-the-art supercomputer.

The area of computing using GPU enhanced systems is changing rapidly. This is especially true for memory management. For instance, simultaneous access to the same memory by a host and a device was not possible until it was recently introduced in the Pascal GPU [15]. However, starting from the early unified shader architecture, the fundamental architectural features of GPUs have not undergone radical changes. Instead what has happened is that features have been added in an incremental fashion while the speed and size of the device has increased gradually. Based on this observation we believe that algorithms that are developed for GPUs today will also be relevant in the near future.

Although the presented algorithms in this thesis can be viewed as proof of concept that carefully designed GPU algorithms for certain graph problems can compete with implementations on traditional parallel supercomputers, it is not to be underestimated that doing so requires substantial effort. For this to become possible on a more regular basis there is a need to continue and further develop higher level abstractions for graph analytics on GPUs. As an example, we believe that the strategy used in Paper III where vertices were grouped according to their degree before being allocated to different thread blocks, is one such technique that could benefit other applications. Also, the use of various reduction operations could be candidates for generic implementation.

It seems clear that GPUs will play a major role in the future of HPC, with large systems containing several interconnected ones. Designing efficient graph algorithms for such systems is still only starting and likely to generate much interesting work in the future. Just like the distinction between traditional shared and distributed algorithms, we believe that one will see a similar division between different GPU algorithms depending on how the underlying devices are interconnected.

## **Bibliography**

- [1] Martín Abadi et al. "Tensorflow: Large-scale machine learning on heterogeneous distributed systems". In: arXiv preprint arXiv:1603.04467 (2016).

- [2] Jeff Andrews and Nick Baker. "Xbox 360 system architecture". In: IEEE micro 26.2 (2006), pp. 25–37.

- [3] Richard Archibald, KJ Evans, and A Salinger. "Accelerating time integration for climate modeling using GPUs". In: *Procedia Computer Science*, (same volume) (2015).

- [4] Tal Ben-Nun et al. "Groute: An asynchronous multi-GPU programming model for irregular computations". In: *Proceedings of the 22nd ACM SIG-PLAN Symposium on Principles and Practice of Parallel Programming*. ACM. 2017, pp. 235–248.

- [5] James Bergstra et al. "Theano: A CPU and GPU math compiler in Python". In: *Proc. 9th Python in Science Conf.* 2010, pp. 1–7.

- [6] Massimo Bernaschi et al. "A flexible high-performance Lattice Boltzmann GPU code for the simulations of fluid flows in complex geometries". In: Concurrency and Computation: Practice and Experience 22.1 (2010), pp. 1–14.

- [7] Vincent D Blondel et al. "Fast unfolding of communities in large networks". In: Journal of statistical mechanics: theory and experiment 2008.10 (2008), P10008.

- [8] Erik G Boman et al. "The Zoltan and Isorropia parallel toolkits for combinatorial scientific computing: Partitioning, ordering and coloring". In: *Scientific Programming* 20.2 (2012), pp. 129–150.

- [9] Andre R Brodtkorb et al. "State-of-the-art in heterogeneous computing". In: *Scientific Programming* 18.1 (2010), pp. 1–33.

- [10] Ian Buck et al. "Brook for GPUs: stream computing on graphics hardware". In: ACM Transactions on Graphics (TOG). Vol. 23. 3. ACM. 2004, pp. 777–786.

- [11] Shuai Che et al. "Rodinia: A benchmark suite for heterogeneous computing". In: Workload Characterization, 2009. IISWC 2009. IEEE International Symposium on. Ieee. 2009, pp. 44–54.

- [12] John Cheng, Max Grossman, and Ty McKercher. *Professional Cuda C Programming*. John Wiley & Sons, 2014.

- [13] Ronan Collobert, Koray Kavukcuoglu, and Clément Farabet. "Torch7: A matlab-like environment for machine learning". In: *BigLearn, NIPS Workshop*. EPFL-CONF-192376. 2011.

- [14] Combinatorial Scientific Computing: Tutorial, Experiences, and Challenges. URL: https://web.stanford.edu/group/mmds/slides2010/Gilbert.pdf.

- [15] NVIDIA Corporation. NVIDIA Tesla P100 GP100 Pascal Whitepaper. Tech. rep. 2016.

- [16] CUDA C Programming Guide. URL: http://docs.nvidia.com/cuda/cuda-c-programming-guide.

- [17] Leonardo Dagum and Ramesh Menon. "OpenMP: an industry standard API for shared-memory programming". In: *IEEE computational science* and engineering 5.1 (1998), pp. 46–55.

- [18] Jean-Philippe Farrugia et al. "GPUCV: A framework for image processing acceleration with graphics processors". In: *Multimedia and Expo, 2006 IEEE International Conference on.* IEEE. 2006, pp. 585–588.

- [19] Haohuan Fu et al. "The Sunway TaihuLight supercomputer: system and applications". In: Science China Information Sciences 59.7 (2016), p. 072001.

ISSN: 1869-1919. DOI: 10.1007/s11432-016-5588-7. URL: http://dx.doi.org/10.1007/s11432-016-5588-7.

- [20] Xiaodong Fu et al. "Investigation of highly efficient algorithms for solving linear equations in the discontinuous deformation analysis method". In: International Journal for Numerical and Analytical Methods in Geomechanics 40.4 (2016), pp. 469–486.

- [21] James Fung and Steve Mann. "OpenVIDIA: parallel GPU computer vision". In: Proceedings of the 13th annual ACM international conference on Multimedia. ACM. 2005, pp. 849–852.

- [22] Mark Govett et al. "Parallelization and Performance of the NIM Weather Model for CPU, GPU and MIC Processors". In: (2016).

- [23] William Gropp et al. "A high-performance, portable implementation of the MPI message passing interface standard". In: *Parallel computing* 22.6 (1996), pp. 789–828.

- [24] Song Han et al. "Dsd: Regularizing deep neural networks with dense-sparse-dense training flow". In: arXiv preprint arXiv:1607.04381 (2016).

- [25] Awni Hannun et al. "Deep speech: Scaling up end-to-end speech recognition". In: arXiv preprint arXiv:1412.5567 (2014).

- [26] John L Henning. "SPEC CPU2000: Measuring CPU performance in the new millennium". In: *Computer* 33.7 (2000), pp. 28–35.

- [27] Justin Hensley. "Amd ctm overview". In: ACM SIGGRAPH 2007 courses. ACM. 2007, p. 7.

- [28] S Heymann et al. "SIFT implementation and optimization for general-purpose GPU". In: (2007).

- [29] Francisco D Igual et al. "Unleashing the high-performance and low-power of multi-core DSPs for general-purpose HPC". In: *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis.* IEEE Computer Society Press. 2012, p. 26.

- [30] Dana Jacobsen, Julien Thibault, and Inanc Senocak. "An MPI-CUDA implementation for massively parallel incompressible flow computations on multi-GPU clusters". In: 48th AIAA Aerospace Sciences Meeting Including the New Horizons Forum and Aerospace Exposition. 2010, p. 522.

- [31] James Jeffers and James Reinders. Intel Xeon Phi coprocessor high-performance programming. Newnes, 2013.

- [32] Yangqing Jia et al. "Caffe: Convolutional architecture for fast feature embedding". In: *Proceedings of the 22nd ACM international conference on Multimedia*. ACM. 2014, pp. 675–678.

- [33] Jeremy Kepner et al. "Graphs, matrices, and the GraphBLAS: Seven good reasons". In: *Procedia Computer Science* 51 (2015), pp. 2453–2462.

- [34] John Kessenich, Dave Baldwin, and Randi Rost. "The opengl shading language". In: *Language version* 1 (2004).

- [35] Dimitri Komatitsch et al. "High-order finite-element seismic wave propagation modeling with MPI on a large GPU cluster". In: *Journal of computational physics* 229.20 (2010), pp. 7692–7714.

- [36] Alex Krizhevsky, Ilya Sutskever, and Geoffrey E Hinton. "ImageNet Classification with Deep Convolutional Neural Networks". In: Advances in Neural Information Processing Systems 25. Ed. by F. Pereira et al. Curran Associates, Inc., 2012, pp. 1097-1105. URL: http://papers.nips.cc/paper/4824-imagenet-classification-with-deep-convolutional-neural-networks.pdf.

- [37] Frédéric Kuznik et al. "LBM based flow simulation using GPU computing processor". In: *Computers & Mathematics with Applications* 59.7 (2010), pp. 2380–2392.

- [38] Hyungdo Lee et al. "Acceleration of Computational Fluid Dynamics Analysis by using Multiple GPUs". In: Proceedings of the International Conference on Bioinformatics & Computational Biology (BIOCOMP). The Steering Committee of The World Congress in Computer Science, Computer Engineering and Applied Computing (WorldComp). 2016, p. 103.

- [39] David Leutwyler et al. "Towards Cloud-Resolving European-Scale Climate Simulations using a fully GPU-enabled Prototype of the COSMO Regional Model". In: EGU General Assembly Conference Abstracts. Vol. 16. 2014, p. 11914.

- [40] David Leutwyler et al. "Towards European-scale convection-resolving climate simulations with GPUs: a study with COSMO 4.19". In: Geoscientific Model Development 9.9 (2016), p. 3393.

- [41] Erik Lindholm et al. "NVIDIA Tesla: A unified graphics and computing architecture". In: *IEEE micro* 28.2 (2008).

- [42] Michael Macedonia. "The GPU enters computing's mainstream". In: Computer 36.10 (2003), pp. 106–108.

- [43] Chris McClanahan. "History and evolution of gpu architecture". In: A Survey Paper (2010), p. 9.

- [44] Michael D McCool and Bruce D'Amora. "Programming using RapidMind on the Cell BE". In: Proceedings of the 2006 ACM/IEEE conference on Supercomputing. ACM. 2006, p. 222.

- [45] Yajie Miao, Mohammad Gowayyed, and Florian Metze. "EESEN: End-to-end speech recognition using deep RNN models and WFST-based decoding". In: Automatic Speech Recognition and Understanding (ASRU), 2015 IEEE Workshop on. IEEE. 2015, pp. 167–174.

- [46] S. Morein et al. Graphics processing architecture employing a unified shader. US Patent 6,897,871. 2005. URL: https://www.google.com/patents/US6897871.

- [47] Aaftab Munshi. "The opencl specification". In: Hot Chips 21 Symposium (HCS), 2009 IEEE. IEEE. 2009, pp. 1–314.

- [48] Uwe Naumann and Olaf Schenk. Combinatorial scientific computing. CRC Press, 2012.

- [49] Jackie Neider, Tom Davis, and Mason Woo. OpenGL programming guide. 1993.

- [50] Chris J Newburn et al. "Offload Compiler Runtime for the Intel® Xeon Phi Coprocessor". In: Parallel and Distributed Processing Symposium Workshops & PhD Forum (IPDPSW), 2013 IEEE 27th International. IEEE. 2013, pp. 1213–1225.

- [51] John Nickolls and William J Dally. "The GPU computing era". In: IEEE micro 30.2 (2010).

- [52] John Nickolls et al. "Scalable parallel programming with CUDA". In: *Queue* 6.2 (2008), pp. 40–53.

- [53] NVIDIA GeForce3 Graphics Cards. URL: http://www.nvidia.com/page/geforce3.html.

- [54] NVIDIA NVLINK HIGH-SPEED INTERCONNECT. URL: http://www.nvidia.com/object/nvlink.html.

- [55] John D Owens et al. "A survey of general-purpose computation on graphics hardware". In: *Computer graphics forum*. Vol. 26. 1. Wiley Online Library. 2007, pp. 80–113.

- [56] John D Owens et al. "GPU computing". In: *Proceedings of the IEEE* 96.5 (2008), pp. 879–899.

- [57] Matthew N Papakipos et al. System, method and article of manufacture for pixel shaders for programmable shading. US Patent 6,532,013. 2003.

- [58] Alex Pothen et al. "Combinatorial algorithms for petascale science". In: (2007).

- [59] Power 4

The First Multi-Core, 1GHz Processor. URL: http://www-03.ibm.com/ibm/history/ibm100/us/en/icons/power4/.

- [60] Kari Pulli et al. "Real-time computer vision with OpenCV". In: Communications of the ACM 55.6 (2012), pp. 61–69.

- [61] Timothy J Purcell et al. "Ray tracing on programmable graphics hardware". In: ACM Transactions on Graphics (TOG). Vol. 21. 3. ACM. 2002, pp. 703–712.

- [62] Jason Sanders and Edward Kandrot. CUDA by Example: An Introduction to General-Purpose GPU Programming, Portable Documents. Addison-Wesley Professional, 2010.

- [63] Mark Segal and Kurt Akeley. "The OpenGL Graphics System: A Specification. Silicon Graphics". In: *Inc.* (30 jul 2006) (1992).

- [64] Mark Segal and Kurt Akeley. The OpenGL graphics system: A specification (version 1.1). 1999.

- [65] Karen Simonyan and Andrew Zisserman. "Very deep convolutional networks for large-scale image recognition". In: arXiv preprint arXiv:1409.1556 (2014).

- [66] Marc Snir. MPI-the Complete Reference: The MPI core. Vol. 1. MIT press, 1998.

- [67] John E Stone, David Gohara, and Guochun Shi. "OpenCL: A parallel programming standard for heterogeneous computing systems". In: *Computing in science & engineering* 12.3 (2010), pp. 66–73.

- [68] Herb Sutter. "The free lunch is over: A fundamental turn toward concurrency in software". In: *Dr. Dobbs journal* 30.3 (2005), pp. 202–210.

- [69] David Tarditi, Sidd Puri, and Jose Oglesby. "Accelerator: using data parallelism to program GPUs for general-purpose uses". In: ACM SIGARCH Computer Architecture News. Vol. 34. 5. ACM. 2006, pp. 325–335.

- [70] Joel M Tendler et al. "POWER4 system microarchitecture". In: *IBM Journal of Research and Development* 46.1 (2002), pp. 5–25.

- [71] Chris J Thompson, Sahngyun Hahn, and Mark Oskin. "Using modern graphics architectures for general-purpose computing: a framework and analysis". In: Microarchitecture, 2002. (MICRO-35). Proceedings. 35th Annual IEEE/ACM International Symposium on. IEEE. 2002, pp. 306–317.

- [72] Yong-hong Tian et al. "Towards human-like and transhuman perception in AI 2.0: a review". In: Front. Inform. Technol. Electron. Eng 18.1 (2017), pp. 58–67.

- [73] Jonas Tölke and Manfred Krafczyk. "TeraFLOP computing on a desktop PC with GPUs for 3D CFD". In: *International Journal of Computational Fluid Dynamics* 22.7 (2008), pp. 443–456.

- [74] TOP 500 The List. URL: htm://www.top500.org/.

- [75] Yangzihao Wang et al. "Gunrock: A high-performance graph processing library on the GPU". In: *Proceedings of the 21st ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming*. ACM. 2016, p. 11.

- [76] Sandra Wienke et al. "OpenACCfirst experiences with real-world applications". In: European Conference on Parallel Processing. Springer. 2012, pp. 859–870.

- [77] Harold Robert Feldman Zatz, Henry P Moreton, and John Erik Lindholm. Programmable pixel shading architecture. US Patent 6,724,394. 2004.

- [78] P. Zhang et al. "GBTL-CUDA: Graph Algorithms and Primitives for GPUs".

In: 2016 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW). 2016, pp. 912–920. DOI: 10.1109/IPDPSW.2016.

185.

- [79] Xiaohui Zhang et al. "Improving deep neural network acoustic models using generalized maxout networks". In: Acoustics, Speech and Signal Processing (ICASSP), 2014 IEEE International Conference on. IEEE. 2014, pp. 215–219.

- [80] Jianlong Zhong and Bingsheng He. "Medusa: Simplified graph processing on GPUs". In: *IEEE Transactions on Parallel and Distributed Systems* 25.6 (2014), pp. 1543–1552.

# Optimizing Approximate Weighted Matching on Nvidia Kepler K40

Md. Naim, Fredrik Manne\*,

Mahantesh Halappanavar, Antonino Tumeo\*\*

and Johannes Langguth\*\*\*

#### Abstract

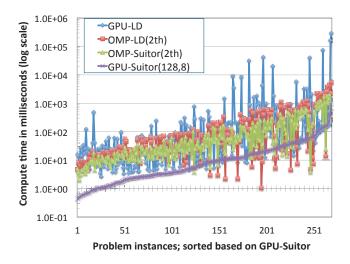

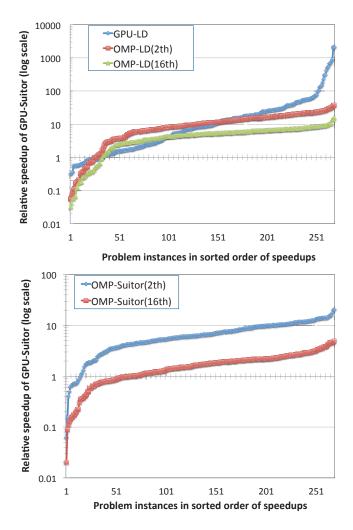

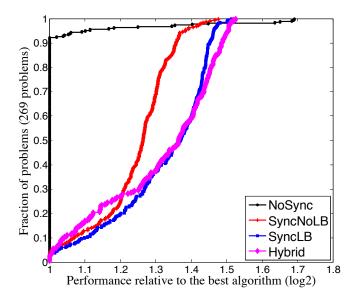

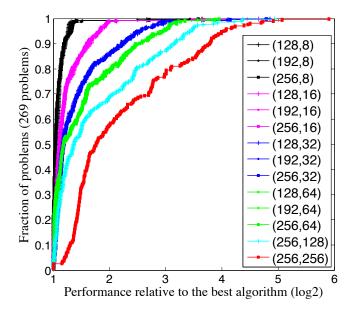

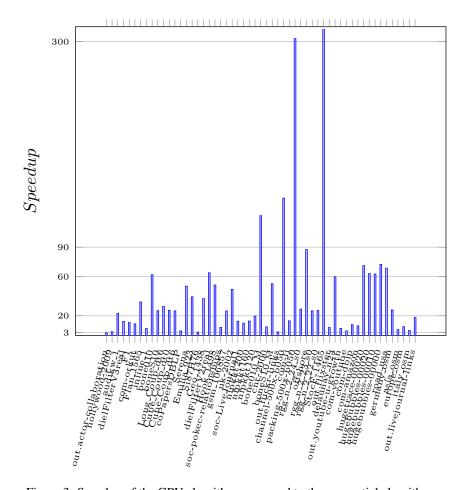

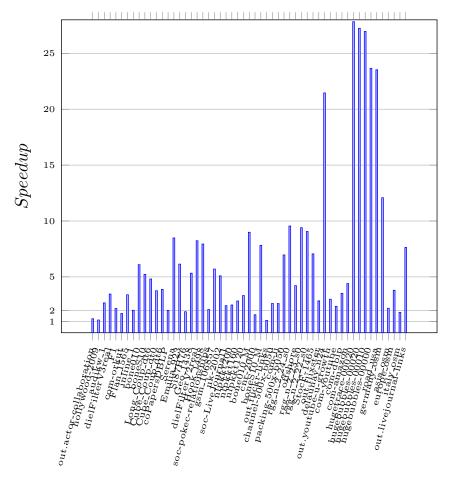

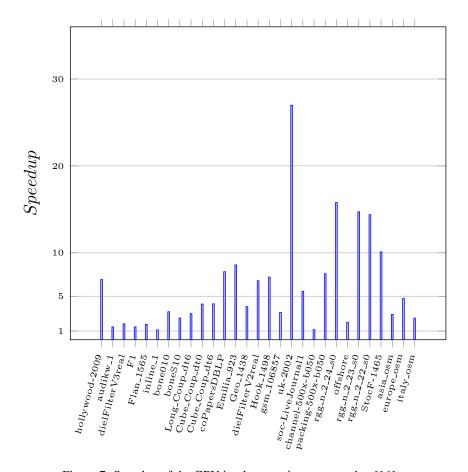

Matching is a fundamental graph problem with numerous applications in science and engineering. While algorithms for computing optimal matchings are difficult to parallelize, approximation algorithms on the other hand generally compute high quality solutions and are amenable to parallelization. In this paper, we present efficient implementations of the current best algorithm for half-approximate weighted matching, the Suitor algorithm, on Nvidia Kepler K-40 platform. We develop four variants of the algorithm that exploit hardware features to address key challenges for a GPU implementation. We also experiment with different combinations of work assigned to a warp. Using an exhaustive set of 269 inputs, we demonstrate that the new implementation outperforms the previous best GPU algorithm by 10 to  $100\times$  for over 100 instances, and from 100 to  $1000\times$ for 15 instances. We also demonstrate up to 20× speedup relative to 2 threads, and up to 5× relative to 16 threads on Intel Xeon platform with 16 cores for the same algorithm. The new algorithms and implementations provided in this paper will have a direct impact on several applications that repeatedly use matching as a key compute kernel. Further, algorithm designs and insights provided in this paper will benefit other researchers implementing graph algorithms on modern GPU architectures.

<sup>\*</sup>Department of Informatics, University of Bergen, N-5020 Bergen, Norway. Email: {md.naim, fredrikm}@ii.uib.no

<sup>\*\*</sup>Pacific Northwest National Laboratory, 902 Battelle Boulevard, P.O.Box 999, MSIN J4-30, Richland, WA 99352, USA.

$Email: \{mahantesh.halappanavar,\,antonino.tumeo\}@pnnl.gov$

<sup>\*\*\*</sup>High performance computing, Simula Research Laboratory, Oslo, Norway. Email: langguth@simula.no

## 1 Introduction

Given a graph G=(V,E) with vertex set V, edge set E and a weight function  $w:E\to\mathbf{R}^+$ , a matching M is a subset of edges such that no two edges in M are incident on the same vertex. A maximum matching maximizes the number of matched edges (cardinality) in M. The objective for a maximum weighted matching is to maximize the sum of the weights of the matched edges. Further, the solutions can be optimal or approximate. In this paper, we only consider half-approximate weighted matching algorithms that guarantee a solution that is at least half of an optimal solution in terms of the cardinality and weight of the matching. We present and compare two main algorithms, Locally-Dominant and Suitor, on two types of architectures, CPUs and GPUs. We also study four variants of the Suitor algorithm on GPUs. The algorithms are listed in Table 1, and are described in Sections 2 and 4.

Table 1: A list of matching algorithms and variants presented and studied in this paper.

| Algorithm           | Description                                     |  |  |  |

|---------------------|-------------------------------------------------|--|--|--|

| OMP-LD              | Active vertices are stored in a shared queue.   |  |  |  |

|                     | Presented in Algorithm 1.                       |  |  |  |

| OMP-Suitor          | Uses locks for synchronization. Presented in    |  |  |  |

|                     | Algorithm 3.                                    |  |  |  |

| GPU-LD              | Thread-per-vertex based implementation of       |  |  |  |

|                     | OMP-LD.                                         |  |  |  |

| GPU-Suitor          | Warp-based implementation of OMP-Suitor.        |  |  |  |

|                     | Synchronization and load balancing are not      |  |  |  |

|                     | used. Presented in Algorithm 4.                 |  |  |  |

| GPU-Suitor-SyncLB   | Synchronization and load balancing employed     |  |  |  |

|                     | among participating warps.                      |  |  |  |

| GPU-Suitor-SyncNoLB | Synchronization, but no load balancing among    |  |  |  |

|                     | warps.                                          |  |  |  |

| GPU-Suitor-Hybrid   | Synchronize and load balance only for the first |  |  |  |

|                     | few iterations of the Suitor algorithm.         |  |  |  |

Matching is a fundamental combinatorial problem with many applications in scientific computing, optimization and data analytics. In scientific computing, matchings are used in the solution of sparse linear systems to place large matrix elements on or close to the diagonal [4]; computation of sparse basis for the null space or column space of under-determined matrices [16]; computation of block-triangular form of a matrix [17]. Approximate weighted matchings are used in multi-level graph algorithms for partitioning and clustering during the coarsening

phase [10]; network alignment [11] and community detection [18]. These applications drive the need for efficient parallel implementations of matching algorithms on emerging multicore and manycore architectures. Many of these applications repeatedly compute matchings several hundreds of times during their execution. Therefore, small improvements in matching performance can lead to large gains in the performance of these applications [11].

An important class of manycore architectures are general purpose graphics programming units (GP-GPUs, or simply GPUs) that are not only powerful but also ubiquitous. The Nvidia Kepler K40 presented in Section 3 is currently one of the best manycore platforms for scientific computing. While many significant performance gains for compute intensive applications with regular and predictable memory access patterns have been demonstrated using GPUs, the efficient implementation of irregular applications such as graph algorithms remains a challenge [21]. Highly irregular degree distributions, poor locality in memory accesses, and minimal computation on accessed data make efficient utilization of compute resources challenging. Using approximate weighted matching as a case study for irregular applications, we introduce several algorithmic ideas that can also be adapted for other graph algorithms.

### 1.1 Contributions

We make the following contributions in this paper:

- Develop new parallel implementations of a weighted matching algorithm (GPU-Suitor) on the Nvidia Kepler architecture. We present four variants of the algorithm and several combinations of threads-per-block and verticesper-warp.

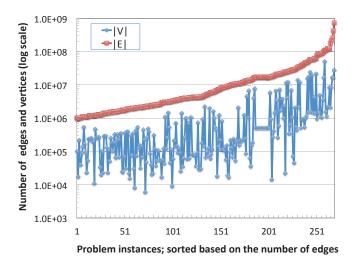

- Present detailed experimental results using 269 test cases representing diverse applications and sparsity patterns (graph structures).

- Demonstrate the superiority of our algorithms over the previous best algorithm (GPU-LD) on GPUs [7], as well as shared-memory (OpenMP) implementations. We show that the new implementation outperforms GPU-LD by 10 to 100× for over 100 instances, and by 100 to 1000× for 15 instances. We also demonstrate up to 20× speedup relative to 2 threads, and up to 20× relative to 16 threads on Intel Xeon platform with 16 cores for the same algorithm.

We organize the presentation in this paper as follows. We first present multithreaded matching algorithms targeting shared-memory architectures in Section 2. The Nvidia Kepler K40 is introduced in Section 3, followed by a discussion on the key challenges and our approaches to overcome them. GPU-Suitor, along with its four variants, are presented in Section 4. Experimental results and

analysis are presented in Section 5, followed by a discussion of related work in Section 6, and our conclusions in Section 7.

## 2 Parallel Weighted Matching

Matching is a classical topic in combinatorial optimization and has been studied extensively [12, 19, 15]. While many variants of the problem exist, we focus on approximate weighted matching for general graphs. In particular, we focus on the work of Halappanavar et al. on the Locally-Dominant Algorithm [7], and the work of Manne and Halappanavar on the Suitor Algorithm [13]. Their work itself was built on the pioneering work of many other researchers in the area, whose parallel algorithms systematically evolved from efficient serial algorithms. Due to space restrictions, we only present these two approximation algorithms in this section. We refer you to the respective papers for details.

### 2.1 The Locally-Dominant (LD) Algorithm

A half-approx weighted matching can be simply computed by considering the edges in a non-increasing order of weights, and by adding all edges that do not violate the matching condition. However, such an approach imposes a serial order on execution. Therefore, the main idea of the LD Algorithm is to identify and match locally-dominant edges in parallel. An edge that is heavier than all the edges incident on its end points is called a locally-dominant edge. Algorithm 1 implements this approach. It takes a graph G = (V, E) as input and returns a matching M as output. The algorithm starts by making a call to Procedure Pro-CESSVERTEX(v) for each vertex (Lines 6 and 7). In Procedure ProcessVertex, for a given vertex, all its neighbors are scanned to find the current heaviest neighbor that has not been matched already. It is important to break ties (duplicate weight) consistently to prevent deadlocks. For this purpose we use vertex indices, which are guaranteed to be unique (Line 5). The identity of the heaviest neighbor for each vertex is then stored in a vector (candidate). After setting the candidate mate for vertex s, say to vertex t, we check if the candidate mate for t is also set to s: candidate[candidate[s]] = s (Line 9). If this is true, we have found a locallydominant edge  $e_{s,t}$ . We add this edge to M, and the two vertices s and t to the queue (Line 12). Some of the vertices might end up not having any candidates available to match with.

The second part of the execution begins when every vertex has been processed and matched vertices have been added to the queue  $Q_C$ . In this part, we iterate until the queue becomes empty (Line 8 in Algorithm 1). Note that at least one edge (the heaviest edge) would get matched in the first loop, and therefore,  $Q_C$  is nonempty if M is nonempty. During each iteration of the **while** loop on Line 8,

Algorithm 1 Parallel Locally-Dominant Algorithm. Input: graph G = (V, E). Output: A matching M represented in vector mate. Data structures: a queue,  $Q_C$ , listing vertices for processing in current step, and a queue,  $Q_N$ , listing vertices to be processed in the next step – both the queues list matched vertices; a vector candidate of size |V| that contains the id of the current heaviest neighbor of each vertex.

```

1: procedure LOCALLY-DOMINANT(G(V, E), mate)

for each v \in V in parallel do

2:

\mathsf{mate}[v] \leftarrow \emptyset

3:

candidate[v] \leftarrow \emptyset

4:

Q_C \leftarrow \emptyset; Q_N \leftarrow \emptyset

5:

for each v \in V in parallel do

6:

7:

ProcessVertex(v, Q_C)

while Q_C \neq \emptyset do

8:

for each u \in Q_C in parallel do

9:

10:

for each v \in adj(u) do

if candidate[v] = u then

11:

ProcessVertex(v, Q_N)

12:

13:

SWAP(Q_C, Q_N)

```

#### Algorithm 2 ProcessVertex

```

1: procedure ProcessVertex(s, Q)

2:

\max_{w} t \leftarrow -\infty

\max_{\text{wt\_id}} \leftarrow \emptyset

3:

for each t \in adj(s) do

4:

if (mate[t] = \emptyset) AND (max_wt < w(e_{s,t})) then

5:

\max_{w} t \leftarrow w(e_{s,t})

6:

7:

\max_{\text{wt\_id}} \leftarrow t

8:

candidate[s] \leftarrow max\_wt\_id

if candidate[candidate[s]] = s then

9:

\mathsf{mate}[s] \leftarrow \mathsf{candidate}[s]

10:

\mathsf{mate}[\mathsf{candidate}[s]] \leftarrow s

11:

12:

Q \leftarrow Q \cup \{s, \text{ candidate}[s]\}

```

we process vertices matched in the previous iterations while adding new vertices to the queue  $Q_N$  that become eligible as edges get matched. Note that we only need to process vertices for which the **candidate** was set to one of the matched vertices (Line 12). This is achieved by adding the newly matched vertices to the queue and checking if any of their unmatched neighbors point to them. If so, those neighbors will have to find new candidates for matching. The algorithm will terminate when the queue becomes empty. The matching is stored in a vector, mate.

The running time of Algorithm 1 is given by  $O(|V| + |E|\Delta)$ , where  $\Delta$  is the

maximum degree in G. The worst case happens when a vertex points to all of its neighbors unsuccessfully, and in order to determine the current heaviest neighbor it needs to check the entire list. However, the runtime can be improved to  $\Theta(|V|+|E|)$  if the adjacency list for each vertex is provided in a non-increasing order of edge weights. Under this assumption, the current heaviest neighbor of a vertex can be computed in constant time. The amount of parallelism is determined by the number of vertices in  $Q_C$  during each iteration of the **while** loop (Line 8). We use the compressed row storage format (CSR) for storing graphs in memory and therefore benefit from caching effects on adjacency lists on platforms with cache hierarchies. On the x86 platforms we use an intrinsic atomic operation  $\_$ sync\_fetch\_and\_add() to add vertices to the tail of the queue.

### 2.2 The Suitor Algorithm

We now present the Suitor algorithm, the currently best performing half-approx algorithm for weighted matching [13]. An important distinction of the Suitor algorithm relative to the Locally-Dominant algorithm is the absence of a central queue for active vertices that need to be considered for matching in a given iteration. Elimination of the queue makes the algorithm better suited for parallel implementation. Further, by paying careful attention to the vertex that is being processed, the Suitor algorithm proactively avoids unnecessary work. Similar to the Locally-Dominant algorithm, we again use vertex identities to break ties consistently. We also use the notion of locally-dominant edges in order to find candidate edges for matching. The Suitor algorithm is detailed in Algorithm 3.

Parallelism is achieved by distributing the executions of the outer for loop (Line 6 in Algorithm 3) among the threads. Multiple threads will concurrently process different vertices, and attempt to find a suitable candidate for each. Since two variables, mate and ws, are shared among the participating threads, there is a need for explicit synchronization among the threads. We use OpenMP locks for synchronization. To prevent conflicts, we define a lock for each vertex (Line 5) and then require that a thread must acquire a partner's lock before executing lines 20 through 29, at which point the lock is released. Immediately after acquiring the lock we test if heaviest > ws[partner] is still true as it is possible that some other thread might have increased the value of ws[partner] after partner was determined to be the best match for current. If this is not the case, then current cannot be the suitor of partner and we must continue the search for next best candidate (lines 26 to 28). If a given vertex v ends up replacing another vertex was the mate, then the thread processing vertex v becomes responsible for finding a suitable mate for w. This is shown in lines 21 to 23. The algorithm terminates when all the vertices have been processed. We note that there is no strict order in which the vertices need to be processed.

The running time of the serial Suitor algorithm is  $O(\Sigma_{u \in V} |adj(u)|^2) = O(|E|\Delta)$

**Algorithm 3** Parallel Suitor algorithm. *Input*: graph G = (V, E). *Output*: A matching M represented in vector mate. *Data structures*: a vector ws of size |V| that stores the weight of the current heaviest neighbor of each vertex.

```

1: procedure OMP-SUITOR(G(V, E), mate)

for each u \in V in parallel do

2:

\mathsf{mate}[u] \leftarrow NULL

3:

ws[u] \leftarrow 0

4:

▷ Initialize the lock for each vertex

omp_init_lock[u]

5:

for each u \in V in parallel do

6:

current \leftarrow u

7:

done \leftarrow False

8:

9:

while (done = False) do

partner \leftarrow \mathsf{mate}[current]

10:

heaviest \leftarrow ws[current]

11:

next \leftarrow \emptyset

12:

for each v \in adj(current) do

▶ For all neighbors of current

13:

if w(current, v) > heaviest and w(current, v) > ws(v) then

14:

15:

partner \leftarrow v

heaviest \leftarrow w(current, v)

\triangleright Weight of edge (current, v)

16:

done \leftarrow True

17:

if heaviest \neq NULL then \triangleright True only if there is a candidate to match

18:

with

19:

omp_set_lock[partner]

▶ Lock the partner

if heaviest > ws[partner] then

20:

if mate[partner] \neq NULL then

\triangleright Check if partner had a

21:

previous offer

22:

next \leftarrow \mathsf{mate}[partner]

done \leftarrow False

23:

24:

mate[partner] \leftarrow current

25:

ws[partner] \leftarrow heaviest

else

26:

done \leftarrow False

27:

\triangleright The partner already has a better offer

28:

next \leftarrow u

omp_unset_lock[partner]

\triangleright Release the lock for partner

29:

if done = False then

30:

current \leftarrow next

▷ Continue the search for next best candidate

31:

```

as a node u might have to traverse its neighbor list |adj(u)| times to find a new partner. Note that  $\Delta$  is the maximum degree in G.

## 3 Architecture and Challenges

The NVIDIA Tesla K40, based on the Kepler architecture, is currently the most powerful single chip GPU board for scientific computing. There exists a dual chip board, Tesla K80, which trades off some of the peak performance of each chip to obtain higher combined performance and has better compute-to-shared-memory and register ratios, but requires multi-gpu programming techniques for effective utilization. The new GPUs based on the Maxwell architecture are more power efficient, but they are primarily targeted for single-precision computation and gaming applications. Their double precision performance is  $\frac{1}{32}$  of the single precision performance.